Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 5712                                                      |

| Number of Logic Elements/Cells | 57120                                                     |

| Total RAM Bits                 | 5215104                                                   |

| Number of I/O                  | 773                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                           |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s60f1020c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2. Stratix Architecture

\$51002-3.2

# Functional Description

Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291 MHz. These blocks are grouped into columns across the device in between certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269 MHz. Several M-RAM blocks are located individually or in pairs within the device's logic array.

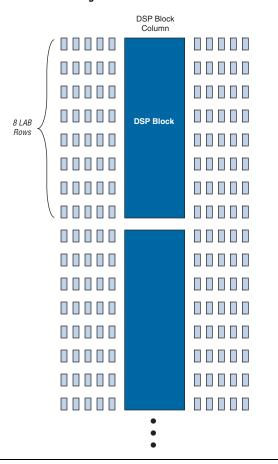

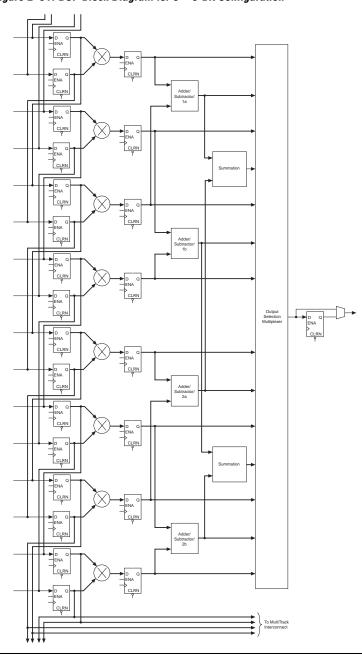

Digital signal processing (DSP) blocks can implement up to either eight full-precision  $9\times 9$ -bit multipliers, four full-precision  $18\times 18$ -bit multipliers, or one full-precision  $36\times 36$ -bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.

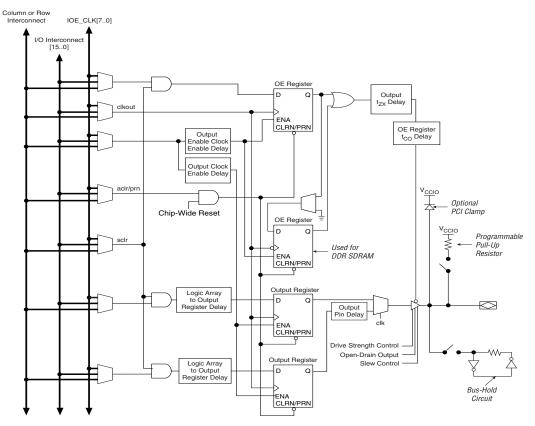

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with

#### Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums: data1 + data2 + carry-in0 or data1 + data2 + carry-in1. The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out 0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

| Table 2–3. TriMatrix Memory Features (Part 2 of 2) |                                                                         |                                                                                                  |                                                                                                                  |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |  |  |  |

| Configurations                                     | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |  |  |

*Notes to Table 2–3:*

- (1) See Table 4–36 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix device must write to the dual-port memory once and then disable the write-enable ports afterwards.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

#### **Memory Modes**

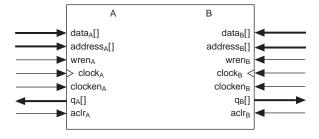

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2-12. True Dual-Port Memory Configuration

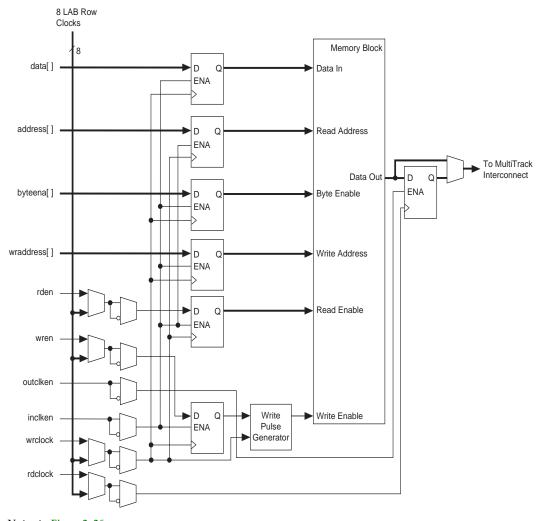

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The eight labelk signals or local interconnect can drive the inclock, outclock, wren, rden, inclr, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, LEs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–15 shows the M512 RAM block control signal generation logic.

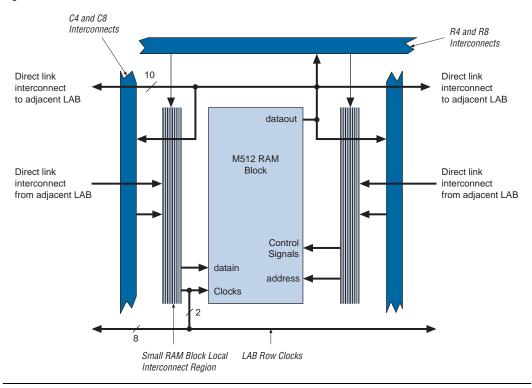

The RAM blocks within Stratix devices have local interconnects to allow LEs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, R8, C4, C8, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. Up to 10 direct link input connections to the M512 RAM block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through 10 direct link interconnects. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–16 shows the M512 RAM block to logic array interface.

Figure 2-16. M512 RAM Block LAB Row Interface

#### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

Figure 2–26. Input/Output Clock Mode in Simple Dual-Port Mode Notes (1), (2)

#### Notes to Figure 2–26:

- (1) All registers shown except the rden register have asynchronous clear ports.

- (2) Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

Figure 2-29. DSP Blocks Arranged in Columns

Figure 2–31. DSP Block Diagram for  $9 \times 9$ -Bit Configuration

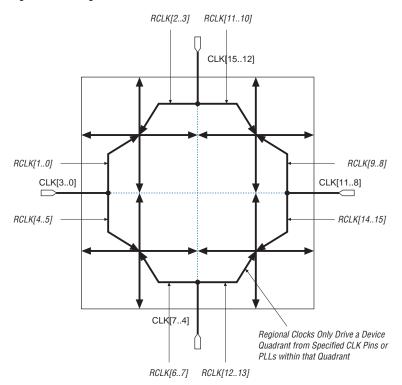

Figure 2-43. Regional Clocks

#### Fast Regional Clock Network

In EP1S25, EP1S20, and EP1S10 devices, there are two fast regional clock networks, FCLK [1..0], within each quadrant, fed by input pins that can connect to fast regional clock networks (see Figure 2–44). In EP1S30 and larger devices, there are two fast regional clock networks within each half-quadrant (see Figure 2–45). Dual-purpose FCLK pins drive the fast clock networks. All devices have eight FCLK pins to drive fast regional clock networks. Any I/O pin can drive a clock or control signal onto any fast regional clock network with the addition of a delay. This signal is driven via the I/O interconnect. The fast regional clock networks can also be driven from internal logic elements.

bandwidth is tuned by varying the charge pump current, loop filter resistor value, high frequency capacitor value, and *m* counter value. You can manually adjust these values if desired. Bandwidth is programmable from 200 kHz to 1.5 MHz.

#### External Clock Outputs

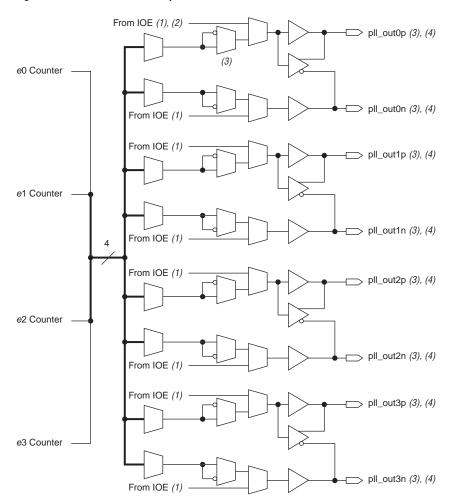

Enhanced PLLs 5 and 6 each support up to eight single-ended clock outputs (or four differential pairs). Differential SSTL and HSTL outputs are implemented using 2 single-ended output buffers which are programmed to have opposite polarity. In Quartus II software, simply assign the appropriate differential I/O standard and the software will implement the inversion. See Figure 2–55.

Figure 2-55. External Clock Outputs for PLLs 5 & 6

#### *Notes to Figure 2–55:*

- (1) The design can use each external clock output pin as a general-purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

- (3) EP1S10, EP1S20, and EP1S25 devices in 672-pin BGA and 484- and 672-pin FineLine BGA packages only have two pairs of external clocks (i.e., pll\_out0p, pll\_out0n, pll\_out1p, and pll\_out1n).

- (4) Differential SSTL and HSTL outputs are implemented using two single-ended output buffers, which are programmed to have opposite polarity.

Figure 2–67. Stratix IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–67:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

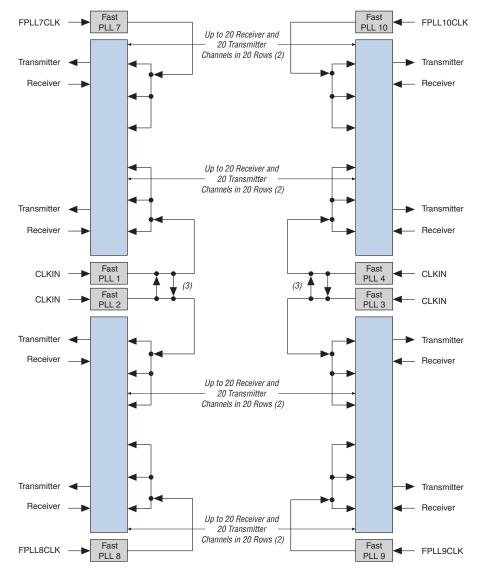

Figure 2-75. Fast PLL & Channel Layout in the EP1S30 to EP1S80 Devices Note (1)

#### Notes to Figure 2-75:

- (1) Wire-bond packages support up to 624 Mbps.

- (2) See Table 2–38 through 2–41 for the number of channels each device supports.

- (3) There is a multiplexer here to select the PLL clock source. If a PLL uses this multiplexer to clock channels outside of its bank quadrant, those clocked channels support up to 840 Mbps for "high" speed channels and 462 Mbps for "low" speed channels as labeled in the device pin-outs at www.altera.com.

| Table 4–7. 1.8-V I/O Specifications |                           |                                               |                          |                        |      |  |  |  |  |

|-------------------------------------|---------------------------|-----------------------------------------------|--------------------------|------------------------|------|--|--|--|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum                  | Maximum                | Unit |  |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                                               | 1.65                     | 1.95                   | V    |  |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                               | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                               | -0.3                     | $0.35 \times V_{CCIO}$ | ٧    |  |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ to } -8 \text{ mA } (10)$ | V <sub>CCIO</sub> - 0.45 |                        | ٧    |  |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 to 8 mA (10)              |                          | 0.45                   | V    |  |  |  |  |

| Table 4–8.        | Table 4–8. 1.5-V I/O Specifications |                              |                        |                         |      |  |  |  |  |  |

|-------------------|-------------------------------------|------------------------------|------------------------|-------------------------|------|--|--|--|--|--|

| Symbol            | Parameter                           | Conditions                   | Minimum                | Maximum                 | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage               |                              | 1.4                    | 1.6                     | V    |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage            |                              | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.3 | V    |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage             |                              | -0.3                   | $0.35 \times V_{CCIO}$  | V    |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage           | I <sub>OH</sub> = -2 mA (10) | $0.75 \times V_{CCIO}$ |                         | V    |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage            | I <sub>OL</sub> = 2 mA (10)  |                        | $0.25 \times V_{CCIO}$  | V    |  |  |  |  |  |

#### Notes to Tables 4–1 through 4–8:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns, or overshoot to the voltage shown in Table 4–9, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.5 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 1 of 2) |     |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Vin (V) Maximum Duty Cycle (%)                                              |     |  |  |  |  |  |  |

| 4.0                                                                         | 100 |  |  |  |  |  |  |

| 4.1                                                                         | 90  |  |  |  |  |  |  |

| 4.2                                                                         | 50  |  |  |  |  |  |  |

| Symbol              | Parameter                   | Conditions                     | Minimum                  | Typical          | Maximum                  | Unit |

|---------------------|-----------------------------|--------------------------------|--------------------------|------------------|--------------------------|------|

| V <sub>CCIO</sub>   | Output supply voltage       |                                | 1.65                     | 1.8              | 1.95                     | V    |

| V <sub>REF</sub>    | Reference voltage           |                                | 0.8                      | 0.9              | 1.0                      | V    |

| V <sub>TT</sub>     | Termination voltage         |                                | V <sub>REF</sub> - 0.04  | V <sub>REF</sub> | V <sub>REF</sub> + 0.04  | V    |

| V <sub>IH(DC)</sub> | High-level DC input voltage |                                | V <sub>REF</sub> + 0.125 |                  |                          | V    |

| V <sub>IL(DC)</sub> | Low-level DC input voltage  |                                |                          |                  | V <sub>REF</sub> - 0.125 | V    |

| V <sub>IH(AC)</sub> | High-level AC input voltage |                                | V <sub>REF</sub> + 0.275 |                  |                          | V    |

| V <sub>IL(AC)</sub> | Low-level AC input voltage  |                                |                          |                  | V <sub>REF</sub> - 0.275 | V    |

| V <sub>OH</sub>     | High-level output voltage   | $I_{OH} = -6.7 \text{ mA}$ (3) | V <sub>TT</sub> + 0.475  |                  |                          | V    |

| V <sub>OL</sub>     | Low-level output voltage    | $I_{OL} = 6.7 \text{ mA } (3)$ |                          |                  | V <sub>TT</sub> – 0.475  | V    |

| Table 4–19          | Table 4–19. SSTL-18 Class II Specifications |                                 |                          |           |                          |      |  |  |  |  |  |

|---------------------|---------------------------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|--|--|

| Symbol              | Parameter                                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>   | Output supply voltage                       |                                 | 1.65                     | 1.8       | 1.95                     | V    |  |  |  |  |  |

| $V_{REF}$           | Reference voltage                           |                                 | 0.8                      | 0.9       | 1.0                      | V    |  |  |  |  |  |

| V <sub>TT</sub>     | Termination voltage                         |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V    |  |  |  |  |  |

| V <sub>IH(DC)</sub> | High-level DC input voltage                 |                                 | V <sub>REF</sub> + 0.125 |           |                          | ٧    |  |  |  |  |  |

| V <sub>IL(DC)</sub> | Low-level DC input voltage                  |                                 |                          |           | V <sub>REF</sub> – 0.125 | V    |  |  |  |  |  |

| V <sub>IH(AC)</sub> | High-level AC input voltage                 |                                 | V <sub>REF</sub> + 0.275 |           |                          | V    |  |  |  |  |  |

| V <sub>IL(AC)</sub> | Low-level AC input voltage                  |                                 |                          |           | V <sub>REF</sub> - 0.275 | V    |  |  |  |  |  |

| V <sub>OH</sub>     | High-level output voltage                   | $I_{OH} = -13.4 \text{ mA}$ (3) | V <sub>TT</sub> + 0.630  |           |                          | V    |  |  |  |  |  |

| V <sub>OL</sub>     | Low-level output voltage                    | I <sub>OL</sub> = 13.4 mA (3)   |                          |           | V <sub>TT</sub> – 0.630  | V    |  |  |  |  |  |

| Table 4–42. M-RA<br>Descriptions (Pa | M Block Internal Timing Microparameter<br>rt 2 of 2)                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                               | Parameter                                                                                                                                                                                                                                                                                                                                                 |

| $t_{MRAMDATABH}$                     | B port hold time after clock                                                                                                                                                                                                                                                                                                                              |

| t <sub>MRAMADDRBSU</sub>             | B port address setup time before clock                                                                                                                                                                                                                                                                                                                    |

| t <sub>MRAMADDRBH</sub>              | B port address hold time after clock                                                                                                                                                                                                                                                                                                                      |

| t <sub>MRAMDATACO1</sub>             | Clock-to-output delay when using output registers                                                                                                                                                                                                                                                                                                         |

| t <sub>MRAMDATACO2</sub>             | Clock-to-output delay without output registers                                                                                                                                                                                                                                                                                                            |

| † <sub>MRAMCLKHL</sub>               | Register minimum clock high or low time. This is a limit on the min time for the clock on the registers in these blocks. The actual performance is dependent upon the internal point-to-point delays in the blocks and may give slower performance as shown in Table 4–36 on page 4–20 and as reported by the timing analyzer in the Quartus II software. |

| t <sub>MRAMCLR</sub>                 | Minimum clear pulse width.                                                                                                                                                                                                                                                                                                                                |

| Table 4-81. I         | Table 4–81. EP1S40 External I/O Timing on Column Pins Using Global Clock Networks |       |         |                |       |                |       |                |      |  |  |

|-----------------------|-----------------------------------------------------------------------------------|-------|---------|----------------|-------|----------------|-------|----------------|------|--|--|

| Davamatav             | -5 Speed Grade                                                                    |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |      |  |  |

| Parameter             | Min                                                                               | Max   | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |  |

| t <sub>INSU</sub>     | 2.126                                                                             |       | 2.268   |                | 2.558 |                | 2.930 |                | ns   |  |  |

| t <sub>INH</sub>      | 0.000                                                                             |       | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCO</sub>    | 2.856                                                                             | 5.585 | 2.856   | 5.987          | 2.856 | 6.541          | 2.847 | 7.253          | ns   |  |  |

| t <sub>XZ</sub>       | 2.796                                                                             | 5.459 | 2.796   | 5.855          | 2.796 | 6.417          | 2.787 | 7.138          | ns   |  |  |

| t <sub>ZX</sub>       | 2.796                                                                             | 5.459 | 2.796   | 5.855          | 2.796 | 6.417          | 2.787 | 7.138          | ns   |  |  |

| t <sub>INSUPLL</sub>  | 1.466                                                                             |       | 1.455   |                | 1.711 |                | 1.906 |                | ns   |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                             |       | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |  |

| t <sub>OUTCOPLL</sub> | 1.092                                                                             | 2.345 | 1.092   | 2.510          | 1.092 | 2.455          | 1.089 | 2.473          | ns   |  |  |

| t <sub>XZPLL</sub>    | 1.032                                                                             | 2.219 | 1.032   | 2.378          | 1.032 | 2.331          | 1.029 | 2.358          | ns   |  |  |

| t <sub>ZXPLL</sub>    | 1.032                                                                             | 2.219 | 1.032   | 2.378          | 1.032 | 2.331          | 1.029 | 2.358          | ns   |  |  |

| Table 4-82. I      | Table 4–82. EP1S40 External I/O Timing on Row Pins Using Fast Regional Clock Networks |       |                |       |                |       |                |       |      |  |  |

|--------------------|---------------------------------------------------------------------------------------|-------|----------------|-------|----------------|-------|----------------|-------|------|--|--|

| Parameter          | -5 Speed Grade                                                                        |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |       | Unit |  |  |

|                    | Min                                                                                   | Max   | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |

| t <sub>INSU</sub>  | 2.472                                                                                 |       | 2.685          |       | 3.083          |       | 3.056          |       | ns   |  |  |

| t <sub>INH</sub>   | 0.000                                                                                 |       | 0.000          |       | 0.000          |       | 0.000          |       | ns   |  |  |

| t <sub>OUTCO</sub> | 2.631                                                                                 | 5.258 | 2.631          | 5.625 | 2.631          | 6.105 | 2.745          | 7.324 | ns   |  |  |

| t <sub>XZ</sub>    | 2.658                                                                                 | 5.312 | 2.658          | 5.681 | 2.658          | 6.173 | 2.772          | 7.406 | ns   |  |  |

| t <sub>ZX</sub>    | 2.658                                                                                 | 5.312 | 2.658          | 5.681 | 2.658          | 6.173 | 2.772          | 7.406 | ns   |  |  |

Tables 4–105 through 4–108 show the output adder delays associated with column and row I/O pins for both fast and slow slew rates. If an I/O standard is selected other than 3.3-V LVTTL 4mA or LVCMOS 2 mA with a fast slew rate, add the selected delay to the external  $t_{\rm OUTCO}$ ,  $t_{\rm OUTCOPLL}$ ,  $t_{\rm XZ}$ ,  $t_{\rm XZPLL}$ , and  $t_{\rm ZXPLL}$  I/O parameters shown in Table 4–55 on page 4–36 through Table 4–96 on page 4–56.

| Table 4–105. Stratix I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 1 of 2) |       |                  |       |         |                |     |         |                |       |      |

|-------------------------------------------------------------------------------------------------------|-------|------------------|-------|---------|----------------|-----|---------|----------------|-------|------|

| Donomo                                                                                                |       | -5 Speed Grade - |       | -6 Spee | -6 Speed Grade |     | d Grade | -8 Speed Grade |       | 11   |

| Parame                                                                                                | ter   | Min              | Max   | Min     | Max            | Min | Max     | Min            | Max   | Unit |

| LVCMOS                                                                                                | 2 mA  |                  | 1,895 |         | 1,990          |     | 1,990   |                | 1,990 | ps   |

|                                                                                                       | 4 mA  |                  | 956   |         | 1,004          |     | 1,004   |                | 1,004 | ps   |

|                                                                                                       | 8 mA  |                  | 189   |         | 198            |     | 198     |                | 198   | ps   |

|                                                                                                       | 12 mA |                  | 0     |         | 0              |     | 0       |                | 0     | ps   |

|                                                                                                       | 24 mA |                  | -157  |         | -165           |     | -165    |                | -165  | ps   |

| 3.3-V LVTTL                                                                                           | 4 mA  |                  | 1,895 |         | 1,990          |     | 1,990   |                | 1,990 | ps   |

|                                                                                                       | 8 mA  |                  | 1,347 |         | 1,414          |     | 1,414   |                | 1,414 | ps   |

|                                                                                                       | 12 mA |                  | 636   |         | 668            |     | 668     |                | 668   | ps   |

|                                                                                                       | 16 mA |                  | 561   |         | 589            |     | 589     |                | 589   | ps   |

|                                                                                                       | 24 mA |                  | 0     |         | 0              |     | 0       |                | 0     | ps   |

| 2.5-V LVTTL                                                                                           | 2 mA  |                  | 2,517 |         | 2,643          |     | 2,643   |                | 2,643 | ps   |

|                                                                                                       | 8 mA  |                  | 834   |         | 875            |     | 875     |                | 875   | ps   |

|                                                                                                       | 12 mA |                  | 504   |         | 529            |     | 529     |                | 529   | ps   |

|                                                                                                       | 16 mA |                  | 194   |         | 203            |     | 203     |                | 203   | ps   |

| 1.8-V LVTTL                                                                                           | 2 mA  |                  | 1,304 |         | 1,369          |     | 1,369   |                | 1,369 | ps   |

|                                                                                                       | 8 mA  |                  | 960   |         | 1,008          |     | 1,008   |                | 1,008 | ps   |

|                                                                                                       | 12 mA |                  | 960   |         | 1,008          |     | 1,008   |                | 1,008 | ps   |

| 1.5-V LVTTL                                                                                           | 2 mA  |                  | 6,680 |         | 7,014          |     | 7,014   |                | 7,014 | ps   |

|                                                                                                       | 4 mA  |                  | 3,275 |         | 3,439          |     | 3,439   |                | 3,439 | ps   |

|                                                                                                       | 8 mA  |                  | 1,589 |         | 1,668          |     | 1,668   |                | 1,668 | ps   |

| GTL                                                                                                   | •     |                  | 16    |         | 17             |     | 17      |                | 17    | ps   |

| GTL+                                                                                                  |       |                  | 9     |         | 9              |     | 9       |                | 9     | ps   |

| 3.3-V PCI                                                                                             |       |                  | 50    |         | 52             |     | 52      |                | 52    | ps   |

| 3.3-V PCI-X 1.0                                                                                       | )     |                  | 50    |         | 52             |     | 52      |                | 52    | ps   |

| Compact PCI                                                                                           |       |                  | 50    |         | 52             |     | 52      |                | 52    | ps   |

| AGP 1×                                                                                                |       |                  | 50    |         | 52             |     | 52      |                | 52    | ps   |

| AGP 2×                                                                                                |       |                  | 1,895 |         | 1,990          |     | 1,990   |                | 1,990 | ps   |

| Table 4–108.   | Table 4–108. Stratix I/O Standard Output Delay Adders for Slow Slew Rate on Row Pins |                |       |         |                |     |                |     |                |      |

|----------------|--------------------------------------------------------------------------------------|----------------|-------|---------|----------------|-----|----------------|-----|----------------|------|

| I/O Stand      | dord.                                                                                | -5 Speed Grade |       | -6 Spee | -6 Speed Grade |     | -7 Speed Grade |     | -8 Speed Grade |      |

| I/U Statit     | ıaru                                                                                 | Min            | Max   | Min     | Max            | Min | Max            | Min | Max            | Unit |

| LVCMOS         | 2 mA                                                                                 |                | 1,571 |         | 1,650          |     | 1,650          |     | 1,650          | ps   |

|                | 4 mA                                                                                 |                | 594   |         | 624            |     | 624            |     | 624            | ps   |

|                | 8 mA                                                                                 |                | 208   |         | 218            |     | 218            |     | 218            | ps   |

|                | 12 mA                                                                                |                | 0     |         | 0              |     | 0              |     | 0              | ps   |

| 3.3-V LVTTL    | 4 mA                                                                                 |                | 1,571 |         | 1,650          |     | 1,650          |     | 1,650          | ps   |

|                | 8 mA                                                                                 |                | 1,393 |         | 1,463          |     | 1,463          |     | 1,463          | ps   |

|                | 12 mA                                                                                |                | 596   |         | 626            |     | 626            |     | 626            | ps   |

|                | 16 mA                                                                                |                | 562   |         | 590            |     | 590            |     | 590            | ps   |

| 2.5-V LVTTL    | 2 mA                                                                                 |                | 2,562 |         | 2,690          |     | 2,690          |     | 2,690          | ps   |

|                | 8 mA                                                                                 |                | 1,343 |         | 1,410          |     | 1,410          |     | 1,410          | ps   |

|                | 12 mA                                                                                |                | 864   |         | 907            |     | 907            |     | 907            | ps   |

|                | 16 mA                                                                                |                | 945   |         | 992            |     | 992            |     | 992            | ps   |

| 1.8-V LVTTL    | 2 mA                                                                                 |                | 6,306 |         | 6,621          |     | 6,621          |     | 6,621          | ps   |

|                | 8 mA                                                                                 |                | 3,369 |         | 3,538          |     | 3,538          |     | 3,538          | ps   |

|                | 12 mA                                                                                |                | 2,932 |         | 3,079          |     | 3,079          |     | 3,079          | ps   |

| 1.5-V LVTTL    | 2 mA                                                                                 |                | 9,759 |         | 10,247         |     | 10,247         |     | 10,247         | ps   |

|                | 4 mA                                                                                 |                | 6,830 |         | 7,172          |     | 7,172          |     | 7,172          | ps   |

|                | 8 mA                                                                                 |                | 5,699 |         | 5,984          |     | 5,984          |     | 5,984          | ps   |

| GTL+           |                                                                                      |                | -333  |         | -350           |     | -350           |     | -350           | ps   |

| CTT            |                                                                                      |                | 591   |         | 621            |     | 621            |     | 621            | ps   |

| SSTL-3 Class I |                                                                                      |                | 267   |         | 280            |     | 280            |     | 280            | ps   |

| SSTL-3 Class I | I                                                                                    |                | -346  |         | -363           |     | -363           |     | -363           | ps   |

| SSTL-2 Class I |                                                                                      |                | 481   | _       | 505            |     | 505            | _   | 505            | ps   |

| SSTL-2 Class I | I                                                                                    |                | -58   |         | -61            |     | -61            |     | -61            | ps   |

| SSTL-18 Class  | I                                                                                    |                | 2,207 |         | 2,317          |     | 2,317          |     | 2,317          | ps   |

| 1.5-V HSTL Cla | ass I                                                                                |                | 1,966 |         | 2,064          |     | 2,064'         |     | 2,064          | ps   |

| 1.8-V HSTL Cla | ass I                                                                                |                | 1,208 |         | 1,268          |     | 1,460          |     | 1,720          | ps   |