Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 7904                                                     |

| Number of Logic Elements/Cells | 79040                                                    |

| Total RAM Bits                 | 7427520                                                  |

| Number of I/O                  | 773                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                          |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s80f1020c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Designs.                                                                                                                                                                                                        |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <pre><pre><pre></pre></pre></pre></file>                                                                                                                                                                         |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| • •                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

|                                             | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

x Altera Corporation

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix® devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version                                          | Changes Made                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | July 2005, v3.2                                       | Minor content changes.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|         | September 2004, v3.1 • Updated Table 1–6 on page 1–5. |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|         | April 2004, v3.0                                      | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |  |  |  |  |  |

|         | January 2004, v2.2                                    | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|         | October 2003, v2.1                                    | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|         | July 2003, v2.0                                       | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

Altera Corporation Section I–1

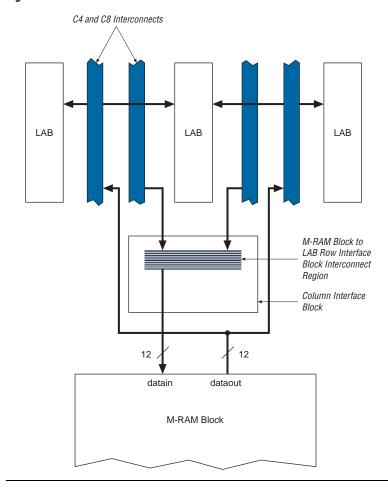

blocks facing to the left, and another 10 possible from the right adjacent LABs for M-RAM blocks facing to the right. For column interfacing, every M-RAM column unit connects to the right and left column lines, allowing each M-RAM column unit to communicate directly with three columns of LABs. Figures 2–21 through 2–23 show the interface between the M-RAM block and the logic array.

Figure 2–23. M-RAM Column Unit Interface to Interconnect

#### Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output block and can be used as an accumulator or as an adder/subtractor.

#### Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or subtraction using the addnsub independent control signal for each first-level adder in  $18 \times 18$ -bit mode. There are two addnsub [1..0] signals available in a DSP block for any configuration. For  $9 \times 9$ -bit mode, one addnsub [1..0] signal controls the top two one-level adders and another addnsub [1..0] signal controls the bottom two one-level adders. A high addnsub signal indicates addition, and a low signal indicates subtraction. The addnsub control signal can be unregistered or registered once or twice when feeding the adder blocks to match data path pipelines.

The signa and signb signals serve the same function as the multiplier block signa and signb signals. The only difference is that these signals can be registered up to two times. These signals are tied to the same signa and signb signals from the multiplier and must be connected to the same clocks and control signals.

#### Accumulator

When configured for accumulation, the adder/output block output feeds back to the accumulator as shown in Figure 2–34. The accum\_sload[1..0] signal synchronously loads the multiplier result to the accumulator output. This signal can be unregistered or registered once or twice. Additionally, the overflow signal indicates the accumulator has overflowed or underflowed in accumulation mode. This signal is always registered and must be externally latched in LEs if the design requires a latched overflow signal.

#### Summation

The output of the adder/subtractor/accumulator block feeds to an optional summation block. This block sums the outputs of the DSP block multipliers. In 9  $\times$  9-bit mode, there are two summation blocks providing the sums of two sets of four 9  $\times$  9-bit multipliers. In 18  $\times$  18-bit mode, there is one summation providing the sum of one set of four 18  $\times$  18-bit multipliers.

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

DSP Block OA[17..0] MultiTrack MultiTrack Interconnect \ Interconnect A1[17..0] OB[17..0] B1[17..0] OC[17..0] A2[17..0] OD[17..0] B2[17..0] OE[17..0] A3[17..0] OF[17..0] B3[17..0] OG[17..0] A4[17..0] OH[17..0] ►B4[17..0]

Figure 2-40. DSP Block Interconnect Interface

Table 2–19 shows the enhanced PLL and fast PLL features in Stratix devices.

| Feature                           | Enhanced PLL                                                    | Fast PLL                           |  |  |

|-----------------------------------|-----------------------------------------------------------------|------------------------------------|--|--|

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)                           | m/(post-scale counter) (2)         |  |  |

| Phase shift                       | Down to 156.25-ps increments (3), (4)                           | Down to 125-ps increments (3), (4) |  |  |

| Delay shift                       | 250-ps increments for ±3 ns                                     |                                    |  |  |

| Clock switchover                  | <b>✓</b>                                                        |                                    |  |  |

| PLL reconfiguration               | <b>✓</b>                                                        |                                    |  |  |

| Programmable bandwidth            | <b>✓</b>                                                        |                                    |  |  |

| Spread spectrum clocking          | ✓                                                               |                                    |  |  |

| Programmable duty cycle           | <b>✓</b>                                                        | ✓                                  |  |  |

| Number of internal clock outputs  | 6                                                               | 3 (5)                              |  |  |

| Number of external clock outputs  | Four differential/eight singled-ended or one single-ended $(6)$ | (7)                                |  |  |

| Number of feedback clock inputs   | 2 (8)                                                           |                                    |  |  |

#### Notes to Table 2-19:

- (1) For enhanced PLLs, *m*, *n*, range from 1 to 512 and post-scale counters *g*, *l*, *e* range from 1 to 1024 with 50% duty cycle. With a non-50% duty cycle the post-scale counters *g*, *l*, *e* range from 1 to 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7, 8, 9, and 10 have two output ports per PLL. PLLs 1, 2, 3, and 4 have three output ports per PLL.

- (6) Every Stratix device has two enhanced PLLs (PLLs 5 and 6) with either eight single-ended outputs or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EPIS80, EPIS60, and EPIS40 devices each have one single-ended output. Devices in the 780 pin FineLine BGA packages do not support PLLs 11 and 12.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

#### PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

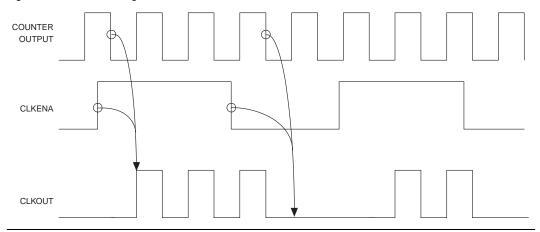

resynchronization or relock period. The clkena signal can also disable clock outputs if the system is not tolerant to frequency overshoot during resynchronization.

The extclkena signals work in the same way as the clkena signals, but they control the external clock output counters (e0, e1, e2, and e3). Upon re-enabling, the PLL does not need a resynchronization or relock period unless the PLL is using external feedback mode. In order to lock in external feedback mode, the external output must drive the board trace back to the FBIN pin.

Figure 2-57. extclkena Signals

#### **Fast PLLs**

Stratix devices contain up to eight fast PLLs with high-speed serial interfacing ability, along with general-purpose features. Figure 2–58 shows a diagram of the fast PLL.

| Table 2- | Table 2–37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2) Note (1) |                 |          |                            |                  |       |       |       |  |  |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|----------------------------|------------------|-------|-------|-------|--|--|--|

|          | Package                                                                                 | Transmitter/    | Total    | Maximum<br>Speed<br>(Mbps) | Center Fast PLLs |       |       |       |  |  |  |

| Device   |                                                                                         | Receiver        | Channels |                            | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |

| EP1S25   | 672-pin FineLine BGA                                                                    | Transmitter (2) | 56       | 624 (4)                    | 14               | 14    | 14    | 14    |  |  |  |

|          | 672-pin BGA                                                                             |                 |          | 624 (3)                    | 28               | 28    | 28    | 28    |  |  |  |

|          |                                                                                         | Receiver        | 58       | 624 (4)                    | 14               | 15    | 15    | 14    |  |  |  |

|          |                                                                                         |                 |          | 624 (3)                    | 29               | 29    | 29    | 29    |  |  |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 70       | 840 (4)                    | 18               | 17    | 17    | 18    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)                    | 35               | 35    | 35    | 35    |  |  |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)                    | 17               | 16    | 16    | 17    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)                    | 33               | 33    | 33    | 33    |  |  |  |

|          | 1,020-pin FineLine                                                                      | Transmitter (2) | 78       | 840 (4)                    | 19               | 20    | 20    | 19    |  |  |  |

|          | BGA                                                                                     |                 |          | 840 (3)                    | 39               | 39    | 39    | 39    |  |  |  |

|          |                                                                                         | Receiver        | 78       | 840 (4)                    | 19               | 20    | 20    | 19    |  |  |  |

|          |                                                                                         |                 |          | 840 (3)                    | 39               | 39    | 39    | 39    |  |  |  |

#### Notes to Table 2–37:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at 840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) The number of channels listed includes the transmitter clock output (tx\_outclock) channel. If the design requires a DDR clock, it can use an extra data channel.

- (3) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if, for example, PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

- (4) These values show the channels available for each PLL without crossing another bank.

When you span two I/O banks using cross-bank support, you can route only two load enable signals total between the PLLs. When you enable rx\_data\_align, you use both rxloadena and txloadena of a PLL. That leaves no loadena for the second PLL.

| Table 2-39            | Table 2–39. EP1S40 Differential Channels (Part 2 of 2) Note (1) |                       |                 |                  |           |           |           |                           |           |           |        |  |

|-----------------------|-----------------------------------------------------------------|-----------------------|-----------------|------------------|-----------|-----------|-----------|---------------------------|-----------|-----------|--------|--|

|                       | Transmitter/                                                    | Total                 | Maximum         | Center Fast PLLs |           |           |           | Corner Fast PLLs (2), (3) |           |           |        |  |

| Package               | Receiver                                                        | Channels              | Speed<br>(Mbps) | PLL1             | PLL2      | PLL3      | PLL4      | PLL7                      | PLL8      | PLL9      | PLL10  |  |

| 956-pin               | Transmitter                                                     | 80                    | 840             | 18               | 17        | 17        | 18        | 20                        | 20        | 20        | 20     |  |

| BGA                   | (4)                                                             |                       | 840 (5)         | 35               | 35        | 35        | 35        | 20                        | 20        | 20        | 20     |  |

|                       | Receiver                                                        | 80                    | 840             | 20               | 20        | 20        | 20        | 18                        | 17        | 17        | 18     |  |

|                       |                                                                 |                       | 840 (5)         | 40               | 40        | 40        | 40        | 18                        | 17        | 17        | 18     |  |

| 1,020-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2)        | 17<br>(3) | 17<br>(3) | 18<br>(2) | 20                        | 20        | 20        | 20     |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 35<br>(5) | 20                        | 20        | 20        | 20     |  |

|                       | Receiver 80 (10 (7)                                             | 80 (10)<br><i>(7)</i> | 840             | 20               | 20        | 20        | 20        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40               | 40        | 40        | 40        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |  |

| 1,508-pin<br>FineLine | Transmitter (4)                                                 | 80 (10)<br><i>(7)</i> | 840             | 18<br>(2)        | 17<br>(3) | 17<br>(3) | 18<br>(2) | 20                        | 20        | 20        | 20     |  |

| BGA                   |                                                                 |                       | 840 (5), (8)    | 35<br>(5)        | 35<br>(5) | 35<br>(5) | 35<br>(5) | 20                        | 20        | 20        | 20     |  |

|                       | Receiver                                                        | 80 (10)<br><i>(7)</i> | 840             | 20               | 20        | 20        | 20        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |  |

|                       |                                                                 |                       | 840 (5), (8)    | 40               | 40        | 40        | 40        | 18<br>(2)                 | 17<br>(3) | 17<br>(3) | 18 (2) |  |

| Table 2–40. EP1S60 Differential Channels (Part 1 of 2) Note (1) |                |                   |                     |                                            |      |      |      |      |      |      |          |

|-----------------------------------------------------------------|----------------|-------------------|---------------------|--------------------------------------------|------|------|------|------|------|------|----------|

| Package                                                         | Transmitter/   | Total<br>Channels | Maximum             | Center Fast PLLs Corner Fast PLLs (2), (3) |      |      |      |      |      |      | (2), (3) |

|                                                                 | Receiver       |                   | Speed<br>(Mbps)     | PLL1                                       | PLL2 | PLL3 | PLL4 | PLL7 | PLL8 | PLL9 | PLL10    |

| 956-pin                                                         | Transmitter 80 | smitter 80        | 840                 | 12                                         | 10   | 10   | 12   | 20   | 20   | 20   | 20       |

| BGA                                                             |                |                   | 840 (5), (8)        | 22                                         | 22   | 22   | 22   | 20   | 20   | 20   | 20       |

|                                                                 | Receiver       | 80                | 840                 | 20                                         | 20   | 20   | 20   | 12   | 10   | 10   | 12       |

|                                                                 |                |                   | 840 <i>(5), (8)</i> | 40                                         | 40   | 40   | 40   | 12   | 10   | 10   | 12       |

The Stratix device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix devices.

| Table 3–2. Stratix Boundary-Scan Register Length |                               |  |  |  |  |  |  |

|--------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| Device                                           | Boundary-Scan Register Length |  |  |  |  |  |  |

| EP1S10                                           | 1,317                         |  |  |  |  |  |  |

| EP1S20                                           | 1,797                         |  |  |  |  |  |  |

| EP1S25                                           | 2,157                         |  |  |  |  |  |  |

| EP1S30                                           | 2,253                         |  |  |  |  |  |  |

| EP1S40                                           | 2,529                         |  |  |  |  |  |  |

| EP1S60                                           | 3,129                         |  |  |  |  |  |  |

| EP1S80                                           | 3,777                         |  |  |  |  |  |  |

| Table 3–3 | Table 3–3. 32-Bit Stratix Device IDCODE |                       |                                    |                 |  |  |  |  |  |  |

|-----------|-----------------------------------------|-----------------------|------------------------------------|-----------------|--|--|--|--|--|--|

|           | IDCODE (32 Bits) (1)                    |                       |                                    |                 |  |  |  |  |  |  |

| Device    | Version (4 Bits)                        | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |  |  |  |  |

| EP1S10    | 0000                                    | 0010 0000 0000 0001   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S20    | 0000                                    | 0010 0000 0000 0010   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S25    | 0000                                    | 0010 0000 0000 0011   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S30    | 0000                                    | 0010 0000 0000 0100   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S40    | 0000                                    | 0010 0000 0000 0101   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S60    | 0000                                    | 0010 0000 0000 0110   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

| EP1S80    | 0000                                    | 0010 0000 0000 0111   | 000 0110 1110                      | 1               |  |  |  |  |  |  |

Notes to Tables 3-2 and 3-3:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

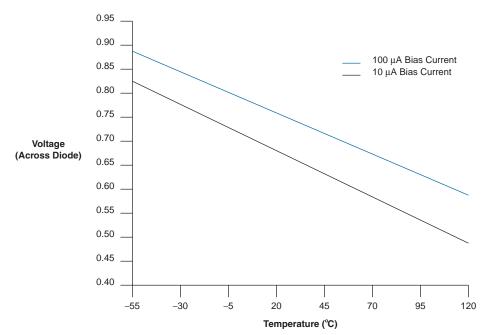

The temperature-sensing diode works for the entire operating range shown in Figure 3–6.

Figure 3-6. Temperature vs. Temperature-Sensing Diode Voltage

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 2 of 2) |                        |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|------------------------|--|--|--|--|--|--|

| Vin (V)                                                                     | Maximum Duty Cycle (%) |  |  |  |  |  |  |

| 4.3                                                                         | 30                     |  |  |  |  |  |  |

| 4.4                                                                         | 17                     |  |  |  |  |  |  |

| 4.5                                                                         | 10                     |  |  |  |  |  |  |

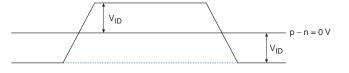

Figures 4–1 and 4–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 4-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform Positive Channel (p) = $V_{IH}$ Negative Channel (n) = $V_{IL}$

#### **Differential Waveform**

| Symbol                  | Parameter                                                                   | Conditions                                                                                 | Minimum | Typical | Maximum | Unit |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>ICM</sub>        | Input common mode voltage (6)                                               | LVDS<br>$0.3 \text{ V} \leq \text{V}_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10 | 100     |         | 1,100   | mV   |

|                         |                                                                             | LVDS<br>$0.3 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 1  through  10        | 1,600   |         | 1,800   | mV   |

|                         |                                                                             | LVDS<br>0.2 V ≤V <sub>ID</sub> ≤1.0 V<br>W = 1                                             | 1,100   |         | 1,600   | mV   |

|                         |                                                                             | LVDS<br>$0.1 \text{ V} \leq V_{\text{ID}} \leq 1.0 \text{ V}$<br>W = 2  through  10        | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1)     | Output differential voltage (single-ended)                                  | R <sub>L</sub> = 100 Ω                                                                     | 250     | 375     | 550     | mV   |

| Δ V <sub>OD</sub>       | Change in V <sub>OD</sub> between high and low                              | R <sub>L</sub> = 100 Ω                                                                     |         |         | 50      | mV   |

| V <sub>OCM</sub>        | Output common mode voltage                                                  | $R_L = 100 \Omega$                                                                         | 1,125   | 1,200   | 1,375   | mV   |

| $\Delta V_{\text{OCM}}$ | Change in V <sub>OCM</sub> between high and low                             | $R_L = 100 \Omega$                                                                         |         |         | 50      | mV   |

| R <sub>L</sub>          | Receiver differential input discrete resistor (external to Stratix devices) |                                                                                            | 90      | 100     | 110     | Ω    |

| Table 4-36          | Table 4–36. Stratix Performance (Part 2 of 2) Notes (1), (2) |     |                               |               |                      |                      |                      |                      |       |  |  |

|---------------------|--------------------------------------------------------------|-----|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|-------|--|--|

|                     |                                                              | F   | Resources L                   | Jsed          |                      | Р                    | erforman             | ce                   |       |  |  |

|                     | Applications                                                 | LEs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | -8<br>Speed<br>Grade | Units |  |  |

| TriMatrix<br>memory | True dual-port<br>RAM 16K × 36 bit                           | 0   | 1                             | 0             | 269.83               | 237.69               | 206.82               | 175.74               | MHz   |  |  |

| M-RAM<br>block      | Single port<br>RAM 32K × 18 bit                              | 0   | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |  |

|                     | Simple dual-port<br>RAM 32K × 18 bit                         | 0   | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |  |

|                     | True dual-port<br>RAM 32K × 18 bit                           | 0   | 1                             | 0             | 275.86               | 244.55               | 212.76               | 180.83               | MHz   |  |  |

|                     | Single port<br>RAM 64K × 9 bit                               | 0   | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |  |

|                     | Simple dual-port<br>RAM 64K × 9 bit                          | 0   | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |  |

|                     | True dual-port<br>RAM 64K × 9 bit                            | 0   | 1                             | 0             | 287.85               | 253.29               | 220.36               | 187.26               | MHz   |  |  |

| DSP block           | 9 × 9-bit multiplier (3)                                     | 0   | 0                             | 1             | 335.0                | 293.94               | 255.68               | 217.24               | MHz   |  |  |

|                     | 18 × 18-bit multiplier (4)                                   | 0   | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |  |  |

|                     | $36 \times 36$ -bit multiplier (4)                           | 0   | 0                             | 1             | 148.25               | 134.71               | 117.16               | 99.59                | MHz   |  |  |

|                     | 36 × 36-bit multiplier (5)                                   | 0   | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.5                | MHz   |  |  |

|                     | 18-bit, 4-tap FIR filter                                     | 0   | 0                             | 1             | 278.78               | 237.41               | 206.52               | 175.50               | MHz   |  |  |

| Larger<br>Designs   | 8-bit, 16-tap parallel<br>FIR filter                         | 58  | 0                             | 4             | 141.26               | 133.49               | 114.88               | 100.28               | MHz   |  |  |

|                     | 8-bit, 1,024-point FFT function                              | 870 | 5                             | 1             | 261.09               | 235.51               | 205.21               | 175.22               | MHz   |  |  |

#### Notes to Table 4–36:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) Numbers not listed will be included in a future version of the data sheet.

- (3) This application uses registered inputs and outputs.

- (4) This application uses registered multiplier input and output stages within the DSP block.

- (5) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

Table 4–116. Stratix Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins in Flip-Chip Packages

| I/O Standard                  | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|-------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| LVTTL                         | 422               | 422               | 390               | 390               | MHz  |

| 2.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.8 V                         | 422               | 422               | 390               | 390               | MHz  |

| 1.5 V                         | 422               | 422               | 390               | 390               | MHz  |

| LVCMOS                        | 422               | 422               | 390               | 390               | MHz  |

| GTL+                          | 300               | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-3 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class I                | 400               | 350               | 300               | 300               | MHz  |

| SSTL-2 Class II               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class I               | 400               | 350               | 300               | 300               | MHz  |

| SSTL-18 Class II              | 400               | 350               | 300               | 300               | MHz  |

| 1.5-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| 1.8-V HSTL Class I            | 400               | 350               | 300               | 300               | MHz  |

| СТТ                           | 300               | 250               | 200               | 200               | MHz  |

| Differential 1.5-V HSTL<br>C1 | 400               | 350               | 300               | 300               | MHz  |

| LVPECL (1)                    | 645               | 645               | 640               | 640               | MHz  |

| PCML (1)                      | 300               | 275               | 275               | 275               | MHz  |

| LVDS (1)                      | 645               | 645               | 640               | 640               | MHz  |

| HyperTransport technology (1) | 500               | 500               | 450               | 450               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12] Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| LVCMOS       | 422               | 390               | 390               | MHz  |

| GTL          | 250               | 200               | 200               | MHz  |

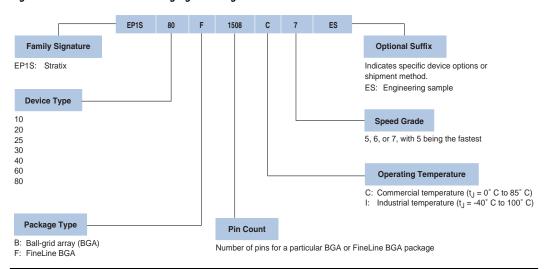

Figure 5-1. Stratix Device Packaging Ordering Information

### Index

| A                                        | Open-Drain Output 2–120                     |

|------------------------------------------|---------------------------------------------|

| Accumulator 2–63                         | Power Sequencing & Hot Socketing 2–140      |

| Adder/Output Blocks 2–61                 | Programmable Drive Strength 2–119           |

| Adder/Subtractor                         | Programmable Pull-Up Resistor 2–122         |

| 2–63                                     | Simple Multiplier Mode 2–64                 |

| Accumulator                              | Single-Port Mode 2–51                       |

| 2–63                                     | Slew-Rate Control 2–120                     |

| AGP 1x Specifications 4–13               | Two-Multipliers                             |

| AGP 2x Specifications 4–13               | Adder Mode 2–67                             |

| Architecture 2–1                         | Adder Mode Implementing Complex             |

| 36 x 36 Multiply Mode 2–66               | Multiply 2–68                               |

| addnsub Signal 2–8                       |                                             |

| Block Diagram 2–2                        | C                                           |

| Bus Hold 2–121                           |                                             |

| Byte Alignment 2–140                     | Class I Specifications 4–11, 4–12           |

| Carry-Select Chain 2–11                  | Class II Specifications 4–11, 4–12, 4–13    |

| Clear & Preset Logic Control 2–13        | Clocks                                      |

| Combined Resources 2–78                  | Clock Feedback 2–96                         |

| Dedicated Circuitry 2–137                | Clock Multiplication & Division 2–88, 2–101 |

| Device Resources 2–3                     | Clock Switchover                            |

| Device Routing Scheme 2–20               | 2–88                                        |

| Digital Signal Processing Block 2–52     | Delay 2–97                                  |

| Direct Link Connection 2–5               | EP1S10, EP1S20 & EP1S25                     |

| Dynamic Arithmetic Mode 2–10             | Device I/O Clock Groups                     |

| in LE 2–11                               | 2–80                                        |

| Four-Multipliers                         | EP1S25, EP1S20 & EP1S10 Device Fast Clock   |

| Adder Mode 2–68                          | Pin Connections to Fast Regional            |

| Functional Description 2–1               | Clocks 2–77                                 |

| LAB                                      | EP1S30 Device Fast Regional Clock Pin Con-  |

| Interconnects 2–4                        | nections to Fast Regional Clocks 2–78       |

| Logic Array Blocks 2–3                   | EP1S30, EP1S40, EP1S60, EP1S80              |

| Structure 2–4                            | Device I/O Clock Groups                     |

| LE Operating Modes 2–8                   | 2–81                                        |

| Logic Elements 2–6                       | External Clock                              |

| Modes of Operation 2–64                  | Inputs 2–102                                |

| Multiplier Size & Configurations per DSP | Outputs 2–92, 2–103                         |

| block 2–70                               | Outputs for Enhanced PLLs 11 & 12 2–95      |

| Multiply-Accumulator Mode 2–67           | Outputs for PLLs 5 & 6 2–93                 |

| MultiTrack Interconnect 2–14             | Fast Regional Clock External I/O Timing     |

| Normal Mode 2–9                          | Parameters 4–34                             |

| in I F 2_0                               | Fast Regional Clock Network 2–76            |

Altera Corporation Index-1