Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 7904                                                        |

| Number of Logic Elements/Cells | 79040                                                       |

| Total RAM Bits                 | 7427520                                                     |

| Number of I/O                  | 773                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s80f1020c7nga |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2005 v3.2       | <ul> <li>Added "Clear Signals" section.</li> <li>Updated "Power Sequencing &amp; Hot Socketing" section.</li> <li>Format changes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated fast regional clock networks description on page 2–73.</li> <li>Deleted the word preliminary from the "specification for the maximum time to relock is 100 µs" on page 2–90.</li> <li>Added information about differential SSTL and HSTL outputs in "External Clock Outputs" on page 2–92.</li> <li>Updated notes in Figure 2–55 on page 2–93.</li> <li>Added information about <i>m</i> counter to "Clock Multiplication &amp; Division" on page 2–101.</li> <li>Updated Note 1 in Table 2–58 on page 2–101.</li> <li>Updated description of "Clock Multiplication &amp; Division" on page 2–88.</li> <li>Updated Table 2–22 on page 2–102.</li> <li>Added references to AN 349 and AN 329 to "External RAM Interfacing" on page 2–115.</li> <li>Table 2–25 on page 2–116: updated the table, updated Notes 3 and 4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.</li> <li>Updated Table 2–26 on page 2–117.</li> <li>Added information about PCI Compliance to page 2–120.</li> <li>Table 2–32 on page 2–126: updated the table and deleted Note 1.</li> <li>Updated reference to device pin-outs now being available on the web on page 2–130.</li> <li>Added Notes 4 and 5 to Table 2–36 on page 2–130.</li> <li>Updated Note 3 in Table 2–37 on page 2–131.</li> <li>Updated Note 5 in Table 2–41 on page 2–135.</li> </ul> |

|         | April 2004, v3.0     | <ul> <li>Added note 3 to rows 11 and 12 in Table 2–18.</li> <li>Deleted "Stratix and Stratix GX Device PLL Availability" table.</li> <li>Added I/O standards row in Table 2–28 that support max and min strength.</li> <li>Row clk [1,3,8,10] was removed from Table 2–30.</li> <li>Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology rows in Table 2–32.</li> <li>Removed the Left and Right I/O Banks row in Table 2–34.</li> <li>Changed RCLK values in Figures 2–50 and 2–51.</li> <li>External RAM Interfacing section replaced.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | November 2003, v2.2  | <ul> <li>Added 672-pin BGA package information in Table 2–37.</li> <li>Removed support for series and parallel on-chip termination.</li> <li>Termination Technology renamed differential on-chip termination.</li> <li>Updated the number of channels per PLL in Tables 2-38 through 2-42.</li> <li>Updated Figures 2–65 and 2–67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | October 2003, v2.1   | <ul> <li>Updated DDR I information.</li> <li>Updated Table 2–22.</li> <li>Added Tables 2–25, 2–29, 2–30, and 2–72.</li> <li>Updated Figures 2–59, 2–65, and 2–67.</li> <li>Updated the Lock Detect section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Section I–2 Altera Corporation

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | January 2005, 3.2    | Updated rise and fall input values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated Note 3 in Table 4–8 on page 4–4.</li> <li>Updated Table 4–10 on page 4–6.</li> <li>Updated Table 4–20 on page 4–12 through Table 4–23 on page 4–13. Added rows V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub> to each table.</li> <li>Updated Table 4–26 on page 4–14 through Table 4–29 on page 4–15.</li> <li>Updated Table 4–31 on page 4–16.</li> <li>Updated Table 4–36 on page 4–20.</li> <li>Added signals t<sub>OUTCO</sub>, T<sub>XZ</sub>, and T<sub>ZX</sub> to Figure 4–4 on page 4–33.</li> <li>Added rows t<sub>M512CLKENSU</sub> and t<sub>M512CLKENH</sub> to Table 4–40 on page 4–24.</li> <li>Added rows t<sub>M4CLKENSU</sub> and t<sub>M4CLKENH</sub> to Table 4–41 on page 4–24.</li> <li>Updated Note 2 in Table 4–54 on page 4–35.</li> <li>Added rows t<sub>MRAMCLKENSU</sub> and t<sub>MRAMCLKENH</sub> to Table 4–42 on page 4–25.</li> <li>Updated Table 4–46 on page 4–29.</li> <li>Updated Table 4–47 on page 4–29.</li> </ul> |

Section I–4 Altera Corporation

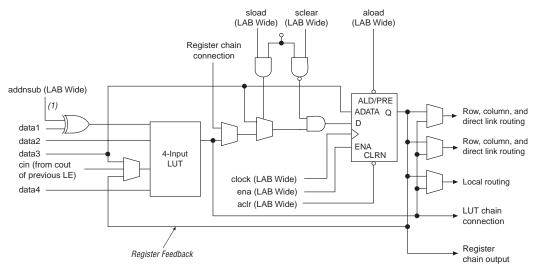

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

### **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 2–14 for more information on LUT chain and register chain connections.

### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

# **LE Operating Modes**

The Stratix LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear,

asynchronous preset load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes. The addnsub control signal is allowed in arithmetic mode.

The Quartus II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinatorial functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–6). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinatorial output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

Figure 2-6. LE in Normal Mode

Note to Figure 2-6:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

can drive other R8 interconnects to extend their range as well as C8 interconnects for row-to-row connections. One R8 interconnect is faster than two R4 interconnects connected together.

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–10 shows the LUT chain and register chain interconnects.

| Table 2–3. TriMatrix Memory Features (Part 2 of 2) |                                                                         |                                                                                                  |                                                                                                                  |  |  |  |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |  |  |  |  |  |  |

| Configurations                                     | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |  |  |  |  |  |

*Notes to Table 2–3:*

- (1) See Table 4–36 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix device must write to the dual-port memory once and then disable the write-enable ports afterwards.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

# **Memory Modes**

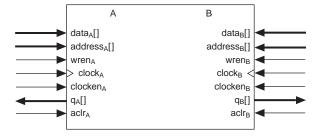

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2-12. True Dual-Port Memory Configuration

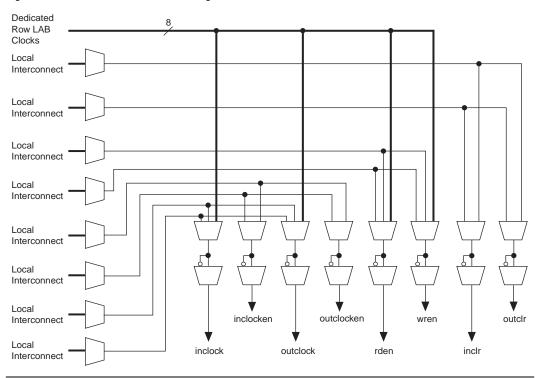

Figure 2-15. M512 RAM Block Control Signals

Table 2–14 shows the summary of input register modes for the DSP block.

| Table 2–14. Input Register Modes                               |          |   |   |  |  |  |  |  |  |

|----------------------------------------------------------------|----------|---|---|--|--|--|--|--|--|

| Register Input Mode $9 \times 9$ $18 \times 18$ $36 \times 36$ |          |   |   |  |  |  |  |  |  |

| Parallel input                                                 | <b>✓</b> | ✓ | ✓ |  |  |  |  |  |  |

| Shift register input                                           | ✓        | ✓ |   |  |  |  |  |  |  |

### Multiplier

The multiplier supports  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multiplication. Each DSP block supports eight possible  $9 \times 9$ -bit or smaller multipliers. There are four multiplier blocks available for multipliers larger than  $9 \times 9$  bits but smaller than  $18 \times 18$  bits. There is one multiplier block available for multipliers larger than  $18 \times 18$  bits but smaller than or equal to  $36 \times 36$  bits. The ability to have several small multipliers is useful in applications such as video processing. Large multipliers greater than  $18 \times 18$  bits are useful for applications such as the mantissa multiplication of a single-precision floating-point number.

The multiplier operands can be signed or unsigned numbers, where the result is signed if either input is signed as shown in Table 2–15. The sign\_a and sign\_b signals provide dynamic control of each operand's representation: a logic 1 indicates the operand is a signed number, a logic 0 indicates the operand is an unsigned number. These sign signals affect all multipliers and adders within a single DSP block and you can register them to match the data path pipeline. The multipliers are full precision (that is, 18 bits for the 18-bit multiply, 36-bits for the 36-bit multiply, and so on) regardless of whether sign\_a or sign\_b set the operands as signed or unsigned numbers.

| Table 2–15. Multiplier S | Table 2–15. Multiplier Signed Representation |          |  |  |  |  |  |  |  |

|--------------------------|----------------------------------------------|----------|--|--|--|--|--|--|--|

| Data A                   | Result                                       |          |  |  |  |  |  |  |  |

| Unsigned                 | Unsigned                                     | Unsigned |  |  |  |  |  |  |  |

| Unsigned                 | Signed                                       | Signed   |  |  |  |  |  |  |  |

| Signed                   | Unsigned                                     | Signed   |  |  |  |  |  |  |  |

| Signed                   | Signed                                       | Signed   |  |  |  |  |  |  |  |

During switchover, the PLL VCO continues to run and will either slow down or speed up, generating frequency drift on the PLL outputs. The clock switchover transitions without any glitches. After the switch, there is a finite resynchronization period to lock onto new clock as the VCO ramps up. The exact amount of time it takes for the PLL to relock relates to the PLL configuration and may be adjusted by using the programmable bandwidth feature of the PLL. The specification for the maximum time to relock is  $100~\mu s$ .

For more information on clock switchover, see *AN 313, Implementing Clock Switchover in Stratix & Stratix GX Devices*.

### PLL Reconfiguration

The PLL reconfiguration feature enables system logic to change Stratix device enhanced PLL counters and delay elements without reloading a Programmer Object File (.pof). This provides considerable flexibility for frequency synthesis, allowing real-time PLL frequency and output clock delay variation. You can sweep the PLL output frequencies and clock delay in prototype environments. The PLL reconfiguration feature can also dynamically or intelligently control system clock speeds or  $t_{\rm CO}$  delays in end systems.

Clock delay elements at each PLL output port implement variable delay. Figure 2–54 shows a diagram of the overall dynamic PLL control feature for the counters and the clock delay elements. The configuration time is less than 20 µs for the enhanced PLL using a input shift clock rate of 22 MHz. The charge pump, loop filter components, and phase shifting using VCO phase taps cannot be dynamically adjusted.

### Control Signals

The fast PLL has the same lock output, pllenable input, and are set input control signals as the enhanced PLL.

If the input clock stops and causes the PLL to lose lock, then the PLL must be reset for correct phase shift operation.

For more information on high-speed differential I/O support, see "High-Speed Differential I/O Support" on page 2–130.

# I/O Structure

IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Differential on-chip termination for LVDS I/O standard

- Programmable pull-up during configuration

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double-data rate (DDR) Registers

The IOE in Stratix devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–59 shows the Stratix IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

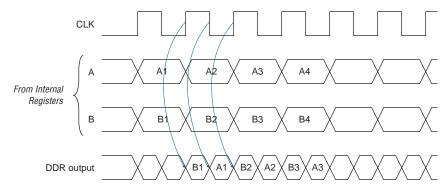

Figure 2-68. Output Timing Diagram in DDR Mode

The Stratix IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. Stratix device I/O pins transfer data on a DDR bidirectional bus to support DDR SDRAM. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

# **External RAM Interfacing**

Stratix devices support DDR SDRAM at up to 200 MHz (400-Mbps data rate) through dedicated phase-shift circuitry, QDR and QDRII SRAM interfaces up to 167 MHz, and ZBT SRAM interfaces up to 200 MHz. Stratix devices also provide preliminary support for reduced latency DRAM II (RLDRAM II) at rates up to 200 MHz through the dedicated phase-shift circuitry.

In addition to the required signals for external memory interfacing, Stratix devices offer the optional clock enable signal. By default the Quartus II software sets the clock enable signal high, which tells the output register to update with new values. The output registers hold their own values if the design sets the clock enable signal low. See Figure 2–64.

To find out more about the DDR SDRAM specification, see the JEDEC web site (www.jedec.org). For information on memory controller megafunctions for Stratix devices, see the Altera web site (www.altera.com). See AN 342: Interfacing DDR SDRAM with Stratix & Stratix GX Devices for more information on DDR SDRAM interface in Stratix. Also see AN 349: QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices and AN 329: ZBT SRAM Controller Reference Design for Stratix & Stratix GX Devices.

- RapidIO

- HyperTransport

### **Dedicated Circuitry**

Stratix devices support source-synchronous interfacing with LVDS, LVPECL, 3.3-V PCML, or HyperTransport signaling at up to 840 Mbps. Stratix devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by a integer factor W (W = 1 through 32). For example, a HyperTransport application where the data rate is 800 Mbps and the clock rate is 400 MHz would require that W be set to 2. The SERDES factor J determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor J can be set to 4, 7, 8, or 10 and does not have to equal the PLL clock-multiplication W value. For a J factor of 1, the Stratix device bypasses the SERDES block. For a J factor of 2, the Stratix device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. See Figure 2–73.

R4, R8, and R24 Interconnect 840 Mbps 840 Mbps 8 Data Dedicated Dedicated Local Receiver Transmitter Interconnect Interface Interface rx load en 8× 8× 105 MHz Fast tx\_load\_en PLL Regional or global clock

Figure 2–73. High-Speed Differential I/O Receiver / Transmitter Interface Example

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed differential I/O clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array.

# **Timing Model**

The DirectDrive<sup>TM</sup> technology and MultiTrack<sup>TM</sup> interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix device densities and speed grades. This section describes and specifies the performance, internal, external, and PLL timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

# **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 4–35 shows the status of the Stratix device timing models.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| ble 4–35. Stratix Device Timing Model Status |             |          |  |  |  |  |  |  |

|----------------------------------------------|-------------|----------|--|--|--|--|--|--|

| Device                                       | Preliminary | Final    |  |  |  |  |  |  |

| EP1S10                                       |             | ✓        |  |  |  |  |  |  |

| EP1S20                                       |             | ✓        |  |  |  |  |  |  |

| EP1S25                                       |             | ✓        |  |  |  |  |  |  |

| EP1S30                                       |             | ✓        |  |  |  |  |  |  |

| EP1S40                                       |             | ✓        |  |  |  |  |  |  |

| EP1S60                                       |             | ✓        |  |  |  |  |  |  |

| EP1S80                                       |             | <b>✓</b> |  |  |  |  |  |  |

# Stratix External I/O Timing

These timing parameters are for both column IOE and row IOE pins. In EP1S30 devices and above, you can decrease the  $t_{SU}$  time by using the FPLLCLK, but may get positive hold time in EP1S60 and EP1S80 devices. You should use the Quartus II software to verify the external devices for any pin.

Tables 4–55 through 4–60 show the external timing parameters on column and row pins for EP1S10 devices.

| Table 4–55. EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks         Note (1) |                |       |                |       |                |       |                |     |      |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|--|--|

|                                                                                                           | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |  |  |  |

| Parameter                                                                                                 | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |  |  |

| t <sub>INSU</sub>                                                                                         | 2.238          |       | 2.325          |       | 2.668          |       | NA             |     | ns   |  |  |  |

| t <sub>INH</sub>                                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |  |  |

| t <sub>OUTCO</sub>                                                                                        | 2.240          | 4.549 | 2.240          | 4.836 | 2.240          | 5.218 | NA             | NA  | ns   |  |  |  |

| t <sub>XZ</sub>                                                                                           | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |  |  |  |

| t <sub>ZX</sub>                                                                                           | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |  |  |  |

| Table 4–56. l         | Table 4–56. EP1S10 External I/O Timing on Column Pins Using Regional Clock Networks         Note (1) |       |         |                |       |                |    |         |      |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------|-------|---------|----------------|-------|----------------|----|---------|------|--|--|--|

|                       | -5 Speed Grade                                                                                       |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |    | d Grade |      |  |  |  |

| Parameter             | Min                                                                                                  | Max   | Min     | Max            | Min   | Max            |    |         | Unit |  |  |  |

| t <sub>INSU</sub>     | 1.992                                                                                                |       | 2.054   |                | 2.359 |                | NA |         | ns   |  |  |  |

| t <sub>INH</sub>      | 0.000                                                                                                |       | 0.000   |                | 0.000 |                | NA |         | ns   |  |  |  |

| t <sub>оитсо</sub>    | 2.395                                                                                                | 4.795 | 2.395   | 5.107          | 2.395 | 5.527          | NA | NA      | ns   |  |  |  |

| t <sub>XZ</sub>       | 2.335                                                                                                | 4.669 | 2.335   | 4.975          | 2.335 | 5.403          | NA | NA      | ns   |  |  |  |

| t <sub>ZX</sub>       | 2.335                                                                                                | 4.669 | 2.335   | 4.975          | 2.335 | 5.403          | NA | NA      | ns   |  |  |  |

| t <sub>INSUPLL</sub>  | 0.975                                                                                                |       | 0.985   |                | 1.097 |                | NA |         | ns   |  |  |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                                |       | 0.000   |                | 0.000 |                | NA | NA      | ns   |  |  |  |

| t <sub>OUTCOPLL</sub> | 1.262                                                                                                | 2.636 | 1.262   | 2.680          | 1.262 | 2.769          | NA | NA      | ns   |  |  |  |

| t <sub>XZPLL</sub>    | 1.202                                                                                                | 2.510 | 1.202   | 2.548          | 1.202 | 2.645          | NA | NA      | ns   |  |  |  |

| t <sub>ZXPLL</sub>    | 1.202                                                                                                | 2.510 | 1.202   | 2.548          | 1.202 | 2.645          | NA | NA      | ns   |  |  |  |

| Davamatav             | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | -8 Spee | d Grade |      |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|------|

| Parameter             | Min     | Max     | Min     | Max     | Min     | Max     | Min     | Max     | Unit |

| t <sub>INSU</sub>     | 1.647   |         | 1.692   |         | 1.940   |         | NA      |         | ns   |

| t <sub>INH</sub>      | 0.000   |         | 0.000   |         | 0.000   |         | NA      |         | ns   |

| t <sub>outco</sub>    | 2.619   | 5.184   | 2.619   | 5.515   | 2.619   | 5.999   | NA      | NA      | ns   |

| t <sub>XZ</sub>       | 2.559   | 5.058   | 2.559   | 5.383   | 2.559   | 5.875   | NA      | NA      | ns   |

| t <sub>ZX</sub>       | 2.559   | 5.058   | 2.559   | 5.383   | 2.559   | 5.875   | NA      | NA      | ns   |

| t <sub>INSUPLL</sub>  | 1.239   |         | 1.229   |         | 1.374   |         | NA      |         | ns   |

| t <sub>INHPLL</sub>   | 0.000   |         | 0.000   |         | 0.000   |         | NA      |         | ns   |

| t <sub>OUTCOPLL</sub> | 1.109   | 2.372   | 1.109   | 2.436   | 1.109   | 2.492   | NA      | NA      | ns   |

| t <sub>XZPLL</sub>    | 1.049   | 2.246   | 1.049   | 2.304   | 1.049   | 2.368   | NA      | NA      | ns   |

| t <sub>ZXPLL</sub>    | 1.049   | 2.246   | 1.049   | 2.304   | 1.049   | 2.368   | NA      | NA      | ns   |

| Table 4–58. EP1S10 External I/O Timing on Row Pin Using Fast Regional Clock Network Note (1) |                |       |                |       |                |       |                |     |      |  |  |  |

|----------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|--|--|--|

|                                                                                              | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |  |  |  |

| Parameter                                                                                    | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |  |  |  |

| t <sub>INSU</sub>                                                                            | 2.212          |       | 2.403          |       | 2.759          |       | NA             |     | ns   |  |  |  |

| t <sub>INH</sub>                                                                             | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |  |  |  |

| t <sub>OUTCO</sub>                                                                           | 2.391          | 4.838 | 2.391          | 5.159 | 2.391          | 5.569 | NA             | NA  | ns   |  |  |  |

| t <sub>XZ</sub>                                                                              | 2.418          | 4.892 | 2.418          | 5.215 | 2.418          | 5.637 | NA             | NA  | ns   |  |  |  |

| t <sub>ZX</sub>                                                                              | 2.418          | 4.892 | 2.418          | 5.215 | 2.418          | 5.637 | NA             | NA  | ns   |  |  |  |

|                       | -5 Speed Grade |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | d Grade |      |

|-----------------------|----------------|-------|---------|----------------|-------|----------------|-----|---------|------|

| Parameter             | Min            | Max   | Min     | Max            | Min   | Max            | Min | Max     | Unit |

| t <sub>INSU</sub>     | 1.351          |       | 1.479   |                | 1.699 |                | NA  |         | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000   |                | 0.000 |                | NA  |         | ns   |

| t <sub>outco</sub>    | 2.732          | 5.380 | 2.732   | 5.728          | 2.732 | 6.240          | NA  | NA      | ns   |

| t <sub>XZ</sub>       | 2.672          | 5.254 | 2.672   | 5.596          | 2.672 | 6.116          | NA  | NA      | ns   |

| t <sub>ZX</sub>       | 2.672          | 5.254 | 2.672   | 5.596          | 2.672 | 6.116          | NA  | NA      | ns   |

| t <sub>INSUPLL</sub>  | 0.923          |       | 0.971   |                | 1.098 |                | NA  |         | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000   |                | 0.000 |                | NA  |         | ns   |

| t <sub>OUTCOPLL</sub> | 1.210          | 2.544 | 1.210   | 2.648          | 1.210 | 2.715          | NA  | NA      | ns   |

| t <sub>XZPLL</sub>    | 1.150          | 2.418 | 1.150   | 2.516          | 1.150 | 2.591          | NA  | NA      | ns   |

| t <sub>ZXPLL</sub>    | 1.150          | 2.418 | 1.150   | 2.516          | 1.150 | 2.591          | NA  | NA      | ns   |

| Table 4–64. EP1S20 External I/O Timing on Row Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |       |  |

|------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|-------|--|

| D                                                                                              | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     | 11-24 |  |

| Parameter                                                                                      | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit  |  |

| t <sub>INSU</sub>                                                                              | 2.032          |       | 2.207          |       | 2.535          |       | NA             |     | ns    |  |

| t <sub>INH</sub>                                                                               | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns    |  |

| t <sub>OUTCO</sub>                                                                             | 2.492          | 5.018 | 2.492          | 5.355 | 2.492          | 5.793 | NA             | NA  | ns    |  |

| t <sub>XZ</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns    |  |

| t <sub>ZX</sub>                                                                                | 2.519          | 5.072 | 2.519          | 5.411 | 2.519          | 5.861 | NA             | NA  | ns    |  |

Output

Buffer

OUTPUT

VMEAS

R<sub>UP</sub>

R<sub>S</sub>

R<sub>DN</sub>

C<sub>L</sub>

GND

Figure 4-7. Output Delay Timing Reporting Setup Modeled by Quartus II

#### *Notes to Figure 4–7:*

- Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2)  $V_{CCINT}$  is 1.42-V unless otherwise specified.

**Table 4–101.** Reporting Methodology For Maximum Timing For Single-Ended Output Pins (Part 1 of 2) Notes (1), (2), (3)

| 1/2.01                |                 | Measurement<br>Point |                |                     |                          |            |                        |                   |

|-----------------------|-----------------|----------------------|----------------|---------------------|--------------------------|------------|------------------------|-------------------|

| I/O Standard          | R <sub>UP</sub> | $R_{DN}$             | R <sub>S</sub> | R <sub>T</sub><br>Ω | V <sub>CCIO</sub><br>(V) | VTT<br>(V) | C <sub>L</sub><br>(pF) | V <sub>MEAS</sub> |

| 3.3-V LVTTL           | -               | -                    | 0              | -                   | 2.950                    | 2.95       | 10                     | 1.500             |

| 2.5-V LVTTL           | -               | -                    | 0              | -                   | 2.370                    | 2.37       | 10                     | 1.200             |

| 1.8-V LVTTL           | -               | -                    | 0              | -                   | 1.650                    | 1.65       | 10                     | 0.880             |

| 1.5-V LVTTL           | -               | -                    | 0              | -                   | 1.400                    | 1.40       | 10                     | 0.750             |

| 3.3-V LVCMOS          | _               | _                    | 0              | _                   | 2.950                    | 2.95       | 10                     | 1.500             |

| 2.5-V LVCMOS          | _               | _                    | 0              | _                   | 2.370                    | 2.37       | 10                     | 1.200             |

| 1.8-V LVCMOS          | -               | -                    | 0              | -                   | 1.650                    | 1.65       | 10                     | 0.880             |

| 1.5-V LVCMOS          | _               | _                    | 0              | _                   | 1.400                    | 1.40       | 10                     | 0.750             |

| 3.3-V GTL             | -               | -                    | 0              | 25                  | 2.950                    | 1.14       | 30                     | 0.740             |

| 2.5-V GTL             | _               | _                    | 0              | 25                  | 2.370                    | 1.14       | 30                     | 0.740             |

| 3.3-V GTL+            | _               | _                    | 0              | 25                  | 2.950                    | 1.35       | 30                     | 0.880             |

| 2.5-V GTL+            | -               | _                    | 0              | 25                  | 2.370                    | 1.35       | 30                     | 0.880             |

| 3.3-V SSTL-3 Class II | _               | _                    | 25             | 25                  | 2.950                    | 1.25       | 30                     | 1.250             |

| Table 4–104. Stratix I/O Standard Row Pin Input Delay Adders |                |      |                |      |                |      |                |      |      |

|--------------------------------------------------------------|----------------|------|----------------|------|----------------|------|----------------|------|------|

| Davis marks in                                               | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      | -8 Speed Grade |      |      |

| Parameter                                                    | Min            | Max  | Min            | Max  | Min            | Max  | Min            | Max  | Unit |

| LVCMOS                                                       |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 3.3-V LVTTL                                                  |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 2.5-V LVTTL                                                  |                | 21   |                | 22   |                | 25   |                | 29   | ps   |

| 1.8-V LVTTL                                                  |                | 181  |                | 190  |                | 218  |                | 257  | ps   |

| 1.5-V LVTTL                                                  |                | 300  |                | 315  |                | 362  |                | 426  | ps   |

| GTL+                                                         |                | -152 |                | -160 |                | -184 |                | -216 | ps   |

| CTT                                                          |                | -168 |                | -177 |                | -203 |                | -239 | ps   |

| SSTL-3 Class I                                               |                | -193 |                | -203 |                | -234 |                | -275 | ps   |

| SSTL-3 Class II                                              |                | -193 |                | -203 |                | -234 |                | -275 | ps   |

| SSTL-2 Class I                                               |                | -262 |                | -276 |                | -317 |                | -373 | ps   |

| SSTL-2 Class II                                              |                | -262 |                | -276 |                | -317 |                | -373 | ps   |

| SSTL-18 Class I                                              |                | -105 |                | -111 |                | -127 |                | -150 | ps   |

| SSTL-18 Class II                                             |                | 0    |                | 0    |                | 0    |                | 0    | ps   |

| 1.5-V HSTL Class I                                           |                | -151 |                | -159 |                | -183 |                | -215 | ps   |

| 1.8-V HSTL Class I                                           |                | -126 |                | -133 |                | -153 |                | -179 | ps   |

| LVDS                                                         |                | -149 |                | -157 |                | -180 |                | -212 | ps   |

| LVPECL                                                       |                | -149 |                | -157 |                | -180 |                | -212 | ps   |

| 3.3-V PCML                                                   |                | -65  |                | -69  |                | -79  |                | -93  | ps   |

| HyperTransport                                               |                | 77   |                | -81  |                | -93  |                | -110 | ps   |

| Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 2 of 2) |                                      |     |     |      |  |  |  |

|------------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|--|--|

| Symbol                                                                 | Parameter                            | Min | Max | Unit |  |  |  |

| t <sub>ARESET</sub>                                                    | Minimum pulse width on areset signal | 10  |     | ns   |  |  |  |

#### Notes to Tables 4–131 through 4–133:

- (1) See "Maximum Input & Output Clock Rates" on page 4–76.

- (2) PLLs 7, 8, 9, and 10 in the EP1S80 device support up to 717-MHz input and output.

- (3) Use this equation (f<sub>OUT</sub> = f<sub>IN</sub> \* ml(n × post-scale counter)) in conjunction with the specified f<sub>INPFD</sub> and f<sub>VCO</sub> ranges to determine the allowed PLL settings.

- (4) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (5) Refer to the section "High-Speed I/O Specification" on page 4–87 for more information.

- (6) This parameter is for high-speed differential I/O mode only.

- (7) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (8) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

# DLL Specifications

Table 4–134 reports the jitter for the DLL in the DQS phase shift reference circuit.

| Table 4–134. DLL Jitter for DQS Phase Shift Reference Circuit |       |  |  |  |  |

|---------------------------------------------------------------|-------|--|--|--|--|

| Frequency (MHz) DLL Jitter (ps)                               |       |  |  |  |  |

| 197 to 200                                                    | ± 100 |  |  |  |  |

| 160 to 196                                                    | ± 300 |  |  |  |  |

| 100 to 159                                                    | ± 500 |  |  |  |  |

For more information on DLL jitter, see the *DDR SRAM* section in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

Table 4–135 lists the Stratix DLL low frequency limit for full phase shift across all PVT conditions. The Stratix DLL can be used below these frequencies, but it will not achieve the full phase shift requested across all