Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 7904                                                       |

| Number of Logic Elements/Cells | 79040                                                      |

| Total RAM Bits                 | 7427520                                                    |

| Number of I/O                  | 1203                                                       |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1508-BBGA, FCBGA                                           |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1s80f1508c6aa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Chapter Revision Dates                                                                       | vii      |

|----------------------------------------------------------------------------------------------|----------|

| About This Handbook  How to Find Information  How to Contact Altera  Typographic Conventions | ix       |

|                                                                                              |          |

| Section I. Stratix Device Family Data Sheet                                                  |          |

| Revision History                                                                             | Part I–1 |

|                                                                                              |          |

| Chapter 1. Introduction                                                                      |          |

| Introduction                                                                                 |          |

| Features                                                                                     | 1–2      |

| Chantar 2 Strativ Architecture                                                               |          |

| Chapter 2. Stratix Architecture                                                              | 2.1      |

| Functional Description                                                                       |          |

| Logic Array Blocks                                                                           |          |

| LAB Interconnects                                                                            |          |

| LAB Control Signals                                                                          |          |

| Logic ElementsLUT Chain & Register Chain                                                     |          |

| addnsub Signal                                                                               |          |

| LE Operating Modes                                                                           |          |

| Clear & Preset Logic Control                                                                 |          |

| MultiTrack Interconnect                                                                      |          |

| TriMatrix Memory                                                                             |          |

| Memory Modes                                                                                 |          |

| Clear Signals                                                                                |          |

| Parity Bit Support                                                                           |          |

| Shift Register Support                                                                       |          |

| Memory Block Size                                                                            |          |

| Independent Clock Mode                                                                       |          |

| Input/Output Clock Mode                                                                      |          |

| Read/Write Clock Mode                                                                        |          |

| Single-Port Mode                                                                             |          |

| Multiplier Block                                                                             |          |

| Adder/Output Blocks                                                                          |          |

| Modes of Operation                                                                           |          |

| DSP Block Interface                                                                                                                                                                                                                                                                                                                                              | 2–70                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| PLLs & Clock Networks                                                                                                                                                                                                                                                                                                                                            |                     |

| Global & Hierarchical Clocking                                                                                                                                                                                                                                                                                                                                   | 2–73                |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                                                             |                     |

| Enhanced PLLs                                                                                                                                                                                                                                                                                                                                                    |                     |

| Fast PLLs                                                                                                                                                                                                                                                                                                                                                        | 2–100               |

| I/O Structure                                                                                                                                                                                                                                                                                                                                                    | 2–104               |

| Double-Data Rate I/O Pins                                                                                                                                                                                                                                                                                                                                        |                     |

| External RAM Interfacing                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Drive Strength                                                                                                                                                                                                                                                                                                                                      |                     |

| Open-Drain Output                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                                                                | 2–120               |

| Bus Hold                                                                                                                                                                                                                                                                                                                                                         |                     |

| Programmable Pull-Up Resistor                                                                                                                                                                                                                                                                                                                                    |                     |

| Advanced I/O Standard Support                                                                                                                                                                                                                                                                                                                                    |                     |

| Differential On-Chip Termination                                                                                                                                                                                                                                                                                                                                 |                     |

| MultiVolt I/O Interface                                                                                                                                                                                                                                                                                                                                          |                     |

| High-Speed Differential I/O Support                                                                                                                                                                                                                                                                                                                              |                     |

| Dedicated Circuitry                                                                                                                                                                                                                                                                                                                                              |                     |

| Byte Alignment                                                                                                                                                                                                                                                                                                                                                   |                     |

| Power Sequencing & Hot Socketing                                                                                                                                                                                                                                                                                                                                 |                     |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support SignalTap II Embedded Logic Analyzer Configuration Operating Modes Configuring Stratix FPGAs with JRunner Configuration Schemes Partial Reconfiguration Remote Update Configuration Modes Stratix Automated Single Event Upset (SEU) Detection Custom-Built Circuitry Software Interface Temperature Sensing Diode |                     |

| Chapter 4. DC & Switching Characteristics Operating Conditions Power Consumption Timing Model                                                                                                                                                                                                                                                                    | 4–1<br>4–17<br>4–19 |

| Preliminary & Final Timing                                                                                                                                                                                                                                                                                                                                       |                     |

| Performance                                                                                                                                                                                                                                                                                                                                                      |                     |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| External Timing Parameters                                                                                                                                                                                                                                                                                                                                       |                     |

| Stratix External I/O Timing                                                                                                                                                                                                                                                                                                                                      |                     |

| I/O Timing Measurement Methodology                                                                                                                                                                                                                                                                                                                               |                     |

| External I/O Delay Parameters                                                                                                                                                                                                                                                                                                                                    | 4–66                |

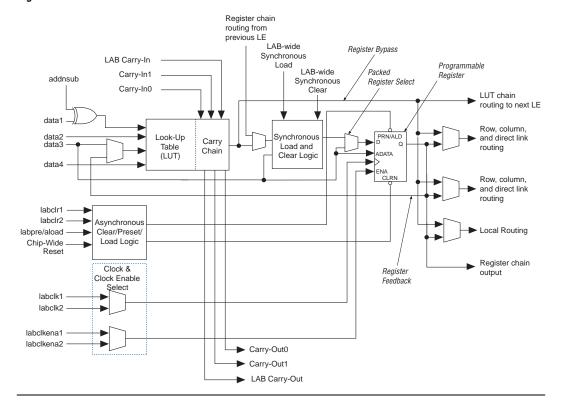

Figure 2-5. Stratix LE

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinatorial functions, the register is bypassed and the output of the LUT drives directly to the outputs of the LE.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and direct link routing connections and one drives local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated

| Table 2–3. TriMatrix Memory Features (Part 2 of 2) |                                                                         |                                                                                                  |                                                                                                                  |  |  |  |  |  |

|----------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |  |  |  |

| Configurations                                     | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |  |  |

*Notes to Table 2–3:*

- (1) See Table 4–36 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix device must write to the dual-port memory once and then disable the write-enable ports afterwards.

Violating the setup or hold time on the address registers could corrupt the memory contents. This applies to both read and write operations.

## **Memory Modes**

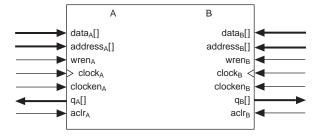

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

Figure 2-12. True Dual-Port Memory Configuration

TriMatrix memory architecture can implement pipelined RAM by registering both the input and output signals to the RAM block. All TriMatrix memory block inputs are registered providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (WREN) signal derived from the global or regional clock. In contrast, a circuit using asynchronous RAM must generate the RAM WREN signal while ensuring its data and address signals meet setup and hold time specifications relative to the WREN signal. The output registers can be bypassed. Flow-through reading is possible in the simple dual-port mode of M512 and M4K RAM blocks by clocking the read enable and read address registers on the negative clock edge and bypassing the output registers.

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The Quartus II software automatically implements larger memory by combining multiple TriMatrix memory blocks. For example, two  $256 \times 16$ -bit RAM blocks can be combined to form a  $256 \times 32$ -bit RAM block. Memory performance does not degrade for memory blocks using the maximum number of words available in one memory block. Logical memory blocks using less than the maximum number of words use physical blocks in parallel, eliminating any external control logic that would increase delays. To create a larger high-speed memory block, the Quartus II software automatically combines memory blocks with LE control logic.

# Clear Signals

When applied to input registers, the asynchronous clear signal for the TriMatrix embedded memory immediately clears the input registers. However, the output of the memory block does not show the effects until the next clock edge. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

## **Parity Bit Support**

The memory blocks support a parity bit for each byte. The parity bit, along with internal LE logic, can implement parity checking for error detection to ensure data integrity. You can also use parity-size data words to store user-specified control bits. In the M4K and M-RAM blocks, byte enables are also available for data input masking during write operations.

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–5 and 2–6 summarize the possible M4K RAM block configurations.

| Table 2-5. M4 | Table 2–5. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|

|               |                                                            | Write Port |          |          |          |          |          |             |          |

| Read Port     | 4K × 1                                                     | 2K × 2     | 1K × 4   | 512 × 8  | 256 × 16 | 128 × 32 | 512 × 9  | 256 × 18    | 128 × 36 |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | ~        | <b>✓</b> | <b>✓</b> |          |             |          |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |

| Table 2–6. M4K RAM Block Configurations (True Dual-Port) |          |                                                  |          |          |          |          |          |  |

|----------------------------------------------------------|----------|--------------------------------------------------|----------|----------|----------|----------|----------|--|

| Don't A                                                  |          |                                                  |          | Port B   |          |          |          |  |

| Port A                                                   | 4K × 1   | 4K × 1  2K × 2  1K × 4  512 × 8  256 × 16  512 × |          |          |          |          |          |  |

| 4K × 1                                                   | <b>✓</b> | <b>✓</b>                                         | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |

| 2K × 2                                                   | ✓        | <b>✓</b>                                         | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 1K × 4                                                   | ✓        | <b>✓</b>                                         | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 512 × 8                                                  | ✓        | <b>✓</b>                                         | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 256 × 16                                                 | ✓        | <b>✓</b>                                         | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 512 × 9                                                  |          |                                                  |          |          |          | <b>✓</b> | <b>✓</b> |  |

| 256 × 18                                                 |          |                                                  |          |          |          | <b>✓</b> | <b>✓</b> |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

| <b>Table 2–11. M-RAM Combined Byte Selection for</b> × <b>144 Mode</b> Notes (1), (2) |             |  |  |  |

|---------------------------------------------------------------------------------------|-------------|--|--|--|

| byteena[150]                                                                          | datain ×144 |  |  |  |

| [0] = 1                                                                               | [80]        |  |  |  |

| [1] = 1                                                                               | [179]       |  |  |  |

| [2] = 1                                                                               | [2618]      |  |  |  |

| [3] = 1                                                                               | [3527]      |  |  |  |

| [4] = 1                                                                               | [4436]      |  |  |  |

| [5] = 1                                                                               | [5345]      |  |  |  |

| [6] = 1                                                                               | [6254]      |  |  |  |

| [7] = 1                                                                               | [7163]      |  |  |  |

| [8] = 1                                                                               | [8072]      |  |  |  |

| [9] = 1                                                                               | [8981]      |  |  |  |

| [10] = 1                                                                              | [9890]      |  |  |  |

| [11] = 1                                                                              | [10799]     |  |  |  |

| [12] = 1                                                                              | [116108]    |  |  |  |

| [13] = 1                                                                              | [125117]    |  |  |  |

| [14] = 1                                                                              | [134126]    |  |  |  |

| [15] = 1                                                                              | [143135]    |  |  |  |

Notes to Tables 2-10 and 2-11:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, i.e., in  $\times$ 16,  $\times$ 32,  $\times$ 64, and  $\times$ 128 modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–19.

#### Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output block and can be used as an accumulator or as an adder/subtractor.

#### Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or subtraction using the addnsub independent control signal for each first-level adder in  $18 \times 18$ -bit mode. There are two addnsub [1..0] signals available in a DSP block for any configuration. For  $9 \times 9$ -bit mode, one addnsub [1..0] signal controls the top two one-level adders and another addnsub [1..0] signal controls the bottom two one-level adders. A high addnsub signal indicates addition, and a low signal indicates subtraction. The addnsub control signal can be unregistered or registered once or twice when feeding the adder blocks to match data path pipelines.

The signa and signb signals serve the same function as the multiplier block signa and signb signals. The only difference is that these signals can be registered up to two times. These signals are tied to the same signa and signb signals from the multiplier and must be connected to the same clocks and control signals.

#### Accumulator

When configured for accumulation, the adder/output block output feeds back to the accumulator as shown in Figure 2–34. The accum\_sload[1..0] signal synchronously loads the multiplier result to the accumulator output. This signal can be unregistered or registered once or twice. Additionally, the overflow signal indicates the accumulator has overflowed or underflowed in accumulation mode. This signal is always registered and must be externally latched in LEs if the design requires a latched overflow signal.

#### Summation

The output of the adder/subtractor/accumulator block feeds to an optional summation block. This block sums the outputs of the DSP block multipliers. In 9  $\times$  9-bit mode, there are two summation blocks providing the sums of two sets of four 9  $\times$  9-bit multipliers. In 18  $\times$  18-bit mode, there is one summation providing the sum of one set of four 18  $\times$  18-bit multipliers.

*Note to Figure 2–42:*

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input to the fast PLL can be driven by an output from another PLL, a pin-driven global or regional clock, or internallygenerated global signals.

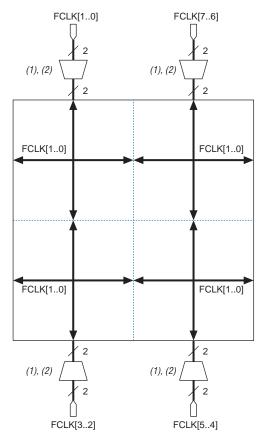

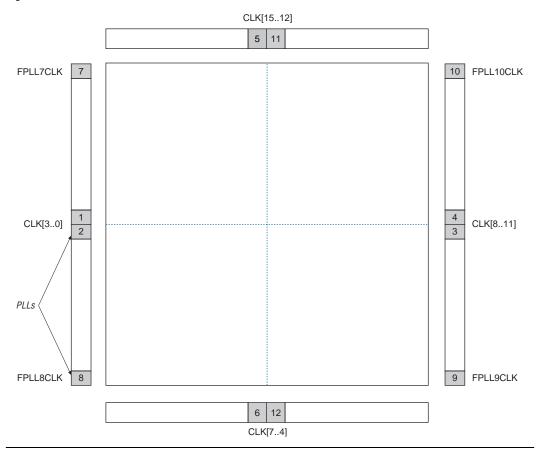

## Regional Clock Network

There are four regional clock networks within each quadrant of the Stratix device that are driven by the same dedicated CLK[15..0] input pins or from PLL outputs. From a top view of the silicon, RCLK [0..3] are in the top left quadrant, RCLK[8..11] are in the top-right quadrant, RCLK[4..7] are in the bottom-left quadrant, and RCLK[12..15] are in the bottom-right quadrant. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. RCLK cannot be driven by internal logic. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 2–43. See Figures 2–50 and 2–51 for RCLK connections from PLLs and CLK pins.

Figure 2–44. EP1S25, EP1S20 & EP1S10 Device Fast Clock Pin Connections to Fast Regional Clocks

### Notes to Figure 2-44:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

Figure 2–49 shows a top-level diagram of the Stratix device and PLL floorplan.

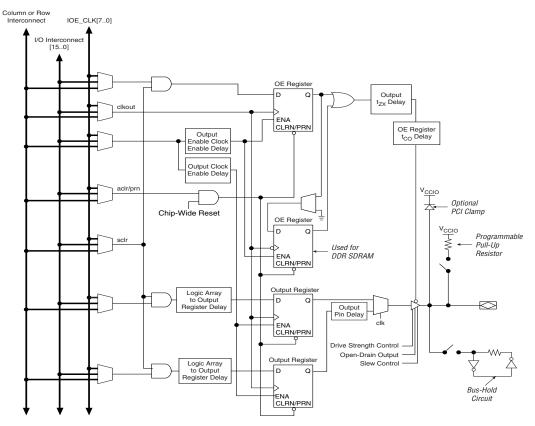

Figure 2–67. Stratix IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–67:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

| Table 2–32. I/O Support by Bank (Part 2 of 2) |                                     |                                     |                                                                 |  |  |  |  |

|-----------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left & Right Banks<br>(1, 2, 5 & 6) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |  |  |

| SSTL-3 Class II                               | ✓                                   | ✓                                   | ✓                                                               |  |  |  |  |

| AGP (1× and 2×)                               | ✓                                   |                                     | ✓                                                               |  |  |  |  |

| CTT                                           | ✓                                   | ✓                                   | ✓                                                               |  |  |  |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

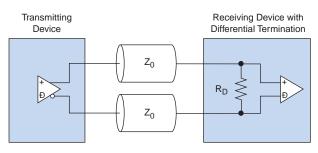

## **Differential On-Chip Termination**

Stratix devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

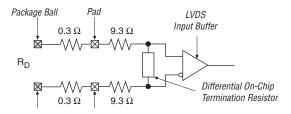

Stratix devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 2–71 shows the device with differential termination.

Figure 2-71. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 2–33 shows the Stratix device differential termination support.

| Table 2–33. Differential Termination Supported by I/O Banks                                                             |                                          |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|--|--|

| Differential Termination Support I/O Standard Support Top & Bottom Banks (3, 4, 7 & 8) Left & Right Banks (1, 2, 5 & 6) |                                          |  |  |  |  |  |  |  |

| Differential termination (1), (2)                                                                                       | Differential termination (1), (2) LVDS ✓ |  |  |  |  |  |  |  |

Notes to Table 2-33:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 2–34 shows the termination support for different pin types.

| Table 2–34. Differential Termination Support Across Pin Types |                |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |

| FCLK                                                          |                |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega \pm 20$  %.

However, there is additional resistance present between the device ball and the input of the receiver buffer, as shown in Figure 2–72. This resistance is because of package trace resistance (which can be calculated as the resistance from the package ball to the pad) and the parasitic layout metal routing resistance (which is shown between the pad and the intersection of the on-chip termination and input buffer).

Figure 2-72. Differential Resistance of LVDS Differential Pin Pair (Rp)

Table 2–35 defines the specification for internal termination resistance for commercial devices.

| Table 2–35. Differential On-Chip Termination |                                            |                     |     |     |     |      |  |  |

|----------------------------------------------|--------------------------------------------|---------------------|-----|-----|-----|------|--|--|

| Cumbal                                       | Resistance Conditions                      |                     |     |     |     |      |  |  |

| Symbol                                       | Description                                | Conditions          | Min | Тур | Max | Unit |  |  |

| R <sub>D</sub> (2)                           | Internal differential termination for LVDS | Commercial (1), (3) | 110 | 135 | 165 | W    |  |  |

|                                              |                                            | Industrial (2), (3) | 100 | 135 | 170 | W    |  |  |

Notes to Table 2-35:

- (1) Data measured over minimum conditions ( $T_j = 0 \text{ C}$ ,  $V_{\text{CCIO}} + 5\%$ ) and maximum conditions ( $T_j = 85 \text{ C}$ ,  $V_{\text{CCIO}} = -5\%$ ).

- (2) Data measured over minimum conditions ( $T_j = -40$  C,  $V_{CCIO} + 5\%$ ) and maximum conditions ( $T_j = 100$  C,  $V_{CCIO} = -5\%$ ).

- (3) LVDS data rate is supported for 840 Mbps using internal differential termination.

### MultiVolt I/O Interface

The Stratix architecture supports the MultiVolt I/O interface feature, which allows Stratix devices in all packages to interface with systems of different supply voltages.

The Stratix VCCINT pins must always be connected to a 1.5-V power supply. With a 1.5-V  $V_{CCINT}$  level, input pins are 1.5-V, 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-V, 1.8-V, 2.5-V, or 3.3-V power supply, depending on the output requirements.

| Table 4–7. 1.8-V I/O Specifications |                           |                                               |                          |                        |      |  |  |  |

|-------------------------------------|---------------------------|-----------------------------------------------|--------------------------|------------------------|------|--|--|--|

| Symbol                              | Parameter                 | Conditions                                    | Minimum                  | Maximum                | Unit |  |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                                               | 1.65                     | 1.95                   | V    |  |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                                               | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                                               | -0.3                     | $0.35 \times V_{CCIO}$ | ٧    |  |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ to } -8 \text{ mA } (10)$ | V <sub>CCIO</sub> - 0.45 |                        | ٧    |  |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 to 8 mA (10)              |                          | 0.45                   | V    |  |  |  |

| Table 4–8. 1.5-V I/O Specifications |                           |                              |                        |                         |      |  |  |

|-------------------------------------|---------------------------|------------------------------|------------------------|-------------------------|------|--|--|

| Symbol                              | Parameter                 | Conditions                   | Minimum                | Maximum                 | Unit |  |  |

| V <sub>CCIO</sub>                   | Output supply voltage     |                              | 1.4                    | 1.6                     | V    |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                              | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.3 | V    |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                              | -0.3                   | $0.35 \times V_{CCIO}$  | V    |  |  |

| V <sub>OH</sub>                     | High-level output voltage | I <sub>OH</sub> = -2 mA (10) | $0.75 \times V_{CCIO}$ |                         | V    |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 mA (10)  |                        | $0.25 \times V_{CCIO}$  | V    |  |  |

#### Notes to Tables 4–1 through 4–8:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 4–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns, or overshoot to the voltage shown in Table 4-9, based on input duty cycle for input currents less than 100 mA. The overshoot is dependent upon duty cycle of the signal. The DC case is equivalent to 100% duty cycle.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.5 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

- (9) Pin pull-up resistance values will lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Drive strength is programmable according to the values shown in the *Stratix Architecture* chapter of the *Stratix Device Handbook, Volume 1*.

| Table 4–9. Overshoot Input Voltage with Respect to Duty Cycle (Part 1 of 2) |     |  |  |  |

|-----------------------------------------------------------------------------|-----|--|--|--|

| Vin (V) Maximum Duty Cycle (%)                                              |     |  |  |  |

| 4.0                                                                         | 100 |  |  |  |

| 4.1                                                                         | 90  |  |  |  |

| 4.2                                                                         | 50  |  |  |  |

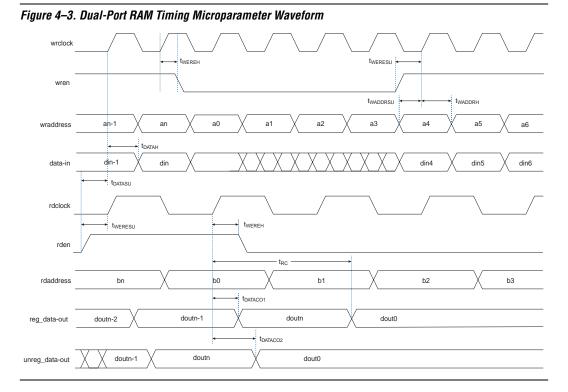

Figure 4–3 shows the TriMatrix memory waveforms for the M512, M4K, and M-RAM timing parameters shown in Tables 4–40 through 4–42.

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 4–44 through 4–50 show the internal timing microparameters for LEs, IOEs, TriMatrix memory structures, DSP blocks, and MultiTrack interconnects.

| Table 4–43. Routing Delay Internal Timing Microparameter Descriptions (Part 1 of 2) |                                                                                    |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                                                              | Parameter                                                                          |  |  |  |  |

| t <sub>R4</sub>                                                                     | Delay for an R4 line with average loading; covers a distance of four LAB columns.  |  |  |  |  |

| t <sub>R8</sub>                                                                     | Delay for an R8 line with average loading; covers a distance of eight LAB columns. |  |  |  |  |

| t <sub>R24</sub>                                                                    | Delay for an R24 line with average loading; covers a distance of 24 LAB columns.   |  |  |  |  |

## Stratix External I/O Timing

These timing parameters are for both column IOE and row IOE pins. In EP1S30 devices and above, you can decrease the  $t_{SU}$  time by using the FPLLCLK, but may get positive hold time in EP1S60 and EP1S80 devices. You should use the Quartus II software to verify the external devices for any pin.

Tables 4–55 through 4–60 show the external timing parameters on column and row pins for EP1S10 devices.

| Table 4–55. EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks Note (1) |                |       |                |       |                |       |                |     |      |

|---------------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|-----|------|

| Parameter                                                                                         | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |     |      |

|                                                                                                   | Min            | Max   | Min            | Max   | Min            | Max   | Min            | Max | Unit |

| t <sub>INSU</sub>                                                                                 | 2.238          |       | 2.325          |       | 2.668          |       | NA             |     | ns   |

| t <sub>INH</sub>                                                                                  | 0.000          |       | 0.000          |       | 0.000          |       | NA             |     | ns   |

| t <sub>OUTCO</sub>                                                                                | 2.240          | 4.549 | 2.240          | 4.836 | 2.240          | 5.218 | NA             | NA  | ns   |

| t <sub>XZ</sub>                                                                                   | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |

| t <sub>ZX</sub>                                                                                   | 2.180          | 4.423 | 2.180          | 4.704 | 2.180          | 5.094 | NA             | NA  | ns   |

| Table 4–56. EP1S10 External I/O Timing on Column Pins Using Regional Clock Networks Note (1) |                |       |                |       |                |       |                |    |      |

|----------------------------------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|----------------|----|------|

| Parameter                                                                                    | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | -8 Speed Grade |    |      |

|                                                                                              | Min            | Max   | Min            | Max   | Min            | Max   |                |    | Unit |

| t <sub>INSU</sub>                                                                            | 1.992          |       | 2.054          |       | 2.359          |       | NA             |    | ns   |

| t <sub>INH</sub>                                                                             | 0.000          |       | 0.000          |       | 0.000          |       | NA             |    | ns   |

| t <sub>оитсо</sub>                                                                           | 2.395          | 4.795 | 2.395          | 5.107 | 2.395          | 5.527 | NA             | NA | ns   |

| t <sub>XZ</sub>                                                                              | 2.335          | 4.669 | 2.335          | 4.975 | 2.335          | 5.403 | NA             | NA | ns   |

| t <sub>ZX</sub>                                                                              | 2.335          | 4.669 | 2.335          | 4.975 | 2.335          | 5.403 | NA             | NA | ns   |

| t <sub>INSUPLL</sub>                                                                         | 0.975          |       | 0.985          |       | 1.097          |       | NA             |    | ns   |

| t <sub>INHPLL</sub>                                                                          | 0.000          |       | 0.000          |       | 0.000          |       | NA             | NA | ns   |

| t <sub>OUTCOPLL</sub>                                                                        | 1.262          | 2.636 | 1.262          | 2.680 | 1.262          | 2.769 | NA             | NA | ns   |

| t <sub>XZPLL</sub>                                                                           | 1.202          | 2.510 | 1.202          | 2.548 | 1.202          | 2.645 | NA             | NA | ns   |

| t <sub>ZXPLL</sub>                                                                           | 1.202          | 2.510 | 1.202          | 2.548 | 1.202          | 2.645 | NA             | NA | ns   |

| Fast Regional Clock External I/O Timing            | I                                                           |

|----------------------------------------------------|-------------------------------------------------------------|

| Parameters 4–49                                    | I/O                                                         |

| Global Clock External I/O Timing                   | Standards                                                   |

| Parameters 4–50 Regional Clock External I/O Timing | 1.5-V 4-14, 4-15                                            |

| Parameters 4–50                                    | I/O Specifications 4–4                                      |

| EP1S60 Devices                                     | 1.8-V                                                       |

| Column Pin                                         | I/O Specifications 4–4                                      |

| Fast Regional Clock External I/O Timing            | 2.5-V                                                       |

| Parameters 4–51                                    | I/O Specifications 4–3                                      |

| Global Clock External I/O Timing                   | 3.3-V 4–13                                                  |

| Parameters 4–52                                    | LVDS I/O Specifications 4–6                                 |

| Regional Clock External I/O Timing                 | PCI Specifications 4–9                                      |

| Parameters 4–51                                    | PCML Specifications 4–8                                     |

| M-RAM                                              | Advanced I/O Standard Support 2–122                         |

| Interface Locations 2–38                           | Column I/O Block Connection to the                          |

| Row Pin                                            | Interconnect 2–107                                          |

| Fast Regional Clock External I/O Timing            | Column Pin                                                  |

| Parameters 4–52                                    | Input Delay Adders 4–66                                     |

| Global Clock External I/O Timing                   | Control Signal Selection per IOE 2–109                      |

| Parameters 4–53                                    | CTT I/O Specifications 4–16                                 |

| Regional Clock External I/O Timing                 | Differential LVDS Input On-Chip                             |

| Parameters 4–53                                    | Termination 2–128                                           |

| EP1S80 Devices                                     | External I/O Delay Parameters 4–66                          |

| Column Pin                                         | GTL+ I/O Specifications 4–10<br>High-Speed Differential I/O |

| Fast Regional Clock External I/O Timing            | Support 2–130                                               |

| Parameters 4–54                                    | HyperTransport Technology                                   |

| Global Clock External I/O Timing                   | Specifications 4–9                                          |

| Parameters 4–55                                    | I/O Banks 2–125                                             |

| Regional Clock External I/O Timing                 | I/O Structure 2–104                                         |

| Parameters 4–54                                    | I/O Support by Bank 2–126                                   |

| Global Clock External I/O Timing                   | IOE Structure 2–105                                         |

| Parameters 4–56                                    | LVCMOS Specifications 4–3                                   |

| Row Pin                                            | LVDS Performance on Fast PLL                                |

| Fast Regional Clock External I/O Timing            | Input 2–103                                                 |

| Parameters 4–55                                    | LVPECL Specifications 4–8                                   |

| Regional Clock External I/O Timing                 | LVTTL Specifications 4–3                                    |

| Parameters 4–56                                    | MultiVolt I/O Interface 2–129                               |

|                                                    | MultiVolt I/O Support 2–130                                 |

| H                                                  | Output Delay Adders for Fast Slew Rate                      |

| HSTL                                               | on Column Pins 4–68                                         |

| Class I Specifications 4–14, 4–15                  | Output Delay Adders for Fast Slew Rate                      |

| Class II Specifications 4–14, 4–15                 | on Row Pins 4–69                                            |

| Ciass II Specifications 4-14, 4-15                 | Output Delay Adders for Slow Slew Rate                      |

|                                                    | on Column Pins 4–70                                         |

|                                                    | Package Options & I/O Pin Counts 1–4                        |

|                                                    | Receiver Input Waveforms for Differential                   |

Index-4 Altera Corporation