# E·XFL

## Altera - EP1S80F1508I7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | -                                                           |

| Number of Logic Elements/Cells | -                                                           |

| Total RAM Bits                 | -                                                           |

| Number of I/O                  | -                                                           |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA (30x30)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep1s80f1508i7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file.                                             |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75:<br>High-Speed Board Designs.                                                                                                                                                                                                     |

| Italic type                                 | Internal timing parameters and variables are shown in italic type.<br>Examples: $t_{PlA}$ , $n + 1$ .                                                                                                                                                                                                                   |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file name=""></file></i> , <i><project name="">.pof</project></i> file.                                                                                                                                                   |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples:<br>Delete key, the Options menu.                                                                                                                                                                                                         |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| ••                                          | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| $\checkmark$                                | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| Ţ                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | January 2005, 3.2    | Updated rise and fall input values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | September 2004, v3.1 | <ul> <li>Updated Note 3 in Table 4–8 on page 4–4.</li> <li>Updated Table 4–10 on page 4–6.</li> <li>Updated Table 4–20 on page 4–12 through Table 4–23 on page 4–13. Added rows V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub> to each table.</li> <li>Updated Table 4–26 on page 4–14 through Table 4–29 on page 4–15.</li> <li>Updated Table 4–31 on page 4–16.</li> <li>Updated Table 4–36 on page 4–20.</li> <li>Added signals t<sub>OUTCO</sub>, T<sub>XZ</sub>, and T<sub>ZX</sub> to Figure 4–4 on page 4–33.</li> <li>Added rows t<sub>M512CLKENSU</sub> and t<sub>M512CLKENH</sub> to Table 4–40 on page 4–24.</li> <li>Updated Note 2 in Table 4–54 on page 4–35.</li> <li>Added rows t<sub>MAACLKENSU</sub> and t<sub>MRAMCLKENH</sub> to Table 4–42 on page 4–25.</li> <li>Updated Table 4–46 on page 4–29.</li> <li>Updated Table 4–47 on page 4–29.</li> </ul> |

## Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums: data1 + data2 + carry-in0 or data1 + data2 + carry-in1. The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out 0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to TriMatrix<sup>™</sup> memory and DSP blocks. A carry chain can continue as far as a full column.

asynchronous load, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix devices provide a chipwide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Stratix architecture, connections between LEs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive™ technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks.

- **R**4 interconnects traversing four blocks to the right or left.

- R8 interconnects traversing eight blocks to the right or left.

- R24 row interconnects for high-speed access across the length of the device.

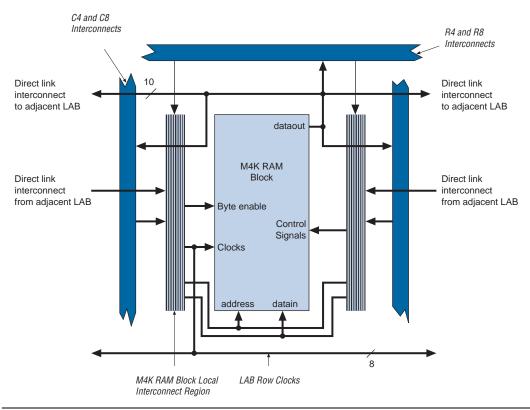

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. Only one side of a M-RAM block interfaces with direct link and row interconnects. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast

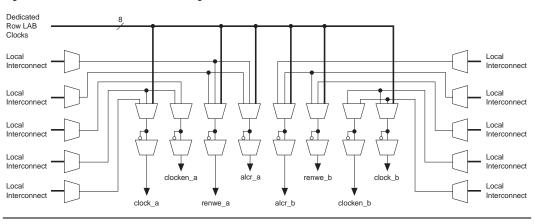

Figure 2–17. M4K RAM Block Control Signals

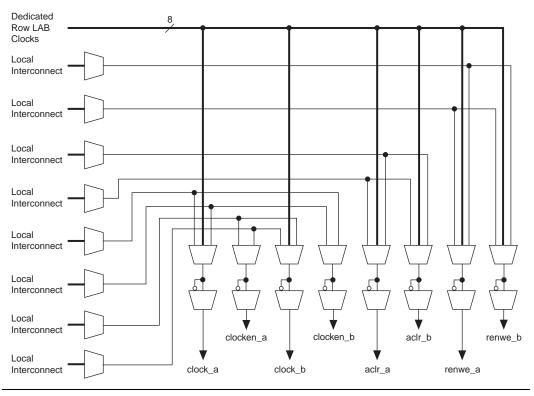

Figure 2–18. M4K RAM Block LAB Row Interface

Figure 2–19. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 2–20 shows an example floorplan for the EP1S60 device and the location of the M-RAM interfaces.

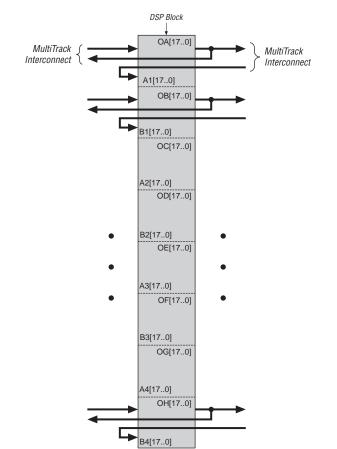

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an  $18 \times 18$ -bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB through direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 2–40 and 2–41 show the DSP block interfaces to LAB rows.

#### Figure 2–40. DSP Block Interconnect Interface

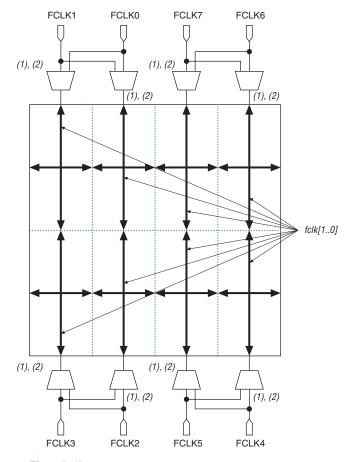

#### Figure 2–45. EP1S30 Device Fast Regional Clock Pin Connections to Fast Regional Clocks

#### Notes to Figure 2-45:

- (1) This is a set of two multiplexers.

- (2) In addition to the FCLK pin inputs, there is also an input from the I/O interconnect.

#### Combined Resources

Within each region, there are 22 distinct dedicated clocking resources consisting of 16 global clock lines, four regional clock lines, and two fast regional clock lines. Multiplexers are used with these clocks to form eight bit busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select two of the eight row clocks to feed the LE registers within the LAB. See Figure 2–46.

bandwidth is tuned by varying the charge pump current, loop filter resistor value, high frequency capacitor value, and *m* counter value. You can manually adjust these values if desired. Bandwidth is programmable from 200 kHz to 1.5 MHz.

## External Clock Outputs

Enhanced PLLs 5 and 6 each support up to eight single-ended clock outputs (or four differential pairs). Differential SSTL and HSTL outputs are implemented using 2 single-ended output buffers which are programmed to have opposite polarity. In Quartus II software, simply assign the appropriate differential I/O standard and the software will implement the inversion. See Figure 2–55.

### External Clock Inputs

Each fast PLL supports single-ended or differential inputs for source synchronous transmitters or for general-purpose use. Source-synchronous receivers support differential clock inputs. The fast PLL inputs are fed by CLK [0..3], CLK [8..11], and FPLL [7..10] CLK pins, as shown in Figure 2–50 on page 2–85.

Table 2–22 shows the I/O standards supported by fast PLL input pins.

| Table 2–22. Fast PLL Port I/O Standards (Part 1 of 2) |       |              |  |  |  |  |  |

|-------------------------------------------------------|-------|--------------|--|--|--|--|--|

| L/O Chandard                                          | li    | nput         |  |  |  |  |  |

| I/O Standard                                          | INCLK | PLLENABLE    |  |  |  |  |  |

| LVTTL                                                 | ~     | $\checkmark$ |  |  |  |  |  |

| LVCMOS                                                | ~     | $\checkmark$ |  |  |  |  |  |

| 2.5 V                                                 | ~     |              |  |  |  |  |  |

| 1.8 V                                                 | ~     |              |  |  |  |  |  |

| 1.5 V                                                 | ~     |              |  |  |  |  |  |

| 3.3-V PCI                                             |       |              |  |  |  |  |  |

| 3.3-V PCI-X 1.0                                       |       |              |  |  |  |  |  |

| LVPECL                                                | ~     |              |  |  |  |  |  |

| 3.3-V PCML                                            | ~     |              |  |  |  |  |  |

| LVDS                                                  | ~     |              |  |  |  |  |  |

| HyperTransport technology                             | ~     |              |  |  |  |  |  |

| Differential HSTL                                     | ~     |              |  |  |  |  |  |

| Differential SSTL                                     |       |              |  |  |  |  |  |

| 3.3-V GTL                                             |       |              |  |  |  |  |  |

| 3.3-V GTL+                                            | ~     |              |  |  |  |  |  |

| 1.5-V HSTL Class I                                    | ~     |              |  |  |  |  |  |

| 1.5-V HSTL Class II                                   |       |              |  |  |  |  |  |

| 1.8-V HSTL Class I                                    | ~     |              |  |  |  |  |  |

| 1.8-V HSTL Class II                                   |       |              |  |  |  |  |  |

| SSTL-18 Class I                                       | ~     |              |  |  |  |  |  |

| SSTL-18 Class II                                      |       |              |  |  |  |  |  |

| SSTL-2 Class I                                        | ~     |              |  |  |  |  |  |

| Table 2- | Table 2–37. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2) Note (1) |                 |          |                                              |                  |       |       |       |  |  |

|----------|-----------------------------------------------------------------------------------------|-----------------|----------|----------------------------------------------|------------------|-------|-------|-------|--|--|

|          |                                                                                         | Transmitter/    | Total    | Total<br>nannels (Maximum<br>Speed<br>(Mbps) | Center Fast PLLs |       |       |       |  |  |

| Device   | Package                                                                                 | Receiver        | Channels |                                              | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |

| EP1S25   | 672-pin FineLine BGA                                                                    | Transmitter (2) | 56       | 624 (4)                                      | 14               | 14    | 14    | 14    |  |  |

|          | 672-pin BGA                                                                             |                 |          | 624 <i>(3)</i>                               | 28               | 28    | 28    | 28    |  |  |

|          |                                                                                         | Receiver        | 58       | 624 (4)                                      | 14               | 15    | 15    | 14    |  |  |

|          |                                                                                         |                 |          | 624 <i>(3)</i>                               | 29               | 29    | 29    | 29    |  |  |

|          | 780-pin FineLine BGA                                                                    | Transmitter (2) | 70       | 840 (4)                                      | 18               | 17    | 17    | 18    |  |  |

|          |                                                                                         |                 |          | 840 <i>(3)</i>                               | 35               | 35    | 35    | 35    |  |  |

|          |                                                                                         | Receiver        | 66       | 840 (4)                                      | 17               | 16    | 16    | 17    |  |  |

|          |                                                                                         |                 |          | 840 (3)                                      | 33               | 33    | 33    | 33    |  |  |

|          | 1,020-pin FineLine                                                                      | Transmitter (2) | 78       | 840 (4)                                      | 19               | 20    | 20    | 19    |  |  |

|          | BGA                                                                                     |                 |          | 840 <i>(3)</i>                               | 39               | 39    | 39    | 39    |  |  |

|          |                                                                                         | Receiver        | 78       | 840 (4)                                      | 19               | 20    | 20    | 19    |  |  |

|          |                                                                                         |                 |          | 840 (3)                                      | 39               | 39    | 39    | 39    |  |  |

#### Notes to Table 2–37:

- (1) The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at 840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

- (2) The number of channels listed includes the transmitter clock output (tx\_outclock) channel. If the design requires a DDR clock, it can use an extra data channel.

- (3) These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-bank channels simultaneously if, for example, PLL\_1 is clocking all receiver channels and PLL\_2 is clocking all transmitter channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank receiver channels or two adjacent PLLs simultaneously clocking transmitter channels. Cross-bank allows for all receiver channels on one side of the device to be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

(4) These values show the channels available for each PLL without crossing another bank.

When you span two I/O banks using cross-bank support, you can route only two load enable signals total between the PLLs. When you enable rx\_data\_align, you use both rxloadena and txloadena of a PLL. That leaves no loadena for the second PLL.

The transmitter external clock output is transmitted on a data channel. The txclk pin for each bank is located in between data transmitter pins. For ×1 clocks (e.g., 622 Mbps, 622 MHz), the high-speed PLL clock bypasses the SERDES to drive the output pins. For half-rate clocks (e.g., 622 Mbps, 311 MHz) or any other even-numbered factor such as 1/4, 1/7, 1/8, or 1/10, the SERDES automatically generates the clock in the Quartus II software.

For systems that require more than four or eight high-speed differential I/O clock domains, a SERDES bypass implementation is possible using IOEs.

# **Byte Alignment**

For high-speed source synchronous interfaces such as POS-PHY 4, XSBI, RapidIO, and HyperTransport technology, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for usercontrolled byte boundary shifting. This simplifies designs while saving LE resources. An input signal to each fast PLL can stall deserializer parallel data outputs by one bit period. You can use an LE-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

# Power Sequencing & Hot Socketing

Because Stratix devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Although you can power up or down the VCCIO and VCCINT power supplies in any sequence, you should not power down any I/O banks that contain configuration pins while leaving other I/O banks powered on. For power up and power down, all supplies (VCCINT and all VCCIO power planes) must be powered up and down within 100 ms of each other. This prevents I/O pins from driving out.

Signals can be driven into Stratix devices before and during power up without damaging the device. In addition, Stratix devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix devices operate as specified by the user. For more information, see *Hot Socketing* in the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter in the *Stratix Device Handbook, Volume 2.*

| Symbol              | Parameter                                                                         | Conditions                                                            | Minimum | Typical | Maximum | Unit |

|---------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------|---------|---------|------|

| V <sub>ICM</sub>    | Input common mode voltage (6)                                                     | LVDS<br>0.3 V ≤V <sub>ID</sub> ≤1.0 V<br><i>W</i> = 1 through 10      | 100     |         | 1,100   | mV   |

|                     |                                                                                   | LVDS<br>$0.3 V \leq V_{ID} \leq 1.0 V$<br>W = 1 through 10            | 1,600   |         | 1,800   | mV   |

|                     |                                                                                   | LVDS<br>0.2 V $\leq$ V <sub>ID</sub> $\leq$ 1.0 V<br>W = 1            | 1,100   |         | 1,600   | mV   |

|                     |                                                                                   | LVDS<br>0.1 V $\leq$ V <sub>ID</sub> $\leq$ 1.0 V<br>W = 2 through 10 | 1,100   |         | 1,600   | mV   |

| V <sub>OD</sub> (1) | Output differential voltage (single-ended)                                        | R <sub>L</sub> = 100 Ω                                                | 250     | 375     | 550     | mV   |

| $\Delta V_{OD}$     | Change in V <sub>OD</sub> between high and low                                    | R <sub>L</sub> = 100 Ω                                                |         |         | 50      | mV   |

| V <sub>OCM</sub>    | Output common mode voltage                                                        | R <sub>L</sub> = 100 Ω                                                | 1,125   | 1,200   | 1,375   | mV   |

| $\Delta V_{OCM}$    | Change in V <sub>OCM</sub> between high and low                                   | R <sub>L</sub> = 100 Ω                                                |         |         | 50      | mV   |

| RL                  | Receiver differential input<br>discrete resistor (external<br>to Stratix devices) |                                                                       | 90      | 100     | 110     | Ω    |

| Table 4–57. L         | Table 4–57. EP1S10 External I/O Timing on Column Pins Using Global Clock Networks Note (1) |         |         |         |                |       |                |     |      |  |

|-----------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|----------------|-------|----------------|-----|------|--|

| Deremeter             | -5 Spee                                                                                    | d Grade | -6 Spee | d Grade | -7 Speed Grade |       | -8 Speed Grade |     |      |  |

| Parameter             | Min                                                                                        | Max     | Min     | Max     | Min            | Max   | Min            | Max | Unit |  |

| t <sub>INSU</sub>     | 1.647                                                                                      |         | 1.692   |         | 1.940          |       | NA             |     | ns   |  |

| t <sub>INH</sub>      | 0.000                                                                                      |         | 0.000   |         | 0.000          |       | NA             |     | ns   |  |

| t <sub>оитсо</sub>    | 2.619                                                                                      | 5.184   | 2.619   | 5.515   | 2.619          | 5.999 | NA             | NA  | ns   |  |

| t <sub>xz</sub>       | 2.559                                                                                      | 5.058   | 2.559   | 5.383   | 2.559          | 5.875 | NA             | NA  | ns   |  |

| t <sub>ZX</sub>       | 2.559                                                                                      | 5.058   | 2.559   | 5.383   | 2.559          | 5.875 | NA             | NA  | ns   |  |

| t <sub>INSUPLL</sub>  | 1.239                                                                                      |         | 1.229   |         | 1.374          |       | NA             |     | ns   |  |

| t <sub>INHPLL</sub>   | 0.000                                                                                      |         | 0.000   |         | 0.000          |       | NA             |     | ns   |  |

| t <sub>OUTCOPLL</sub> | 1.109                                                                                      | 2.372   | 1.109   | 2.436   | 1.109          | 2.492 | NA             | NA  | ns   |  |

| t <sub>XZPLL</sub>    | 1.049                                                                                      | 2.246   | 1.049   | 2.304   | 1.049          | 2.368 | NA             | NA  | ns   |  |

| t <sub>ZXPLL</sub>    | 1.049                                                                                      | 2.246   | 1.049   | 2.304   | 1.049          | 2.368 | NA             | NA  | ns   |  |

| Table 4–58. EP1S10 External I/O Timing on Row Pin Using Fast Regional Clock Network Note (1) |                  |       |         |                |       |                |     |                |      |

|----------------------------------------------------------------------------------------------|------------------|-------|---------|----------------|-------|----------------|-----|----------------|------|

| Parameter                                                                                    | -5 Speed Grade - |       | -6 Spee | -6 Speed Grade |       | -7 Speed Grade |     | -8 Speed Grade |      |

|                                                                                              | Min              | Max   | Min     | Max            | Min   | Max            | Min | Max            | Unit |

| t <sub>INSU</sub>                                                                            | 2.212            |       | 2.403   |                | 2.759 |                | NA  |                | ns   |

| t <sub>INH</sub>                                                                             | 0.000            |       | 0.000   |                | 0.000 |                | NA  |                | ns   |

| t <sub>OUTCO</sub>                                                                           | 2.391            | 4.838 | 2.391   | 5.159          | 2.391 | 5.569          | NA  | NA             | ns   |

| t <sub>xz</sub>                                                                              | 2.418            | 4.892 | 2.418   | 5.215          | 2.418 | 5.637          | NA  | NA             | ns   |

| t <sub>ZX</sub>                                                                              | 2.418            | 4.892 | 2.418   | 5.215          | 2.418 | 5.637          | NA  | NA             | ns   |

# **Maximum Input & Output Clock Rates**

Tables 4–114 through 4–119 show the maximum input clock rate for column and row pins in Stratix devices.

| Table 4–114. Stratix Maximum Input Clock Rate for CLK[74] & CLK[1512]         Pins in Flip-Chip Packages (Part 1 of 2) |                   |                   |                   |                   |      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|--|--|--|

| I/O Standard                                                                                                           | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |  |

| LVTTL                                                                                                                  | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 2.5 V                                                                                                                  | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 1.8 V                                                                                                                  | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 1.5 V                                                                                                                  | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| LVCMOS                                                                                                                 | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| GTL                                                                                                                    | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| GTL+                                                                                                                   | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| SSTL-3 Class I                                                                                                         | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-3 Class II                                                                                                        | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-2 Class I                                                                                                         | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-2 Class II                                                                                                        | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-18 Class I                                                                                                        | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| SSTL-18 Class II                                                                                                       | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.5-V HSTL Class I                                                                                                     | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.5-V HSTL Class II                                                                                                    | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.8-V HSTL Class I                                                                                                     | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 1.8-V HSTL Class II                                                                                                    | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| 3.3-V PCI                                                                                                              | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| 3.3-V PCI-X 1.0                                                                                                        | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| Compact PCI                                                                                                            | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| AGP 1×                                                                                                                 | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| AGP 2×                                                                                                                 | 422               | 422               | 390               | 390               | MHz  |  |  |  |

| CTT                                                                                                                    | 300               | 250               | 200               | 200               | MHz  |  |  |  |

| Differential 1.5-V HSTL<br>C1                                                                                          | 400               | 350               | 300               | 300               | MHz  |  |  |  |

| LVPECL (1)                                                                                                             | 645               | 645               | 622               | 622               | MHz  |  |  |  |

| PCML (1)                                                                                                               | 300               | 275               | 275               | 275               | MHz  |  |  |  |

| I/O Standard                     | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|----------------------------------|-------------------|-------------------|-------------------|------|

| GTL+                             | 250               | 200               | 200               | MHz  |

| SSTL-3 Class I                   | 300               | 250               | 250               | MHz  |

| SSTL-3 Class II                  | 300               | 250               | 250               | MHz  |

| SSTL-2 Class I                   | 300               | 250               | 250               | MHz  |

| SSTL-2 Class II                  | 300               | 250               | 250               | MHz  |

| SSTL-18 Class I                  | 300               | 250               | 250               | MHz  |

| SSTL-18 Class II                 | 300               | 250               | 250               | MHz  |

| 1.5-V HSTL Class I               | 300               | 180               | 180               | MHz  |

| 1.5-V HSTL Class II              | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class I               | 300               | 180               | 180               | MHz  |

| 1.8-V HSTL Class II              | 300               | 180               | 180               | MHz  |

| 3.3-V PCI                        | 422               | 390               | 390               | MHz  |

| 3.3-V PCI-X 1.0                  | 422               | 390               | 390               | MHz  |

| Compact PCI                      | 422               | 390               | 390               | MHz  |

| AGP 1×                           | 422               | 390               | 390               | MHz  |

| AGP 2×                           | 422               | 390               | 390               | MHz  |

| CTT                              | 250               | 180               | 180               | MHz  |

| Differential 1.5-V HSTL<br>C1    | 300               | 180               | 180               | MHz  |

| LVPECL (1)                       | 422               | 400               | 400               | MHz  |

| PCML (1)                         | 215               | 200               | 200               | MHz  |

| LVDS (1)                         | 422               | 400               | 400               | MHz  |

| HyperTransport<br>technology (1) | 422               | 400               | 400               | MHz  |

Table 4–117. Stratix Maximum Input Clock Rate for CLK[7..4] & CLK[15..12]

Pins in Wire-Bond Packages (Part 2 of 2)

Table 4–118. Stratix Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins &

FPLL[10..7]CLK Pins in Wire-Bond Packages (Part 1 of 2)

| I/O Standard | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |

|--------------|-------------------|-------------------|-------------------|------|

| LVTTL        | 422               | 390               | 390               | MHz  |

| 2.5 V        | 422               | 390               | 390               | MHz  |

| 1.8 V        | 422               | 390               | 390               | MHz  |

| 1.5 V        | 422               | 390               | 390               | MHz  |

| in Flip-Chip Packages (Part 2 of 2) |                   |                   |                   |                   |      |  |  |  |  |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|------|--|--|--|--|

| I/O Standard                        | -5 Speed<br>Grade | -6 Speed<br>Grade | -7 Speed<br>Grade | -8 Speed<br>Grade | Unit |  |  |  |  |

| SSTL-2 Class II (3)                 | 200               | 200               | 167               | 167               | MHz  |  |  |  |  |

| SSTL-2 Class II (4)                 | 200               | 200               | 167               | 167               | MHz  |  |  |  |  |

| SSTL-2 Class II (5)                 | 150               | 134               | 134               | 134               | MHz  |  |  |  |  |

| SSTL-18 Class I                     | 150               | 133               | 133               | 133               | MHz  |  |  |  |  |

| SSTL-18 Class II                    | 150               | 133               | 133               | 133               | MHz  |  |  |  |  |

| 1.5-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |  |  |  |  |

| 1.5-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |  |  |  |  |

| 1.8-V HSTL Class I                  | 250               | 225               | 200               | 200               | MHz  |  |  |  |  |

| 1.8-V HSTL Class II                 | 225               | 200               | 200               | 200               | MHz  |  |  |  |  |

| 3.3-V PCI                           | 350               | 300               | 250               | 250               | MHz  |  |  |  |  |

| 3.3-V PCI-X 1.0                     | 350               | 300               | 250               | 250               | MHz  |  |  |  |  |

| Compact PCI                         | 350               | 300               | 250               | 250               | MHz  |  |  |  |  |

| AGP 1×                              | 350               | 300               | 250               | 250               | MHz  |  |  |  |  |

| AGP 2×                              | 350               | 300               | 250               | 250               | MHz  |  |  |  |  |

| CTT                                 | 200               | 200               | 200               | 200               | MHz  |  |  |  |  |

| Differential 1.5-V HSTL<br>C1       | 225               | 200               | 200               | 200               | MHz  |  |  |  |  |

| Differential 1.8-V HSTL<br>Class I  | 250               | 225               | 200               | 200               | MHz  |  |  |  |  |

| Differential 1.8-V HSTL<br>Class II | 225               | 200               | 200               | 200               | MHz  |  |  |  |  |

| Differential SSTL-2 (6)             | 200               | 200               | 167               | 167               | MHz  |  |  |  |  |

| LVPECL (2)                          | 500               | 500               | 500               | 500               | MHz  |  |  |  |  |

| PCML (2)                            | 350               | 350               | 350               | 350               | MHz  |  |  |  |  |

| LVDS (2)                            | 500               | 500               | 500               | 500               | MHz  |  |  |  |  |

| HyperTransport<br>technology (2)    | 350               | 350               | 350               | 350               | MHz  |  |  |  |  |

Table A 190 Strativ Maxin Autnut Clock Data for DLLE 6 11 101 Div

Global & Hierarchical Clocking 2-73 Global & Regional Clock Connections from Side Pins & Fast PLL Outputs 2-85 from Top Clock Pins & Enhanced PLL Outputs 2-86 Global Clock External I/O Timing Parameters 4-35 Global Clock Network 2–74 Global Clocking 2-75 Independent Clock Mode 2-44 Input/Output Clock Mode 2 - 46Simple Dual-Port Mode 2–48 True Dual-Port Mode 2-47 Maximum Input & Output Clock Rates 4–76 Maximum Input Clock Rate for CLK (0, 2, 9, 11) Pins in Flip-Chip Packages 4–77 Wire-Bond Packages 4-79 (1, 3, 8, 10) Pins in Flip-Chip Packages 4–78 Wire-Bond Packages 4-80 (7..4) & CLK(15..12) Pins in Flip-Chip Packages 4–76 Wire-Bond Packages 4–78 Maximum Output Clock Rate for PLL (1, 2, 3, 4) Pins in Flip-Chip Packages 4–83 Wire-Bond Packages 4-85 (5, 6, 11, 12) Pins in Flip-Chip

Packages 4-81 Wire-Bond Packages 4–84 Phase & Delay Shifting 2–96 Phase Delay 2-96 PLL Clock Networks 2-73 Read/Write Clock Mode 2 - 49in Simple Dual-Port Mode 2-50 Regional Clock 2–75 External I/O Timing Parameters 4–34 Regional Clock Bus 2–79 Regional Clock Network 2–75 Spread-Spectrum Clocking 2-98 Configuration 3–5 32-Bit IDCODE 3-3 and Testing 3-1 Data Sources for Configuration 3-7 Local Update Mode 3–12 Local Update Transition Diagram 3–12 Operating Modes 3-5 Partial Reconfiguration 3–7 Remote Update 3–8 Remote Update Transition Diagram 3–11 Schemes 3-7 SignalTap II Embedded Logic Analyzer 3–5 Stratix FPGAs with JRunner 3-7 Control Signals 2–104

# D

DC Switching Absolute Maximum Ratings 4–1 Bus Hold Parameters 4–16 Capacitance 4–17 DC & Switching Characteristics 4–1 External Timing Parameters 4–33 Operating Conditions 4–1 Performance 4–20 Power Consumption 4–17 Recommended Operating Conditions 4–1 DDR Double-Data Rate I/O Pins 2–111 Device Features EP1S10, EP1S20, EP1S25, EP1S30, 1–3 EP1S40, EP1S60, EP1S80, 1–3