Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-2                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 100MHz                                                                            |

| Connectivity               | EBI/EMI, SCI, SmartCard                                                           |

| Peripherals                | POR, WDT                                                                          |

| Number of I/O              | 8                                                                                 |

| Program Memory Size        | ·                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | •                                                                                 |

| RAM Size                   | •                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.15V ~ 3.6V                                                                      |

| Data Converters            | ·                                                                                 |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-LQFP                                                                          |

| Supplier Device Package    | 144-LQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417708rf100av |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.2       UBC Register Functions       126         7.2.1       Break Address Register A (BARA)       126         7.2.2       Break Address Register B (BARB)       126         7.2.3       Break ASID Register B (BASRA)       127         7.2.4       Break ASID Register B (BASRB)       127         7.2.5       Break Address Mask Register A (BAMRA)       127         7.2.6       Break Address Mask Register A (BAMRA)       128         7.2.7       Break Address Mask Register B (BARB)       128         7.2.8       Break Address Mask Register B (BBRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Register B (BDRB)       131         7.2.11       Break Outrol Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.5       Instruction Fetch Cycle Break       135         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         8.1       Overview       141         8.1.1       Power-Down Modes       141         8                                                          |       | 7.1.4                      | Break Conditions and Register Settings | 125 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|----------------------------------------|-----|--|--|

| 7.2.2       Break AGD Register B (BARB)       126         7.2.3       Break ASID Register A (BASRA)       127         7.2.4       Break ASID Register B (BASRB)       127         7.2.5       Break Address Mask Register A (BAMRA)       127         7.2.6       Break Address Mask Register B (BAMRB)       128         7.2.7       Break Address Mask Register B (BARB)       128         7.2.7       Break Bus Cycle Register A (BBRA)       128         7.2.8       Break Bus Cycle Register B (BBRB)       130         7.2.10       Break Data Mask Register B (BDMRB)       131         7.2.11       Break Operation Flow       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       136         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       141         8.1       Overview       141         8.1.1       Proor. Down Modes       141         8.1.1       Proor. Down Modes       141         8.1.1       Proor. Down Modes       141         8.1.3 <td>7.2</td> <td colspan="5">UBC Register Functions 126</td> | 7.2   | UBC Register Functions 126 |                                        |     |  |  |

| 7.2.3       Break ASID Register A (BASRA)       127         7.2.4       Break ASID Register B (BASRB)       127         7.2.5       Break Address Mask Register A (BAMRA)       127         7.2.6       Break Address Mask Register A (BBAMRB)       128         7.2.7       Break Address Mask Register B (BAMRB)       128         7.2.7       Break Bus Cycle Register A (BBRA)       128         7.2.8       Break Data Register B (BDRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Register B (BDRB)       130         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1.1       Powerbown Modes       141         8.1.2       Register Configuration       142         <                                                      |       | 7.2.1                      | Break Address Register A (BARA)        | 126 |  |  |

| 7.2.4       Break ASID Register B (BASRB)       127         7.2.5       Break Address Mask Register A (BAMRA)       127         7.2.6       Break Address Mask Register B (BAMRB)       128         7.2.7       Break Bus Cycle Register B (BBRA)       128         7.2.8       Break Data Register B (BDRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Mask Register B (BDMRB)       131         7.2.11       Break Control Register B (BDRR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow.       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Oscirigiuration       143         8.2       Register Description       143         8.3       Sleep Mode       145         8.3       Standby Control Regis                                                                   |       | 7.2.2                      | Break Address Register B (BARB)        | 126 |  |  |

| 7.2.5       Break Address Mask Register A (BAMRA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | 7.2.3                      | Break ASID Register A (BASRA)          | 127 |  |  |

| 7.2.6       Break Address Mask Register B (BAMRB)       128         7.2.7       Break Bus Cycle Register A (BBRA)       128         7.2.8       Break Bus Cycle Register B (BBRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Mask Register B (BDRB)       131         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       143         8.2.1       Standby Control Register (STBCR)       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.2       Canceling Standby Mode       145         8.4.3       Canc                                                                   |       | 7.2.4                      | Break ASID Register B (BASRB)          | 127 |  |  |

| 7.2.7       Break Bus Cycle Register A (BBRA)       128         7.2.8       Break Bus Cycle Register B (BBRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Mask Register B (BDRB)       131         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow.       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.1       Transition to Standby Mode       145         8.4       Standby Mode       145                                                                                            |       | 7.2.5                      | Break Address Mask Register A (BAMRA)  | 127 |  |  |

| 7.2.8       Break Bus Cycle Register B (BBRB)       129         7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Mask Register B (BDMRB)       131         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.4.2       Canceling Sleep Mode       145         8.4.3       Clock Pause Function       147         8.5.4       Standby Mode       145                                                                                           |       | 7.2.6                      | Break Address Mask Register B (BAMRB)  | 128 |  |  |

| 7.2.9       Break Data Register B (BDRB)       130         7.2.10       Break Data Mask Register B (BDMRB)       131         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2       Register Description       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.4.2       Canceling Standby Mode       145         8.4.3       Clock Pause Function       147         8.5       Module Standby Function       147         8.5.1                                                                                                           |       | 7.2.7                      | Break Bus Cycle Register A (BBRA)      | 128 |  |  |

| 7.2.10       Break Data Mask Register B (BDMRB)       131         7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Power-Down Modes       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.4       Standby Mode       145         8.4.1       Transition to Standby Mode       145         8.4.2       Canceling Standby Mode       145         8.4.3       Clock Pause Function       147         8                                                                                                      |       | 7.2.8                      | Break Bus Cycle Register B (BBRB)      | 129 |  |  |

| 7.2.11       Break Control Register (BRCR)       132         7.3       UBC Operation       134         7.3.1       User Break Operation Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 7.2.9                      | Break Data Register B (BDRB)           | 130 |  |  |

| 7.3       UBC Operation       134         7.3.1       User Break Operation Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 7.2.10                     | Break Data Mask Register B (BDMRB)     | 131 |  |  |

| 7.3.1       User Break Operation Flow       134         7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2       Register Description       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.3.2       Canceling Sleep Mode       145         8.4.1       Transition to Standby Mode       145         8.4.3       Clock Pause Function       147         8.5       Module Standby Function       147         8.6       Timing of TATUS Pin Changes       148         8.6.1       Timing for Canceling Standbys       148         8.6.2       Timing for Canceling Standbys       150         8.6.3 </td <td></td> <td>7.2.11</td> <td>Break Control Register (BRCR)</td> <td>132</td>                     |       | 7.2.11                     | Break Control Register (BRCR)          | 132 |  |  |

| 7.3.2       Instruction Fetch Cycle Break       135         7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2       Register Description       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.3.2       Canceling Sleep Mode       145         8.4.1       Transition to Standby Mode       145         8.4.2       Canceling Standby Mode       146         8.4.3       Clock Pause Function       147         8.5.2       Clearing the Module Standby Function       147         8.5.2       Clearing the Module Standby Function       147         8.6.1       Timing of STATUS Pin Changes       148         8.6.2       Timing for Canceling Standbys       150                                                                                                | 7.3   | UBC C                      | Deration                               | 134 |  |  |

| 7.3.3       Data Access Cycle Break       136         7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2       Register Description       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.4       Standby Mode       145         8.4.1       Transition to Standby Mode       145         8.4.2       Canceling Standby Mode       146         8.4.3       Clock Pause Function       147         8.5.1       Transition to Module Standby Function       147         8.5.2       Clearing the Module Standby Function       147         8.5.4       Timing of STATUS Pin Changes       148         8.6.1       Timing for Canceling Standbys       150                                                                                                      |       | 7.3.1                      | User Break Operation Flow              | 134 |  |  |

| 7.3.4       Saved Program Counter (PC) Value       137         7.3.5       Examples of Use       138         7.3.6       Cautions       140         Section 8       Power-Down Modes       141         8.1       Overview       141         8.1.1       Power-Down Modes       141         8.1.2       Register Configuration       142         8.1.3       Pin Configuration       143         8.2       Register Description       143         8.2.1       Standby Control Register (STBCR)       143         8.3       Sleep Mode       145         8.3.1       Transition to Sleep Mode       145         8.3.2       Canceling Sleep Mode       145         8.4.1       Transition to Standby Mode       145         8.4.2       Canceling Standby Mode       146         8.4.3       Clock Pause Function       147         8.5.1       Transition to Module Standby Function       147         8.5.2       Clearing the Module Standby Function       147         8.6.1       Timing for Resets       148         8.6.2       Timing for Canceling Standbys       150         8.6.3       Timing for Canceling Standbys       150 <td></td> <td>7.3.2</td> <td>Instruction Fetch Cycle Break</td> <td>135</td>                    |       | 7.3.2                      | Instruction Fetch Cycle Break          | 135 |  |  |

| 7.3.5Examples of Use1387.3.6Cautions140Section 8Power-Down Modes1418.1Overview1418.1.1Power-Down Modes1418.1.2Register Configuration1428.1.3Pin Configuration1438.2Register Description1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1478.6Timing of STATUS Pin Changes1488.6.1Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 7.3.3                      | Data Access Cycle Break                | 136 |  |  |

| 7.3.6Cautions.140Section 8Power-Down Modes1418.1Overview.1418.1.1Power-Down Modes1418.1.2Register Configuration1428.1.3Pin Configuration1438.2Register Description1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1478.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Steep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 7.3.4                      | Saved Program Counter (PC) Value       | 137 |  |  |

| Section 8Power-Down Modes1418.1Overview.1418.1.1Power-Down Modes1418.1.2Register Configuration1428.1.3Pin Configuration1438.2Register Description1438.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | 7.3.5                      | Examples of Use                        | 138 |  |  |

| 8.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 7.3.6                      | Cautions                               | 140 |  |  |

| 8.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                            |                                        |     |  |  |

| 8.1.1Power-Down Modes1418.1.2Register Configuration1428.1.3Pin Configuration1438.2Register Description1438.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1478.6.4Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Step Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Secti | 10n 8                      | Power-Down Modes                       | 141 |  |  |

| 8.1.2Register Configuration1428.1.3Pin Configuration1438.2Register Description1438.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1478.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.1   | Overvi                     | ew                                     | 141 |  |  |

| 8.1.3Pin Configuration1438.2Register Description1438.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.6Timing of STATUS Pin Changes1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys1508.6.3Timing for Canceling Standbys150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 8.1.1                      | Power-Down Modes                       | 141 |  |  |

| 8.2Register Description1438.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 8.1.2                      | Register Configuration                 | 142 |  |  |

| 8.2.1Standby Control Register (STBCR)1438.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1458.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Step Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | 8.1.3                      | Pin Configuration                      | 143 |  |  |

| 8.3Sleep Mode1458.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.2   | Registe                    | er Description                         | 143 |  |  |

| 8.3.1Transition to Sleep Mode1458.3.2Canceling Sleep Mode1458.4Standby Mode1458.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1478.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 8.2.1                      | Standby Control Register (STBCR)       | 143 |  |  |

| 8.3.2Canceling Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.3   | Sleep M                    | Node                                   | 145 |  |  |

| 8.4Standby Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 8.3.1                      | Transition to Sleep Mode               | 145 |  |  |

| 8.4.1Transition to Standby Mode1458.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 8.3.2                      | Canceling Sleep Mode                   | 145 |  |  |

| 8.4.2Canceling Standby Mode1468.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.4   | Standb                     | y Mode                                 | 145 |  |  |

| 8.4.3Clock Pause Function1478.5Module Standby Function1478.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 8.4.1                      | · · · · · · · · · · · · · · · · · · ·  |     |  |  |

| 8.5Module Standby Function.1478.5.1Transition to Module Standby Function.1478.5.2Clearing the Module Standby Function.1488.6Timing of STATUS Pin Changes.1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys.1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | 8.4.2                      |                                        |     |  |  |

| 8.5.1Transition to Module Standby Function1478.5.2Clearing the Module Standby Function1488.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | 8.4.3                      | Clock Pause Function                   | 147 |  |  |

| 8.5.2Clearing the Module Standby Function.1488.6Timing of STATUS Pin Changes.1488.6.1Timing for Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.5   | Module                     | e Standby Function                     | 147 |  |  |

| 8.6Timing of STATUS Pin Changes1488.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | 8.5.1                      |                                        |     |  |  |

| 8.6.1Timing for Resets1488.6.2Timing for Canceling Standbys1508.6.3Timing for Canceling Sleep Mode151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 8.5.2                      | Clearing the Module Standby Function   | 148 |  |  |

| 8.6.2Timing for Canceling Standbys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.6   | Timing                     |                                        |     |  |  |

| 8.6.3 Timing for Canceling Sleep Mode 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 8.6.1                      |                                        |     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 8.6.2                      | Timing for Canceling Standbys          | 150 |  |  |

| 8.7 Hardware Standby Mode 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                            |                                        | 151 |  |  |

| 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.7   | Hardwa                     | are Standby Mode                       | 153 |  |  |

### 2.3.3 Instruction Formats

Table 2.3 explains the meaning of instruction formats and source and destination operands. The meaning of the operands depends on the operation code. The following symbols are used.

| xxxx: | Operation code       |

|-------|----------------------|

| mmmm: | Source register      |

| nnnn: | Destination register |

| iiii: | Immediate data       |

| dddd: | Displacement         |

### Table 2.3Instruction Formats

| Instruction Format                   | Source<br>Operand                                  | Destination<br>Operand                           | Instruction<br>Example |

|--------------------------------------|----------------------------------------------------|--------------------------------------------------|------------------------|

| 0 format 15 0<br>xxxx xxxx xxxx xxxx | _                                                  |                                                  | NOP                    |

| n format 15 0<br>xxxx nnnn xxxx xxxx |                                                    | nnnn: register<br>direct                         | MOVT Rn                |

|                                      | Control register or system register                | nnnn: register<br>direct                         | STS<br>MACH,Rn         |

|                                      | Control register or system register                | nnnn: register<br>indirect with<br>pre-decrement | STC.L<br>SR,@-Rn       |

| m format 15 0<br>xxxx mmmm xxxx xxxx | mmmm: register<br>direct                           | Control register<br>or system<br>register        | LDC<br>Rm,SR           |

|                                      | mmmm: register<br>indirect with post-<br>increment | Control register<br>or system<br>register        | LDC.L<br>@Rm+,SR       |

|                                      | mmmm: register<br>indirect                         | _                                                | JMP @Rm                |

|                                      | mmmm: PC-<br>relative using Rm                     |                                                  | BRAF Rm                |

### 3.6.2 Data Array

The data array is assigned to H'F3000000 to H'F3FFFFFF. To access a data array, the 32-bit address field (for read/write operations), and 32-bit data field (for write operations) must be specified. These are specified in the general register. The address section specifies information for selecting the entry to be accessed; the data section specifies the longword data to be written to the data array (figure 3.14 (2)).

In the address section, specify the entry address for selecting the entry (bits 16–12), W for selecting the way (bits 9–8: 00 is way 0, 01 is way 1, 10 is way 2, 11 is way 3), and H'F3 to indicate data array access (bits 31–24). The IX bit in MMUCR indicates whether an EX-OR is taken of the entry address and ASID.

Both reading and writing use the longword of the data array specified by the entry address and way number. The access size of the data array is fixed at longword.

# Section 7 User Break Controller (UBC)

### 7.1 Overview

The user break controller (UBC) provides functions that simplify program debugging. These functions make it easy to design an effective self-monitoring debugger, enabling programs to be debugged in the chip alone, without using an in-circuit emulator. Break conditions that can be set in the UBC are instruction fetch or data read/write, data size, data content, address value, and stop timing during instruction fetches.

#### 7.1.1 Features

The features of the user break controller are listed below.

- Two break channels (channel A and channel B). User break interrupts can be requested using either independent or sequential condition for the two channels (sequential breaks are channel A, then channel B).

- Selection and setting of the following as break compare conditions:

- Address

- Selection of 32-bit logical address and ASID to be compared Address: Compare all bits, mask bottom 10 bits, mask bottom 12 bits. mask all bits ASID: Compare all bits/mask all bits

- Data (channel B only, 32-bit maskable)

- Bus cycle: Instruction fetch/data access

- Read/write

- Operand size: byte/word/longword

- The instruction fetch cycle break can be performed before or after the instruction is executed.

- User break trap generated when break conditions are satisfied. A user-designed user break trap routine can be run.

### 7.1.2 Block Diagram

Figure 7.1 shows the logical block diagram of the user break controller.

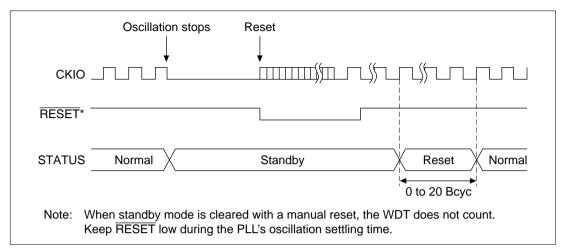

#### **Standby to Manual Reset:**

#### Figure 8.6 Standby to Manual Reset STATUS Output

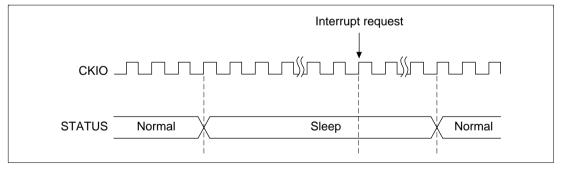

#### 8.6.3 Timing for Canceling Sleep Mode

### **Sleep to Interrupt:**

Figure 8.7 Sleep to Interrupt STATUS Output

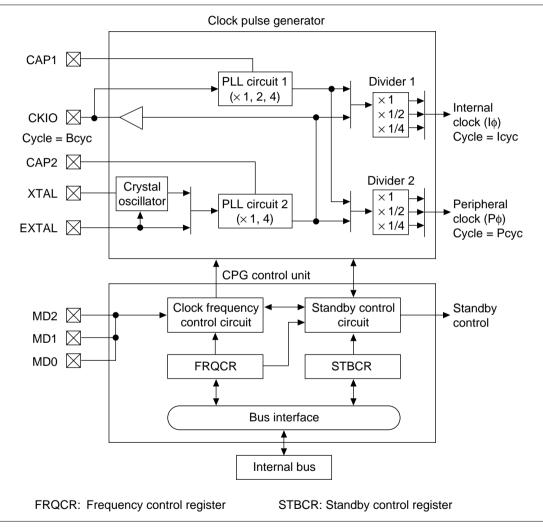

### 9.2 Overview of the CPG

### 9.2.1 CPG Block Diagram

A block diagram of the on-chip clock pulse generator is shown in figure 9.1(SH7708, SH7708S) and figure 9.2(SH7708R).

Figure 9.1 Block Diagram of Clock Pulse Generator(SH7708, SH7708S)

### 10.2 BSC Registers

### 10.2.1 Bus Control Register 1 (BCR1)

The bus control register 1 (BCR1) is a 16-bit read/write register that sets the functions and bus cycle status for each area. It is initialized to H'0000 by a power-on reset, but is not initialized by a manual reset or in standby mode. Do not access external memory outside area 0 until BCR1 register initialization is complete.

| Bit:           | 15     | 14     | 13       | 12     | 11     | 10     | 9      | 8      |

|----------------|--------|--------|----------|--------|--------|--------|--------|--------|

| Bit name:      |        | —      | HIZMEM*2 | HIZCNT | ENDIAN | A0BST1 | A0BST0 | A5BST1 |

| Initial value: | 0      | 0      | 0        | 0      | 0/1*1  | 0      | 0      | 0      |

| R/W:           | R      | R      | R/W      | R/W    | R      | R/W    | R/W    | R/W    |

|                |        |        |          |        |        |        |        |        |

| Bit:           | 7      | 6      | 5        | 4      | 3      | 2      | 1      | 0      |

| Bit name:      | A5BST0 | A6BST1 | A6BST0   | DRAM   | DRAM   | DRAM   | A5PCM  | A6PCM  |

|                |        |        |          | TP2    | TP1    | TP0    |        |        |

| Initial value: | 0      | 0      | 0        | 0      | 0      | 0      | 0      | 0      |

| R/W:           | R/W    | R/W    | R/W      | R/W    | R/W    | R/W    | R/W    | R/W    |

|                |        |        |          |        |        |        |        |        |

Notes: 1. Samples the value of the external pin designating endian upon a power-on reset. 2. Reserved bit in the SH7708.

Bits 15 and 14—Reserved: These bits always read 0. The write value should always be 0.

Bits 13 (SH7708)—Reserved: These bits always read 0. The write value should always be 0. This bit is not supported in emulator.

Bit 13 (SH7708S, SH7708R) —High-Z Memory Control (HIZMEM): Specifies the state of A25 to A0, BS, CS, RD/WR, WE/DQM, RD, MD3/CE2A, and MD4/CE2B in standby mode.

| Bit 13: HIZMEM | Description                             |                 |

|----------------|-----------------------------------------|-----------------|

| 0              | High-impedance (high-Z) in standby mode | (Initial value) |

| 1              | Drive state in standby mode             |                 |

Bit 12—High-Z Control (HIZCNT): Specifies the state of the RAS and CAS signals in the standby and bus-released states.

Bits 9 and 8—CAS-Before-RAS Refresh RAS Assert Time (TRAS1, TRAS0): These bits set the RAS assert period for CAS-before-RAS refreshing of the DRAM connected to area 2.

| Bit 9: TRAS1 | Bit 8: TRAS0 | Description |                 |

|--------------|--------------|-------------|-----------------|

| 0            | 0            | 2 cycles    | (Initial value) |

|              | 1            | 3 cycles    |                 |

| 1            | 0            | 4 cycles    |                 |

|              | 1            | 5 cycles    |                 |

In the SH7708, set the same values in the TRAS bits in MCR and DCR.

Bit 6—Burst Enable (BE): Specifies whether to conduct a burst access of the DRAM connected to area 2.

| Bit 6: BE | Description                 |                 |

|-----------|-----------------------------|-----------------|

| 0         | Burst disabled              | (Initial value) |

| 1         | High-speed page mode access |                 |

Bits 4 and 3—Address Multiplex (AMX1, AMX0): These bits specify address multiplexing for the DRAM connected to area 2.

| Bit 4: AMX1 | Bit 3: AMX0 | Description                   |                 |

|-------------|-------------|-------------------------------|-----------------|

| 0           | 0           | 8-bit column address product  | (Initial value) |

|             | 1           | 9-bit column address product  |                 |

| 1           | 0           | 10-bit column address product |                 |

|             | 1           | 11-bit column address product |                 |

Bit 2—Refresh Control (RFSH): Determines whether or not refreshing of the DRAM connected to area 2 is performed.

| Bit 2: RFSH | Description |                 |

|-------------|-------------|-----------------|

| 0           | No refresh  | (Initial value) |

| 1           | Refresh     |                 |

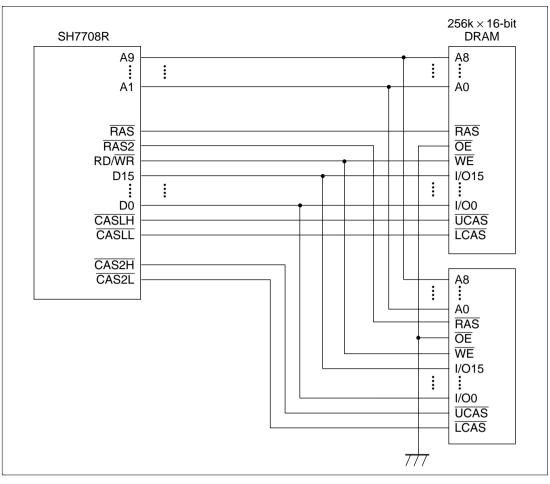

Figure 10.14 Example of DRAM Connection (16-Bit Data Width)

### 13.1.3 Pin Configuration

The SCI has the serial pins summarized in table 13.1.

| Pin Name          | Abbreviation | Input/Output | Function             |

|-------------------|--------------|--------------|----------------------|

| Serial clock pin  | SCK          | Input/output | Clock input/output   |

| Receive data pin  | RxD          | Input        | Receive data input   |

| Transmit data pin | TxD          | Output       | Transmit data output |

Note: These pins function as mode input pins MD0–MD02 after a power-on reset. They are made to function as serial pins by performing SCI operation settings with the TE, RE, CKEI, and CKE0 bits in SCSCR and the C/Ā bit in SCSMR. Break status transmission and detection can be performed by means of the SCI's SCSPTR register.

### 13.1.4 Register Configuration

Table 13.2 summarizes the SCI internal registers. These registers select the communication mode (asynchronous or synchronous), specify the data format and bit rate, and control the transmitter and receiver sections.

| Name                    | Abbreviation | R/W     | Initial Value* <sup>2</sup> | Address    | Access Size |

|-------------------------|--------------|---------|-----------------------------|------------|-------------|

| Serial mode register    | SCSMR        | R/W     | H'00                        | H'FFFFFE80 | 8           |

| Bit rate register       | SCBRR        | R/W     | H'FF                        | H'FFFFFE82 | 8           |

| Serial control register | SCSCR        | R/W     | H'00                        | H'FFFFFE84 | 8           |

| Transmit data register  | SCTDR        | R/W     | H'FF                        | H'FFFFFE86 | 8           |

| Serial status register  | SCSSR        | R/(W)*1 | H'84                        | H'FFFFFE88 | 8           |

| Receive data register   | SCRDR        | R       | H'00                        | H'FFFFFE8A | 8           |

| Serial port register    | SCSPTR       | R/W     | Undefined (Initialized)*3   | H'FFFFFF7C | 8           |

### Table 13.2 Registers

Notes: 1 Only 0 can be written, to clear the flags.

2 Initialized by power-on reset or manual reset.

3. All bits except 2 and 0 are initialized to 0. The value of bits 2 and 0 is undefined.

Bit 3—Stop Bit Length (STOP): Selects one or two bits as the stop bit length in asynchronous mode. This setting is used only in asynchronous mode. It is ignored in synchronous mode because no stop bits are added.

In receiving, only the first stop bit is checked, regardless of the STOP bit setting. If the second stop bit is 1, it is treated as a stop bit, but if the second stop bit is 0, it is treated as the start bit of the next incoming character.

| Bit 3: STOP | Description                                                                       |        |

|-------------|-----------------------------------------------------------------------------------|--------|

| 0           | One stop bit (Initial v                                                           | /alue) |

|             | In transmitting, a single 1-bit is added at the end of each transmitte character. | d      |

| 1           | Two stop bits                                                                     |        |

|             | In transmitting, two 1-bits are added at the end of each transmitted character.   |        |

Bit 2—Multiprocessor Mode (MP): Selects multiprocessor format. When multiprocessor format is selected, settings of the parity enable (PE) and parity mode  $(O/\overline{E})$  bits are ignored. The MP bit setting is used only in asynchronous mode; it is ignored in synchronous mode. For the multiprocessor communication function, see section 13.3.3, Multiprocessor Communication.

| Bit 2: MP | Description                      |                 |

|-----------|----------------------------------|-----------------|

| 0         | Multiprocessor function disabled | (Initial value) |

| 1         | Multiprocessor format selected   |                 |

Bits 1 and 0—Clock Select 1 and 0 (CKS1 and CKS0): These bits select the internal clock source of the on-chip baud rate generator. Four clock sources are available:  $P\phi$ ,  $P\phi/4$ ,  $P\phi/16$  and  $P\phi/64$ . For further information on the clock source, bit rate register settings, and baud rate, see section 13.2.9, Bit Rate Register.

| Bit 1: CKS1 | Bit 0: CKS0 | Description |                 |

|-------------|-------------|-------------|-----------------|

| 0           | 0           | Ρφ          | (Initial value) |

|             | 1           | Ρφ/4        |                 |

| 1           | 0           | Ρφ/16       |                 |

|             | 1           | Ρφ/64       |                 |

Note: Po: Peripheral clock

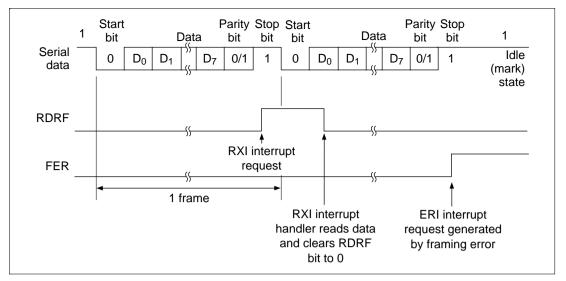

Figure 13.8 SCI Receive Operation (Example: 8-bit Data with Parity and One Stop Bit)

### 13.3.3 Multiprocessor Communication

The multiprocessor communication function enables several processors to share a single serial communication line. The processors communicate in asynchronous mode using a format with an additional multiprocessor bit (multiprocessor format).

In multiprocessor communication, each receiving processor is addressed by a unique ID. A serial communication cycle consists of an ID-sending cycle that identifies the receiving processor, and a data-sending cycle. The multiprocessor bit distinguishes ID-sending cycles from data-sending cycles. The transmitting processor starts by sending the ID of the receiving processor with which it wants to communicate as data with the multiprocessor bit set to 1. Next the transmitting processor sends transmit data with the multiprocessor bit cleared to 0.

Receiving processors skip incoming data until they receive data with the multiprocessor bit set to 1. When they receive data with the multiprocessor bit set to 1, receiving processors compare the data with their IDs. The receiving processor with a matching ID continues to receive further incoming data. Processors with IDs not matching the received data skip further incoming data until they again receive data with the multiprocessor bit set to 1. Multiple processors can send and receive data in this way.

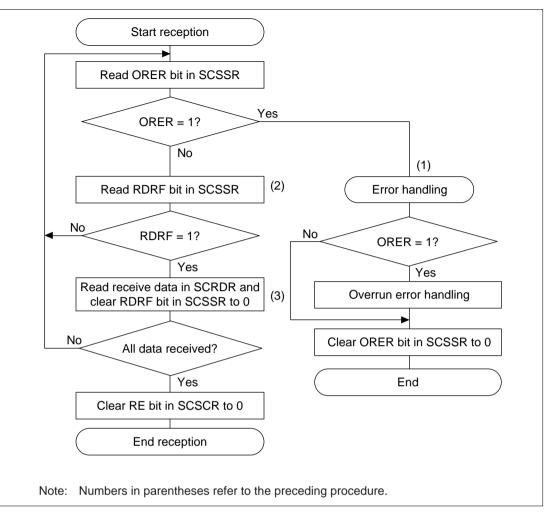

Figure 13.18 Sample Flowchart for Serial Receiving

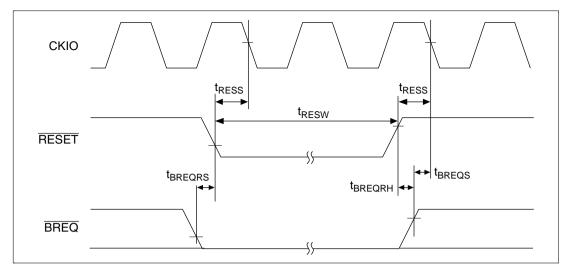

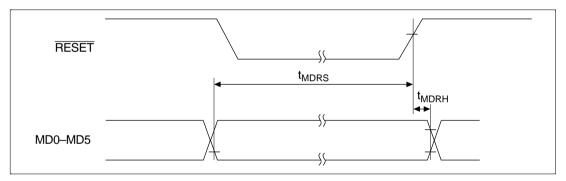

Figure 16.11 Manual Reset Input Timing

Figure 16.12 Mode Input Timing

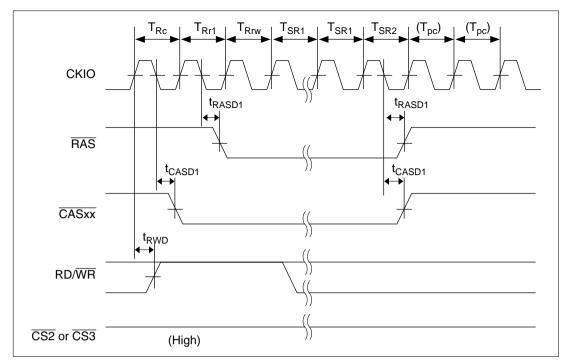

Figure 16.33 DRAM Self-Refresh Cycle (TPC = 0)

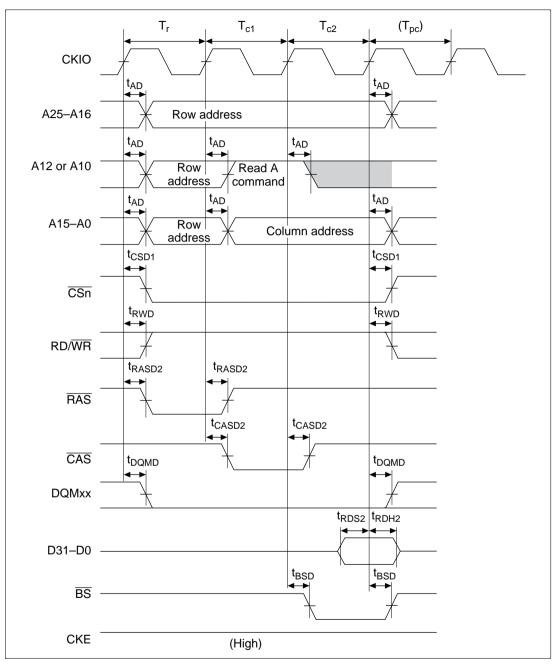

Figure 16.34 Synchronous DRAM Read Bus Cycle (RCD = 0, CAS Latency = 1, TPC = 0)

#### Renesas

## 17.2 DC Characteristics

| Item                            |                                          | Symbol          | Min                                                  | Тур               | Max                                | Unit Remarks |                                                   |

|---------------------------------|------------------------------------------|-----------------|------------------------------------------------------|-------------------|------------------------------------|--------------|---------------------------------------------------|

| Power sup                       | ply voltage                              | $V_{cc}$        | 3.15                                                 | 3.3               | 3.6                                | V            | In normal operation, sleep mode, and standby mode |

| Current                         | Normal operation                         | I <sub>cc</sub> |                                                      | 120* <sup>1</sup> | 200 *1                             | mΑ           | V <sub>cc</sub> = 3.3 V                           |

|                                 |                                          |                 |                                                      |                   |                                    | _            | *1 lø = 100 MHz                                   |

|                                 |                                          |                 |                                                      |                   |                                    |              | Bø = 50 MHz                                       |

|                                 | In sleep mode                            | _               | _                                                    | 75* <sup>2</sup>  | 100 *2                             | -            | *2 Bø = 60 MHz                                    |

|                                 |                                          |                 |                                                      |                   |                                    | -            | Pø = 30 MHz                                       |

|                                 | In standby mode                          | _               | _                                                    | 0.1* <sup>3</sup> | 1* <sup>3</sup>                    | mA           | <sup>*</sup> 3 V <sub>cc</sub> = 3.3 V/ Ta= 30 °C |

| Input                           | RESET, NMI                               | VIH             | $\frac{V_{CC} \times 0.9 - 0.9}{V_{CC} - 0.5 - 0.5}$ |                   | $V_{CC} + 0.3 V$<br>$V_{CC} + 0.3$ |              |                                                   |