#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Core ProcessorM8CCore Size8-BitSpeed24MHzConnectivityIPC, SPIPeripheralsLVD, POR, WDTNumber of I/O13Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-Nufsize1.71V ~ 3.6VData ConvertersA/D 1x10bOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-QFN (3x3)                                                                                     |                            |                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------|

| Core Size8-BitCore Size24MHzSpeed24MHzConnectivityI²C, SPIPeripheralsLVD, POR, WDTNumber of I/O13Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3) | Product Status             | Obsolete                                                                    |

| Speed24MHzConnectivityPC, SPIPeripheralsLVD, POR, WDTNumber of I/O13Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.X1V ~ 3.6VVoltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOperating Temperature0°C ~ 70°C (TA)Mounting Type6°L = MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                 | Core Processor             | M8C                                                                         |

| ConnectivityI²C, SPIPeripheralsLVD, POR, WDTNumber of I/O13Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting Type16-UFQFNSupplier Device Package16-QFN (3x3)                                                                  | Core Size                  | 8-Bit                                                                       |

| PeripheralsLVD, POR, WDTNumber of I/O13Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFRN (3x3)                                                                                         | Speed                      | 24MHz                                                                       |

| Number of I/O13Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                   | Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                  | Peripherals                | LVD, POR, WDT                                                               |

| Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1×10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                                                 | Number of I/O              | 13                                                                          |

| EEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                                                                         | Program Memory Size        | 8KB (8K x 8)                                                                |

| RAM SizeIK × 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                                                                                     | Program Memory Type        | FLASH                                                                       |

| Voltage - Supply (Vcc/Vdd)1.71V ~ 3.6VData ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                                                                                                   | EEPROM Size                | -                                                                           |

| Data ConvertersA/D 1x10bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeSurface MountPackage / Case16-UFQFNSupplier Device Package16-QFN (3x3)                                                                                                                                                                                                                         | RAM Size                   | 1K x 8                                                                      |

| Oscillator Type Internal   Operating Temperature 0°C ~ 70°C (TA)   Mounting Type Surface Mount   Package / Case 16-UFQFN   Supplier Device Package 16-QFN (3x3)                                                                                                                                                                                                                                | Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                |

| Operating Temperature 0°C ~ 70°C (TA)   Mounting Type Surface Mount   Package / Case 16-UFQFN   Supplier Device Package 16-QFN (3x3)                                                                                                                                                                                                                                                           | Data Converters            | A/D 1x10b                                                                   |

| Mounting Type Surface Mount   Package / Case 16-UFQFN   Supplier Device Package 16-QFN (3x3)                                                                                                                                                                                                                                                                                                   | Oscillator Type            | Internal                                                                    |

| Package / Case 16-UFQFN   Supplier Device Package 16-QFN (3x3)                                                                                                                                                                                                                                                                                                                                 | Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Supplier Device Package 16-QFN (3x3)                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | 16-UFQFN                                                                    |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/cy7c60413-16lkxc                                                                                                                                                                                                                                                                                                       | Supplier Device Package    | 16-QFN (3x3)                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c60413-16lkxc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The basic I<sup>2</sup>C features include:

- +Slave, transmitter, and receiver operation

- +Byte processing for low CPU overhead

- \*Interrupt or polling CPU interface

- +Support for clock rates of up to 400 kHz

- +7- or 10-bit addressing (through firmware support)

- \*SMBus operation (through firmware support)

- Enhanced features of the I<sup>2</sup>C Slave Enhanced Module include:

- Support for 7-bit hardware address compare

- Flexible data buffering schemes

- +A 'no bus stalling' operating mode

- A low power bus monitoring mode

The I<sup>2</sup>C block controls the data (SDA) and the clock (SCL) to the external I<sup>2</sup>C interface through direct connections to two dedicated GPIO pins. When I<sup>2</sup>C is enabled, these GPIO pins are not available for general purpose use. The enCoRe V LV CPU firmware interacts with the block through I/O register reads and writes, and firmware synchronization is implemented through polling and/or interrupts.

In the default operating mode, which is firmware compatible with previous versions of  $I^2C$  slave modules, the  $I^2C$  bus is stalled upon every received address or byte, and the CPU is required to read the data or supply data as required before the  $I^2C$  bus continues. However, this  $I^2C$  Slave Enhanced module provides new data buffering capability as an enhanced feature. In the EZI<sup>2</sup>C buffering mode, the  $I^2C$  slave interface appears as a 32-byte RAM buffer to the external  $I^2C$  master. Using a simple predefined protocol, the master controls the read and write pointers into the RAM. When this method is enabled, the slave never stalls the bus. In this protocol, the data available in the RAM (this is managed by the CPU) is valid.

### Additional System Resources

System Resources, some of which have been previously listed, provide additional capability useful to complete systems. Additional resources include low voltage detection and power on reset. The following statements describe the merits of each system resource:

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced power-on reset (POR) circuit eliminates the need for a system supervisor.

- The 3.6 V maximum input, 1.8, 2.5, or 3 V selectable output, low dropout regulator (LDO) provides regulation for I/Os. A register controlled bypass mode enables the user to disable the LDO.

- Standard Cypress PSoC IDE tools are available for debugging the enCoRe V LV family of parts.

## **Getting Started**

The quickest way to understanding the enCoRe V silicon is by reading this datasheet and using the PSoC Designer Integrated Development Environment (IDE). This datasheet is an overview of the enCoRe V integrated circuit and presents specific pin, register, and electrical specifications. For in-depth information, along with detailed programming information, refer to the *PSoC Programmable System-on-Chip Technical Reference Manual*, for CY8C28xxx PSoC devices.

For up-to-date ordering, packaging, and electrical specification information, reference the latest enCoRe V device datasheets on the web at http://www.cypress.com.

### **Application Notes**

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

### **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

### Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

### **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

### **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

### **Technical Support**

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

## **Designing with PSoC Designer**

The development process for the PSoC device differs from that of a traditional fixed-function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and lowering inventory costs. These configurable resources, called PSoC blocks, have the ability to implement a wide variety of user-selectable functions. The PSoC development process is:

- 1. Select user modules.

- 2. Configure user modules.

- 3. Organize and connect.

- 4. Generate, verify, and debug.

#### Select User Modules

PSoC Designer provides a library of prebuilt, pretested hardware peripheral components called "user modules." User modules make selecting and implementing peripheral devices, both analog and digital, simple.

### **Configure User Modules**

Each user module that you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a PWM User Module configures one or more digital PSoC blocks, one for each eight bits of resolution. Using these parameters, you can establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All of the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the user module and provide performance specifications. Each datasheet describes the use of each user module parameter, and other information that you may need to successfully implement your design.

#### **Organize and Connect**

Build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. Perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides APIs with high-level functions to control and respond to hardware events at run time, and interrupt service routines that you can adapt as needed.

A complete code development environment lets you to develop and customize your applications in C, assembly language, or both.

The last step in the development process takes place inside PSoC Designer's Debugger (accessed by clicking the Connect icon). PSoC Designer downloads the HEX image to the ICE where it runs at full-speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint, and watch-variable features, the debug interface provides a large trace buffer. It lets you to define complex breakpoint events that include monitoring address and data bus values, memory locations, and external signals.

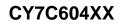

### 32-Pin Part Pinout

### Figure 6. CY7C60445 32-Pin enCoRe V LV Device

### Table 2. 32-Pin Part Pinout (QFN)

| Pin No. | Туре        | Name                   | Description                                           |

|---------|-------------|------------------------|-------------------------------------------------------|

| 1       | IOH         | P0[1]                  | Digital I/O                                           |

| 2       | I/O         | P2[7]                  | Digital I/O                                           |

| 3       | I/O         | P2[5]                  | Digital I/O, crystal out (Xout)                       |

| 4       | I/O         | P2[3]                  | Digital I/O, crystal in (Xin)                         |

| 5       | I/O         | P2[1]                  | Digital I/O                                           |

| 6       | I/O         | P3[3]                  | Digital I/O                                           |

| 7       | I/O         | P3[1]                  | Digital I/O                                           |

| 8       | IOHR        | P1[7]                  | Digital I/O, I <sup>2</sup> C SCL, SPI SS             |

| 9       | IOHR        | P1[5]                  | Digital I/O, I <sup>2</sup> C SDA, SPI MISO           |

| 10      | IOHR        | P1[3]                  | Digital I/O, SPI CLK                                  |

| 11      | IOHR        | P1[1] <sup>(1,2)</sup> | Digital I/O, ISSP CLK, I <sup>2</sup> C SCL, SPI MOSI |

| 12      | Power       | Vss                    | Ground connection                                     |

| 13      | IOHR        | P1[0] <sup>(1,2)</sup> | Digital I/O, ISSP DATA, I <sup>2</sup> C SDA, SPI CLK |

| 14      | IOHR        | P1[2]                  | Digital I/O                                           |

| 15      | IOHR        | P1[4]                  | Digital I/O, optional external clock input (EXTCLK)   |

| 16      | IOHR        | P1[6]                  | Digital I/O                                           |

| 17      | Reset Input | XRES                   | Active high external reset with internal pull-down    |

| 18      | I/O         | P3[0]                  | Digital I/O                                           |

| 19      | I/O         | P3[2]                  | Digital I/O                                           |

| 20      | I/O         | P2[0]                  | Digital I/O                                           |

| 21      | I/O         | P2[2]                  | Digital I/O                                           |

| 22      | I/O         | P2[4]                  | Digital I/O                                           |

| 23      | I/O         | P2[6]                  | Digital I/O                                           |

| 24      | IOH         | P0[0]                  | Digital I/O                                           |

| 25      | IOH         | P0[2]                  | Digital I/O                                           |

| 26      | IOH         | P0[4]                  | Digital I/O                                           |

| 27      | IOH         | P0[6]                  | Digital I/O                                           |

### Table 2. 32-Pin Part Pinout (QFN) (continued)

| Pin No. | Туре  | Name  | Description                            |

|---------|-------|-------|----------------------------------------|

| 28      | Power | Vdd   | Supply voltage                         |

| 29      | IOH   | P0[7] | Digital I/O                            |

| 30      | IOH   | P0[5] | Digital I/O                            |

| 31      | IOH   | P0[3] | Digital I/O                            |

| 32      | Power | Vss   | Ground connection                      |

| CP      | Power | Vss   | Center pad must be connected to ground |

$\textbf{LEGEND} \ \textbf{I} = \textbf{Input}, \ \textbf{O} = \textbf{Output}, \ \textbf{OH} = 5 \ \textbf{mA} \ \textbf{High} \ \textbf{Output} \ \textbf{Drive}, \ \textbf{R} = \textbf{Regulated} \ \textbf{Output}.$

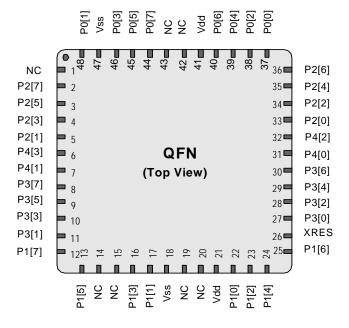

### **48-Pin Part Pinout**

### Figure 7. CY7C60455/CY7C60456 48-Pin enCoRe V LV Device

### Table 3. 48-Pin Part Pinout (QFN)

| Pin No. | Туре  | Name                   | Description                                           |

|---------|-------|------------------------|-------------------------------------------------------|

| 1       | NC    | NC                     | No connection                                         |

| 2       | I/O   | P2[7]                  | Digital I/O                                           |

| 3       | I/O   | P2[5]                  | Digital I/O, crystal out (Xout)                       |

| 4       | I/O   | P2[3]                  | Digital I/O, crystal in (Xin)                         |

| 5       | I/O   | P2[1]                  | Digital I/O                                           |

| 6       | I/O   | P4[3]                  | Digital I/O                                           |

| 7       | I/O   | P4[1]                  | Digital I/O                                           |

| 8       | I/O   | P3[7]                  | Digital I/O                                           |

| 9       | I/O   | P3[5]                  | Digital I/O                                           |

| 10      | I/O   | P3[3]                  | Digital I/O                                           |

| 11      | I/O   | P3[1]                  | Digital I/O                                           |

| 12      | IOHR  | P1[7]                  | Digital I/O, I <sup>2</sup> C SCL, SPI SS             |

| 13      | IOHR  | P1[5]                  | Digital I/O, I <sup>2</sup> C SDA, SPI MISO           |

| 14      | NC    | NC                     | No connection                                         |

| 15      | NC    | NC                     | No connection                                         |

| 16      | IOHR  | P1[3]                  | Digital I/O, SPI CLK                                  |

| 17      | IOHR  | P1[1] <sup>(1,2)</sup> | Digital I/O, ISSP CLK, I <sup>2</sup> C SCL, SPI MOSI |

| 18      | Power | Vss                    | Supply ground                                         |

| 19      | NC    | NC                     | No connection                                         |

| 20      | NC    | NC                     | No connection                                         |

| 21      | Power | Vdd                    | Supply voltage                                        |

### Table 3. 48-Pin Part Pinout (QFN) (continued)

| Pin No. | Туре  | Name                   | Description                                         |

|---------|-------|------------------------|-----------------------------------------------------|

| 22      | IOHR  | P1[0] <sup>(1,2)</sup> | Digital I/O, ISSP DATA, I2C SDA, SPI CLK            |

| 23      | IOHR  | P1[2]                  | Digital I/O                                         |

| 24      | IOHR  | P1[4]                  | Digital I/O, optional external clock input (EXTCLK) |

| 25      | IOHR  | P1[6]                  | Digital I/O                                         |

| 26      | XRES  | Ext Reset              | Active high external reset with internal pull-down  |

| 27      | I/O   | P3[0]                  | Digital I/O                                         |

| 28      | I/O   | P3[2]                  | Digital I/O                                         |

| 29      | I/O   | P3[4]                  | Digital I/O                                         |

| 30      | I/O   | P3[6]                  | Digital I/O                                         |

| 31      | I/O   | P4[0]                  | Digital I/O                                         |

| 32      | I/O   | P4[2]                  | Digital I/O                                         |

| 33      | I/O   | P2[0]                  | Digital I/O                                         |

| 34      | I/O   | P2[2]                  | Digital I/O                                         |

| 35      | I/O   | P2[4]                  | Digital I/O                                         |

| 36      | I/O   | P2[6]                  | Digital I/O                                         |

| 37      | IOH   | P0[0]                  | Digital I/O                                         |

| 38      | IOH   | P0[2]                  | Digital I/O                                         |

| 39      | IOH   | P0[4]                  | Digital I/O                                         |

| 40      | IOH   | P0[6]                  | Digital I/O                                         |

| 41      | Power | Vdd                    | Supply voltage                                      |

| 42      | NC    | NC                     | No connection                                       |

| 43      | NC    | NC                     | No connection                                       |

| 44      | IOH   | P0[7]                  | Digital I/O                                         |

| 45      | IOH   | P0[5]                  | Digital I/O                                         |

| 46      | IOH   | P0[3]                  | Digital I/O                                         |

| 47      | Power | Vss                    | Supply ground                                       |

| 48      | IOH   | P0[1]                  | Digital I/O                                         |

| CP      | Power | Vss                    | Center pad must be connected to ground              |

LEGEND I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output

### Table 6. Register Map Bank 1 Table: Configuration Space

| Name               |              |              | Name    |                           |        | Nome |                    | A      | Nome     | Addr (1 Hav) | A      |

|--------------------|--------------|--------------|---------|---------------------------|--------|------|--------------------|--------|----------|--------------|--------|

| PRT0DM0            | Addr (1,Hex) | Access<br>RW | Name    | <b>Addr (1,Hex)</b><br>40 | Access | Name | Addr (1,Hex)<br>80 | Access | Name     | Addr (1,Hex) | Access |

| PRT0DM0<br>PRT0DM1 | 01           | RW           |         | 40                        |        |      | 80                 |        |          | C1           |        |

| PRIUDIVIT          | 01           | RW           |         | 41                        |        |      |                    |        |          | C1<br>C2     |        |

|                    | 02           |              |         | 42                        |        |      | 82<br>83           |        |          | C2<br>C3     |        |

| PRT1DM0            | 03           | RW           |         | 43                        |        |      | 83<br>84           |        |          | C3           |        |

| PRT1DM0<br>PRT1DM1 | 04           | RW           |         | 44 45                     |        |      | 84<br>85           |        |          | C4<br>C5     |        |

| PRIIDMI            | 05           | RW           |         | 45<br>46                  |        |      | 85                 |        |          | C5<br>C6     |        |

|                    |              |              | -       |                           |        |      |                    |        |          |              |        |

| PPTOPMO            | 07           | D)A/         |         | 47                        |        | -    | 87                 |        |          | C7           |        |

| PRT2DM0            | 08           | RW           |         | 48                        |        |      | 88                 |        |          | C8           |        |

| PRT2DM1            | 09           | RW           |         | 49                        |        |      | 89                 |        |          | C9           |        |

|                    | 0A           |              |         | 4A                        |        |      | 8A                 |        |          | CA           |        |

|                    | 0B           |              |         | 4B                        |        |      | 8B                 |        |          | СВ           |        |

| PRT3DM0            | 0C           | RW           |         | 4C                        |        |      | 8C                 |        |          | CC           |        |

| PRT3DM1            | 0D           | RW           |         | 4D                        |        |      | 8D                 |        |          | CD           |        |

|                    | 0E           |              |         | 4E                        |        |      | 8E                 |        |          | CE           |        |

|                    | 0F           |              |         | 4F                        |        |      | 8F                 |        |          | CF           |        |

| PRT4DM0            | 10           | RW           |         | 50                        |        |      | 90                 |        |          | D0           |        |

| PRT4DM1            | 11           | RW           |         | 51                        |        |      | 91                 |        |          | D1           |        |

|                    | 12           |              |         | 52                        |        |      | 92                 |        |          | D2           |        |

|                    | 13           |              |         | 53                        |        |      | 93                 |        |          | D3           |        |

|                    | 14           |              |         | 54                        |        |      | 94                 |        |          | D4           |        |

|                    | 15           |              |         | 55                        |        |      | 95                 |        |          | D5           |        |

|                    | 16           |              |         | 56                        |        |      | 96                 |        |          | D6           |        |

|                    | 17           |              |         | 57                        |        |      | 97                 |        |          | D7           |        |

|                    | 18           |              |         | 58                        |        |      | 98                 |        |          | D8           |        |

|                    | 19           |              |         | 59                        |        |      | 99                 |        |          | D9           |        |

|                    | 1A           |              |         | 5A                        |        |      | 9A                 |        |          | DA           |        |

|                    | 1B           |              |         | 5B                        |        |      | 9B                 |        |          | DB           |        |

|                    | 1C           |              |         | 5C                        |        |      | 9C                 |        | IO_CFG   | DC           | RW     |

|                    | 1D           |              | -       | 5D                        |        |      | 9D                 |        | OUT_P1   | DD           | RW     |

|                    | 1E           |              | -       | 5E                        |        |      | 9E                 |        |          | DE           |        |

|                    | 1F           |              | -       | 5F                        |        |      | 9F                 |        |          | DF           |        |

|                    | 20           |              |         | 60                        |        |      | A0                 |        | OSC_CR0  | E0           | RW     |

|                    | 21           |              |         | 61                        |        |      | A1                 |        | ECO_CFG  | E1           | #      |

|                    | 22           |              |         | 62                        |        |      | A2                 |        | OSC_CR2  | E2           | RW     |

|                    | 23           |              |         | 63                        |        |      | A3                 |        | VLT_CR   | E3           | RW     |

|                    | 24           |              |         | 64                        |        |      | A4                 |        | VLT_CMP  | E4           | R      |

|                    | 25           |              |         | 65                        |        |      | A5                 |        | 121_0    | E5           |        |

|                    | 26           |              |         | 66                        |        | -    | A6                 |        |          | E6           |        |

|                    | 27           |              | -       | 67                        |        | -    | A7                 |        |          | E7           |        |

|                    | 28           |              |         | 68                        |        |      | A8                 |        | IMO_TR   | E8           | W      |

| SPI_CFG            | 29           | RW           |         | 69                        |        |      | A9                 |        | ILO_TR   | E9           | W      |

| 3FI_CFG            | 29<br>2A     | RVV          |         | 69<br>6A                  |        |      | A9<br>AA           |        |          | EA           | vv     |

|                    | 2A<br>2B     |              |         | 6A<br>6B                  |        |      | AA<br>AB           |        | SLP_CFG  | EB           | RW     |

|                    | 2B<br>2C     |              | TMP_DR0 |                           | DW     |      |                    |        |          |              | RW     |

|                    |              |              |         | 6C                        | RW     |      | AC                 |        | SLP_CFG2 | EC           | RW     |

|                    | 2D           |              | TMP_DR1 | 6D                        | RW     | -    | AD                 |        | SLP_CFG3 | ED           | rtvv   |

|                    | 2E           |              | TMP_DR2 | 6E                        | RW     |      | AE                 |        |          | EE           |        |

|                    | 2F           |              | TMP_DR3 | 6F                        | RW     |      | AF                 |        |          | EF           |        |

|                    | 30           |              |         | 70                        |        |      | B0                 |        |          | FO           |        |

|                    | 31           |              |         | 71                        |        |      | B1                 |        |          | F1           |        |

|                    | 32           |              |         | 72                        |        |      | B2                 |        |          | F2           |        |

|                    | 33           |              |         | 73                        |        |      | B3                 |        |          | F3           |        |

|                    | 34           |              |         | 74                        |        |      | B4                 |        |          | F4           |        |

|                    | 35           |              |         | 75                        |        |      | B5                 |        |          | F5           |        |

|                    | 36           |              |         | 76                        |        |      | B6                 |        |          | F6           |        |

|                    | 37           |              |         | 77                        |        |      | B7                 |        | CPU_F    | F7           | RL     |

|                    | 38           |              |         | 78                        |        |      | B8                 |        |          | F8           |        |

|                    | 39           |              |         | 79                        |        |      | B9                 |        |          | F9           |        |

|                    | 3A           |              |         | 7A                        |        |      | BA                 |        |          | FA           |        |

|                    | 3B           |              |         | 7B                        |        |      | BB                 |        |          | FB           |        |

|                    | 3C           |              |         | 7C                        |        |      | BC                 |        |          | FC           |        |

|                    | 3D           |              |         | 7D                        |        |      | BD                 |        |          | FD           |        |

|                    |              |              |         |                           |        |      |                    |        |          |              |        |

|                    | 3E           |              |         | 7E                        |        |      | BE                 |        |          | FE           |        |

Gray fields are reserved and should not be accessed. # Access is bit specific.

## **Electrical Specifications**

This section presents the DC and AC electrical specifications of the enCoRe V LV devices. For the most up to date electrical specifications, verify that you have the most recent datasheet available by visiting the company web site at http://www.cypress.com.

### **DC Electrical Characteristics**

#### DC Chip Level Specifications

Table 9 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 9. DC Chip Level Specifications

| Symbol                | Description                                    | Conditions                                                                             | Min  | Тур | Max | Units |

|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|-----|-------|

| Vdd <sup>[5, 6]</sup> | Supply voltage                                 | See table titled DC POR and LVD Specifications on page 22.                             | 1.71 | -   | 3.6 | V     |

| I <sub>DD24</sub>     | Supply current, IMO = 24 MHz                   | Conditions are Vdd $\leq$ 3.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 24 MHz<br>No I2C/SPI | _    | 2.9 | 4.0 | mA    |

| I <sub>DD12</sub>     | Supply current, IMO = 12 MHz                   | Conditions are Vdd $\leq$ 3.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 12 MHz<br>No I2C/SPI | _    | 1.7 | 2.6 | mA    |

| I <sub>DD6</sub>      | Supply current, IMO = 6 MHz                    | Conditions are Vdd $\leq$ 3.0 V, T <sub>A</sub> = 25 °C,<br>CPU = 6 MHz<br>No I2C/SPI  | _    | 1.2 | 1.8 | mA    |

| I <sub>SB1</sub>      | Standby current with POR, LVD, and Sleep timer | Vdd $\leq$ 3.0V, T <sub>A</sub> = 25 °C, I/O regulator turned off                      | _    | 1.1 | 1.5 | μΑ    |

| I <sub>SB0</sub>      | Deep sleep current                             | Vdd $\leq$ 3.0 V, T <sub>A</sub> = 25 °C, I/O regulator turned off                     | _    | 0.1 | _   | μΑ    |

Notes

When Vdd remains in the range from 1.71 V to 1.9 V for more than 50 µsec, the slew rate when moving from the 1.71 V to 1.9 V range to greater than 2 V must be slower than 1 V/500 µsec to avoid triggering POR. The only other restriction on slew rates for any other voltage range or transition is the SR<sub>POWER\_UP</sub> parameter.

If powering down in standby sleep mode, to properly detect and recover from a VDD brown out condition any of the following actions must be taken:

Bring the device out of sleep before powering down.

□ Assure that VDD falls below 100 mV before powering backup.

□ Set the No Buzz bit in the OSC\_CR0 register to keep the voltage monitoring circuit powered during sleep.

Increase the buzz rate to assure that the falling edge of VDD is captured. The rate is configured through the PSSDC bits in the SLP\_CFG register. For the referenced registers, refer to the enCoRe V Technical Reference Manual. In deep sleep mode, additional low power voltage monitoring circuitry allows VDD brown out conditions to be detected for edge rates slower than 1 V/ms.

## DC General Purpose I/O Specifications [7]

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 1.71 V to 3.6 V and 0 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C. Typical parameters apply to 3.3 V at 25 °C. These are for design guidance only.

| Table 10. | 3.0 V to | 3.6 V DC GPI | O Specifications |

|-----------|----------|--------------|------------------|

|-----------|----------|--------------|------------------|

| Symbol            | Description                                                                       | Conditions                                                                                                                                                                                  | Min       | Тур   | Max  | Units |

|-------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|------|-------|

| R <sub>PU</sub>   | Pull-up resistor                                                                  | -                                                                                                                                                                                           | 4         | 5.6   | 8    | kΩ    |

| V <sub>OH1</sub>  | High output voltage<br>Port 2 or 3 pins                                           | IOH $\leq$ 10 µA, maximum of 10 mA source current in all I/Os                                                                                                                               | Vdd – 0.2 | _     | -    | V     |

| V <sub>OH2</sub>  | High output voltage<br>Port 2 or 3 pins                                           | IOH = 1 mA, maximum of 20 mA source current in all I/Os                                                                                                                                     | Vdd – 0.9 | -     | -    | V     |

| V <sub>OH3</sub>  | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>disabled for Port 1 | IOH < 10 μA, maximum of 10 mA source<br>current in all I/Os                                                                                                                                 | Vdd – 0.2 | -     | _    | V     |

| V <sub>OH4</sub>  | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>disabled for Port 1 | IOH = 5 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                  | Vdd – 0.9 | -     | _    | V     |

| V <sub>OH5</sub>  | High output voltage<br>Port 1 pins with LDO regulator enabled<br>for 3 V out      | IOH < 10 $\mu$ A, Vdd > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                                          | 2.85      | 3.00  | 3.3  | V     |

| V <sub>OH6</sub>  | High output voltage<br>Port 1 pins with LDO regulator enabled<br>for 3 V out      | IOH = 5 mA, Vdd > 3.1 V, maximum of<br>20 mA source current in all I/Os                                                                                                                     | 2.20      | -     | _    | V     |

| V <sub>OH7</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V<br>out              | IOH < 10 $\mu$ A, Vdd > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                                  | 2.35      | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V<br>out              | IOH = 2 mA, Vdd > 2.7 V, maximum of<br>20 mA source current in all I/Os                                                                                                                     | 1.90      | -     | _    | V     |

| V <sub>OH9</sub>  | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out              | IOH < 10 $\mu$ A, Vdd > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                                  | 1.60      | 1.80  | 2.1  | V     |

| V <sub>OH10</sub> | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out              | IOH = 1 mA, Vdd > 2.7 V, maximum of<br>20 mA source current in all I/Os                                                                                                                     | 1.20      | -     | _    | V     |

| V <sub>OL</sub>   | Low output voltage                                                                | IOL = 25 mA, Vdd > 3.3 V, maximum of<br>60 mA sink current on even port pins (for<br>example, P0[2] and P1[4]) and 60 mA sink<br>current on odd port pins (for example,<br>P0[3] and P1[5]) | -         | -     | 0.75 | V     |

| V <sub>IL</sub>   | Input low voltage                                                                 | -                                                                                                                                                                                           | -         | -     | 0.80 | V     |

| $V_{IH}$          | Input high voltage                                                                | -                                                                                                                                                                                           | 2.00      | _     | _    | V     |

| $V_{H}$           | Input hysteresis voltage                                                          | -                                                                                                                                                                                           | _         | 80    | -    | mV    |

| Ι <sub>ΙL</sub>   | Input leakage (absolute value)                                                    | _                                                                                                                                                                                           | -         | 0.001 | 1    | μΑ    |

| C <sub>PIN</sub>  | Pin capacitance                                                                   | Package and pin dependent<br>Temp = 25 °C                                                                                                                                                   | 0.5       | 1.7   | 5    | pF    |

7. Errata: P1[3], P1[6], and P1[7] pins are susceptible to latch up when the I/O sink current exceeds 25 mA per pin on these pins. Add a series resistor > 300  $\Omega$  to P1[3], P1[6], and P1[7] pins to restrict current to within latch up limits. For more information please refer to "Errata" on page 33.

Note

### ADC Electrical Specifications

## Table 13.ADC User Module Electrical Specifications

| Symbol                 | Description                  | Conditions                                                                                     | Min                       | Тур                       | Max                       | Units |

|------------------------|------------------------------|------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input                  |                              |                                                                                                |                           | •                         | •                         |       |

| V <sub>IN</sub>        | Input voltage range          | -                                                                                              | 0                         | -                         | VREFADC                   | V     |

| C <sub>IIN</sub>       | Input capacitance            | -                                                                                              |                           | -                         | 5                         | pF    |

| R <sub>IN</sub>        | Input resistance             | Equivalent switched cap input resistance for 8-, 9-, or 10-bit resolution                      | 1/(500fF ×<br>data clock) | 1/(400fF ×<br>data clock) | 1/(300fF ×<br>data clock) | Ω     |

| Reference              |                              |                                                                                                | •                         | •                         |                           | •     |

| V <sub>REFADC</sub>    | ADC reference voltage        | -                                                                                              | 1.14                      | -                         | 1.26                      | V     |

| <b>Conversion Rate</b> | <b>)</b>                     | •                                                                                              | 1                         |                           |                           |       |

| F <sub>CLK</sub>       | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications for accuracy | 2.25                      | -                         | 6                         | MHz   |

| S8                     | 8-bit sample rate            | Data Clock set to 6 MHz.<br>Sample Rate = 0.001/<br>(2^Resolution/Data Clock)                  | -                         | _                         | _                         | ksps  |

| S10                    | 10-bit sample rate           | Data Clock set to 6 MHz.<br>Sample Rate = 0.001/<br>(2^Resolution/Data Clock)                  | -                         | 5.859                     | _                         | ksps  |

| DC Accuracy            |                              |                                                                                                |                           |                           |                           |       |

| RES                    | Resolution                   | Can be set to 8-, 9-, or 10-bit                                                                | 8                         | -                         | 10                        | bits  |

| DNL                    | Differential nonlinearity    | -                                                                                              | -1                        | -                         | +2                        | LSB   |

| INL                    | Integral nonlinearity        | -                                                                                              | -2                        | -                         | +2                        | LSB   |

| E <sub>Offset</sub>    | Offset error                 | 8-bit resolution                                                                               | 0                         | 3.2                       | 19.2                      | LSB   |

|                        |                              | 10-bit resolution                                                                              | 0                         | 12.8                      | 76.8                      | LSB   |

| E <sub>gain</sub>      | Gain error                   | For any resolution                                                                             | -5                        | -                         | +5                        | %FSR  |

| Power                  |                              | •                                                                                              |                           | •                         | •                         | •     |

| I <sub>ADC</sub>       | Operating current            | -                                                                                              | _                         | 2.1                       | 2.6                       | mA    |

| PSRR                   | Power supply rejection ratio | PSRR (Vdd > 3.0 V)                                                                             | _                         | 24                        | -                         | dB    |

|                        |                              | PSRR (Vdd < 3.0 V)                                                                             | -                         | 30                        | -                         | dB    |

### **AC Electrical Characteristics**

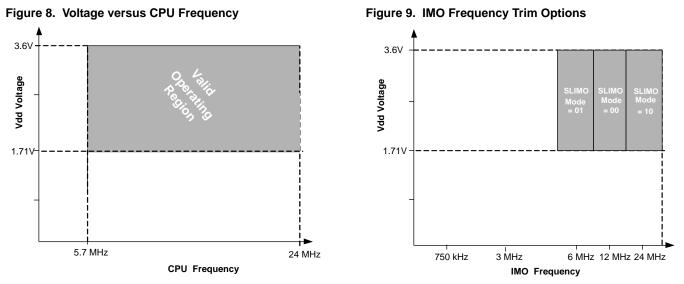

### AC Chip Level Specifications

Table 16 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

### Table 16. AC Chip Level Specifications

| Symbol                 | Description                                                 | Conditions                                            | Min  | Тур | Max  | Units |

|------------------------|-------------------------------------------------------------|-------------------------------------------------------|------|-----|------|-------|

| F <sub>CPU</sub>       | Processing frequency                                        |                                                       | 5.7  | -   | 25.2 | MHz   |

| F <sub>32K1</sub>      | Internal low speed oscillator<br>frequency                  | Trimmed for 3.3 V operation using factory trim values | 19   | 32  | 50   | kHz   |

| F <sub>32K_U</sub>     | Internal low speed oscillator<br>(ILO) untrimmed frequency) | _                                                     | 13   | 32  | 82   | kHz   |

| F <sub>32K2</sub>      | Internal low speed oscillator<br>frequency                  | Untrimmed                                             | 13   | 32  | 82   | kHz   |

| F <sub>IMO24</sub>     | Internal main oscillator stability<br>for 24 MHz ± 5%       | -                                                     | 22.8 | 24  | 25.2 | MHz   |

| F <sub>IMO12</sub>     | Internal main oscillator stability for 12 MHz               | -                                                     | 11.4 | 12  | 12.6 | MHz   |

| F <sub>IMO6</sub>      | Internal main oscillator stability for 6 MHz                | _                                                     | 5.7  | 6.0 | 6.3  | MHz   |

| DCIMO                  | Duty Cycle of IMO                                           | -                                                     | 40   | 50  | 60   | %     |

| DC <sub>ILO</sub>      | Internal low speed oscillator duty cycle                    | -                                                     | 40   | 50  | 60   | %     |

| SR <sub>POWER_UP</sub> | Power supply slew rate                                      | -                                                     | -    | -   | 250  | V/ms  |

| T <sub>XRST</sub>      | External reset pulse width at power up                      | After supply voltage is valid                         | 1    | _   | _    | ms    |

| T <sub>XRST2</sub>     | External reset pulse width after power up <sup>[17]</sup>   | Applies after part has booted                         | 10   | -   | -    | μS    |

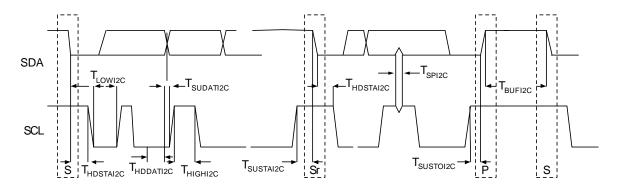

### AC I<sup>2</sup>C Specifications

Table 20 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 20. AC Characteristics of the I<sup>2</sup>C SDA and SCL Pins

| Symbol                | Description                                                                                  | Standar | rd Mode | Fast                | Units |       |

|-----------------------|----------------------------------------------------------------------------------------------|---------|---------|---------------------|-------|-------|

| Symbol                | Description                                                                                  | Min     | Max     | Min                 | Max   | Units |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                          | 0       | 100     | 0                   | 400   | kHz   |

| T <sub>HDSTAI2C</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4.0     | -       | 0.6                 | -     | μS    |

| T <sub>LOWI2C</sub>   | LOW period of the SCL clock                                                                  | 4.7     | -       | 1.3                 | -     | μS    |

| T <sub>HIGHI2C</sub>  | HIGH period of the SCL clock                                                                 | 4.0     | -       | 0.6                 | -     | μs    |

| T <sub>SUSTAI2C</sub> | Setup Time for a Repeated START condition                                                    | 4.7     | -       | 0.6                 | -     | μS    |

| T <sub>HDDATI2C</sub> | Data hold time                                                                               | 0       | -       | 0                   | -     | μS    |

| T <sub>SUDATI2C</sub> | Data setup time                                                                              | 250     | -       | 100 <sup>(18)</sup> | -     | ns    |

| T <sub>SUSTOI2C</sub> | Setup time for STOP condition                                                                | 4.0     | -       | 0.6                 | -     | μS    |

| T <sub>BUFI2C</sub>   | Bus free time between a STOP and START condition                                             | 4.7     | -       | 1.3                 | -     | μS    |

| T <sub>SPI2C</sub>    | Pulse width of spikes are suppressed by the input filter                                     | _       | _       | 0                   | 50    | ns    |

## Figure 12. Definition of Timing for Fast/Standard Mode on the I<sup>2</sup>C Bus

Note

<sup>18.</sup> A fast mode I2C bus device can be used in a standard mode I2C bus system, but the requirement t<sub>SU;DAT</sub> Š 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the standard mode I2C bus specification) before the SCL line is released.

## Table 21. SPI Master AC Specifications

| Symbol                | Description             | Conditions                                                               | Min       | Тур | Max    | Units |

|-----------------------|-------------------------|--------------------------------------------------------------------------|-----------|-----|--------|-------|

| F <sub>SCLK</sub>     | SCLK clock frequency    | $\begin{array}{c} V_{DD} \geq 2.4 \ V \\ V_{DD} \ < 2.4 \ V \end{array}$ | -         | -   | 6<br>3 | MHz   |

| DC                    | SCLK duty cycle         | -                                                                        | -         | 50  | _      | %     |

| T <sub>SETUP</sub>    | MISO to SCLK setup time | $\begin{array}{c} V_{DD} \geq 2.4 \ V \\ V_{DD} < 2.4 \ V \end{array}$   | 60<br>100 | -   | _      | ns    |

| T <sub>HOLD</sub>     | SCLK to MISO hold time  | -                                                                        | 40        | -   | _      | ns    |

| T <sub>OUT_VAL</sub>  | SCLK to MOSI valid time | -                                                                        | -         | -   | 40     | ns    |

| T <sub>OUT_HIGH</sub> | MOSI high time          | _                                                                        | 40        | -   | _      | ns    |

## Table 22.SPI Slave AC Specifications

| Symbol                 | Description                    | Conditions                                                             | Min    | Тур | Max     | Units |

|------------------------|--------------------------------|------------------------------------------------------------------------|--------|-----|---------|-------|

| F <sub>SCLK</sub>      | SCLK clock frequency           | $\begin{array}{c} V_{DD} \geq 2.4 \ V \\ V_{DD} < 2.4 \ V \end{array}$ | -      | _   | 12<br>6 | MHz   |

| T <sub>LOW</sub>       | SCLK low time                  | -                                                                      | 41.67  | -   | -       | ns    |

| T <sub>HIGH</sub>      | SCLK high time                 | -                                                                      | 41.67  | -   | -       | ns    |

| T <sub>SETUP</sub>     | MOSI to SCLK setup time        | -                                                                      | 30     | -   | -       | ns    |

| T <sub>HOLD</sub>      | SCLK to MOSI hold time         | -                                                                      | 50     | -   | -       | ns    |

| T <sub>SS_MISO</sub>   | SS high to MISO valid          | -                                                                      | -      | -   | 153     | ns    |

| T <sub>SCLK_MISO</sub> | SCLK to MISO valid             | -                                                                      | -      | -   | 125     | ns    |

| T <sub>SS_HIGH</sub>   | SS high time                   | -                                                                      | -      | -   | 50      | ns    |

| T <sub>SS_CLK</sub>    | Time from SS low to first SCLK | -                                                                      | 2/SCLK | -   | -       | ns    |

| T <sub>CLK_SS</sub>    | Time from last SCLK to SS high | -                                                                      | 2/SCLK | -   | _       | ns    |

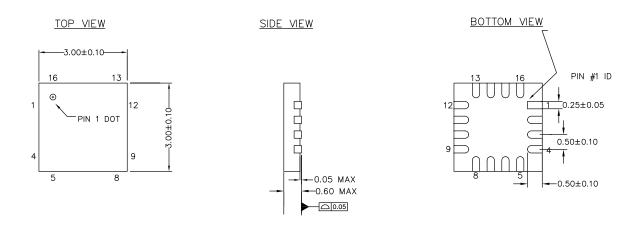

## Package Diagram

This section illustrates the packaging specifications for the enCoRe V LV device, along with the thermal impedances for each package. **Important Note** Emulation tools may require a larger area on the target PCB than the chip's footprint. For a detailed description of the enCoRe V LV emulation tools and their dimensions, refer to the development kit.

### **Packaging Dimensions**

Figure 13. 16-pin Chip-On-Lead (3 × 3 × 0.6 mm) LG16A/LD16A (Sawn) Package Outline, 001-09116

NOTES

- 1. REFERENCE JEDEC # MO-220

- 2. ALL DIMENSIONS ARE IN MILLIMETERS

001-09116 \*I

## **Package Handling**

Some IC packages require baking before they are soldered onto a PCB to remove moisture that may have been absorbed after leaving the factory. A label on the package has details about the actual bake temperature and the minimum bake time to remove this moisture. The maximum bake time is the aggregate time that the parts exposed to the bake temperature. Exceeding this exposure may degrade device reliability.

### Table 23.Package Handling

| Parameter | Description      | Minimum           | Typical | Maximum           | Unit  |

|-----------|------------------|-------------------|---------|-------------------|-------|

| TBAKETEMP | Bake Temperature | -                 | 125     | See package label | °C    |

| TBAKETIME | Bake Time        | See package label | -       | 72                | hours |

### **Thermal Impedances**

| Package                | Typical θ <sub>JA</sub> <sup>(19)</sup> |

|------------------------|-----------------------------------------|

| 16 QFN                 | 32.69 °C/W                              |

| 32 QFN <sup>(20)</sup> | 19.51 °C/W                              |

| 48 QFN <sup>(20)</sup> | 17.68 °C/W                              |

### **Capacitance on Crystal Pins**

Table 24. Typical Package Capacitance on Crystal Pins

| Package | Package Capacitance |

|---------|---------------------|

| 32 QFN  | 3.2 pF              |

| 48 QFN  | 3.3 pF              |

### Solder Reflow Peak Temperature

Following is the minimum solder reflow peak temperature to achieve good solderability.

| Package | Minimum Peak Temperature <sup>(21)</sup> | Maximum Peak Temperature |

|---------|------------------------------------------|--------------------------|

| 16 QFN  | 240 °C                                   | 260 °C                   |

| 32 QFN  | 240 °C                                   | 260 °C                   |

| 48 QFN  | 240 °C                                   | 260 °C                   |

<sup>19.</sup>  $T_J = T_A + Power x \theta_{JA}$ . 20. To achieve the thermal impedance specified for the package, solder the center thermal pad to the PCB ground plane.

<sup>21.</sup> Higher temperatures may be required based on the solder melting point. Typical temperatures for solder are 220 ± 5 °C with Sn-Pb or 245 ± 5 °C with Sn-Ag-Cu paste. Refer to the solder manufacturer specifications.

## **Ordering Information**

| Ordering Code     | Package Information                           | Flash | SRAM | No. of GPIOs | Target Applications            |  |

|-------------------|-----------------------------------------------|-------|------|--------------|--------------------------------|--|

| CY7C60413-16LKXC  | 16-Pin QFN<br>(3x3 mm)                        | 8 K   | 1 K  | 13           | Feature-rich wireless mouse    |  |

| CY7C64013-16LKXCT | 16-Pin QFN - (Tape and Reel)<br>(3X3 mm)      | 8 K   | 1 K  | 13           | Feature-rich wireless mouse    |  |

| CY7C60445-32LQXC  | 32-Pin QFN<br>(5x5x0.55 mm)                   | 16 K  | 1 K  | 28           | Feature-rich wireless mouse    |  |

| CY7C60445-32LQXCT | 32-Pin QFN - (Tape and Reel)<br>(5x5x0.55 mm) | 16 K  | 1 K  | 28           | Feature-rich wireless mouse    |  |

| CY7C60455-48LTXC  | 48-Pin QFN<br>(7x7x0.9 mm)                    | 16 K  | 1 K  | 36           | Mid-tier wireless keyboard     |  |

| CY7C60455-48LTXCT | 48-Pin QFN - (Tape and Reel)<br>(7x7x0.9 mm)  | 16 K  | 1 K  | 36           | Mid-tier wireless keyboard     |  |

| CY7C60456-48LTXC  | 48-Pin QFN<br>(7x7x0.9 mm)                    | 32 K  | 2 K  | 36           | Feature-rich wireless keyboard |  |

| CY7C60456-48LTXCT | 48-Pin QFN - (Tape and Reel)<br>(7x7x0.9 mm)  | 32 K  | 2 K  | 36           | Feature-rich wireless keyboard |  |

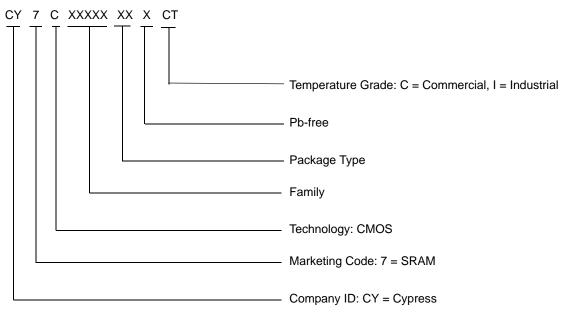

## **Ordering Code Definitions**

## Errata

This section describes the errata for the enCoRe V – CY7C643xx and enCoRe V LV – CY7C604xx. Details include errata trigger conditions, scope of impact, available workaround, and silicon revision applicability. Contact your local Cypress Sales Representative if you have questions.

Contact your local Cypress Gales Representative if you have que

### CY7C604xx Errata Summary

The following Errata item applies to the CY7C643xx and CY7C604xx data sheets.

1. Latch up susceptibility when maximum I/O sink current exceeded

- PROBLEM DEFINITION

- P1[3], P1[6], and P1[7] pins are susceptible to latch up when the I/O sink current exceeds 25 mA per pin on these pins.

- PARAMETERS AFFECTED LU – Latch up current. Per JESD78A, the maximum allowable latch up current per pin is 100 mA. Cypress internal specification is 200 mA latch up current limit.

- TRIGGER CONDITIONS

Latch up occurs when both the following conditions are met:

- A. The offending I/O is externally connected to a voltage higher than the I/O high state, causing a current to flow into the pin that exceeds 25 mA.

- B. A Port1 I/O (P1[1], P1[4], and P1[5] respectively) adjacent to the offending I/O is connected to a voltage lower than the I/O low state. This causes a signal that drops below Vss (signal undershoot) and a current greater than 200 mA to flow out of the pin.

- SCOPE OF IMPACT

The trigger conditions outlined in this item exceed the maximum ratings specified in the CY7C643xx and CY7C604xx data sheets.

### WORKAROUND

Add a series resistor > 300  $\Omega$  to P1[3], P1[6], and P1[7] pins to restrict current to within latch up limits.

FIX STATUS

This issue will be corrected in the next new silicon revision.

# **Document History Page**

|      | t Title: CY70<br>t Number: 0 |                    | oRe™ V Low '       | Voltage Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. | ECN No.                      | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| **   | 626516                       | TYJ                | See ECN            | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *A   | 735721                       | TYJ / ARI          | See ECN            | Added new block diagram, replaced TBDs, corrected values, updated pinout information, changed part number to reflect new specifications.                                                                                                                                                                                                                                                                                                                                                                   |

| *В   | 1120504                      | ARI                | See ECN            | Corrected the description to pin 29 on Table 1, the Typ/Max values for I <sub>SB0</sub> on<br>the DC chip-level specifications, and the Min voltage value for Vdd <sub>IWRITE</sub> in the<br>DC Programming Specifications table.<br>Corrected Flash Write Endurance minimum value in the DC Programming<br>Specifications table.<br>Corrected the Flash Erase Time max value and the Flash Block Write Time<br>max value in the AC Programming Specifications table.<br>Implemented new latest template. |

| *C   | 1225864                      | AESA / ARI         | See ECN            | Corrected the description to pin 13, 29 on Table 1 and 22,44 on Table 2.<br>Added sections Register Reference, Register Conventions and Register<br>Mapping Tables. Corrected Max values on the DC Chip-Level Specifications<br>table.                                                                                                                                                                                                                                                                     |

| *D   | 1446763                      | AESA               | See ECN            | Changed T <sub>ERASEB</sub> parameter, max value to 18ms in Table 13, AC Programming Specification.                                                                                                                                                                                                                                                                                                                                                                                                        |

| *E   | 1639963                      | AESA               | See ECN            | Post to www.cypress.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *F   | 2138889                      | TYJ/<br>PYRS       | See ECN            | Updated Ordering Code table:<br>- Ordering code changed for 32-QFN package: From -32LKXC to -32LTXC<br>- Added a new package type – "LTXC" for 48-QFN<br>- Included Tape and Reel ordering code for 32-QFN and 48-QFN packages<br>Changed active current values at 24, 12 and 6MHz in table "DC Chip-Level<br>Specifications"<br>- IDD24: 2.15 to 3.1mA<br>- IDD12: 1.45 to 2.0mA<br>- IDD6: 1.1 to 1.5mA<br>Added information on using P1[0] and P1[1] as the I2C interface during POR<br>or reset events |

# Document History Page (continued)