# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M3                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                           |

| Number of I/O              | 83                                                                        |

| Program Memory Size        | 1MB (1M × 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                              |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg980f1024-qfp100t |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.1.11 TFT Direct Drive

The EBI contains a TFT controller which can drive a TFT via a 565 RGB interface. The TFT controller supports programmable display and port sizes and offers accurate control of frequency and setup and hold timing. Direct Drive is supported for TFT displays which do not have their own frame buffer. In that case TFT Direct Drive can transfer data from either on-chip memory or from an external memory device to the TFT at low CPU load. Automatic alpha-blending and masking is also supported for transfers through the EBI interface.

### 2.1.12 Universal Serial Bus Controller (USB)

The USB is a full-speed USB 2.0 compliant OTG host/device controller. The USB can be used in Device, On-the-go (OTG) Dual Role Device or Host-only configuration. In OTG mode the USB supports both Host Negotiation Protocol (HNP) and Session Request Protocol (SRP). The device supports both full-speed (12MBit/s) and low speed (1.5MBit/s) operation. The USB device includes an internal dedicated Descriptor-Based Scatter/Gather DMA and supports up to 6 OUT endpoints and 6 IN endpoints, in addition to endpoint 0. The on-chip PHY includes all OTG features, except for the voltage booster for supplying 5V to VBUS when operating as host.

### 2.1.13 Inter-Integrated Circuit Interface (I2C)

The  $I^2C$  module provides an interface between the MCU and a serial  $I^2C$ -bus. It is capable of acting as both a master and a slave, and supports multi-master buses. Both standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates all the way from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also provided to allow implementation of an SMBus compliant system. The interface provided to software by the  $I^2C$  module, allows both fine-grained control of the transmission process and close to automatic transfers. Automatic recognition of slave addresses is provided in all energy modes.

# 2.1.14 Universal Synchronous/Asynchronous Receiver/Transmitter (US-ART)

The Universal Synchronous Asynchronous serial Receiver and Transmitter (USART) is a very flexible serial I/O module. It supports full duplex asynchronous UART communication as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with ISO7816 SmartCards, IrDA and I2S devices.

### 2.1.15 Pre-Programmed USB/UART Bootloader

The bootloader presented in application note AN0042 is pre-programmed in the device at factory. The bootloader enables users to program the EFM32 through a UART or a USB CDC class virtual UART without the need for a debugger. The autobaud feature, interface and commands are described further in the application note.

### 2.1.16 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous serial Receiver and Transmitter (UART) is a very flexible serial I/O module. It supports full- and half-duplex asynchronous UART communication.

# 2.1.17 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

| Symbol                | Parameter                                                                         | Condition                                                                         | Min                  | Тур                 | Мах                 | Unit |

|-----------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|---------------------|---------------------|------|

|                       |                                                                                   | Sourcing 20 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH      | 0.60V <sub>DD</sub>  |                     |                     | V    |

|                       |                                                                                   | Sourcing 20 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH       | 0.80V <sub>DD</sub>  |                     |                     | V    |

|                       |                                                                                   | Sinking 0.1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST    |                      | 0.20V <sub>DD</sub> |                     | V    |

|                       |                                                                                   | Sinking 0.1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST     |                      | 0.10V <sub>DD</sub> |                     | V    |

|                       |                                                                                   | Sinking 1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW         |                      | 0.10V <sub>DD</sub> |                     | V    |

| V <sub>IOOL</sub>     | Output low voltage<br>(Production test                                            | Sinking 1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW          |                      | 0.05V <sub>DD</sub> |                     | V    |

| VIOOL                 | condition = 3.0V,<br>DRIVEMODE =<br>STANDARD)                                     | Sinking 6 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD    |                      |                     | 0.30V <sub>DD</sub> | V    |

|                       |                                                                                   | Sinking 6 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD     |                      |                     | 0.20V <sub>DD</sub> | V    |

|                       |                                                                                   | Sinking 20 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH       |                      |                     | 0.35V <sub>DD</sub> | V    |

|                       |                                                                                   | Sinking 20 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH        |                      |                     | 0.20V <sub>DD</sub> | V    |

| I <sub>IOLEAK</sub>   | Input leakage cur-<br>rent                                                        | High Impedance IO connected to GROUND or V <sub>DD</sub>                          |                      | ±0.1                | ±40                 | nA   |

| R <sub>PU</sub>       | I/O pin pull-up resis-<br>tor                                                     |                                                                                   |                      | 40                  |                     | kOhm |

| R <sub>PD</sub>       | I/O pin pull-down re-<br>sistor                                                   |                                                                                   |                      | 40                  |                     | kOhm |

| R <sub>IOESD</sub>    | Internal ESD series resistor                                                      |                                                                                   |                      | 200                 |                     | Ohm  |

| t <sub>IOGLITCH</sub> | Pulse width of puls-<br>es to be removed<br>by the glitch sup-<br>pression filter |                                                                                   | 10                   |                     | 50                  | ns   |

|                       |                                                                                   | GPIO_Px_CTRL DRIVEMODE<br>= LOWEST and load capaci-<br>tance $C_L$ =12.5-25pF.    | 20+0.1C <sub>L</sub> |                     | 250                 | ns   |

| t <sub>IOOF</sub>     | Output fall time                                                                  | GPIO_Px_CTRL DRIVEMODE<br>= LOW and load capacitance<br>C <sub>L</sub> =350-600pF | 20+0.1C <sub>L</sub> |                     | 250                 | ns   |

| V <sub>IOHYST</sub>   | I/O pin hysteresis<br>(V <sub>IOTHR+</sub> - V <sub>IOTHR-</sub> )                | V <sub>DD</sub> = 1.98 - 3.8 V                                                    | 0.10V <sub>DD</sub>  |                     |                     | V    |

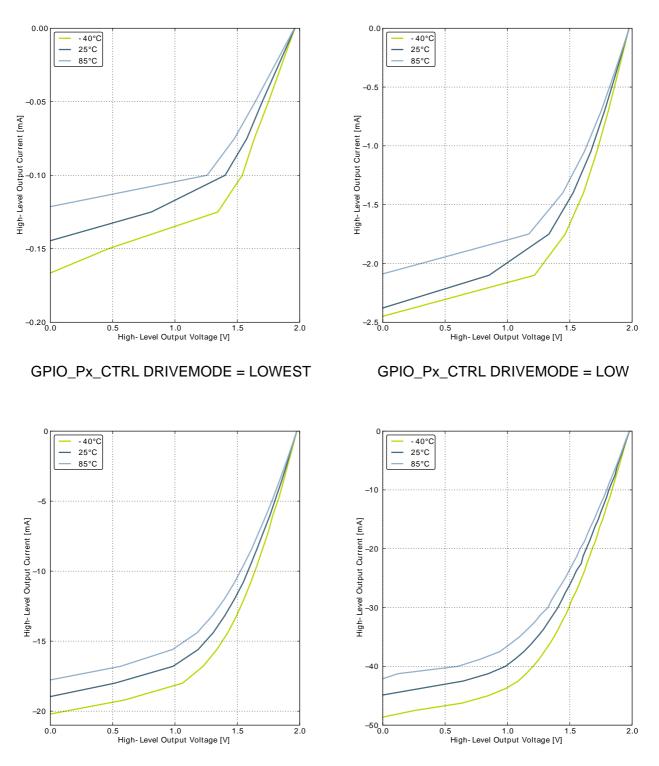

### Figure 3.5. Typical High-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

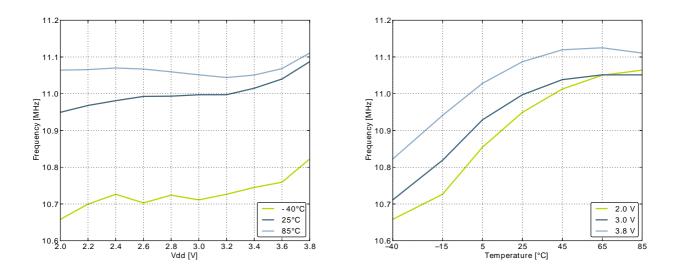

Figure 3.13. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature

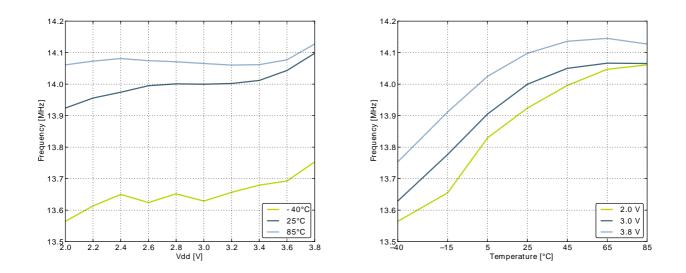

Figure 3.14. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature

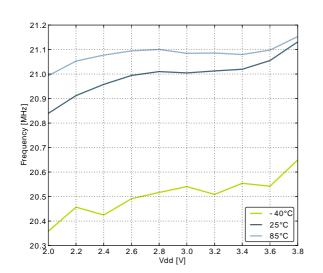

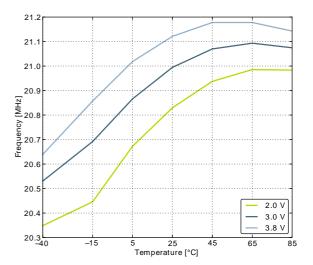

Figure 3.15. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

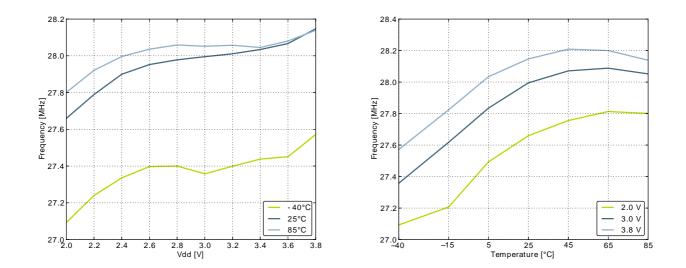

#### Figure 3.16. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

### 3.9.5 AUXHFRCO

#### Table 3.12. AUXHFRCO

| Symbol                              | Parameter                                              | Condition                      | Min               | Тур               | Max               | Unit   |

|-------------------------------------|--------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|--------|

|                                     |                                                        | 28 MHz frequency band          | 27.5              | 28.0              | 28.5              | MHz    |

|                                     |                                                        | 21 MHz frequency band          | 20.6              | 21.0              | 21.4              | MHz    |

|                                     | Oscillation frequen-                                   | 14 MHz frequency band          | 13.7              | 14.0              | 14.3              | MHz    |

|                                     | cy, V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =25°C | 11 MHz frequency band          | 10.8              | 11.0              | 11.2              | MHz    |

|                                     |                                                        | 7 MHz frequency band           | 6.48 <sup>1</sup> | 6.60 <sup>1</sup> | 6.72 <sup>1</sup> | MHz    |

|                                     |                                                        | 1 MHz frequency band           | 1.15 <sup>2</sup> | 1.20 <sup>2</sup> | 1.25 <sup>2</sup> | MHz    |

| t <sub>AUXHFRCO_settlir</sub>       | <sub>g</sub> Settling time after<br>start-up           | f <sub>AUXHFRCO</sub> = 14 MHz |                   | 0.6               |                   | Cycles |

| DC <sub>AUXHFRCO</sub>              | Duty cycle                                             | f <sub>AUXHFRCO</sub> = 14 MHz | 48.5              | 50                | 51                | %      |

| TUNESTEP <sub>AU&gt;</sub><br>HFRCO | Frequency step<br>for LSB change in<br>TUNING value    |                                |                   | 0.3 <sup>3</sup>  |                   | %      |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_AUXHFRCOCTRL register may be used to adjust the AUXHFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the AUXHFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

### 3.10.1 Typical performance

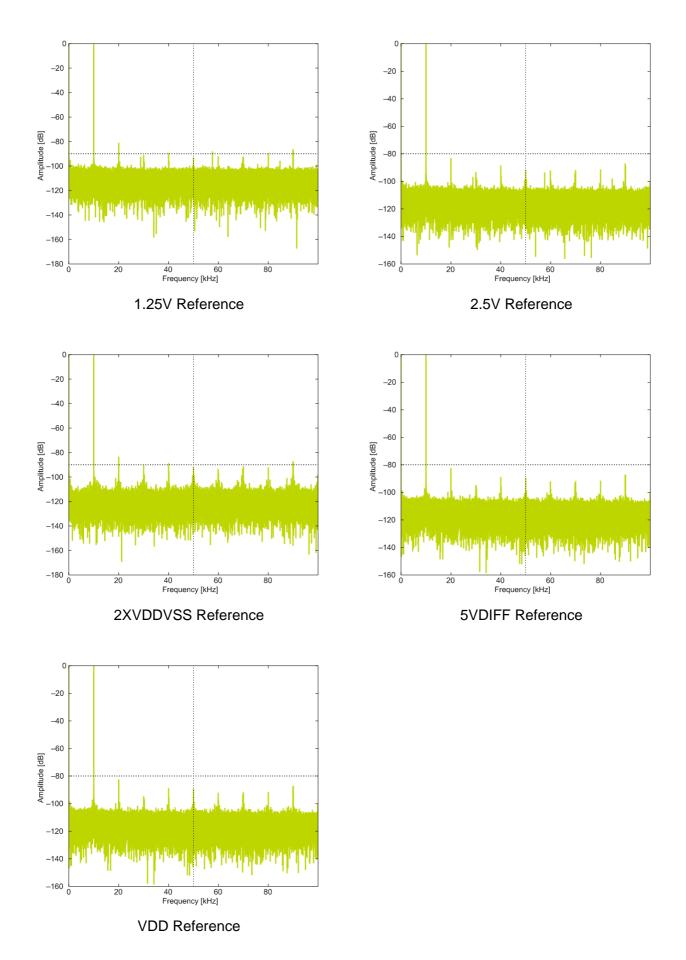

#### Figure 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

| Symbol                 | Parameter                               | Condition                                                                | Min | Тур | Max | Unit |

|------------------------|-----------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

|                        |                                         | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 58  |     | dB   |

|                        |                                         | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 59  |     | dB   |

|                        |                                         | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 57  |     | dB   |

|                        | Signal to Noise-                        | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 54  |     | dB   |

| SNDR <sub>DAC</sub>    | pulse Distortion Ra-<br>tio (SNDR)      | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 56  |     | dB   |

|                        |                                         | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 53  |     | dB   |

|                        |                                         | 500 kSamples/s, 12 bit, differential, $V_{DD}$ reference                 |     | 55  |     | dB   |

|                        | Spurious-Free<br>Dynamic<br>Range(SFDR) | 500 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |     | 62  |     | dBc  |

|                        |                                         | 500 kSamples/s, 12 bit, single ended, internal 2.5V reference            |     | 56  |     | dBc  |

| SFDR <sub>DAC</sub>    |                                         | 500 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |     | 61  |     | dBc  |

|                        |                                         | 500 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |     | 55  |     | dBc  |

|                        |                                         | 500 kSamples/s, 12 bit, differential, $V_{\text{DD}}$ reference          |     | 60  |     | dBc  |

| N/                     | Offeet veltege                          | After calibration, single ended                                          |     | 2   | 12  | mV   |

| V <sub>DACOFFSET</sub> | Offset voltage                          | After calibration, differential                                          |     | 2   |     | mV   |

| DNL <sub>DAC</sub>     | Differential non-lin-<br>earity         |                                                                          |     | ±1  |     | LSB  |

| INL <sub>DAC</sub>     | Integral non-lineari-<br>ty             |                                                                          |     | ±5  |     | LSB  |

| MC <sub>DAC</sub>      | No missing codes                        |                                                                          |     | 12  |     | bits |

<sup>1</sup>Measured with a static input code and no loading on the output.

# 3.12 Operational Amplifier (OPAMP)

The electrical characteristics for the Operational Amplifiers are based on simulations.

#### Table 3.16. OPAMP

| Symbol             | Parameter      | Condition                                                | Min | Тур | Max | Unit |

|--------------------|----------------|----------------------------------------------------------|-----|-----|-----|------|

| I <sub>OPAMP</sub> | Active Current | (OPA2)BIASPROG=0xF,<br>(OPA2)HALFBIAS=0x0, Unity<br>Gain |     | 350 | 405 | μA   |

|                    |                | (OPA2)BIASPROG=0x7,<br>(OPA2)HALFBIAS=0x1, Unity<br>Gain |     | 95  | 115 | μA   |

| Symbol | Parameter | Condition                                                                                                                                  | Min | Тур  | Max | Unit              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="0&lt;/td"><td></td><td>196</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 196  |     | μV <sub>RMS</sub> |

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="1&lt;/td"><td></td><td>229</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 229  |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=0</f<10>                                                                                      |     | 1230 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=1</f<10>                                                                                      |     | 2130 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=0</f<1>                                                                                        |     | 1630 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=1</f<1>                                                                                        |     | 2590 |     | μV <sub>RMS</sub> |

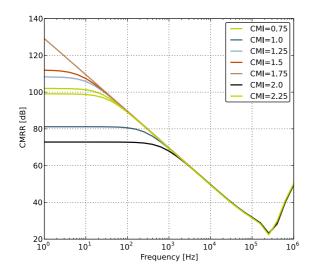

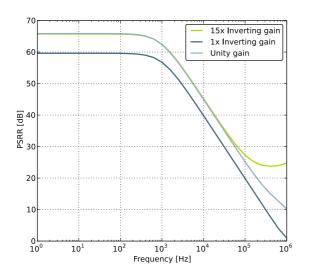

Figure 3.26. OPAMP Positive Power Supply Rejection Ratio

# 3.13 Analog Comparator (ACMP)

#### Table 3.17. ACMP

| Symbol                  | Parameter                                                   | Condition                                                                  | Min | Тур  | Max             | Unit |

|-------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------|-----|------|-----------------|------|

| V <sub>ACMPIN</sub>     | Input voltage range                                         |                                                                            | 0   |      | V <sub>DD</sub> | V    |

| V <sub>ACMPCM</sub>     | ACMP Common<br>Mode voltage range                           |                                                                            | 0   |      | V <sub>DD</sub> | V    |

|                         |                                                             | BIASPROG=0b0000, FULL-<br>BIAS=0 and HALFBIAS=1 in<br>ACMPn_CTRL register  |     | 0.1  | 0.6             | μA   |

| I <sub>ACMP</sub>       | Active current                                              | BIASPROG=0b1111, FULL-<br>BIAS=0 and HALFBIAS=0 in<br>ACMPn_CTRL register  |     | 2.87 | 12              | μΑ   |

|                         |                                                             | BIASPROG=0b1111, FULL-<br>BIAS=1 and HALFBIAS=0 in<br>ACMPn_CTRL register  |     | 250  | 520             | μΑ   |

| IACMPREF                | Current consump-<br>tion of internal volt-<br>age reference | Internal voltage reference off.<br>Using external voltage refer-<br>ence   |     | 0    |                 | μA   |

|                         |                                                             | Internal voltage reference                                                 |     | 5    |                 | μA   |

| V <sub>ACMPOFFSET</sub> | Offset voltage                                              | BIASPROG= 0b1010, FULL-<br>BIAS=0 and HALFBIAS=0 in<br>ACMPn_CTRL register | -12 | 0    | 12              | mV   |

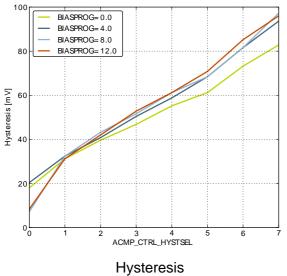

| V <sub>ACMPHYST</sub>   | ACMP hysteresis                                             | Programmable                                                               |     | 17   |                 | mV   |

|                         |                                                             | CSRESSEL=0b00 in<br>ACMPn_INPUTSEL                                         |     | 43   |                 | kOhm |

| D                       | Capacitive Sense                                            | CSRESSEL=0b01 in<br>ACMPn_INPUTSEL                                         |     | 78   |                 | kOhm |

| R <sub>CSRES</sub>      | Internal Resistance                                         | CSRESSEL=0b10 in<br>ACMPn_INPUTSEL                                         |     | 111  |                 | kOhm |

|                         |                                                             | CSRESSEL=0b11 in<br>ACMPn_INPUTSEL                                         |     | 145  |                 | kOhm |

| t <sub>ACMPSTART</sub>  | Startup time                                                |                                                                            |     |      | 10              | μs   |

The total ACMP current is the sum of the contributions from the ACMP and its internal voltage reference as given in Equation 3.1 (p. 43).  $I_{ACMPREF}$  is zero if an external voltage reference is used.

#### Total ACMP Active Current

$I_{ACMPTOTAL} = I_{ACMP} + I_{ACMPREF}$

(3.1)

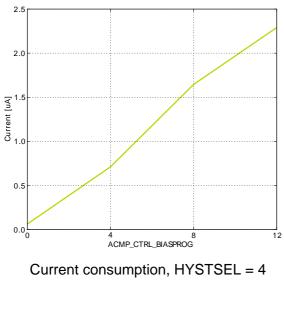

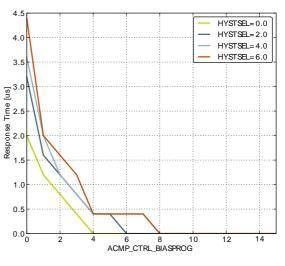

Figure 3.30. ACMP Characteristics, Vdd = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

Response time

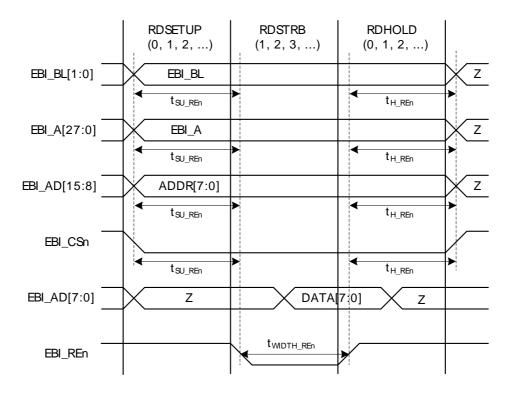

#### Figure 3.33. EBI Read Enable Related Output Timing

Table 3.21. EBI Read Enable Related Output Timing

| Symbol                       | Parameter                                                                                                  | Min                                                                 | Тур | Max | Unit |

|------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|------|

| t <sub>OH_REn 1234</sub>     | Output hold time, from trailing EBI_REn/<br>EBI_NANDREn edge to EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn invalid | -10.00 + (RDHOLD *<br>t <sub>HFCORECLK</sub> )                      |     |     | ns   |

| tosu_REn <sup>12345</sup>    | Output setup time, from EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading EBI_REn/EBI_NANDREn<br>edge    | -10.00 + (RDSETUP<br><sup>* t</sup> нғсопесік)                      |     |     | ns   |

| twiDTH_REn <sup>123456</sup> | EBI_REn pulse width                                                                                        | -9.00 + ((RD-<br>STRB+1) * t <sub>HFCORE-</sub><br><sub>CLK</sub> ) |     |     | ns   |

<sup>1</sup>Applies for all addressing modes (figure only shows D8A8. Output timing for EBI\_AD only applies to multiplexed addressing modes D8A24ALE and D16A16ALE)

<sup>2</sup>Applies for both EBI\_REn and EBI\_NANDREn (figure only shows EBI\_REn)

<sup>3</sup>Applies for all polarities (figure only shows active low signals)

$^4\text{Measurement}$  done at 10% and 90% of  $V_{\text{DD}}$  (figure shows 50% of  $_{\text{VDD}})$

<sup>5</sup>The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFRE=0. The leading edge of EBI\_REn can be moved to the right by setting HALFRE=1. This decreases the length of  $t_{WIDTH_REn}$  and increases the length of  $t_{OSU_REn}$  by 1/2 \*  $t_{HFCLKNODIV}$ .

<sup>6</sup>When page mode is used, RDSTRB is replaced by RDPA for page hits.

# **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32GG980.

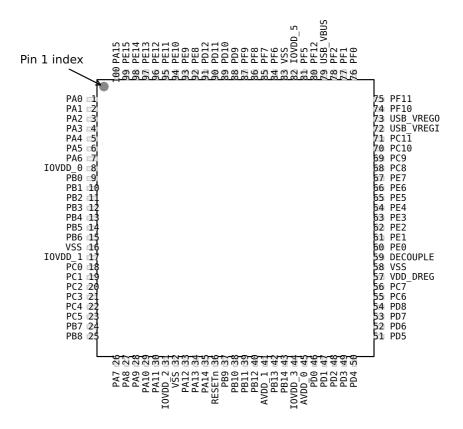

### 4.1 Pinout

The *EFM32GG980* pinout is shown in Figure 4.1 (p. 54) and Table 4.1 (p. 54). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32GG980 Pinout (top view, not to scale)

Table 4.1. Device Pinout

|       | QFP100 Pin#<br>and Name | Pin Alternate Functionality / Description |                 |                 |                           |                           |

|-------|-------------------------|-------------------------------------------|-----------------|-----------------|---------------------------|---------------------------|

| Pin # | Pin Name                | Analog                                    | EBI             | Timers          | Communication             | Other                     |

| 1     | PA0                     | LCD_SEG13                                 | EBI_AD09 #0/1/2 | TIM0_CC0 #0/1/4 | I2C0_SDA #0<br>LEU0_RX #4 | PRS_CH0 #0<br>GPIO_EM4WU0 |

| 2     | PA1                     | LCD_SEG14                                 | EBI_AD10 #0/1/2 | TIM0_CC1 #0/1   | I2C0_SCL #0               | CMU_CLK1 #0<br>PRS_CH1 #0 |

| 3     | PA2                     | LCD_SEG15                                 | EBI_AD11 #0/1/2 | TIM0_CC2 #0/1   |                           | CMU_CLK0 #0               |

|       | QFP100 Pin#<br>and Name |                            | Pin Altern      | ate Functionality / [         | Description                             |                                         |

|-------|-------------------------|----------------------------|-----------------|-------------------------------|-----------------------------------------|-----------------------------------------|

| Pin # | Pin Name                | Analog                     | EBI             | Timers                        | Communication                           | Other                                   |

| 60    | PE0                     |                            | EBI_A07 #0/1/2  | TIM3_CC0 #1<br>PCNT0_S0IN #1  | U0_TX #1<br>I2C1_SDA #2                 |                                         |

| 61    | PE1                     |                            | EBI_A08 #0/1/2  | TIM3_CC1 #1<br>PCNT0_S1IN #1  | U0_RX #1<br>I2C1_SCL #2                 |                                         |

| 62    | PE2                     | BU_VOUT                    | EBI_A09 #0      | TIM3_CC2 #1                   | U1_TX #3                                | ACMP0_O #1                              |

| 63    | PE3                     | BU_STAT                    | EBI_A10 #0      |                               | U1_RX #3                                | ACMP1_O #1                              |

| 64    | PE4                     | LCD_COM0                   | EBI_A11 #0/1/2  |                               | US0_CS #1                               |                                         |

| 65    | PE5                     | LCD_COM1                   | EBI_A12 #0/1/2  |                               | US0_CLK #1                              |                                         |

| 66    | PE6                     | LCD_COM2                   | EBI_A13 #0/1/2  |                               | US0_RX #1                               |                                         |

| 67    | PE7                     | LCD_COM3                   | EBI_A14 #0/1/2  |                               | US0_TX #1                               |                                         |

| 68    | PC8                     | ACMP1_CH0                  | EBI_A15 #0/1/2  | TIM2_CC0 #2                   | US0_CS #2                               | LES_CH8 #0                              |

| 69    | PC9                     | ACMP1_CH1                  | EBI_A09 #1/2    | TIM2_CC1 #2                   | US0_CLK #2                              | LES_CH9 #0<br>GPIO_EM4WU2               |

| 70    | PC10                    | ACMP1_CH2                  | EBI_A10 #1/2    | TIM2_CC2 #2                   | US0_RX #2                               | LES_CH10 #0                             |

| 71    | PC11                    | ACMP1_CH3                  | EBI_ALE #1/2    |                               | US0_TX #2                               | LES_CH11 #0                             |

| 72    | USB_VREGI               |                            |                 |                               |                                         |                                         |

| 73    | USB_VREGO               |                            |                 |                               |                                         |                                         |

| 74    | PF10                    |                            |                 |                               | U1_TX #1<br>USB_DM                      |                                         |

| 75    | PF11                    |                            |                 |                               | U1_RX #1<br>USB_DP                      |                                         |

| 76    | PF0                     |                            |                 | TIM0_CC0 #5<br>LETIM0_OUT0 #2 | US1_CLK #2<br>I2C0_SDA #5<br>LEU0_TX #3 | DBG_SWCLK #0/1/2/3                      |

| 77    | PF1                     |                            |                 | TIM0_CC1 #5<br>LETIM0_OUT1 #2 | US1_CS #2<br>I2C0_SCL #5<br>LEU0_RX #3  | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3       |

| 78    | PF2                     | LCD_SEG0                   | EBI_ARDY #0/1/2 | TIM0_CC2 #5                   | LEU0_TX #4                              | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4 |

| 79    | USB_VBUS                | USB 5.0 V VBUS input.      |                 |                               |                                         | _                                       |

| 80    | PF12                    |                            |                 |                               | USB_ID                                  |                                         |

| 81    | PF5                     | LCD_SEG3                   | EBI_REn #0/2    | TIM0_CDTI2 #2/5               | USB_VBUSEN #0                           | PRS_CH2 #1                              |

| 82    | IOVDD_5                 | Digital IO power supply 5. |                 | ·                             |                                         | -<br>-                                  |

| 83    | VSS                     | Ground.                    |                 |                               |                                         | -                                       |

| 84    | PF6                     | LCD_SEG24                  | EBI_BL0 #0/1/2  | TIM0_CC0 #2                   | U0_TX #0                                |                                         |

| 85    | PF7                     | LCD_SEG25                  | EBI_BL1 #0/1/2  | TIM0_CC1 #2                   | U0_RX #0                                |                                         |

| 86    | PF8                     | LCD_SEG26                  | EBI_WEn #1      | TIM0_CC2 #2                   |                                         | ETM_TCLK #1                             |

| 87    | PF9                     | LCD_SEG27                  | EBI_REn #1      |                               |                                         | ETM_TD0 #1                              |

| 88    | PD9                     | LCD_SEG28                  | EBI_CS0 #0/1/2  |                               |                                         |                                         |

| 89    | PD10                    | LCD_SEG29                  | EBI_CS1 #0/1/2  |                               |                                         |                                         |

| 90    | PD11                    | LCD_SEG30                  | EBI_CS2 #0/1/2  |                               |                                         |                                         |

| 91    | PD12                    | LCD_SEG31                  | EBI_CS3 #0/1/2  |                               |                                         |                                         |

| 92    | PE8                     | LCD_SEG4                   | EBI_AD00 #0/1/2 | PCNT2_S0IN #1                 |                                         | PRS_CH3 #1                              |

| 93    | PE9                     | LCD_SEG5                   | EBI_AD01 #0/1/2 | PCNT2_S1IN #1                 |                                         |                                         |

|       | QFP100 Pin#<br>and Name | Pin Alternate Functionality / Description |                 |             |                                        |                                            |  |  |

|-------|-------------------------|-------------------------------------------|-----------------|-------------|----------------------------------------|--------------------------------------------|--|--|

| Pin # | Pin Name                | Analog                                    | EBI             | Timers      | Communication                          | Other                                      |  |  |

| 94    | PE10                    | LCD_SEG6                                  | EBI_AD02 #0/1/2 | TIM1_CC0 #1 | US0_TX #0                              | BOOT_TX                                    |  |  |

| 95    | PE11                    | LCD_SEG7                                  | EBI_AD03 #0/1/2 | TIM1_CC1 #1 | US0_RX #0                              | LES_ALTEX5 #0<br>BOOT_RX                   |  |  |

| 96    | PE12                    | LCD_SEG8                                  | EBI_AD04 #0/1/2 | TIM1_CC2 #1 | US0_RX #3<br>US0_CLK #0<br>I2C0_SDA #6 | CMU_CLK1 #2<br>LES_ALTEX6 #0               |  |  |

| 97    | PE13                    | LCD_SEG9                                  | EBI_AD05 #0/1/2 |             | US0_TX #3<br>US0_CS #0<br>I2C0_SCL #6  | LES_ALTEX7 #0<br>ACMP0_O #0<br>GPIO_EM4WU5 |  |  |

| 98    | PE14                    | LCD_SEG10                                 | EBI_AD06 #0/1/2 | TIM3_CC0 #0 | LEU0_TX #2                             |                                            |  |  |

| 99    | PE15                    | LCD_SEG11                                 | EBI_AD07 #0/1/2 | TIM3_CC1 #0 | LEU0_RX #2                             |                                            |  |  |

| 100   | PA15                    | LCD_SEG12                                 | EBI_AD08 #0/1/2 | TIM3_CC2 #0 |                                        |                                            |  |  |

### **4.2 Alternate Functionality Pinout**

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in Table 4.2 (p. 58). The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

#### Note

Some functionality, such as analog interfaces, do not have alternate settings or a LOCA-TION bitfield. In these cases, the pinout is shown in the column corresponding to LOCA-TION 0.

| Alternate     |      |     | LOC | ATION |   |   |   |                                                           |  |  |

|---------------|------|-----|-----|-------|---|---|---|-----------------------------------------------------------|--|--|

| Functionality | 0    | 1   | 2   | 3     | 4 | 5 | 6 | Description                                               |  |  |

| ACMP0_CH0     | PC0  |     |     |       |   |   |   | Analog comparator ACMP0, channel 0.                       |  |  |

| ACMP0_CH1     | PC1  |     |     |       |   |   |   | Analog comparator ACMP0, channel 1.                       |  |  |

| ACMP0_CH2     | PC2  |     |     |       |   |   |   | Analog comparator ACMP0, channel 2.                       |  |  |

| ACMP0_CH3     | PC3  |     |     |       |   |   |   | Analog comparator ACMP0, channel 3.                       |  |  |

| ACMP0_CH4     | PC4  |     |     |       |   |   |   | Analog comparator ACMP0, channel 4.                       |  |  |

| ACMP0_CH5     | PC5  |     |     |       |   |   |   | Analog comparator ACMP0, channel 5.                       |  |  |

| ACMP0_CH6     | PC6  |     |     |       |   |   |   | Analog comparator ACMP0, channel 6.                       |  |  |

| ACMP0_CH7     | PC7  |     |     |       |   |   |   | Analog comparator ACMP0, channel 7.                       |  |  |

| ACMP0_O       | PE13 | PE2 | PD6 |       |   |   |   | Analog comparator ACMP0, digital output.                  |  |  |

| ACMP1_CH0     | PC8  |     |     |       |   |   |   | Analog comparator ACMP1, channel 0.                       |  |  |

| ACMP1_CH1     | PC9  |     |     |       |   |   |   | Analog comparator ACMP1, channel 1.                       |  |  |

| ACMP1_CH2     | PC10 |     |     |       |   |   |   | Analog comparator ACMP1, channel 2.                       |  |  |

| ACMP1_CH3     | PC11 |     |     |       |   |   |   | Analog comparator ACMP1, channel 3.                       |  |  |

| ACMP1_O       | PF2  | PE3 | PD7 |       |   |   |   | Analog comparator ACMP1, digital output.                  |  |  |

| ADC0_CH0      | PD0  |     |     |       |   |   |   | Analog to digital converter ADC0, input channel number 0. |  |  |

| ADC0_CH1      | PD1  |     |     |       |   |   |   | Analog to digital converter ADC0, input channel number 1. |  |  |

| ADC0_CH2      | PD2  |     |     |       |   |   |   | Analog to digital converter ADC0, input channel number 2. |  |  |

#### Table 4.2. Alternate functionality overview

### **EFM°32**

#### ...the world's most energy friendly microcontrollers

| Alternate     | LOCATION |      |      |      |     |     |   |                                                                                                               |  |  |  |

|---------------|----------|------|------|------|-----|-----|---|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Functionality | 0        | 1    | 2    | 3    | 4   | 5   | 6 | Description                                                                                                   |  |  |  |

| LES_CH7       | PC7      |      |      |      |     |     |   | LESENSE channel 7.                                                                                            |  |  |  |

| LES_CH8       | PC8      |      |      |      |     |     |   | LESENSE channel 8.                                                                                            |  |  |  |

| LES_CH9       | PC9      |      |      |      |     |     |   | LESENSE channel 9.                                                                                            |  |  |  |

| LES_CH10      | PC10     |      |      |      |     |     |   | LESENSE channel 10.                                                                                           |  |  |  |

| LES_CH11      | PC11     |      |      |      |     |     |   | LESENSE channel 11.                                                                                           |  |  |  |

| LETIM0_OUT0   | PD6      | PB11 | PF0  | PC4  |     |     |   | Low Energy Timer LETIM0, output channel 0.                                                                    |  |  |  |

| LETIM0_OUT1   | PD7      | PB12 | PF1  | PC5  |     |     |   | Low Energy Timer LETIM0, output channel 1.                                                                    |  |  |  |

| LEU0_RX       | PD5      | PB14 | PE15 | PF1  | PA0 |     |   | LEUART0 Receive input.                                                                                        |  |  |  |

| LEU0_TX       | PD4      | PB13 | PE14 | PF0  | PF2 |     |   | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |  |  |  |

| LEU1_RX       | PC7      | PA6  |      |      |     |     |   | LEUART1 Receive input.                                                                                        |  |  |  |

| LEU1_TX       | PC6      | PA5  |      |      |     |     |   | LEUART1 Transmit output. Also used as receive input in half duplex communication.                             |  |  |  |

| LFXTAL_N      | PB8      |      |      |      |     |     |   | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |  |  |  |

| LFXTAL_P      | PB7      |      |      |      |     |     |   | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |  |  |  |

| PCNT0_S0IN    |          | PE0  | PC0  | PD6  |     |     |   | Pulse Counter PCNT0 input number 0.                                                                           |  |  |  |

| PCNT0_S1IN    |          | PE1  | PC1  | PD7  |     |     |   | Pulse Counter PCNT0 input number 1.                                                                           |  |  |  |

| PCNT1_S0IN    | PC4      | PB3  |      |      |     |     |   | Pulse Counter PCNT1 input number 0.                                                                           |  |  |  |

| PCNT1_S1IN    | PC5      | PB4  |      |      |     |     |   | Pulse Counter PCNT1 input number 1.                                                                           |  |  |  |

| PCNT2_S0IN    | PD0      | PE8  |      |      |     |     |   | Pulse Counter PCNT2 input number 0.                                                                           |  |  |  |

| PCNT2_S1IN    | PD1      | PE9  |      |      |     |     |   | Pulse Counter PCNT2 input number 1.                                                                           |  |  |  |

| PRS_CH0       | PA0      |      |      |      |     |     |   | Peripheral Reflex System PRS, channel 0.                                                                      |  |  |  |

| PRS_CH1       | PA1      |      |      |      |     |     |   | Peripheral Reflex System PRS, channel 1.                                                                      |  |  |  |

| PRS_CH2       | PC0      | PF5  |      |      |     |     |   | Peripheral Reflex System PRS, channel 2.                                                                      |  |  |  |

| PRS_CH3       | PC1      | PE8  |      |      |     |     |   | Peripheral Reflex System PRS, channel 3.                                                                      |  |  |  |

| TIM0_CC0      | PA0      | PA0  | PF6  | PD1  | PA0 | PF0 |   | Timer 0 Capture Compare input / output channel 0.                                                             |  |  |  |

| TIM0_CC1      | PA1      | PA1  | PF7  | PD2  | PC0 | PF1 |   | Timer 0 Capture Compare input / output channel 1.                                                             |  |  |  |

| TIM0_CC2      | PA2      | PA2  | PF8  | PD3  | PC1 | PF2 |   | Timer 0 Capture Compare input / output channel 2.                                                             |  |  |  |

| TIM0_CDTI0    | PA3      |      |      |      | PC2 |     |   | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |  |  |  |

| TIM0_CDTI1    | PA4      |      |      |      | PC3 |     |   | Timer 0 Complimentary Deat Time Insertion channel 1.                                                          |  |  |  |

| TIM0_CDTI2    | PA5      |      | PF5  |      | PC4 | PF5 |   | Timer 0 Complimentary Deat Time Insertion channel 2.                                                          |  |  |  |

| TIM1_CC0      |          | PE10 | PB0  | PB7  | PD6 |     |   | Timer 1 Capture Compare input / output channel 0.                                                             |  |  |  |

| TIM1_CC1      |          | PE11 | PB1  | PB8  | PD7 |     |   | Timer 1 Capture Compare input / output channel 1.                                                             |  |  |  |

| TIM1_CC2      |          | PE12 | PB2  | PB11 |     |     |   | Timer 1 Capture Compare input / output channel 2.                                                             |  |  |  |

| TIM2_CC0      | PA8      | PA12 | PC8  |      |     |     |   | Timer 2 Capture Compare input / output channel 0.                                                             |  |  |  |

| TIM2_CC1      | PA9      | PA13 | PC9  |      |     |     |   | Timer 2 Capture Compare input / output channel 1.                                                             |  |  |  |

| TIM2_CC2      | PA10     | PA14 | PC10 |      |     |     |   | Timer 2 Capture Compare input / output channel 2.                                                             |  |  |  |

| TIM3_CC0      | PE14     | PE0  | 1    |      |     |     |   | Timer 3 Capture Compare input / output channel 0.                                                             |  |  |  |

| TIM3_CC1      | PE15     | PE1  |      |      |     |     |   | Timer 3 Capture Compare input / output channel 1.                                                             |  |  |  |

| TIM3_CC2      | PA15     | PE2  |      |      |     |     |   | Timer 3 Capture Compare input / output channel 2.                                                             |  |  |  |

| U0_RX         | PF7      | PE1  | PA4  |      |     |     |   | UART0 Receive input.                                                                                          |  |  |  |

#### Table 4.3. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin<br>9 | Pin<br>8 | Pin<br>7 | Pin<br>6 | Pin<br>5 | Pin<br>4 | Pin<br>3 | Pin<br>2 | Pin<br>1 | Pin<br>0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Port A | PA15      | PA14      | PA13      | PA12      | PA11      | PA10      | PA9      | PA8      | PA7      | PA6      | PA5      | PA4      | PA3      | PA2      | PA1      | PA0      |

| Port B | -         | PB14      | PB13      | PB12      | PB11      | PB10      | PB9      | PB8      | PB7      | PB6      | PB5      | PB4      | PB3      | PB2      | PB1      | PB0      |

| Port C | -         | -         | -         | -         | PC11      | PC10      | PC9      | PC8      | PC7      | PC6      | PC5      | PC4      | PC3      | PC2      | PC1      | PC0      |

| Port D | -         | -         | -         | PD12      | PD11      | PD10      | PD9      | PD8      | PD7      | PD6      | PD5      | PD4      | PD3      | PD2      | PD1      | PD0      |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9      | PE8      | PE7      | PE6      | PE5      | PE4      | PE3      | PE2      | PE1      | PE0      |

| Port F | -         | -         | -         | PF12      | PF11      | PF10      | PF9      | PF8      | PF7      | PF6      | PF5      | -        | -        | PF2      | PF1      | PF0      |

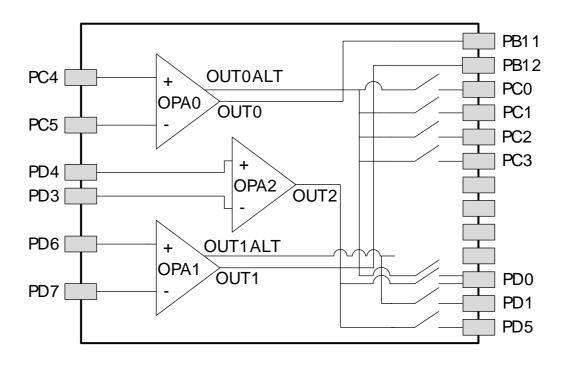

# 4.4 Opamp Pinout Overview

The specific opamp terminals available in EFM32GG980 is shown in Figure 4.2 (p. 66) .

#### Figure 4.2. Opamp Pinout

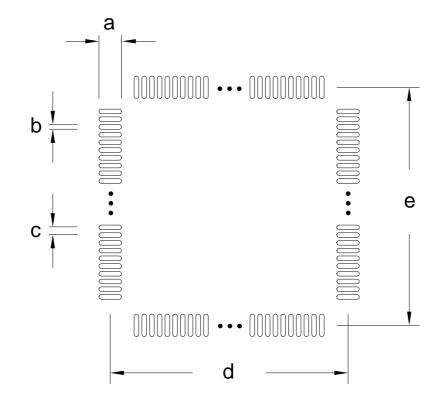

#### Figure 5.3. LQFP100 PCB Stencil Design

Table 5.3. QFP100 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| a      | 1.35      |

| b      | 0.20      |

| с      | 0.50      |

| d      | 15.40     |

| e      | 15.40     |

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see Figure 4.3 (p. 67) .

## **5.2 Soldering Information**

The latest IPC/JEDEC J-STD-020 recommendations for Pb-Free reflow soldering should be followed.

# **7 Revision History**

# 7.1 Revision 1.40

March 21st, 2016

Added clarification on conditions for INL<sub>ADC</sub> and DNL<sub>ADC</sub> parameters.

Reduced maximum and typical current consumption for all EM0 entries except 48 MHz in the Current Consumption table in the Electrical Characteristics section.

Increased maximum specifications for EM2 current, EM3 current, and EM4 current in the Current Consumption table in the Electrical Characteristics section.

Increased typical specification for EM2 and EM3 current at 85 C in the Current Consumption table in the Electrical Characteristics section.

Added EM2, EM3, and EM4 current consumption vs. temperature graphs.

Added a new EM2 entry and specified the existing specification is for EM0 for the BOD threshold on falling external supply voltage in the Power Management table in the Electrical Characteristics section.

Reduced maximum input leakage current in the GPIO table in the Electrical Characteristics section.

Added a maximum current consumption specification to the LFRCO table in the Electrical Characteristics section.

Added maximum specifications for the active current including references for two channels to the DAC table in the Electrical Characteristics section.

Increased the maximum specification for DAC offset voltage in the DAC table in the Electrical Characteristics section.

Increased the typical specifications for active current with FULLBIAS=1 and capacitive sense internal resistance in the ACMP table in the Electrical Characteristics section.

Added minimum and maximum specifications and updated the typical value for the VCMP offset voltage in the VCMP table in the Electrical Characteristics section.

Removed the maximum specification and reduced the typical value for hysteresis in the VCMP table in the Electrical Characteristics section.

Updated all graphs in the Electrical Characteristics section to display data for 2.0 V as the minimum voltage.

### 7.2 Revision 1.30

May 23rd, 2014

Removed "preliminary" markings

Updated HFRCO figures.

Corrected single power supply voltage minimum value from 1.85V to 1.98V.

Updated Current Consumption information.

Updated Power Management information.

# 7.10 Revision 0.91

March 21th, 2011

Added new alternative locations for EBI and SWO.

Added new USB Pin to pinout table.

Corrected slew rate data for Opamps.

## 7.11 Revision 0.90

February 4th, 2011

Initial preliminary release.

# A Disclaimer and Trademarks

# A.1 Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

# A.2 Trademark Information

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISO-modem®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.