Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status         Obsolete           Core Processor         HC08           Core Size         8-Bit           Speed         8MHz           Connectivity         LINbus, SCI, SPI           Peripherals         LVD, POR, PWM           Number of I/O         21           Program Memory Size         16KB (16K x 8)           Program Memory Type         FLASH           EEPROM Size         -           RAM Size         1K x 8           Voltage - Supply (Vcc/Vdd)         3V ~ 5.5V           Data Converters         A/D 8x10b           Oscillator Type         Internal           Operating Temperature         -40°C ~ 125°C (TA)           Mounting Type         Surface Mount           Package / Case         32-LQFP           Supplier Device Package         32-LQFP (7x7) | Details                    |                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Processor         HC08           Core Size         8-Bit           Speed         8MHz           Connectivity         LINbus, SCI, SPI           Peripherals         LVD, POR, PWM           Number of I/O         21           Program Memory Size         16KB (16K x 8)           Program Memory Type         FLASH           EEPROM Size         -           RAM Size         1K x 8           Voltage - Supply (Vcc/Vdd)         3V ~ 5.5V           Data Converters         A/D 8x10b           Oscillator Type         Internal           Operating Temperature         -40°C ~ 125°C (TA)           Mounting Type         Surface Mount           Package / Case         32-LQFP           Supplier Device Package         32-LQFP (7x7)                                           |                            |                                                                        |

| Core Size         8-Bit           Speed         8MHz           Connectivity         LINbus, SCI, SPI           Peripherals         LVD, POR, PWM           Number of I/O         21           Program Memory Size         16KB (16K x 8)           Program Memory Type         FLASH           EEPROM Size         -           RAM Size         1K x 8           Voltage - Supply (Vcc/Vdd)         3V ~ 5.5V           Data Converters         A/D 8x10b           Oscillator Type         Internal           Operating Temperature         -40°C ~ 125°C (TA)           Mounting Type         Surface Mount           Package / Case         32-LQFP           Supplier Device Package         32-LQFP (7x7)                                                                                 | Product Status             | Obsolete                                                               |

| Speed 8MHz  Connectivity LINbus, SCI, SPI  Peripherals LVD, POR, PWM  Number of I/O 21  Program Memory Size 16KB (16K x 8)  Program Memory Type FLASH  EEPROM Size -  RAM Size 1K x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                          | Core Processor             | HC08                                                                   |

| Connectivity LINbus, SCI, SPI  Peripherals LVD, POR, PWM  Number of I/O 21  Program Memory Size 16KB (16K x 8)  Program Memory Type FLASH  EEPROM Size -  RAM Size 1K x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                      | Core Size                  | 8-Bit                                                                  |

| PeripheralsLVD, POR, PWMNumber of I/O21Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Speed                      | 8MHz                                                                   |

| Number of I/O 21  Program Memory Size 16KB (16K x 8)  Program Memory Type FLASH  EEPROM Size -  RAM Size 1K x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Connectivity               | LINbus, SCI, SPI                                                       |

| Program Memory Size 16KB (16K x 8)  Program Memory Type FLASH  EEPROM Size - IK x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Peripherals                | LVD, POR, PWM                                                          |

| Program Memory Type FLASH  EEPROM Size -  RAM Size 1K x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP  Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Number of I/O              | 21                                                                     |

| EEPROM Size - IK x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP  Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Program Memory Size        | 16KB (16K x 8)                                                         |

| RAM Size 1K x 8  Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP  Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case32-LQFPSupplier Device Package32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EEPROM Size                | -                                                                      |

| Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  -40°C ~ 125°C (TA)  Mounting Type  Surface Mount  Package / Case  32-LQFP  Supplier Device Package  32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RAM Size                   | 1K x 8                                                                 |

| Oscillator Type Internal Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP  Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Operating Temperature -40°C ~ 125°C (TA)  Mounting Type Surface Mount  Package / Case 32-LQFP  Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data Converters            | A/D 8x10b                                                              |

| Mounting Type Surface Mount Package / Case 32-LQFP Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                               |

| Package / Case 32-LQFP Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Supplier Device Package 32-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | 32-LQFP                                                                |

| Purchase LIDI https://www.o.vfl.com/grodust_dotail/gvn.com/condustars/mc000sr15cmfic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supplier Device Package    | 32-LQFP (7x7)                                                          |

| ruichase ond https://www.e-xii.com/product-detail/htxp-semiconductors/mc908gr16amije                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr16amfje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr.        | Register Name                                     |                 | Bit 7 | 6       | 5       | 4         | 3                   | 2       | 1         | Bit 0   |

|--------------|---------------------------------------------------|-----------------|-------|---------|---------|-----------|---------------------|---------|-----------|---------|

|              | ESCI Data Register                                | Read:           | R7    | R6      | R5      | R4        | R3                  | R2      | R1        | R0      |

| \$0018       | (SCDR)                                            | Write:          | T7    | T6      | T5      | T4        | T3                  | T2      | T1        | T0      |

|              | See page 164.                                     | Reset:          |       |         |         | Unaffecte | d by reset          |         |           |         |

| \$0019       | ESCI Baud Rate Register<br>(SCBR)                 | Read:<br>Write: | LINT  | LINR    | SCP1    | SCP0      | R                   | SCR2    | SCR1      | SCR0    |

|              | See page 165.                                     | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

|              | Keyboard Status                                   | Read:           | 0     | 0       | 0       | 0         | KEYF                | 0       | IMASKK    | MODEK   |

| \$001A       | and Control Register<br>(INTKBSCR)                | Write:          |       |         |         |           |                     | ACKK    | IIVIAGRIX | MODER   |

|              | See page 103.                                     | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

| \$001B       | Keyboard Interrupt Enable<br>Register (INTKBIER)  | Read:<br>Write: | KBIE7 | KBIE6   | KBIE5   | KBIE4     | KBIE3               | KBIE2   | KBIE1     | KBIE0   |

|              | See page 104.                                     | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

|              | Timebase Module Control                           | Read:           | TBIF  | TBR2    | TBR1    | TBR0      | 0                   | TBIE    | TBON      | R       |

| \$001C       | Register (TBCR)                                   | Write:          |       | TDITE   | IDITI   | TDITO     | TACK                | TOIL    |           | 11      |

|              | See page 214.                                     | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

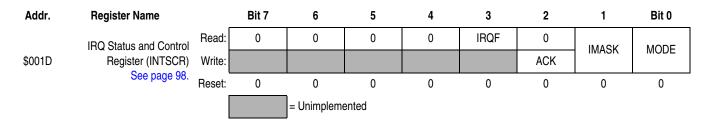

|              | IRQ Status and Control                            | Read:           | 0     | 0       | 0       | 0         | IRQF                | 0       | IMASK     | MODE    |

| \$001D       | Register (INTSCR)                                 | Write:          |       |         |         |           |                     | ACK     | IIVIAOR   | WODL    |

|              | See page 98.                                      | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

| \$001F (CONF | Configuration Register 2                          | Read:           | 0     | 0       | 0       | 0         | R                   | TBMCLK- | OSCENIN-  | ESCIBD- |

|              | (CONFIG2) <sup>(1)</sup><br>See page 75.          | Write:          |       |         |         |           | 11                  | SEL     | STOP      | SRC     |

|              | 000 page 70.                                      | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 1       |

| \$001F       | Configuration Register 1 (CONFIG1) <sup>(1)</sup> | Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD   | LVI5OR3<br>(Note 1) | SSREC   | STOP      | COPD    |

|              | See page 76.                                      | Reset:          | 0     | 0       | 0       | 0         | 0                   | 0       | 0         | 0       |

<sup>1.</sup> One-time writable register after each reset, except LVI5OR3 bit. LVI5OR3 bit is only reset via POR (power-on reset).

|        |                                                  | _               |        |            |       |             |    |              |     |       |

|--------|--------------------------------------------------|-----------------|--------|------------|-------|-------------|----|--------------|-----|-------|

|        | Timer 1 Status and Control                       | Read:           | TOF    | TOIE       | TSTOP | 0           | 0  | PS2          | PS1 | PS0   |

| \$0020 | Register (T1SC)                                  | Write:          | 0      | TOIL       | 13101 | TRST        |    | F 52         | 131 | F30   |

|        | See page 225.                                    | Reset:          | 0      | 0          | 1     | 0           | 0  | 0            | 0   | 0     |

|        | Timer 1 Counter                                  | Read:           | Bit 15 | 14         | 13    | 12          | 11 | 10           | 9   | Bit 8 |

| \$0021 | Register High (T1CNTH)                           | Write:          |        |            |       |             |    |              |     |       |

|        | See page 226.                                    | Reset:          | 0      | 0          | 0     | 0           | 0  | 0            | 0   | 0     |

|        | Timer 1 Counter                                  | Read:           | Bit 7  | 6          | 5     | 4           | 3  | 2            | 1   | Bit 0 |

| \$0022 |                                                  | Write:          |        |            |       |             |    |              |     |       |

|        | See page 226.                                    | Reset:          | 0      | 0          | 0     | 0           | 0  | 0            | 0   | 0     |

| \$0023 | Timer 1 Counter Modulo<br>Register High (T1MODH) | Read:<br>Write: | Bit 15 | 14         | 13    | 12          | 11 | 10           | 9   | Bit 8 |

|        | See page 227.                                    | Reset:          | 1      | 1          | 1     | 1           | 1  | 1            | 1   | 1     |

|        |                                                  | [               |        | = Unimplem | ented | R = Reserve | d  | U = Unaffect | ed  |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 7)

MC68HC908GR16A Data Sheet, Rev. 1.0

#### Memory

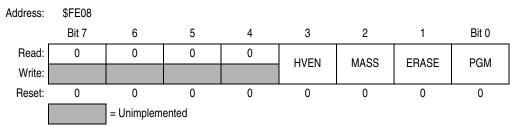

# 2.6.2 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

# **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

## MASS — Mass Erase Control Bit

Setting this read/write bit configures the 16-Kbyte FLASH array for mass erase operation.

- 1 = MASS erase operation selected

- 0 = PAGE erase operation selected

## **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

# **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

MC68HC908GR16A Data Sheet, Rev. 1.0

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

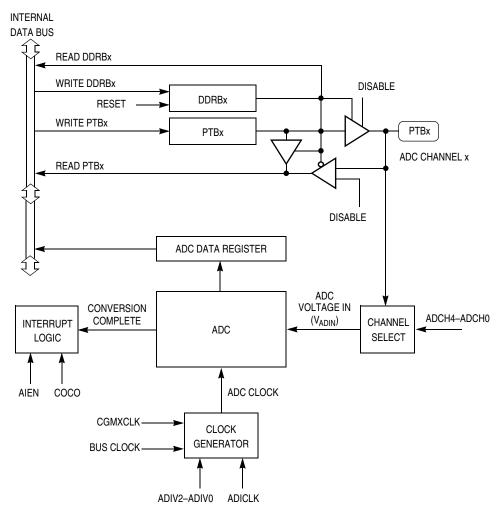

Figure 3-2. ADC Block Diagram

# 3.3.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{REFH}$ , the ADC converts the signal to \$3FF (full scale). If the input voltage equals  $V_{REFL}$ , the ADC converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are a straight-line linear conversion.

# **NOTE**

The ADC input voltage must always be greater than  $V_{SSAD}$  and less than  $V_{DDAD}$ . Connect the  $V_{DDAD}$  pin to the same voltage potential as the  $V_{DD}$  pin, and connect the  $V_{SSAD}$  pin to the same voltage potential as the  $V_{SS}$  pin. The  $V_{DDAD}$  pin should be routed carefully for maximum noise immunity.

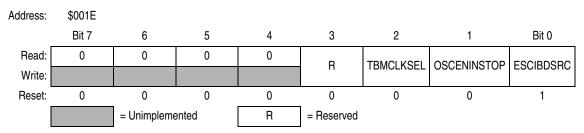

# **Chapter 5 Configuration Register (CONFIG)**

# 5.1 Introduction

This section describes the configuration registers, CONFIG1 and CONFIG2. The configuration registers enable or disable these options:

- Stop mode recovery time (32 CGMXCLK cycles or 4096 CGMXCLK cycles)

- COP timeout period (262,128 or 8176 COPCLK cycles)

- STOP instruction

- Computer operating properly module (COP)

- Low-voltage inhibit (LVI) module control and voltage trip point selection

- Enable/disable the oscillator (OSC) during stop mode

- Enable/disable an extra divide by 128 prescaler in timebase module

# 5.2 Functional Description

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. All of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU), it is recommended that these registers be written immediately after reset. The configuration registers are located at \$001E and \$001F and may be read at anytime.

## NOTE

On a FLASH device, the options except LVI5OR3 are one-time writable by the user after each reset. The LVI5OR3 bit is one-time writable by the user only after each POR (power-on reset). The CONFIG registers are not in the FLASH memory but are special registers containing one-time writable latches after each reset. Upon a reset, the CONFIG registers default to predetermined settings as shown in Figure 5-1 and Figure 5-2.

Figure 5-1. Configuration Register 2 (CONFIG2)

### External Interrupt (IRQ)

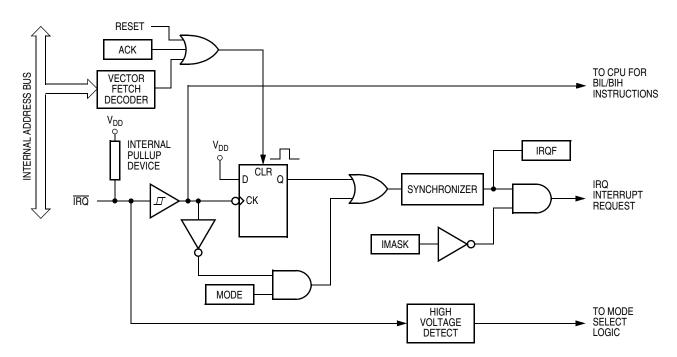

Figure 8-1. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered (MODE = 1), the interrupt remains set until both of these events occur:

- Vector fetch or software clear

- Return of the interrupt pin to a high level

The vector fetch or software clear may occur before or after the interrupt pin returns to a high level. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR masks all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

## NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

Figure 8-2. IRQ I/O Register Summary

MC68HC908GR16A Data Sheet, Rev. 1.0

# Chapter 9 Keyboard Interrupt Module (KBI)

# 9.1 Introduction

The keyboard interrupt module (KBI) provides eight independently maskable external interrupts which are accessible via PTA0-PTA7. When a port pin is enabled for keyboard interrupt function, an internal pullup device is also enabled on the pin.

# 9.2 Features

Features include:

- Eight keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Hysteresis buffers

- · Programmable edge-only or edge- and level- interrupt sensitivity

- Exit from low-power modes

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

# 9.3 Functional Description

Writing to the KBIE7–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin also enables its internal pullup device. A low level applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling edge- and low-level sensitive, an interrupt request is present as long as any keyboard interrupt pin is low and the pin is keyboard interrupt enabled.

Table 12-1. Port Control Register Bits Summary

| Port | Bit | DDR   | Modu    | ule Control   | Pin        |

|------|-----|-------|---------|---------------|------------|

|      | 0   | DDRA0 |         | KBIE0         | PTA0/KBD0  |

|      | 1   | DDRA1 |         | KBIE1         | PTA1/KBD1  |

|      | 2   | DDRA2 |         | KBIE2         | PTA2/KBD2  |

| ^    | 3   | DDRA3 | KDD     | KBIE3         | PTA3/KBD3  |

| Α    | 4   | DDRA4 | KBD     | KBIE4         | PTA4/KBD4  |

|      | 5   | DDRA5 |         | KBIE5         | PTA5/KBD5  |

|      | 6   | DDRA6 |         | KBIE6         | PTA6/KBD6  |

|      | 7   | DDRA7 |         | KBIE7         | PTA7/KBD7  |

|      | 0   | DDRB0 |         |               | PTB0/AD0   |

|      | 1   | DDRB1 |         |               | PTB1/AD1   |

|      | 2   | DDRB2 |         |               | PTB2/AD2   |

| В    | 3   | DDRB3 | ADC     | ADCH4-ADCH0   | PTB3/AD3   |

|      | 4   | DDRB4 | ADO     | ADOITH-ADOITO | PTB4/AD4   |

|      | 5   | DDRB5 |         |               | PTB5/AD5   |

|      | 6   | DDRB6 |         |               | PTB6/AD6   |

|      | 7   | DDRB7 |         |               | PTB7/AD7   |

|      | 0   | DDRC0 |         |               | PTC0       |

|      | 1   | DDRC1 |         |               | PTC1       |

|      | 2   | DDRC2 |         |               | PTC2       |

| С    | 3   | DDRC3 |         |               | PTC3       |

|      | 4   | DDRC4 |         |               | PTC4       |

|      | 5   | DDRC5 |         |               | PTC5       |

|      | 6   | DDRC6 |         |               | PTC6       |

|      | 0   | DDRD0 |         |               | PTD0/SS    |

|      | 1   | DDRD1 | SPI     | SPE           | PTD1/MISO  |

|      | 2   | DDRD2 | 011     | 01 L          | PTD2/MOSI  |

| D    | 3   | DDRD3 |         |               | PTD3/SPSCK |

|      | 4   | DDRD4 | TIM1    | ELS0B:ELS0A   | PTD4/T1CH0 |

|      | 5   | DDRD5 | 1 11111 | ELS1B:ELS1A   | PTD5/T1CH1 |

|      | 6   | DDRD6 | TIM2    | ELS0B:ELS0A   | PTD6/T2CH0 |

|      | 7   | DDRD7 | 111112  | ELS1B:ELS1A   | PTD7/T2CH1 |

|      | 0   | DDRE0 | SCI     | ENSCI         | PTE0/TxD   |

|      | 1   | DDRE1 | 301     | 2,1001        | PTE1/RxD   |

| E    | 2   | DDRE2 |         |               | PTE2       |

| _    | 3   | DDRE3 |         |               | PTE3       |

|      | 4   | DDRE4 |         |               | PTE4       |

|      | 5   | DDRE5 |         |               | PTE5       |

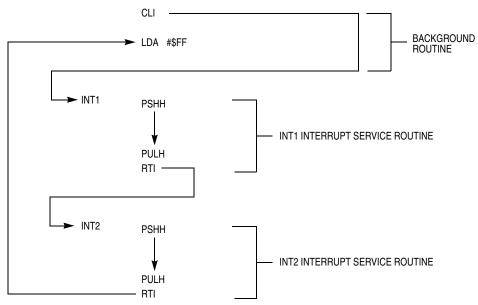

example shown in Figure 13-4, if an interrupt is pending upon exit from the interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

Figure 13-4. Interrupt Recognition Example

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, save the H register and then restore it prior to exiting the routine.

See Figure 13-5 for a flowchart depicting interrupt processing.

# 13.3.2 Sources

The sources in Table 13-1 can generate CPU interrupt requests.

# 13.3.2.1 Software Interrupt (SWI) Instruction

The software interrupt (SWI) instruction causes a non-maskable interrupt.

# NOTE

A software interrupt pushes PC onto the stack. An SWI does **not** push PC – 1, as a hardware interrupt does.

## 13.3.2.2 Break Interrupt

The break module causes the CPU to execute an SWI instruction at a software-programmable break point.

# 14.4.2.1 Character Length

The transmitter can accommodate either 8-bit or 9-bit data. The state of the M bit in ESCI control register 1 (SCC1) determines character length. When transmitting 9-bit data, bit T8 in ESCI control register 3 (SCC3) is the ninth bit (bit 8).

## 14.4.2.2 Character Transmission

During an ESCI transmission, the transmit shift register shifts a character out to the TxD pin. The ESCI data register (SCDR) is the write-only buffer between the internal data bus and the transmit shift register.

To initiate an ESCI transmission:

- Enable the ESCI by writing a 1 to the enable ESCI bit (ENSCI) in ESCI control register 1 (SCC1).

- 2. Enable the transmitter by writing a 1 to the transmitter enable bit (TE) in ESCI control register 2 (SCC2).

- 3. Clear the ESCI transmitter empty bit (SCTE) by first reading ESCI status register 1 (SCS1) and then writing to the SCDR. For 9-bit data, also write the T8 bit in SCC3.

- 4. Repeat step 3 for each subsequent transmission.

At the start of a transmission, transmitter control logic automatically loads the transmit shift register with a preamble of 1s. After the preamble shifts out, control logic transfers the SCDR data into the transmit shift register. A 0 start bit automatically goes into the least significant bit (LSB) position of the transmit shift register. A 1 stop bit goes into the most significant bit (MSB) position.

The ESCI transmitter empty bit, SCTE, in SCS1 becomes set when the SCDR transfers a byte to the transmit shift register. The SCTE bit indicates that the SCDR can accept new data from the internal data bus. If the ESCI transmit interrupt enable bit, SCTIE, in SCC2 is also set, the SCTE bit generates a transmitter CPU interrupt request.

When the transmit shift register is not transmitting a character, the TxD pin goes to the idle condition, high. If at any time software clears the ENSCI bit in ESCI control register 1 (SCC1), the transmitter and receiver relinquish control of the port E pins.

### 14.4.2.3 Break Characters

Writing a 1 to the send break bit, SBK, in SCC2 loads the transmit shift register with a break character. For TXINV = 0 (output not inverted), a transmitted break character contains all 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCC1 and the LINR bits in SCBR. As long as SBK is at 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one 1. The automatic 1 at the end of a break character guarantees the recognition of the start bit of the next character.

When LINR is cleared in SCBR, the ESCI recognizes a break character when a start bit is followed by eight or nine 0 data bits and a 0 where the stop bit should be, resulting in a total of 10 or 11 consecutive 0 data bits. When LINR is set in SCBR, the ESCI recognizes a break character when a start bit is followed by 9 or 10 0 data bits and a 0 where the stop bit should be, resulting in a total of 11 or 12 consecutive 0 data bits.

Receiving a break character has these effects on ESCI registers:

- Sets the framing error bit (FE) in SCS1

- Sets the ESCI receiver full bit (SCRF) in SCS1

- Clears the ESCI data register (SCDR)

MC68HC908GR16A Data Sheet, Rev. 1.0

## NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle will cause the receiver to wake up.

# 14.4.3.7 Receiver Interrupts

These sources can generate CPU interrupt requests from the ESCI receiver:

- ESCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has

transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting

the ESCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver

CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

# 14.4.3.8 Error Interrupts

These receiver error flags in SCS1 can generate CPU interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new

character before the previous character was read from the SCDR. The previous character remains

in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3

enables OR to generate ESCI error CPU interrupt requests.

- Noise flag (NF) The NF bit is set when the ESCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate ESCI error CPU interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate ESCI error CPU interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the ESCI detects a parity error in incoming

data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate ESCI error CPU

interrupt requests.

# 14.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

# 14.5.1 Wait Mode

The ESCI module remains active in wait mode. Any enabled CPU interrupt request from the ESCI module can bring the MCU out of wait mode.

If ESCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

# 14.5.2 **Stop Mode**

The ESCI module is inactive in stop mode. The STOP instruction does not affect ESCI register states. ESCI module operation resumes after the MCU exits stop mode.

Because the internal clock is inactive during stop mode, entering stop mode during an ESCI transmission or reception results in invalid data.

MC68HC908GR16A Data Sheet, Rev. 1.0

# 14.6 ESCI During Break Module Interrupts

The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state. See Chapter 19 Development Support.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 14.7 I/O Signals

Port E shares two of its pins with the ESCI module. The two ESCI I/O pins are:

- PTE0/TxD transmit data

- PTE1/RxD receive data

# 14.7.1 PTE0/TxD (Transmit Data)

The PTE0/TxD pin is the serial data output from the ESCI transmitter. The ESCI shares the PTE0/TxD pin with port E. When the ESCI is enabled, the PTE0/TxD pin is an output regardless of the state of the DDRE0 bit in data direction register E (DDRE).

# 14.7.2 PTE1/RxD (Receive Data)

The PTE1/RxD pin is the serial data input to the ESCI receiver. The ESCI shares the PTE1/RxD pin with port E. When the ESCI is enabled, the PTE1/RxD pin is an input regardless of the state of the DDRE1 bit in data direction register E (DDRE).

# 14.8 I/O Registers

These I/O registers control and monitor ESCI operation:

- ESCI control register 1, SCC1

- ESCI control register 2, SCC2

- ESCI control register 3, SCC3

- ESCI status register 1, SCS1

- ESCI status register 2, SCS2

- ESCI data register, SCDR

- ESCI baud rate register, SCBR

- ESCI prescaler register, SCPSC

- ESCI arbiter control register, SCIACTL

- ESCI arbiter data register, SCIADAT

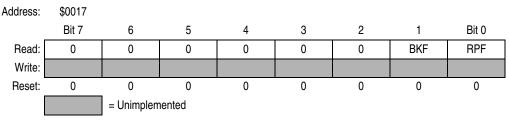

# 14.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Incoming data

Figure 14-15. ESCI Status Register 2 (SCS2)

# **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

# RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

# 14.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

| Address: | \$0018              |    |    |    |    |    |    |       |

|----------|---------------------|----|----|----|----|----|----|-------|

|          | Bit 7               | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

| Read:    | R7                  | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| Write:   | T7                  | T6 | T5 | T4 | T3 | T2 | T1 | T0    |

| Reset:   | Unaffected by reset |    |    |    |    |    |    |       |

Figure 14-16. ESCI Data Register (SCDR)

# R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

## NOTE

Do not use read-modify-write instructions on the ESCI data register.

MC68HC908GR16A Data Sheet, Rev. 1.0

# PDS2-PDS0 — Prescaler Divisor Select Bits

These read/write bits select the prescaler divisor as shown in Table 14-10. Reset clears PDS2-PDS0.

## NOTE

The setting of '000' will bypass not only this prescaler but also the prescaler divisor fine adjust (PDFA). It is not recommended to bypass the prescaler while ENSCI is set, because the switching is not glitch free.

**Table 14-10. ESCI Prescaler Division Ratio**

| PS[2:1:0] | Prescaler Divisor (PD) |

|-----------|------------------------|

| 0 0 0     | Bypass this prescaler  |

| 0 0 1     | 2                      |

| 0 1 0     | 3                      |

| 0 1 1     | 4                      |

| 1 0 0     | 5                      |

| 1 0 1     | 6                      |

| 1 1 0     | 7                      |

| 1 1 1     | 8                      |

# PSSB4-PSSB0 — Clock Insertion Select Bits

These read/write bits select the number of clocks inserted in each 32 output cycle frame to achieve more timing resolution on the **average** prescaler frequency as shown in Table 14-11. Reset clears PSSB4–PSSB0.

**Table 14-11. ESCI Prescaler Divisor Fine Adjust**

| PSSB[4:3:2:1:0] | Prescaler Divisor Fine Adjust (PDFA) |

|-----------------|--------------------------------------|

| 0 0 0 0 0       | 0/32 = 0                             |

| 0 0 0 0 1       | 1/32 = 0.03125                       |

| 0 0 0 1 0       | 2/32 = 0.0625                        |

| 0 0 0 1 1       | 3/32 = 0.09375                       |

| 0 0 1 0 0       | 4/32 = 0.125                         |

| 0 0 1 0 1       | 5/32 = 0.15625                       |

| 0 0 1 1 0       | 6/32 = 0.1875                        |

| 0 0 1 1 1       | 7/32 = 0.21875                       |

| 0 1 0 0 0       | 8/32 = 0.25                          |

| 0 1 0 0 1       | 9/32 = 0.28125                       |

| 0 1 0 1 0       | 10/32 = 0.3125                       |

| 0 1 0 1 1       | 11/32 = 0.34375                      |

| 0 1 1 0 0       | 12/32 = 0.375                        |

| 0 1 1 0 1       | 13/32 = 0.40625                      |

| 0 1 1 1 0       | 14/32 = 0.4375                       |

| 0 1 1 1 1       | 15/32 = 0.46875                      |

Continued on next page

MC68HC908GR16A Data Sheet, Rev. 1.0

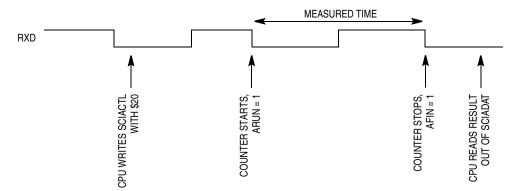

Figure 14-21. Bit Time Measurement with ACLK = 0

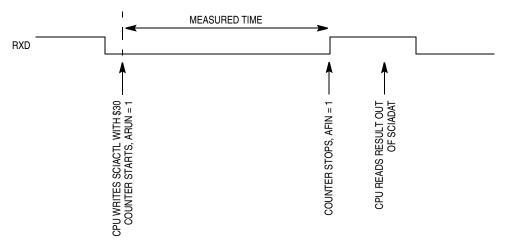

Figure 14-22. Bit Time Measurement with ACLK = 1, Scenario A

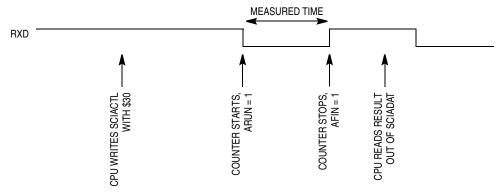

Figure 14-23. Bit Time Measurement with ACLK = 1, Scenario B

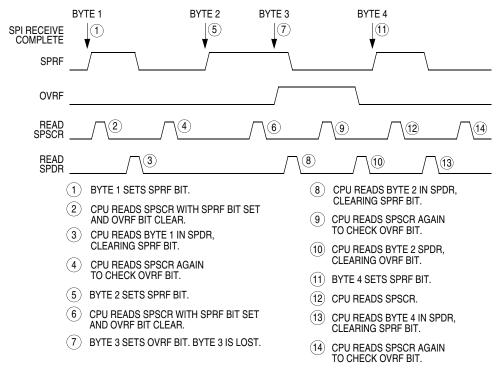

In this case, an overflow can be missed easily. Since no more SPRF interrupts can be generated until this OVRF is serviced, it is not obvious that bytes are being lost as more transmissions are completed. To prevent this, either enable the OVRF interrupt or do another read of the SPSCR following the read of the SPDR. This ensures that the OVRF was not set before the SPRF was cleared and that future transmissions can set the SPRF bit. Figure 16-11 illustrates this process. Generally, to avoid this second SPSCR read, enable the OVRF to the CPU by setting the ERRIE bit.

Figure 16-11. Clearing SPRF When OVRF Interrupt Is Not Enabled

## 16.6.2 Mode Fault Error

Setting SPMSTR selects master mode and configures the SPSCK and MOSI pins as outputs and the MISO pin as an input. Clearing SPMSTR selects slave mode and configures the SPSCK and MOSI pins as inputs and the MISO pin as an output. The mode fault bit, MODF, becomes set any time the state of the slave select pin,  $\overline{SS}$ , is inconsistent with the mode selected by SPMSTR.

To prevent SPI pin contention and damage to the MCU, a mode fault error occurs if:

- The SS pin of a slave SPI goes high during a transmission

- The SS pin of a master SPI goes low at any time

For the MODF flag to be set, the mode fault error enable bit (MODFEN) must be set. Clearing the MODFEN bit does not clear the MODF flag but does prevent MODF from being set again after MODF is cleared.

MODF generates a receiver/error CPU interrupt request if the error interrupt enable bit (ERRIE) is also set. The SPRF, MODF, and OVRF interrupts share the same CPU interrupt vector. (See Figure 16-12.) It is not possible to enable MODF or OVRF individually to generate a receiver/error CPU interrupt request. However, leaving MODFEN low prevents MODF from being set.

## Serial Peripheral Interface (SPI) Module

When enabled, the SPI controls data direction of the SPSCK pin regardless of the state of the data direction register of the shared I/O port.

# **16.11.4 SS** (Slave Select)

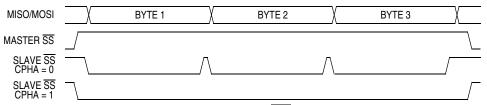

The  $\overline{SS}$  pin has various functions depending on the current state of the SPI. For an SPI configured as a slave,  $\overline{SS}$  is used to select a slave. For CPHA = 0,  $\overline{SS}$  is used to define the start of a transmission. (See 16.4 Transmission Formats.) Since it is used to indicate the start of a transmission,  $\overline{SS}$  must be toggled high and low between each byte transmitted for the CPHA = 0 format. However, it can remain low between transmissions for the CPHA = 1 format. See Figure 16-13.

Figure 16-13. CPHA/SS Timing

When an SPI is configured as a slave, the  $\overline{SS}$  pin is always configured as an input. It cannot be used as a general-purpose I/O regardless of the state of the MODFEN control bit. However, the MODFEN bit can still prevent the state of  $\overline{SS}$  from creating a MODF error. See 16.12.2 SPI Status and Control Register.

#### NOTE

A high on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high-impedance state. The slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

When an SPI is configured as a master, the  $\overline{SS}$  input can be used in conjunction with the MODF flag to prevent multiple masters from driving MOSI and SPSCK. (See 16.6.2 Mode Fault Error.) For the state of the  $\overline{SS}$  pin to set the MODF flag, the MODFEN bit in the SPSCK register must be set. If MODFEN is 0 for an SPI master, the  $\overline{SS}$  pin can be used as a general-purpose I/O under the control of the data direction register of the shared I/O port. When MODFEN is 1,  $\overline{SS}$  is an input-only pin to the SPI regardless of the state of the data direction register of the shared I/O port.

The CPU can always read the state of the  $\overline{SS}$  pin by configuring the appropriate pin as an input and reading the port data register. See Table 16-2.

| SPE | SPMSTR            | MODFEN | SPI Configuration   | Function of SS Pin                        |

|-----|-------------------|--------|---------------------|-------------------------------------------|

| 0   | X <sup>(1))</sup> | Х      | Not enabled         | General-purpose I/O;<br>SS ignored by SPI |

| 1   | 0                 | Х      | Slave               | Input-only to SPI                         |

| 1   | 1                 | 0      | Master without MODF | General-purpose I/O;<br>SS ignored by SPI |

| 1   | 1                 | 1      | Master with MODF    | Input-only to SPI                         |

**Table 16-2. SPI Configuration**

1. X = Don't care

### **Development Support**

When the internal address bus matches the value written in the break address registers or when software writes a 1 to the BRKA bit in the break status and control register, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode)

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

## **CAUTION**

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

# 19.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (SBFCR) enables software to clear status bits during the break state. See 15.7.3 SIM Break Flag Control Register and the **Break Interrupts** subsection for each module.

# 19.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

# 19.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

# 19.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (SBSR)

- Break flag control register (SBFCR)

## **Development Support**

Table 19-2. Mode Differences

|         |                      |                     | tions                |                     |                    |                   |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |

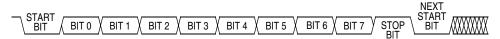

### 19.3.1.4 Data Format

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format. Transmit and receive baud rates must be identical.

Figure 19-12. Monitor Data Format

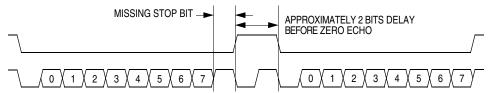

# 19.3.1.5 Break Signal

A start bit (0) followed by nine 0 bits is a break signal. When the monitor receives a break signal, it drives the PTA0 pin high for the duration of approximately two bits and then echoes back the break signal.

Figure 19-13. Break Transaction

### 19.3.1.6 Baud Rate

The communication baud rate is controlled by the crystal frequency or external clock and the state of the PTB4 pin (when  $\overline{IRQ}$  is set to  $V_{TST}$ ) upon entry into monitor mode. If monitor mode was entered with  $V_{DD}$  on  $\overline{IRQ}$  and the reset vector blank, then the baud rate is independent of PTB4.

Table 19-1 also lists external frequencies required to achieve a standard baud rate of 7200 bps. The effective baud rate is the bus frequency divided by 278. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle. See 20.5 5-Vdc Electrical Characteristics for this limit.

## 19.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

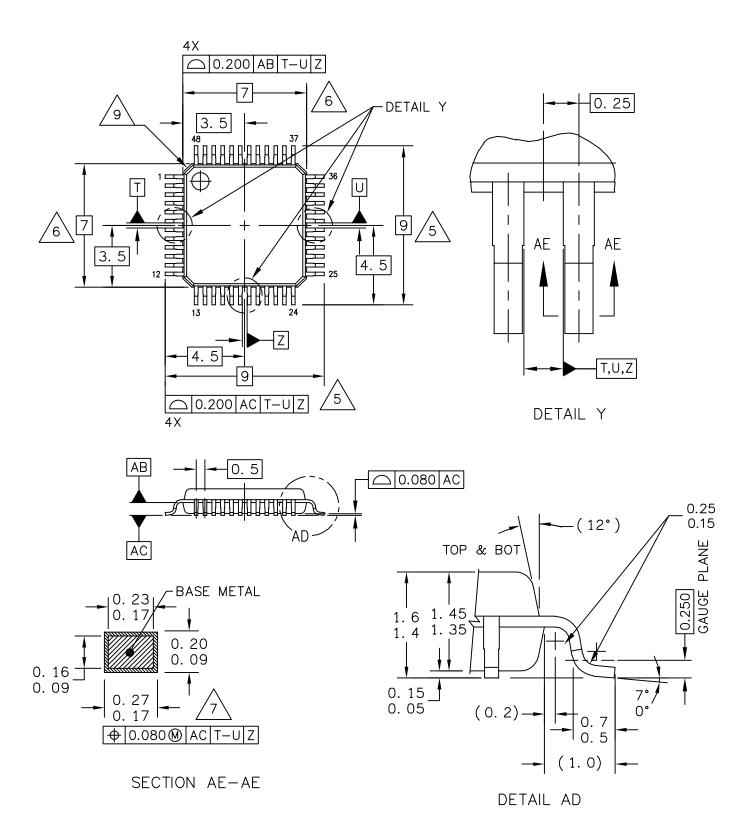

| FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | L OUTLINE | PRINT VERSION NO    | OT TO SCALE     |             |

|-------------------------------------------------------|-----------|---------------------|-----------------|-------------|

| TITLE:                                                |           |                     | ): 98ASH00962A  | REV: G      |

| LQFP, 48 LEAD, 0.5                                    |           | CASE NUMBER: 932-03 |                 | 14 APR 2005 |

| (7.0 X 7.0 X                                          | 1.4)      | STANDARD: JE        | EDEC MS-026-BBC |             |