# E·XFL

Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST6                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               |                                                                       |

| Peripherals                | LVD, POR, WDT                                                         |

| Number of I/O              | 9                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                          |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                |                                                                       |

| RAM Size                   | 64 × 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                               |

| Data Converters            | A/D 4x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t01cm3-tr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|    | 9.1  | ST6 ARCHITECTURE                                                               | 52       |

|----|------|--------------------------------------------------------------------------------|----------|

|    | 9.2  | ADDRESSING MODES                                                               | 52       |

|    | 9.3  | INSTRUCTION SET                                                                | 53       |

| 10 | ELE  | CTRICAL CHARACTERISTICS                                                        | 58       |

|    | 10.1 | PARAMETER CONDITIONS                                                           | 58       |

|    |      | 10.1.1 Minimum and Maximum Values                                              |          |

|    |      | 10.1.2Typical Values                                                           | 58       |

|    |      | 10.1.3Typical Curves                                                           |          |

|    |      | 10.1.5Pin Input Voltage                                                        |          |

|    |      | ABSOLUTE MAXIMUM RATINGS                                                       |          |

|    |      | 10.2.1 Voltage Characteristics                                                 | 59       |

|    |      | 10.2.2Current Characteristics                                                  |          |

|    | 10.3 | 10.2.3Thermal Characteristics                                                  |          |

|    |      | 10.3.1 General Operating Conditions                                            |          |

|    |      | 10.3.20perating Conditions with Low Voltage Detector (LVD)                     |          |

|    | 10.4 | SUPPLY CURRENT CHARACTERISTICS                                                 | 62       |

|    |      | 10.4.1 RUN Modes                                                               |          |

|    |      | 10.4.2WAIT Modes                                                               |          |

|    |      | 10.4.3STOP Mode                                                                |          |

|    |      | 10.4.5On-Chip Peripherals                                                      |          |

|    |      | CLOCK AND TIMING CHARACTERISTICS                                               |          |

|    |      | 10.5.1 General Timings                                                         |          |

|    |      | 10.5.2External Clock Source                                                    | 68       |

|    |      | 10.5.3Crystal and Ceramic Resonator Oscillators         10.5.4RC Oscillator    | 69<br>70 |

|    |      | 10.5.5Oscillator Safeguard (OSG) and Low Frequency Auxiliary Oscillator (LFAO) |          |

|    |      | MEMORY CHARACTERISTICS                                                         |          |

|    |      | 10.6.1 RAM and Hardware Registers                                              |          |

|    |      | 10.6.2EPROM Program Memory                                                     |          |

|    |      | EMC CHARACTERISTICS                                                            |          |

|    |      | 10.7.1 Functional EMS         10.7.2 Absolute Electrical Sensitivity           |          |

|    |      | 10.7.3ESD Pin Protection Strategy                                              |          |

|    |      | I/O PORT PIN CHARACTERISTICS                                                   |          |

|    |      | 10.8.1 General Characteristics                                                 |          |

|    | 40.0 | 10.8.20utput Driving Current                                                   | 78       |

|    |      |                                                                                |          |

|    |      | 10.9.1 Asynchronous RESET Pin                                                  |          |

|    | 10.1 | 0 TIMER PERIPHERAL CHARACTERISTICS                                             |          |

|    |      | 10.10.1Watchdog Timer                                                          | 83       |

|    |      | 10.10.28-Bit Timer                                                             | 83       |

|    | 10.1 | 1 8-BIT ADC CHARACTERISTICS                                                    | 84       |

# MEMORY MAP (Cont'd)

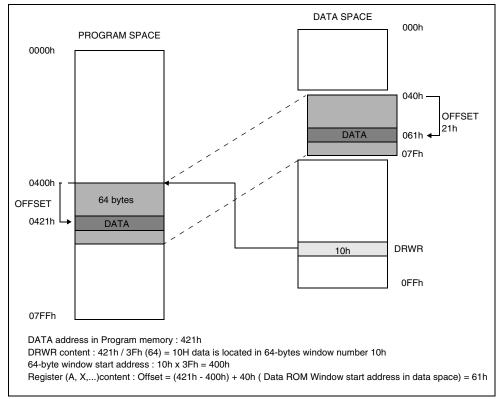

# 3.1.6.2 Data ROM Window memory addressing

In cases where some data (look-up tables for example) are stored in program memory, reading these data requires the use of the Data ROM window mechanism. To do this:

1. The DRWR register has to be loaded with the 64-byte block number where the data are located (in program memory). This number also gives the start address of the block.

2. Then, the offset address of the byte in the Data ROM Window (corresponding to the offset in the 64-byte block in program memory) has to be loaded in a register (A, X,...).

When the above two steps are completed, the data can be read.

To understand how to determine the DRWR and the content of the register, please refer to the example shown in Figure 6. In any case the calcula-

tion is automatically handled by the ST6 development tools.

Please refer to the user manual of the correspoding tool.

#### 3.1.6.3 Recommendations

Care is required when handling the DRWR register as it is write only. For this reason, the DRWR contents should not be changed while executing an interrupt service routine, as the service routine cannot save and then restore the register's previous contents. If it is impossible to avoid writing to the DRWR during the interrupt service routine, an image of the register must be saved in a RAM location, and each time the program writes to the DRWR, it must also write to the image register. The image register must be written first so that, if an interrupt occurs between the two instructions, the DRWR is not affected.

# 3.2 PROGRAMMING MODES

#### 3.2.1 Program Memory

EPROM/OTP programming mode is set by a +12.5V voltage applied to the TEST/V<sub>PP</sub> pin. The programming flow of the ST62T00C, T01/E01C and T03C is described in the User Manual of the EPROM Programming Board.

#### Table 3. ST6200C/03C Program Memory Map

| Device Address | Description          |

|----------------|----------------------|

| 0000h-0B9Fh    | Reserved             |

| 0BA0h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

#### Table 4. ST6201C Program Memory Map

| Device Address | Description          |

|----------------|----------------------|

| 0000h-087Fh    | Reserved             |

| 0880h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

**Note:** OTP/EPROM devices can be programmed with the development tools available from STMicroelectronics (please refer to Section 12 on page 95).

#### 3.2.2 EPROM Erasing

The EPROM devices can be erased by exposure to Ultra Violet light. The characteristics of the MCU are such that erasure begins when the memory is exposed to light with a wave lengths shorter than approximately 4000Å. It should be noted that sunlight and some types of fluorescent lamps have wavelengths in the range 3000-4000Å.

It is thus recommended that the window of the MCU packages be covered by an opaque label to prevent unintentional erasure problems when testing the application in such an environment.

The recommended erasure procedure is exposure to short wave ultraviolet light which have a wavelength 2537Å. The integrated dose (i.e. U.V. intensity x exposure time) for erasure should be a minimum of 30W-sec/cm<sup>2</sup>. The erasure time with this dosage is approximately 30 to 40 minutes using an ultraviolet lamp with 12000 $\mu$ W/cm<sup>2</sup> power rating. The EPROM device should be placed within 2.5cm (1inch) of the lamp tubes during erasure.

# **3.3 OPTION BYTES**

Each device is available for production in user programmable versions (OTP) as well as in factory coded versions (ROM). OTP devices are shipped to customers with a default content (00h), while ROM factory coded parts contain the code supplied by the customer. This implies that OTP devices have to be configured by the customer using the Option Bytes while the ROM devices are factory-configured.

The two option bytes allow the hardware configuration of the microcontroller to be selected.

The option bytes have no address in the memory map and can be accessed only in programming mode (for example using a standard ST6 programming tool).

In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see Section 11.6.2 "ROM VERSION" on page 93). It is therefore impossible to read the option bytes.

The option bytes can be only programmed once. It is not possible to change the selected options after they have been programmed.

In order to reach the power consumption value indicated in Section 10.4, the option byte must be programmed to its default value. Otherwise, an over-consumption will occur.

# MSB OPTION BYTE

Bits 15:11 = **Reserved**, must be always cleared.

Bit 10 = Reserved, must be always set.

Bit 9 = **EXTCNTL** *External STOP MODE control.* 0: EXTCNTL mode not available. STOP mode is not available with the watchdog active.

1: EXTCNTL mode available. STOP mode is available with the watchdog active by setting NMI pin to one.

Bit 8 = **LVD** Low Voltage Detector on/off.

This option bit enable or disable the Low Voltage Detector (LVD) feature.

- 0: Low Voltage Detector disabled

- 1: Low Voltage Detector enabled.

# LSB OPTION BYTE

Bit 7 = **PROTECT** *Readout Protection.*

This option bit enables or disables external access to the internal program memory.

- 0: Program memory not read-out protected

- 1: Program memory read-out protected

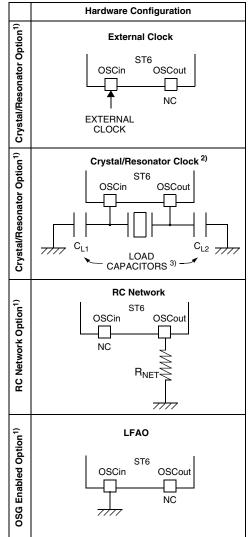

Bit 6 = **OSC** Oscillator selection.

This option bit selects the main oscillator type.

- 0: Quartz crystal, ceramic resonator or external clock

- 1: RC network

Bit 5 = **Reserved**, must be always cleared.

Bit 4 = Reserved, must be always set.

Bit 3 = **NMI PULL** *NMI Pull-Up* on/off. This option bit enables or disables the internal pullup on the NMI pin. 0: Pull-up disabled 1: Pull-up enabled

Bit 2 = Reserved, must be always set.

Bit 1 = WDACT Hardware or software watchdog.

This option bit selects the watchdog type.

0: Software (watchdog to be enabled by software)

1: Hardware (watchdog always enabled)

Bit 0 = OSGEN Oscillator Safeguard on/off.

This option bit enables or disables the oscillator Safeguard (OSG) feature.

0: Oscillator Safeguard disabled

1: Oscillator Safeguard enabled

|                  | MSB OPTION BYTE         |   |   |   |   |     |              |     |      | LS   | B OP        | TION B | YTE       |           |   |   |

|------------------|-------------------------|---|---|---|---|-----|--------------|-----|------|------|-------------|--------|-----------|-----------|---|---|

|                  | 15 8                    |   |   |   |   |     |              | 7   |      |      |             |        |           |           | 0 |   |

|                  | Reserved EXT<br>CTL LVD |   |   |   |   | LVD | PRO-<br>TECT | OSC | Res. | Res. | NMI<br>PULL | Res.   | WD<br>ACT | OSG<br>EN |   |   |

| Default<br>Value | х                       | х | х | х | х | х   | х            | х   | х    | х    | х           | х      | х         | х         | х | х |

# CPU REGISTERS (Cont'd)

The 12-bit length allows the direct addressing of 4096 bytes in Program Space.

However, if the program space contains more than 4096 bytes, the additional memory in program space can be addressed by using the Program ROM Page register.

The PC value is incremented after reading the address of the current instruction. To execute relative jumps, the PC and the offset are shifted through the ALU, where they are added; the result is then shifted back into the PC. The program counter can be changed in the following ways:

- CALL instruction

PC = Call address

- Relative Branch InstructionPC = PC +/- offset

| <ul> <li>Interrupt</li> </ul> | PC = Interrupt vector |

|-------------------------------|-----------------------|

| - Reset                       | PC = Reset vector     |

- RET & RETI instructions PC = Pop (stack)

- Normal instruction PC = PC + 1

Flags (C, Z). The ST6 CPU includes three pairs of flags (Carry and Zero), each pair being associated with one of the three normal modes of operation: Normal mode, Interrupt mode and Non Maskable Interrupt mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during Normal operation, another pair is used during Interrupt mode (CI, ZI), and a third pair is used in the Non Maskable Interrupt mode (CNMI, ZN-MI).

The ST6 CPU uses the pair of flags associated with the current mode: as soon as an interrupt (or a Non Maskable Interrupt) is generated, the ST6 CPU uses the Interrupt flags (or the NMI flags) instead of the Normal flags. When the RETI instruction is executed, the previously used set of flags is restored. It should be noted that each flag set can only be addressed in its own context (Non Maskable Interrupt, Normal Interrupt or Main routine). The flags are not cleared during context switching and thus retain their status.

#### C : Carry flag.

This bit is set when a carry or a borrow occurs during arithmetic operations; otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction; it also participates in the rotate left instruction.

0: No carry has occured

1: A carry has occured

#### Z : Zero flag

This flag is set if the result of the last arithmetic or logical operation was equal to zero; otherwise it is cleared.

- 0: The result of the last operation is different from zero

- 1: The result of the last operation is zero

Switching between the three sets of flags is performed automatically when an NMI, an interrupt or a RETI instruction occurs. As NMI mode is automatically selected after the reset of the MCU, the ST6 core uses the NMI flags first.

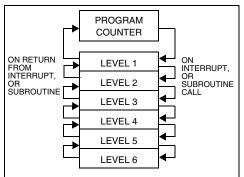

Stack. The ST6 CPU includes a true LIFO (Last In First Out) hardware stack which eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level are shifted into the next level down, while the content of the PC is shifted into the first level (the original contents of the sixth stack level are lost). When a subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is popped back into the previous level.

#### Figure 8. Stack manipulation

Since the accumulator, in common with all other data space registers, is not stored in this stack, management of these registers should be performed within the subroutine.

**Caution:** The stack will remain in its "deepest" position if more than 6 nested calls or interrupts are executed, and consequently the last return address will be lost.

It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

# CLOCK SYSTEM (Cont'd)

# 5.1.1 Main Oscillator

57

The oscillator configuration is specified by selecting the appropriate option in the option bytes (refer to the Option Bytes section of this document). When the CRYSTAL/RESONATOR option is selected, it must be used with a quartz crystal, a ceramic resonator or an external signal provided on the OSCin pin. When the RC NETWORK option is selected, the system clock is generated by an external resistor (the capacitor is implemented internally).

The main oscillator can be turned off (when the OSG ENABLED option is selected) by setting the OSCOFF bit of the ADC Control Register (not available on some devices). This will automatically start the Low Frequency Auxiliary Oscillator (LFAO).

The main oscillator can be turned off by resetting the OSCOFF bit of the A/D Converter Control Register or by resetting the MCU. When the main oscillator starts there is a delay made up of the oscillator start-up delay period plus the duration of the software instruction at a clock frequency  $f_{LFAO}$ .

**Caution:** It should be noted that when the RC network option is selected, the accuracy of the frequency is about 20% so it may not be suitable for some applications (For more details, please refer to the Electrical Characteristics Section).

#### Notes:

1. To select the options shown in column 1 of the above table, refer to the Option Byte section.

This schematic are given for guidance only and are subject to the schematics given by the crystal or ceramic resonator manufacturer.

3. For more details, please refer to the Electrical Characteristics Section.

# Table 5. Oscillator Configurations

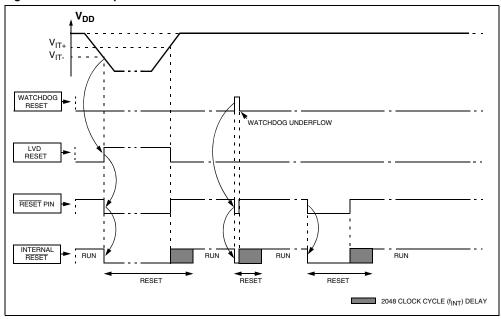

# 5.3 RESET

# 5.3.1 Introduction

The MCU can be reset in three ways:

- A low pulse input on the RESET pin

- Internal Watchdog reset

- Internal Low Voltage Detector (LVD) reset

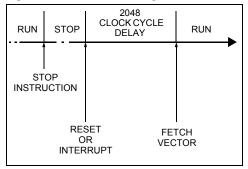

#### 5.3.2 RESET Sequence

The basic RESET sequence consists of 3 main phases:

- Internal (watchdog or LVD) or external Reset event

- A delay of 2048 clock (f<sub>INT</sub>) cycles

- RESET vector fetch

The reset delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The RESET vector fetch phase duration is 2 clock cycles.

When a reset occurs:

- The stack is cleared

- The PC is loaded with the address of the Reset vector. It is located in program ROM starting at address 0FFEh.

A jump to the beginning of the user program must be coded at this address.

The interrupt flag is automatically set, so that the CPU is in Non Maskable Interrupt mode. This prevents the initialization routine from being interrupted. The initialization routine should therefore be terminated by a RETI instruction, in order to go back to normal mode.

# Figure 13. RESET Sequence

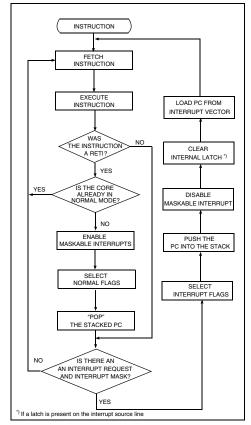

# 5.10 INTERRUPT HANDLING PROCEDURE

The interrupt procedure is very similar to a call procedure, in fact the user can consider the interrupt as an asynchronous call procedure. As this is an asynchronous event, the user cannot know the context and the time at which it occurred. As a result, the user should save all Data space registers which may be used within the interrupt routines. The following list summarizes the interrupt procedure:

When an interrupt request occurs, the following actions are performed by the MCU automatically:

- The core switches from the normal flags to the interrupt flags (or the NMI flags).

- The PC contents are stored in the top level of the stack.

- The normal interrupt lines are inhibited (NMI still active).

- The internal latch (if any) is cleared.

- The associated interrupt vector is loaded in the PC.

When an interrupt request occurs, the following actions must be performed by the user software:

- User selected registers have to be saved within the interrupt service routine (normally on a software stack).

- The source of the interrupt must be determined by polling the interrupt flags (if more than one source is associated with the same vector).

- The RETI (RETurn from Interrupt) instruction must end the interrupt service routine.

After the RETI instruction is executed, the MCU returns to the main routine.

**Caution:** When a maskable interrupt occurs while the ST6 core is in NORMAL mode and during the execution of an "Idi IOR, 00h" instruction (disabling all maskable interrupts): if the interrupt request occurs during the first 3 cycles of the "Idi" instruction (which is a 4-cycle instruction) the core will switch to interrupt mode BUT the flags CN and ZN will NOT switch to the interrupt pair CI and ZI.

#### 5.10.1 Interrupt Response Time

$\nabla$

This is defined as the time between the moment when the Program Counter is loaded with the interrupt vector and when the program has jump to the interrupt subroutine and is ready to execute the code. It depends on when the interrupt occurs while the core is processing an instruction.

#### Table 6. Interrupt Response Time

| Minimum | 6 CPU cycles  |

|---------|---------------|

| Maximum | 11 CPU cycles |

One CPU cycle is 13 external clock cycles thus 11 CPU cycles = 11 x (13 /8M) = 17.875  $\mu$ s with an 8 MHz external quartz.

# 6.3 STOP MODE

STOP mode is the lowest power consumption mode of the MCU (see Figure 22).

The MCU goes into STOP mode as soon as the STOP instruction is executed. This has the following effects:

- Program execution is stopped, the microcontroller can be considered as being "frozen".

- The contents of RAM and the peripheral registers are kept safely as long as the power supply voltage is higher than the RAM retention voltage.

- The oscillator is stopped, so peripherals cannot work except the those that can be driven by an external clock.

# Exit from STOP Mode

The MCU remains in STOP mode until one of the following events occurs:

- RESET (Watchdog, LVD or RESET pin)

- A peripheral interrupt (assuming this peripheral can be driven by an external clock)

- An external interrupt (I/O port, NMI)

In all cases a delay of 2048 clock cycles ( $f_{\text{INT}}$ ) is generated to make sure the oscillator has started properly.

The Program Counter then points to the starting address of the interrupt or RESET service routine (see Figure 21).

#### STOP Mode and Watchdog

When the Watchdog is active (hardware or software activation), the STOP instruction is disabled and a WAIT instruction will be executed in its place unless the EXCTNL option bit is set to 1 in the option bytes and a a high level is present on the NMI pin. In this case, the STOP instruction will be executed and the Watchdog will be frozen.

#### Figure 21. STOP Mode Timing Overview

# I/O PORTS (Cont'd) Table 9. I/O Port Option Selections

|                |                                          | MODE                              | ption Se   | AVAILABLE ON <sup>(1)</sup>          | SCHEMATIC                                                                                                                                        |

|----------------|------------------------------------------|-----------------------------------|------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Input DDRx ORx DRx                       |                                   |            | PA1-PA3<br>PB0, PB1, PB3,<br>PB5-PB7 | Data in                                                                                                                                          |

|                | 0                                        | 0                                 | 1          |                                      |                                                                                                                                                  |

| Digital Input  |                                          | Reset sta<br>Input<br>vith pull u |            | PA1-PA3<br>PB0, PB1, PB3,            | $ \begin{array}{c} & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ \end{array} $ Data in |

| Digit          | DDRx<br>0                                | ORx<br>0                          | DRx<br>0   | PB5-PB7                              |                                                                                                                                                  |

|                | Input<br>with pull up<br>with interrupt  |                                   |            | PA1-PA3<br>PB0, PB1, PB3,            | $ \begin{array}{c} & & & & \\ & & & & \\ & & & & \\ & & & & $                                                                                    |

|                | DDRx<br>0                                | ORx<br>1                          | DRx<br>0   | PB5-PB7                              |                                                                                                                                                  |

| Analog Input   | Analog Input                             |                                   |            | PB3, PB5-PB7<br>(Except on           |                                                                                                                                                  |

| Anal           | DDRx<br>0                                | ORx<br>1                          | DRx<br>1   | ST6203C)                             |                                                                                                                                                  |

|                | Open drain output (5mA)                  |                                   |            | PB0, PB1, PB3,<br>PB5-PB7            | P-buffer disconnected                                                                                                                            |

|                | Open drain output (20 mA)                |                                   |            | PA1-PA3                              | Data out                                                                                                                                         |

| Digital output | DDRx<br>1                                | ORx<br>0                          | DRx<br>0/1 |                                      |                                                                                                                                                  |

| Digital        | Push-pull output (5mA)                   |                                   |            | PB0, PB1, PB3,<br>PB5-PB7            |                                                                                                                                                  |

|                | Push-pull output (20 mA)<br>DDRx ORx DRx |                                   |            | PA1-PA3                              |                                                                                                                                                  |

|                | 1                                        | 1                                 | 0/1        |                                      | -                                                                                                                                                |

# WATCHDOG TIMER (Cont'd)

# 8.1.7 Register Description

# WATCHDOG REGISTER (WDGR)

Address: 0D8h - Read/Write

Reset Value: 1111 1110 (FEh)

| 7  |    |    |    |    |    |    | 0 |

|----|----|----|----|----|----|----|---|

| то | T1 | T2 | Т3 | T4 | T5 | SR | С |

# Bits 7:2 = T[5:0] Downcounter bits

**Caution:** These bits are reversed and shifted with respect to the physical counter: bit-7 (T0) is the LSB of the Watchdog downcounter and bit-2 (T5) is the MSB.

#### Bit 1 = SR: Software Reset bit

Software can generate a reset by clearing this bit while the C bit is set. When C = 0 (Watchdog deactivated) the SR bit is the MSB of the 7-bit timer. 0: Generate (write)

1: No software reset generated, MSB of 7-bit timer

#### Bit 0 = **C** Watchdog Control bit.

If the hardware option is selected (WDACT bit in Option byte), this bit is forced high and cannot be changed by the user (the Watchdog is always active). When the software option is selected (WDACT bit in Option byte), the Watchdog function is activated by setting the C bit, and cannot then be deactivated (except by resetting the MCU).

When C is kept cleared the counter can be used as a 7-bit timer.

0: Watchdog deactivated

1: Watchdog activated

# 8-BIT TIMER (Cont'd)

#### 8.2.3 Counter/Prescaler Description

#### Prescaler

The prescaler input is the internal frequency  $f_{INT}$  divided by 12. The prescaler decrements on the rising edge, depending on the division factor programmed by the PS[2:0] bits in the TSCR register.

The state of the 7-bit prescaler can be read in the PSCR register.

When the prescaler reaches 0, it is automatically reloaded with 7Fh.

#### Counter

The free running 8-bit downcounter is fed by the output of the programmable prescaler, and is decremented on every rising edge of the  $f_{COUNTER}$  clock signal coming from the prescaler.

It is possible to read or write the contents of the counter on the fly, by reading or writing the timer counter register (TCR).

When the downcounter reaches 0, it is automatically reloaded with the value 0FFh.

#### Counter Clock and Prescaler

The counter clock frequency is given by:

$f_{COUNTER} = f_{PRESCALER} / 2^{PS[2:0]}$

where f<sub>PRESCALER</sub> is:

– f<sub>INT</sub>/12

The timer input clock feeds the 7-bit programmable prescaler. The prescaler output can be programmed by selecting one of the 8 available prescaler taps using the PS[2:0] bits in the Status/Control Register (TSCR). Thus the division factor of the prescaler can be set to  $2^n$  (where n equals 0, to 7). See Figure 27.

The clock input is enabled by the PSI (Prescaler Initialize) bit in the TSCR register. When PSI is reset, the counter is frozen and the prescaler is loaded with the value 7Fh. When PSI is set, the prescaler and the counter run at the rate of the selected clock source.

#### **Counter and Prescaler Initialization**

After RESET, the counter and the prescaler are initialized to 0FFh and 7Fh respectively.

The 7-bit prescaler can be initialized to 7Fh by clearing the PSI bit. Direct write access to the

prescaler is also possible when PSI = 1. Then, any value between 0 and 7Fh can be loaded into it.

The 8-bit counter can be initialized separately by writing to the TCR register.

# 8.2.3.1 8-bit Counting and Interrupt Capability on Counter Underflow

Whatever the division factor defined for the prescaler, the Timer Counter works as an 8-bit downcounter. The input clock frequency is user selectable using the PS[2:0] bits.

When the downcounter decrements to zero, the TMZ (Timer Zero) bit in the TSCR is set. If the ETI (Enable Timer Interrupt) bit in the TSCR is also set, an interrupt request is generated.

The Timer interrupt can be used to exit the MCU from WAIT or STOP mode.

The TCR can be written at any time by software to define a time period ending with an underflow event, and therefore manage delay or timer functions.

TMZ is set when the downcounter reaches zero; however, it may also be set by writing 00h in the TCR register or by setting bit 7 of the TSCR register.

The TMZ bit must be cleared by user software when servicing the timer interrupt to avoid undesired interrupts when leaving the interrupt service routine.

Note: A write to the TCR register will predominate over the 8-bit counter decrement to 00h function, i.e. if a write and a TCR register decrement to 00h occur simultaneously, the write will take precedence, and the TMZ bit is not set until the 8-bit counter underflows again.

#### 8.2.4 Low Power Modes

| Mode | Description                                                                               |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| WAIT | No effect on timer.<br>Timer interrupt events cause the device to<br>exit from WAIT mode. |  |  |  |  |  |  |

| STOP | Timer registers are frozen.                                                               |  |  |  |  |  |  |

#### 8.2.5 Interrupts

| Interrupt Event     | Event<br>Flag | Enable<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Stop |

|---------------------|---------------|---------------|----------------------|----------------------|

| Timer Zero<br>Event | TMZ           | ETI           | Yes                  | No                   |

# **INSTRUCTION SET** (Cont'd)

**Conditional Branch**. Branch instructions perform a branch in the program when the selected condition is met.

**Bit Manipulation Instructions.** These instructions can handle any bit in Data space memory. One group either sets or clears. The other group (see Conditional Branch) performs the bit test branch operations.

# Table 17. Conditional Branch Instructions

**Control Instructions**. Control instructions control microcontroller operations during program execution.

**Jump and Call.** These two instructions are used to perform long (12-bit) jumps or subroutine calls to any location in the whole program space.

| Instruction   | Branch If | Bytes | Cycles | Fla | ags |

|---------------|-----------|-------|--------|-----|-----|

| Instruction   | Dranch II | Dytes | Cycles | Z   | С   |

| JRC e         | C = 1     | 1     | 2      | *   | *   |

| JRNC e        | C = 0     | 1     | 2      | *   | *   |

| JRZ e         | Z = 1     | 1     | 2      | *   | *   |

| JRNZ e        | Z = 0     | 1     | 2      | *   | *   |

| JRR b, rr, ee | Bit = 0   | 3     | 5      | *   | Δ   |

| JRS b, rr, ee | Bit = 1   | 3     | 5      | *   | Δ   |

#### Notes:

b 3-bit address

e 5 bit signed displacement in the range -15 to +16

ee 8 bit signed displacement in the range -126 to +129

#### Table 18. Bit Manipulation Instructions

| Instruction | Addressing Mode | Bytes Cycles | Bytes    | Fla | igs |

|-------------|-----------------|--------------|----------|-----|-----|

| instruction | Addressing Mode | Bytes        | Cycles Z | Z   | C   |

| SET b,rr    | Bit Direct      | 2            | 4        | *   | *   |

| RES b,rr    | Bit Direct      | 2            | 4        | *   | *   |

rr

Δ

#### Notes:

b 3-bit address

rr Data space register

Bit Manipulation Instructions should not be used on Port Data Registers and any registers with read only and/or write only bits (see I/O port chapter)

#### Table 19. Control Instructions

| Instruction | Addressing Mode | Bytes | Cycles | Fla | igs |

|-------------|-----------------|-------|--------|-----|-----|

| instruction | Addressing Mode | Bytes | Cycles | Z   | C   |

| NOP         | Inherent        | 1     | 2      | *   | *   |

| RET         | Inherent        | 1     | 2      | *   | *   |

| RETI        | Inherent        | 1     | 2      | Δ   | Δ   |

| STOP (1)    | Inherent        | 1     | 2      | *   | *   |

| WAIT        | Inherent        | 1     | 2      | *   | *   |

Notes:

This instruction is deactivated and a WAIT is automatically executed instead of a STOP if the watchdog function is selected.

Δ Affected \*Not Affected

#### Table 20. Jump & Call Instructions

| Instruction | Addressing Mode | Bytes Cycles | Cyclos | Fla | igs |

|-------------|-----------------|--------------|--------|-----|-----|

| instruction | Addressing Mode | Bytes        | Cycles | Z   | С   |

| CALL abc    | Extended        | 2            | 4      | *   | *   |

| JP abc      | Extended        | 2            | 4      | *   | *   |

Notes:

abc 12-bit address

Not Affected

Not Affected

Data space register

Not Affected

Affected. The tested bit is shifted into carry.

# **OPERATING CONDITIONS** (Cont'd)

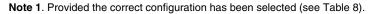

# 10.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$ .

| Symbol              | Parameter                                         | Conditions                         | Min | Typ <sup>1)</sup> | Max | Unit |

|---------------------|---------------------------------------------------|------------------------------------|-----|-------------------|-----|------|

| V <sub>IT+</sub>    | Reset release threshold<br>(V <sub>DD</sub> rise) |                                    | 3.9 | 4.1               | 4.3 | v    |

| V <sub>IT-</sub>    | Reset generation threshold (V <sub>DD</sub> fall) |                                    | 3.6 | 3.8               | 4   | v    |

| V <sub>hys</sub>    | LVD voltage threshold hysteresis                  | V <sub>IT+</sub> -V <sub>IT-</sub> | 50  | 300               | 700 | mV   |

| Vt <sub>POR</sub>   | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                    |     |                   |     | mV/s |

| t <sub>g(VDD)</sub> | Filtered glitch delay on V <sub>DD</sub> 3)       | Not detected by the LVD            |     | 30                |     | ns   |

#### Notes:

1. LVD typical data are based on  $T_A=25^{\circ}C$ . They are given only as design guidelines and are not tested.

The minimum V<sub>DD</sub> rise time rate is needed to insure a correct device power-on and LVD reset. Not tested in production.

Data based on characterization results, not tested in production.

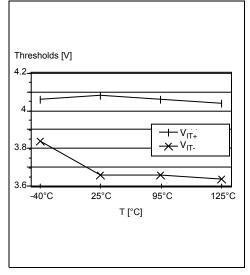

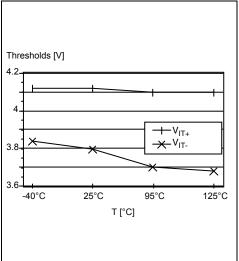

# Figure 33. LVD Threshold Versus V<sub>DD</sub> and f<sub>OSC</sub><sup>3)</sup>

Figure 34. Typical LVD Thresholds Versus Temperature for OTP devices

# Figure 35. Typical LVD thresholds vs. Temperature for ROM devices

# **10.5 CLOCK AND TIMING CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub>.

# 10.5.1 General Timings

| Symbol               | Parameter                            | Conditions              | Min  | Typ <sup>1)</sup> | Max    | Unit             |

|----------------------|--------------------------------------|-------------------------|------|-------------------|--------|------------------|

| +                    | Instruction cycle time               |                         | 2    | 4                 | 5      | t <sub>CPU</sub> |

| <sup>t</sup> c(INST) |                                      | f <sub>CPU</sub> =8 MHz | 3.25 | 6.5               | 8.125  | μs               |

| +                    | Interrupt reaction time 2)           |                         | 6    |                   | 11     | t <sub>CPU</sub> |

| t <sub>v(IT)</sub>   | $t_{v(IT)} = \Delta t_{c(INST)} + 6$ | f <sub>CPU</sub> =8 MHz | 9.75 |                   | 17.875 | μs               |

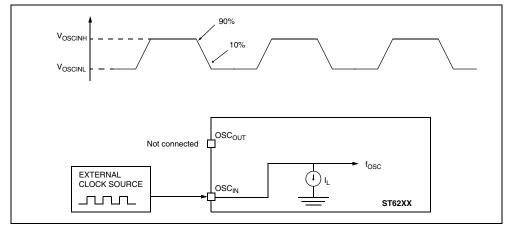

#### 10.5.2 External Clock Source

| Symbol              | Parameter                          | Conditions                                        | Min                             | Тур | Max                             | Unit |

|---------------------|------------------------------------|---------------------------------------------------|---------------------------------|-----|---------------------------------|------|

| V <sub>OSCINH</sub> | OSCIN input pin high level voltage | See Figure 43                                     | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     | V <sub>DD</sub>                 | V    |

| VOSCINL             | OSCIN input pin low level voltage  | See Figure 45                                     | V <sub>SS</sub>                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | v    |

| ١L                  | OSCx Input leakage current         | V <sub>SS</sub> ≸∕ <sub>IN</sub> ≸∕ <sub>DD</sub> |                                 |     | ± 2                             | μA   |

#### Notes:

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

#### Figure 43. Typical Application with an External Clock Source

# **10.7 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

#### 10.7.1 Functional EMS

(Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Neg <sup>1)</sup> | Pos <sup>1)</sup> | Unit |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|-------------------|------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | -2                | 2                 |      |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | $V_{DD}$ =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz conforms to IEC 1000-4-4           | -2.5              | 3                 | kV   |

#### Notes:

1. Data based on characterization results, not tested in production.

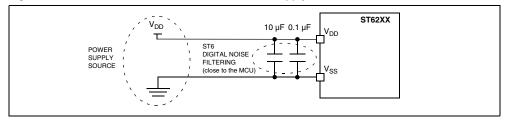

The suggested 10 μF and 0.1 μF decoupling capacitors on the power supply lines are proposed as a good price vs. EMC performance tradeoff. They have to be put as close as possible to the device power supply pins. Other EMC recommendations are given in other sections (I/Os, RESET, OSCx pin characteristics).

# Figure 50. EMC Recommended Star Network Power Supply Connection<sup>2)</sup>

# I/O PORT PIN CHARACTERISTICS (Cont'd)

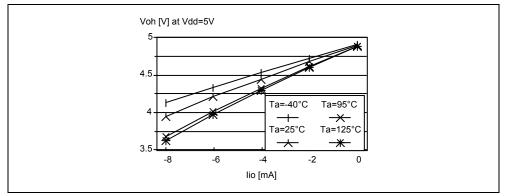

# Figure 59. Typical V<sub>OH</sub> at V<sub>DD</sub> = 5V

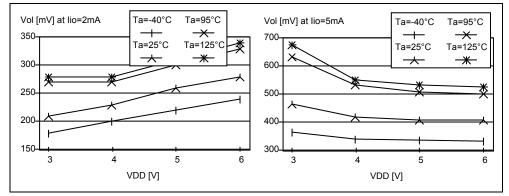

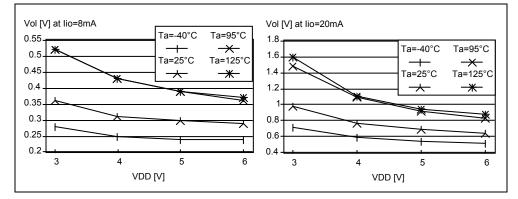

# Figure 60. Typical V<sub>OL</sub> vs V<sub>DD</sub> (standard I/Os)

Figure 61. Typical V<sub>OL</sub> vs V<sub>DD</sub> (high-sink I/Os)

# 8-BIT ADC CHARACTERISTICS (Cont'd)

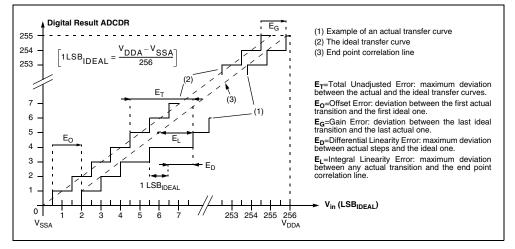

#### ADC Accuracy

| Symbol            | Parameter                       | Conditions                                                  | Min | Тур.  | Max                               | Unit |

|-------------------|---------------------------------|-------------------------------------------------------------|-----|-------|-----------------------------------|------|

| IE <sub>T</sub> I | Total unadjusted error 1)       |                                                             |     | 1.2   | ±2, fosc>1.2MHz<br>±4, fosc>32KHz |      |

| EO                | Offset error 1)                 | Vpp=5V <sup>2)</sup>                                        |     | 0.72  |                                   |      |

| E <sub>G</sub>    | Gain Error <sup>1)</sup>        | V <sub>DD</sub> =5V <sup>2)</sup><br>f <sub>OSC</sub> =8MHz |     | -0.31 |                                   | LSB  |

| IE <sub>D</sub> I | Differential linearity error 1) |                                                             |     | 0.54  |                                   |      |

| ΙΕ <sub>L</sub> Ι | Integral linearity error 1)     |                                                             |     |       |                                   |      |

Notes:

57

Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken:

Analog input pins must have a negative injection less than 1mA (assuming that the impedance of the analog voltage is lower than the specified limits).

- Pure digital pins must have a negative injection less than 1mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

2. Data based on characterization results over the whole temperature range, monitored in production.

#### Figure 67. ADC Accuracy Characteristics

Note: ADC not present on some devices. See device summary on page 1.

# **11.4 PACKAGE/SOCKET FOOTPRINT PROPOSAL**

#### Table 21. Suggested List of DIP16 Socket Types

| Package / Probe |         | Adaptor / Socket Reference | Same<br>Footprint | Socket Type |

|-----------------|---------|----------------------------|-------------------|-------------|

| DIP16           | TEXTOOL | 216-33-40                  | Х                 | Textool     |

# Table 22. Suggested List of SO16 Socket Types

| Package / Probe        | Adaptor / Socket Reference                                        | Same<br>Footprint | Socket Type |

|------------------------|-------------------------------------------------------------------|-------------------|-------------|

| SO16                   | ENPLAS OTS-16-1.27-04                                             |                   | Open Top    |

| 3016                   | YAMAICHI IC51-347.KS-7704                                         |                   |             |

| EMU PROBE              | Adapter from SO16 to DIP16 footprint<br>(delivered with emulator) | х                 | SMD to DIP  |

| Programming<br>Adapter | Logical Systems PA16SO1-08H-6                                     | х                 | Open Top    |

# Table 23. Suggested List of SSOP16 Socket Types

| Package / Probe        | Adaptor / Socket Reference                                              | Same<br>Footprint | Socket Type |

|------------------------|-------------------------------------------------------------------------|-------------------|-------------|

| SSOP16                 | ENPLAS OTS-16-0.65-01                                                   |                   | Open Top    |

| EMU PROBE              | Adapter from SSOP16 to DIP16 footprint<br>(sales type: ST626X-P/SSOP16) | х                 | SMD to DIP  |

| Programming<br>Adapter | Logical Systems PA16SS-OT-6                                             | х                 | Open Top    |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WAR-RANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURIS-DICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE. ST PRODUCTS ARE NOT RECOM-

UNLESS EXPRESSEY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOM-MENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLI-CATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com