# E·XFL

Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Obsolete                                                           |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | -                                                                  |

| Peripherals                | LVD, POR, WDT                                                      |

| Number of I/O              | 9                                                                  |

| Program Memory Size        | 2KB (2K x 8)                                                       |

| Program Memory Type        | OTP                                                                |

| EEPROM Size                |                                                                    |

| RAM Size                   | 64 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | A/D 4x8b                                                           |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                     |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t01cm3 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.2 PROGRAMMING MODES

#### 3.2.1 Program Memory

EPROM/OTP programming mode is set by a +12.5V voltage applied to the TEST/V<sub>PP</sub> pin. The programming flow of the ST62T00C, T01/E01C and T03C is described in the User Manual of the EPROM Programming Board.

#### Table 3. ST6200C/03C Program Memory Map

| Device Address | Description          |

|----------------|----------------------|

| 0000h-0B9Fh    | Reserved             |

| 0BA0h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

#### Table 4. ST6201C Program Memory Map

| Device Address | Description          |

|----------------|----------------------|

| 0000h-087Fh    | Reserved             |

| 0880h-0F9Fh    | User ROM             |

| 0FA0h-0FEFh    | Reserved             |

| 0FF0h-0FF7h    | Interrupt Vectors    |

| 0FF8h-0FFBh    | Reserved             |

| 0FFCh-0FFDh    | NMI Interrupt Vector |

| 0FFEh-0FFFh    | Reset Vector         |

**Note:** OTP/EPROM devices can be programmed with the development tools available from STMicroelectronics (please refer to Section 12 on page 95).

#### 3.2.2 EPROM Erasing

The EPROM devices can be erased by exposure to Ultra Violet light. The characteristics of the MCU are such that erasure begins when the memory is exposed to light with a wave lengths shorter than approximately 4000Å. It should be noted that sunlight and some types of fluorescent lamps have wavelengths in the range 3000-4000Å.

It is thus recommended that the window of the MCU packages be covered by an opaque label to prevent unintentional erasure problems when testing the application in such an environment.

The recommended erasure procedure is exposure to short wave ultraviolet light which have a wavelength 2537Å. The integrated dose (i.e. U.V. intensity x exposure time) for erasure should be a minimum of 30W-sec/cm<sup>2</sup>. The erasure time with this dosage is approximately 30 to 40 minutes using an ultraviolet lamp with 12000 $\mu$ W/cm<sup>2</sup> power rating. The EPROM device should be placed within 2.5cm (1inch) of the lamp tubes during erasure.

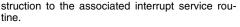

# 5.4 INTERRUPTS

The ST6 core may be interrupted by four maskable interrupt sources, in addition to a Non Maskable Interrupt (NMI) source. The interrupt processing flowchart is shown in Figure 18.

Maskable interrupts must be enabled by setting the GEN bit in the IOR register. However, even if they are disabled (GEN bit = 0), interrupt events are latched and may be processed as soon as the GEN bit is set.

Each source is associated with a specific Interrupt Vector, located in Program space (see Table 7). In the vector location, the user must write a Jump in-

When an interrupt source generates an interrupt request, the PC register is loaded with the address of the interrupt vector, which then causes a Jump to the relevant interrupt service routine, thus servicing the interrupt.

Interrupt are triggered by events either on external pins, or from the on-chip peripherals. Several events can be ORed on the same interrupt vector. On-chip peripherals have flag registers to determine which event triggered the interrupt.

Figure 17. Interrupts Block Diagram

# 5.9 EXTERNAL INTERRUPTS (I/O Ports)

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the GEN bit is set. These interrupts allow the processor to exit from STOP mode.

The external interrupt polarity is selected through the IOR register.

External interrupts are linked to vectors #1 and # 2.

Interrupt requests on vector #1 can be configured either as edge or level-sensitive using the LES bit in the IOR Register.

Interrupt requests from vector #2 are always edge sensitive. The edge polarity can be configured using the ESB bit in the IOR Register.

In edge-sensitive mode, a latch is set when a edge occurs on the interrupt source line and is cleared when the associated interrupt routine is started. So, an interrupt request can be stored until completion of the currently executing interrupt routine, before being processed. If several interrupt requests occurs before completion of the current interrupt routine, only the first request is stored.

Storing of interrupt requests is not possible in level sensitive mode. To be taken into account, the low level must be present on the interrupt pin when the MCU samples the line after instruction execution.

#### 5.9.1 Notes on using External Interrupts

#### ESB bit Spurious Interrupt on Vector #2

If a pin associated with interrupt vector #2 is configured as interrupt with pull-up, whenever vector #2 is configured to be rising edge sensitive (by setting the ESB bit in the IOR register), an interrupt is latched although a rising edge may not have occured on the associated pin. This is due to the vector #2 circuitry.The workaround is to discard this first interrupt request in the routine (using a flag for example).

# Masking of One Interrupt by Another on Vector #2.

When two or more port pins (associated with interrupt vector #2) are configured together as input with interrupt (falling edge sensitive), as long as one pin is stuck at '0', the other pin can never generate an interrupt even if an active edge occurs at this pin. The same thing occurs when one pin is stuck at '1' and interrupt vector #2 is configured as rising edge sensitive.

To avoid this the first pin must input a signal that goes back up to '1' right after the falling edge. Otherwise, in the interrupt routine for the first pin, deactivate the "input with interrupt" mode using the port control registers (DDR, OR, DR). An active edge on another pin can then be latched.

#### I/O port Configuration Spurious Interrupt on Vector #2

If a pin associated with interrupt vector #2 is in 'input with pull-up' state, a '0' level is present on the pin and the ESB bit = 0, when the I/O pin is configured as interrupt with pull-up by writing to the DDRx, ORx and DRx register bits, an interrupt is latched although a falling edge may not have occurred on the associated pin.

In the opposite case, if the pin is in interrupt with pull-up state , a 0 level is present on the pin and the ESB bit =1, when the I/O port is configured as input with pull-up by writing to the DDRx, ORx and DRx bits, an interrupt is latched although a rising edge may not have occurred on the associated pin.

# 5.11 REGISTER DESCRIPTION

#### INTERRUPT OPTION REGISTER (IOR)

Address: 0C8h — Write Only Reset status: 00h

| 7 |     |     |     |   |   |   | 0 |  |

|---|-----|-----|-----|---|---|---|---|--|

| - | LES | ESB | GEN | - | - | - | - |  |

**Caution:** This register is write-only and cannot be accessed by single-bit operations (SET, RES, DEC,...).

Bit 7 =Reserved, must be cleared.

Bit 6 = LES Level/Edge Selection bit.

0: Falling edge sensitive mode is selected for interrupt vector #1

#### Table 7. Interrupt Mapping

1: Low level sensitive mode is selected for interrupt vector #1

Bit 5 = **ESB** Edge Selection bit. 0: Falling edge mode on interrupt vector #2 1: Rising edge mode on interrupt vector #2

Bit 4 = **GEN** *Global Enable Interrupt.* 0: Disable all maskable interrupts 1: Enable all maskable interrupts

**Note:** When the GEN bit is cleared, the NMI interrupt is active but cannot be used to exit from STOP or WAIT modes.

Bits 3:0 = Reserved, must be cleared.

| Vector<br>number | Source<br>Block | Description            | Register<br>Label | Flag | Exit<br>from<br>STOP | Vector<br>Address | Priority<br>Order |

|------------------|-----------------|------------------------|-------------------|------|----------------------|-------------------|-------------------|

|                  | RESET           | Reset                  | N/A               | N/A  | yes                  | FFEh-FFFh         |                   |

| Vector #0        | NMI             | Non Maskable Interrupt | N/A               | N/A  | yes                  | FFCh-FFDh         | Highest           |

|                  |                 |                        |                   |      |                      |                   | Priority          |

|                  | NOT USED        |                        |                   |      |                      |                   |                   |

| Vector #1        | Port A          | Ext. Interrupt Port A  | N/A               | N/A  | yes                  | FF6h-FF7h         |                   |

| Vector #2        | Port B          | Ext. Interrupt Port B  | N/A               | N/A  | yes                  | FF4h-FF5h         |                   |

| Vector #3        | TIMER           | Timer underflow        | TSCR              | TMZ  | yes                  | FF2h-FF3h         | Lowest            |

| Vector #4        | ADC *           | End Of Conversion      | ADCR              | EOC  | no                   | FF0h-FF1h         | Priority          |

\* Depending on device. See device summary on page 1.

# 6.4 NOTES RELATED TO WAIT AND STOP MODES

#### 6.4.1 Exit from Wait and Stop Modes

#### 6.4.1.1 NMI Interrupt

It should be noted that when the GEN bit in the IOR register is low (interrupts disabled), the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

## 6.4.1.2 Restart Sequence

When the MCU exits from WAIT or STOP mode, it should be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) prior to entering WAIT or STOP mode, as well as on the interrupt type.

Normal Mode. If the MCU was in the main routine when the WAIT or STOP instruction was executed, exit from Stop or Wait mode will occur as soon as an interrupt occurs; the related interrupt routine is executed and, on completion, the instruction which follows the STOP or WAIT instruction is then executed, providing no other interrupts are pending.

Non Maskable Interrupt Mode. If the STOP or WAIT instruction has been executed during execution of the non-maskable interrupt routine, the MCU exits from Stop or Wait mode as soon as an interrupt occurs: the instruction which follows the STOP or WAIT instruction is executed, and the MCU remains in non-maskable interrupt mode, even if another interrupt has been generated.

**Normal Interrupt Mode.** If the MCU was in interrupt mode before the STOP or WAIT instruction was executed, it exits from STOP or WAIT mode

57

as soon as an interrupt occurs. Nevertheless, two cases must be considered:

- If the interrupt is a normal one, the interrupt routine in which the WAIT or STOP mode was entered will be completed, starting with the execution of the instruction which follows the STOP or the WAIT instruction, and the MCU is still in interrupt mode. At the end of this routine pending interrupts will be serviced according to their priority.

- In the event of a non-maskable interrupt, the non-maskable interrupt service routine is processed first, then the routine in which the WAIT or STOP mode was entered will be completed by executing the instruction following the STOP or WAIT instruction. The MCU remains in normal interrupt mode.

#### 6.4.2 Recommended MCU Configuration

For lowest power consumption during RUN or WAIT modes, the user software must configure the MCU as follows:

- Configure unused I/Os as output push-pull low mode

- Place all peripherals in their power down modes before entering STOP mode

- Select the Low Frequency Auxiliary Oscillator (provided this runs at a lower frequency than the main oscillator).

The WAIT and STOP instructions are not executed if an enabled interrupt request is pending.

## I/O PORTS (Cont'd)

# 7.2.5 Instructions NOT to be used to access Port Data registers (SET, RES, INC and DEC)

DO NOT USE READ-MODIFY-WRITE INSTRUC-TIONS (SET, RES, INC and DEC) ON PORT DATA REGISTERS IF ANY PIN OF THE PORT IS CONFIGURED IN INPUT MODE.

These instructions make an implicit read and write back of the entire register. In port input mode, however, the data register reads from the input pins directly, and not from the data register latches. Since data register information in input mode is used to set the characteristics of the input pin (interrupt, pull-up, analog input), these may be unintentionally reprogrammed depending on the state of the input pins.

As a general rule, it is better to only use single bit instructions on data registers when the whole (8bit) port is in output mode. In the case of inputs or of mixed inputs and outputs, it is advisable to keep a copy of the data register in RAM. Single bit instructions may then be used on the RAM copy, after which the whole copy register can be written to the port data register:

SET bit, datacopy LD a, datacopy LD DRA, a

#### 7.2.6 Recommendations

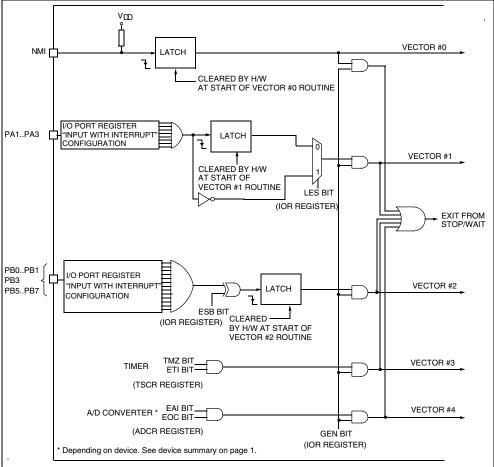

#### 1. Safe I/O State Switching Sequence

Switching the I/O ports from one state to another should be done in a sequence which ensures that no unwanted side effects can occur. The recommended safe transitions are illustrated in Figure 24 The Interrupt Pull-up to Input Analog transition (and vice-vesra) is potentially risky and should be avoided when changing the I/O operating mode.

#### 2. Handling Unused Port Bits

On ports that have less than 8 external pins connected:

- Leave the unbonded pins in reset state and do not change their configuration.

- Do not use instructions that act on a whole port register (INC, DEC, or read operations). Unavailable bits must be masked by software (AND instruction). Thus, when a read operation performed on an incomplete port is followed by a comparison, use a mask.

#### 3. High Impedance Input

On any CMOS device, it is not recommended to connect high impedance on input pins. The choice of these impedance has to be done with respect to the maximum leakage current defined in the datasheet. The risk is to be close or out of specification on the input levels applied to the device.

#### 7.3 LOW POWER MODES

The WAIT and STOP instructions allow the ST62xx to be used in situations where low power consumption is needed. The lowest power consumption is achieved by configuring I/Os in output push-pull low mode.

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| STOP | No effect on I/O ports. External interrupts cause the device to exit from STOP mode. |

#### 7.4 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR, DR and OR registers (see Table 8) and the GEN-bit in the IOR register is set.

Note \*. xxx = DDR, OR, DR Bits respectively

# 8 ON-CHIP PERIPHERALS

# 8.1 WATCHDOG TIMER (WDG)

#### 8.1.1 Introduction

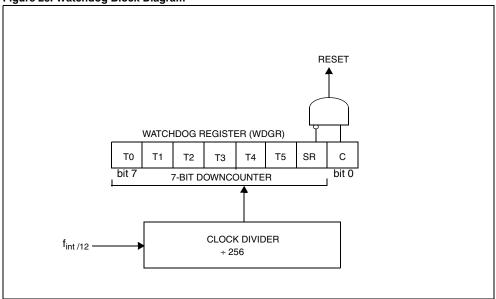

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless the program refreshes the counter's contents before the SR bit becomes cleared.

#### Figure 25. Watchdog Block Diagram

#### 8.1.2 Main Features

- Programmable timer (64 steps of 3072 clock cycles)

- Software reset

- Reset (if watchdog activated) when the SR bit reaches zero

- Hardware or software watchdog activation selectable by option bit (Refer to the option bytes section)

# WATCHDOG TIMER (Cont'd)

These instructions test the C bit and reset the MCU (i.e. disable the Watchdog) if the bit is set (i.e. if the Watchdog is active), thus disabling the Watchdog.

For more information on the use of the watchdog, please read application note AN1015.

**Note:** This note applies only when the watchdog is used as a standard timer. It is recommended to read the counter twice, as it may sometimes return an invalid value if the read is performed while the counter is decremented (counter bits in transient state). To validate the return value, both values read must be equal. The counter decrements every 384  $\mu$ s at 8 MHz f<sub>osc</sub>.

## 8.1.5 Low Power Modes

| as a WAIT. If, however, the<br>nter is frozen and the CPU en-<br>atchdog resumes its activity. |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

#### 8.1.6 Interrupts

None.

# A/D CONVERTER (Cont'd)

# 8.3.3 Functional Description

## 8.3.3.1 Analog Power Supply

The high and low level reference voltage pins are internally connected to the  $V_{DD}$  and  $V_{SS}$  pins.

Conversion accuracy may therefore be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

#### 8.3.3.2 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than or equal to  $V_{DDA}$  (high-level voltage reference) then the conversion result in the DR register is FFh (full scale) without overflow indication.

If input voltage ( $V_{AIN}$ ) is lower than or equal to  $V_{SSA}$  (low-level voltage reference) then the conversion result in the DR register is 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADR register. The accuracy of the conversion is described in the parametric section.

R<sub>AIN</sub> is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the allocated time. Refer to the electrical characteristics chapter for more details.

With an oscillator clock frequency less than 1.2MHz, conversion accuracy is decreased.

## 8.3.3.3 Analog Input Selection

57/

Selection of the input pin is done by configuring the related I/O line as an analog input via the Data Direction, Option and Data registers (refer to I/O ports description for additional information).

**Caution:** Only one I/O line must be configured as an analog input at any time. The user must avoid any situation in which more than one I/O pin is selected as an analog input simultaneously, because they will be shorted internally.

#### 8.3.3.4 Software Procedure

Refer to the Control register (ADCR) and Data register (ADR) in Section 8.3.7 for the bit definitions.

#### Analog Input Configuration

The analog input must be configured through the Port Control registers (DDRx, ORx and DRx). Refer to the I/O port chapter.

#### ADC Configuration

In the ADCR register:

- Reset the PDS bit to power on the ADC. This bit must be set at least one instruction before the beginning of the conversion to allow stabilisation of the A/D converter.

- Set the EAI bit to enable the ADC interrupt if needed.

#### ADC Conversion

In the ADCR register:

Set the STA bit to start a conversion. This automatically clears (resets to "0") the End Of Conversion Bit (EOC).

When a conversion is complete

- The EOC bit is set by hardware to flag that conversion is complete and that the data in the ADC data conversion register is valid.

- An interrupt is generated if the EAI bit was set

Setting the STA bit will start a new count and will clear the EOC bit (thus clearing the interrupt condition)

#### Note:

Setting the STA bit must be done by a different instruction from the instruction that powers-on the ADC (setting the PDS bit) in order to make sure the voltage to be converted is present on the pin.

Each conversion has to be separately initiated by writing to the STA bit.

The STA bit is continuously scanned so that, if the user sets it to "1" while a previous conversion is in progress, a new conversion is started before completing the previous one. The start bit (STA) is a write only bit, any attempt to read it will show a logical "0".

#### **INSTRUCTION SET** (Cont'd)

Arithmetic and Logic. These instructions are used to perform arithmetic calculations and logic operations. In AND, ADD, CP, SUB instructions one operand is always the accumulator while, depending on the addressing mode, the other can be either a data space memory location or an imme-diate value. In CLR, DEC, INC instructions the op-erand can be any of the 256 data space address-es. In COM, RLC, SLA the operand is always the accumulator.

#### Table 16. Arithmetic & Logic Instructions

| Instruction | Addressing Mede | Butes | Cualas | Fla      | igs |

|-------------|-----------------|-------|--------|----------|-----|

| instruction | Addressing Mode | Bytes | Cycles | Z        | С   |

| ADD A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| ADD A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| ADD A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| ADDI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

| AND A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| AND A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| AND A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| ANDI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

| CLR A       | Short Direct    | 2     | 4      | Δ        | Δ   |

| CLR r       | Direct          | 3     | 4      | *        | *   |

| COM A       | Inherent        | 1     | 4      | Δ        | Δ   |

| CP A, (X)   | Indirect        | 1     | 4      | Δ        | Δ   |

| CP A, (Y)   | Indirect        | 1     | 4      | Δ        | Δ   |

| CP A, rr    | Direct          | 2     | 4      | Δ        | Δ   |

| CPI A, #N   | Immediate       | 2     | 4      | Δ        | Δ   |

| DEC X       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC Y       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC V       | Short Direct    | 1     | 4      | $\Delta$ | *   |

| DEC W       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC A       | Direct          | 2     | 4      | Δ        | *   |

| DEC rr      | Direct          | 2     | 4      | Δ        | *   |

| DEC (X)     | Indirect        | 1     | 4      | $\Delta$ | *   |

| DEC (Y)     | Indirect        | 1     | 4      | Δ        | *   |

| INC X       | Short Direct    | 1     | 4      | Δ        | *   |

| INC Y       | Short Direct    | 1     | 4      | Δ        | *   |

| INC V       | Short Direct    | 1     | 4      | Δ        | *   |

| INC W       | Short Direct    | 1     | 4      | Δ        | *   |

| INC A       | Direct          | 2     | 4      | Δ        | *   |

| INC rr      | Direct          | 2     | 4      | $\Delta$ | *   |

| INC (X)     | Indirect        | 1     | 4      | Δ        | *   |

| INC (Y)     | Indirect        | 1     | 4      | Δ        | *   |

| RLC A       | Inherent        | 1     | 4      | Δ        | Δ   |

| SLA A       | Inherent        | 2     | 4      | Δ        | Δ   |

| SUB A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| SUB A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| SUB A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| SUBI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

#### Notes:

X,Y Index Registers V, W Short Direct Registers

Affected Λ

# Immediate data (stored in ROM memory)

Not Affected

rr Data space register

# **10 ELECTRICAL CHARACTERISTICS**

# **10.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $\ensuremath{\mathsf{V}_{SS}}\xspace.$

## 10.1.1 Minimum and Maximum Values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 10.1.2 Typical Values

Unless otherwise specified, typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (for the  $4.5V \pounds_{DD}$ \$.0V voltage range) and V<sub>DD</sub>=3.3V (for the  $3V \pounds_{DD}$ \$.6V voltage range). They are given only as design guidelines and are not tested.

#### 10.1.3 Typical Curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

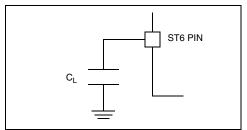

#### 10.1.4 Loading Capacitor

The loading conditions used for pin parameter measurement is shown in Figure 30.

#### Figure 30. Pin Loading Conditions

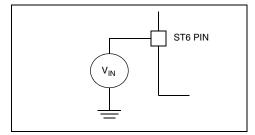

#### 10.1.5 Pin Input Voltage

The input voltage measurement on a pin of the device is described in Figure 31.

#### Figure 31. Pin Input Voltage

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

## 10.4.2 WAIT Modes

| Symbol          | Parameter                                                                                      |                          |                                                 | Conditions                                                                                                                                                     | Typ 1)                          | Max <sup>2)</sup>               | Unit |

|-----------------|------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------|

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 38)    |                          | devices                                         | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz                                | 330<br>350<br>370<br>410<br>480 | 550<br>600<br>650<br>700<br>800 |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) | 4.5VÝ <sub>DD</sub> ⑤.0V | .5V <sup>4/</sup> DD <sup>6</sup> .0V<br>OTP de | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 18<br>26<br>41<br>57<br>70      | 60<br>80<br>120<br>180<br>200   |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>(see Figure 40)                                   |                          | ROM devices                                     | $\begin{array}{l} f_{OSC}=32kHz\\ f_{OSC}=1MHz\\ f_{OSC}=2MHz\\ f_{OSC}=2MHz\\ f_{OSC}=4MHz\\ f_{OSC}=8MHz \end{array}$                                        | 190<br>210<br>240<br>280<br>350 | 300<br>350<br>400<br>500<br>600 |      |

| I <sub>DD</sub> | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 38)    |                          | devices                                         | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz                                | 80<br>90<br>100<br>120<br>150   | 120<br>140<br>150<br>200<br>250 | μA   |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) |                          | OTP d                                           | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 5<br>8<br>16<br>18<br>20        | 30<br>40<br>50<br>60<br>100     |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 40)    |                          | ROM devices                                     | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 60<br>65<br>80<br>100<br>130    | 100<br>110<br>120<br>150<br>210 |      |

#### Notes:

67/

1. Typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (4.5V $\$V_{DD}$ \$.0V range) and V<sub>DD</sub>=3.3V (3V $\$V_{DD}$ \$.6V range).

Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>OSC</sub> max.

All I/O pins in input with pull-up mode (no load), all peripherals in reset state; clock input (OSC<sub>IN</sub>) driven by external square wave, OSG and LVD disabled.

# EMC CHARACTERISTICS (Cont'd)

#### 10.7.2 Absolute Electrical Sensitivity

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the AN1181 application note.

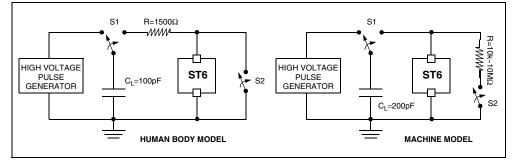

# 10.7.2.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends of the number of supply pins of the device (3 parts\*(n+1) supply pin). Two models are usually simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard. See Figure 51 and the following test sequences.

#### Human Body Model Test Sequence

- CL is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to R.

- A discharge from CL through R (body resistance) to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

#### Machine Model Test Sequence

- CL is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to ST6.

- A discharge from C<sub>L</sub> to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

- R (machine resistance), in series with S2, ensures a slow discharge of the ST6.

#### Absolute Maximum Ratings

| Symbol                | Ratings                                                | Conditions            | Maximum value 1) | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 2000             | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>A</sub> =+25°C | 200              | v    |

#### Notes:

1. Data based on characterization results, not tested in production.

# Figure 51. Typical Equivalent ESD Circuits

# EMC CHARACTERISTICS (Cont'd)

# 10.7.3 ESD Pin Protection Strategy

To protect an integrated circuit against Electro-Static Discharge the stress must be controlled to prevent degradation or destruction of the circuit elements. The stress generally affects the circuit elements which are connected to the pads but can also affect the internal devices when the supply pads receive the stress. The elements to be protected must not receive excessive current, voltage or heating within their structure.

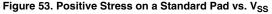

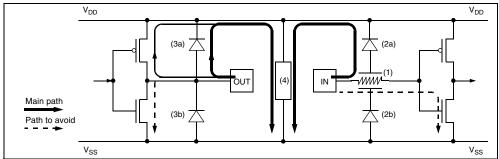

An ESD network combines the different input and output ESD protections. This network works, by allowing safe discharge paths for the pins subjected to ESD stress. Two critical ESD stress cases are presented in Figure 53 and Figure 54 for standard pins.

#### Standard Pin Protection

To protect the output structure the following elements are added:

- A diode to  $V_{DD}$  (3a) and a diode from  $V_{SS}$  (3b)

- A protection device between  $V_{DD}$  and  $V_{SS}$  (4)

To protect the input structure the following elements are added:

- A resistor in series with the pad (1)

- A diode to  $V_{DD}$  (2a) and a diode from  $V_{SS}$  (2b)

- A protection device between  $V_{DD}$  and  $V_{SS}$  (4)

Figure 54. Negative Stress on a Standard Pad vs. VDD

| Symbol            | Ratings                                                                     | Value           | Unit |

|-------------------|-----------------------------------------------------------------------------|-----------------|------|

| R <sub>thJA</sub> | Package thermal resistance (junction to ambient)<br>DIP16<br>SO16<br>SSOP16 | 90<br>90<br>125 | °C/W |

| PD                | Power dissipation <sup>1)</sup>                                             | 500             | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>                                  | 150             | °C   |

## **11.2 THERMAL CHARACTERISTICS**

#### Notes:

- 1. The power dissipation is obtained from the formula  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD}xV_{DD}$ ) and  $P_{PORT}$  is the port power dissipation determined by the user.

- 2. The average chip-junction temperature can be obtained from the formula  $T_J = T_A + P_D x$  RthJA.

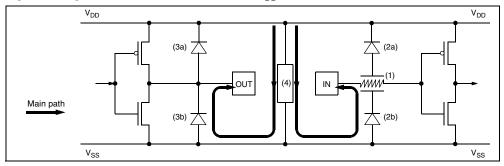

# 11.5 ORDERING INFORMATION

The following section deals with the procedure for transfer of customer codes to STMicroelectronics and also details the ST6 factory coded device type.

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to www.st.com or contact the ST Sales Office nearest to you.

Figure 72. ST6 Factory Coded Device Types

# TRANSFER OF CUSTOMER CODE (Cont'd)

# 11.6.2 ROM VERSION

The ST6200C, 01C and 03C are mask programmed ROM version of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, selecting as ROM options the options defined in the programmable option byte of the OTP version.

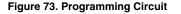

Note: ZPD15 is used for overvoltage protection

**ROM Readout Protection.** If the ROM READOUT PROTECTION option is selected, a protection fuse can be blown to prevent any access to the program memory content.

In case the user wants to blow this fuse, high voltage must be applied on the  $V_{\mbox{\scriptsize PP}}$  pin.

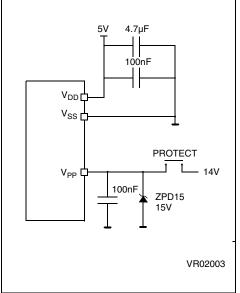

Figure 74. Programming wave form

# **12 DEVELOPMENT TOOLS**

STMicroelectronics offers a range of hardware and software development tools for the ST6 microcontroller family. Full details of tools available for the ST6 from third party manufacturers can be obtain from the STMicroelectronics Internet site: → http://www.st.com.

| Third Party <sup>1)</sup> | Designation                                                                                                                                                                                                                                                                                                       | CT Coles Tures     | Web eite eddrec -                                   |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------|

| Inira Party "             | Designation                                                                                                                                                                                                                                                                                                       | ST Sales Type      | Web site address                                    |

| ACTUM                     | ST-REALIZER II: Graphical Schematic<br>based Development available from<br>STMicroelectronics.                                                                                                                                                                                                                    | STREALIZER-II      | http://www.actum.com/                               |

| CEIBO                     | Low cost emulator available from CEI-<br>BO.                                                                                                                                                                                                                                                                      |                    | http://www.ceibo.com/                               |

| RAISONANCE                | This tool includes in the same environ-<br>ment: an assembler, linker, C compiler,<br>debugger and simulator. The assembler<br>package (plus limited C compiler) is free<br>and can be downloaded from raisonance<br>web site. The full version is available<br>both from STMicroelectronics and Raiso-<br>nance. | ST6RAIS-SWC/<br>PC | http://www.raisonance.com/                          |

| SOFTEC                    | High end emulator available from SOFTEC.                                                                                                                                                                                                                                                                          |                    | http://www.softecmicro.com/                         |

|                           | Gang programmer available from<br>SOFTEC.                                                                                                                                                                                                                                                                         |                    |                                                     |

| ADVANCED EQUIPMENT        | Single and gang programmers                                                                                                                                                                                                                                                                                       |                    | http://www.aec.com.tw/                              |

| ADVANCED TRANSDATA        |                                                                                                                                                                                                                                                                                                                   |                    | http://www.adv-transdata.com/                       |

| BP MICROSYSTEMS           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.bpmicro.com/                             |

| DATA I/O                  |                                                                                                                                                                                                                                                                                                                   |                    | http://www.data-io.com/                             |

| DATAMAN                   |                                                                                                                                                                                                                                                                                                                   |                    | http://www.dataman.com/                             |

| EE TOOLS                  |                                                                                                                                                                                                                                                                                                                   |                    | http://www.eetools.com/                             |

| ELNEC                     |                                                                                                                                                                                                                                                                                                                   |                    | http://www.elnec.com/                               |

| HI-LO SYSTEMS             |                                                                                                                                                                                                                                                                                                                   |                    | http://www.hilosystems.com.tw/                      |

| ICE TECHNOLOGY            |                                                                                                                                                                                                                                                                                                                   |                    | http://www.icetech.com/                             |

| LEAP                      |                                                                                                                                                                                                                                                                                                                   |                    | http://www.leap.com.tw/                             |

| LLOYD RESEARCH            |                                                                                                                                                                                                                                                                                                                   |                    | http://www.lloyd-research.com/                      |

| LOGICAL DEVICES           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.chipprogram-<br>mers.com/                |

| MQP ELECTRONICS           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.mqp.com/                                 |

| NEEDHAMS<br>ELECTRONICS   |                                                                                                                                                                                                                                                                                                                   |                    | http://www.needhams.com/                            |

| STAG PROGRAMMERS          |                                                                                                                                                                                                                                                                                                                   |                    | http://www.stag.co.uk/                              |

|                           |                                                                                                                                                                                                                                                                                                                   | 1                  |                                                     |

| SYSTEM GENERAL CORP       |                                                                                                                                                                                                                                                                                                                   |                    | http://www.sg.com.tw                                |

| TRIBAL MICROSYSTEMS       |                                                                                                                                                                                                                                                                                                                   |                    | http://www.sg.com.tw<br>http://www.tribalmicro.com/ |

Note 1: For latest information on third party tools, please visit our Internet site: → http://www.st.com.

# **13 ST6 APPLICATION NOTES**

| IDENTIFICATION        | DESCRIPTION                                                              |  |  |

|-----------------------|--------------------------------------------------------------------------|--|--|

| MOTOR CONTROL         |                                                                          |  |  |

| AN392                 | MICROCONTROLLER AND TRIACS ON THE 110/240V MAINS                         |  |  |

| AN414                 | CONTROLLING A BRUSH DC MOTOR WITH AN ST6265 MCU                          |  |  |

| AN416                 | SENSORLESS MOTOR DRIVE WITH THE ST62 MCU + TRIAC                         |  |  |

| AN422                 | IMPROVES UNIVERSAL MOTOR DRIVE                                           |  |  |

| AN863                 | IMPROVED SENSORLESS CONTROL WITH THE ST62 MCU FOR UNIVERSAL MOTOR        |  |  |

| BATTERY MANAGEMENT    |                                                                          |  |  |

| AN417                 | FROM NICD TO NIMH FAST BATTERY CHARGING                                  |  |  |

| AN433                 | ULTRA FAST BATTERY CHARGER USING ST6210 MICROCONTROLLER                  |  |  |

| AN859                 | AN INTELLIGENT ONE HOUR MULTICHARGER FOR Li-Ion, NIMH and NICd BATTERIES |  |  |

| HOME APPLIANCE        |                                                                          |  |  |

| AN674                 | MICROCONTROLLERS IN HOME APPLIANCES: A SOFT REVOLUTION                   |  |  |

| AN885                 | ST62 MICROCONTROLLERS DRIVE HOME APPLIANCE MOTOR TECHNOLOGY              |  |  |

| GRAPHICAL DESIGN      |                                                                          |  |  |

| AN676                 | BATTERY CHARGER USING THE ST6-REALIZER                                   |  |  |

| AN677                 | PAINLESS MICROCONTROLLER CODE BY GRAPHICAL APPLICATION DESCRIPTION       |  |  |

| AN839                 | ANALOG MULTIPLE KEY DECODING USING THE ST6-REALIZER                      |  |  |

| AN840                 | CODED LOCK USING THE ST6-REALIZER                                        |  |  |

| AN841                 | A CLOCK DESIGN USING THE ST6-REALIZER                                    |  |  |

| AN842                 | 7 SEGMENT DISPLAY DRIVE USING THE ST6-REALIZER                           |  |  |

| COST REDUCTION        |                                                                          |  |  |

| AN431                 | USING ST6 ANALOG INPUTS FOR MULTIPLE KEY DECODING                        |  |  |

| AN594                 | DIRECT SOFTWARE LCD DRIVE WITH ST621X AND ST626X                         |  |  |

| AN672                 | OPTIMIZING THE ST6 A/D CONVERTER ACCURACY                                |  |  |

| AN673                 | REDUCING CURRENT CONSUMPTION AT 32KHZ WITH ST62                          |  |  |

| DESIGN IMPROVEMENTS   |                                                                          |  |  |

| AN420                 | EXPANDING A/D RESOLUTION OF THE ST6 A/D CONVERTER                        |  |  |

| AN432                 | USING ST62XX I/O PORTS SAFELY                                            |  |  |

| AN434                 | MOVEMENT DETECTOR CONCEPTS FOR NOISY ENVIRONMENTS                        |  |  |

| AN435                 | DESIGNING WITH MICROCONTROLLERS IN NOISY ENVIRONMENTS                    |  |  |

| AN669                 | SIMPLE RESET CIRCUITS FOR THE ST6                                        |  |  |

| AN670                 | OSCILLATOR SELECTION FOR ST62                                            |  |  |

| AN671                 | PREVENTION OF DATA CORRUPTION IN ST6 ON-CHIP EEPROM                      |  |  |

| AN911                 | ST6 MICRO IS EMC CHAMPION                                                |  |  |

| AN975                 | UPGRADING FROM ST625X/6XB TO ST625X/6XC                                  |  |  |

| AN1015                | SOFTWARE TECHNIQUES FOR IMPROVING ST6 EMC PERFORMANCE                    |  |  |

| PERIPHERAL OPERATIONS |                                                                          |  |  |

| AN590                 | PWM GENERATION WITH ST62 AUTO-RELOAD TIMER                               |  |  |

| AN591                 | INPUT CAPTURE WITH ST62 AUTO-RELOAD TIMER                                |  |  |

| AN592                 | PLL GENERATION USING THE ST62 AUTO-RELOAD TIMER                          |  |  |

| AN593                 | ST62 IN-CIRCUIT PROGRAMMING                                              |  |  |

| AN678                 | LCD DRIVING WITH ST6240                                                  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WAR-RANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURIS-DICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE. ST PRODUCTS ARE NOT RECOM-

UNLESS EXPRESSEY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOM-MENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLI-CATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com