Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Obsolete                                                           |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | -                                                                  |

| Peripherals                | LVD, POR, WDT                                                      |

| Number of I/O              | 9                                                                  |

| Program Memory Size        | 1KB (1K x 8)                                                       |

| Program Memory Type        | OTP                                                                |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 64 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | -                                                                  |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                            |

| Supplier Device Package    | -                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t03cb6 |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **5 CLOCKS, SUPPLY AND RESET**

# 5.1 CLOCK SYSTEM

The main oscillator of the MCU can be driven by any of these clock sources:

- external clock signal

- external AT-cut parallel-resonant crystal

- external ceramic resonator

- external RC network (R<sub>NET</sub>).

In addition, an on-chip Low Frequency Auxiliary Oscillator (LFAO) is available as a back-up clock system or to reduce power consumption.

An optional Oscillator Safeguard (OSG) filters spikes from the oscillator lines, and switches to the LFAO backup oscillator in the event of main oscillator failure. It also automatically limits the internal clock frequency ( $f_{\rm INT}$ ) as a function of  $V_{DD}$ , in order to guarantee correct operation. These functions are illustrated in Figure 10, and Figure 11.

Table 5 illustrates various possible oscillator configurations using an external crystal or ceramic resonator, an external clock input, an external resistor ( $R_{NET}$ ), or the lowest cost solution using only the LFAO.

For more details on configuring the clock options, refer to the Option Bytes section of this document.

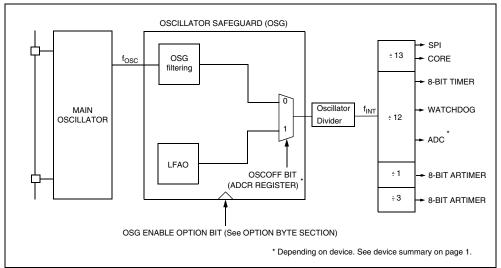

The internal MCU clock frequency ( $f_{INT}$ ) is divided by 12 to drive the Timer, the Watchdog timer and the A/D converter, by 13 to drive the CPU core and the SPI and by 1 or 3 to drive the ARTIMER, as shown in Figure 9.

With an 8 MHz oscillator, the fastest CPU cycle is therefore  $1.625\mu s$ .

A CPU cycle is the smallest unit of time needed to execute any operation (for instance, to increment the Program Counter). An instruction may require two, four, or five CPU cycles for execution.

47/

# Figure 9. Clock Circuit Block Diagram

# CLOCK SYSTEM (Cont'd)

# 5.1.3 Low Frequency Auxiliary Oscillator (LFAO)

The Low Frequency Auxiliary Oscillator has three main purposes. Firstly, it can be used to reduce power consumption in non timing critical routines. Secondly, it offers a fully integrated system clock, without any external components. Lastly, it acts as a backup oscillator in case of main oscillator failure.

This oscillator is available when the OSG ENA-BLED option is selected in the option byte (refer to the Option Bytes section of this document). In this case, it automatically starts one of its periods after the first missing edge of the main oscillator, whatever the reason for the failure (main oscillator defective, no clock circuitry provided, main oscillator switched off...). See Figure 11.

User code, normal interrupts, WAIT and STOP instructions, are processed as normal, at the reduced  $f_{LFAO}$  frequency. The A/D converter accuracy is decreased, since the internal frequency is below 1.2 MHz.

At power on, until the main oscillator starts, the reset delay counter is driven by the LFAO. If the main oscillator starts before the 2048 cycle delay has elapsed, it takes over. The Low Frequency Auxiliary Oscillator is automatically switched off as soon as the main oscillator starts.

# 5.1.4 Register Description

### ADC CONTROL REGISTER (ADCR)

Address: 0D1h — Read/Write Reset value: 0100 0000 (40h)

| 7         |           |           |           |            | 0         |

|-----------|-----------|-----------|-----------|------------|-----------|

| ADCR<br>7 | ADCR<br>6 | ADCR<br>5 | ADCR<br>4 | OSC<br>OFF | ADCR<br>0 |

# Bit 7:3, 1:0 = ADCR[7:3], ADCR[1:0] ADC Control Register.

These bits are used to control the A/D converter (if available on the device) otherwise they are not used.

Bit 2 = OSCOFF Main Oscillator Off.

0: Main oscillator enabled

1: Main oscillator disabled

**Note:** The OSG must be enabled using the OS-GEN option in the Option Byte, otherwise the OS-COFF setting has no effect.

# 6.4 NOTES RELATED TO WAIT AND STOP MODES

## 6.4.1 Exit from Wait and Stop Modes

## 6.4.1.1 NMI Interrupt

It should be noted that when the GEN bit in the IOR register is low (interrupts disabled), the NMI interrupt is active but cannot cause a wake up from STOP/WAIT modes.

# 6.4.1.2 Restart Sequence

When the MCU exits from WAIT or STOP mode, it should be noted that the restart sequence depends on the original state of the MCU (normal, interrupt or non-maskable interrupt mode) prior to entering WAIT or STOP mode, as well as on the interrupt type.

Normal Mode. If the MCU was in the main routine when the WAIT or STOP instruction was executed, exit from Stop or Wait mode will occur as soon as an interrupt occurs; the related interrupt routine is executed and, on completion, the instruction which follows the STOP or WAIT instruction is then executed, providing no other interrupts are pending.

Non Maskable Interrupt Mode. If the STOP or WAIT instruction has been executed during execution of the non-maskable interrupt routine, the MCU exits from Stop or Wait mode as soon as an interrupt occurs: the instruction which follows the STOP or WAIT instruction is executed, and the MCU remains in non-maskable interrupt mode, even if another interrupt has been generated.

**Normal Interrupt Mode.** If the MCU was in interrupt mode before the STOP or WAIT instruction was executed, it exits from STOP or WAIT mode

57

as soon as an interrupt occurs. Nevertheless, two cases must be considered:

- If the interrupt is a normal one, the interrupt routine in which the WAIT or STOP mode was entered will be completed, starting with the execution of the instruction which follows the STOP or the WAIT instruction, and the MCU is still in interrupt mode. At the end of this routine pending interrupts will be serviced according to their priority.

- In the event of a non-maskable interrupt, the non-maskable interrupt service routine is processed first, then the routine in which the WAIT or STOP mode was entered will be completed by executing the instruction following the STOP or WAIT instruction. The MCU remains in normal interrupt mode.

#### 6.4.2 Recommended MCU Configuration

For lowest power consumption during RUN or WAIT modes, the user software must configure the MCU as follows:

- Configure unused I/Os as output push-pull low mode

- Place all peripherals in their power down modes before entering STOP mode

- Select the Low Frequency Auxiliary Oscillator (provided this runs at a lower frequency than the main oscillator).

The WAIT and STOP instructions are not executed if an enabled interrupt request is pending.

# I/O PORTS (Cont'd)

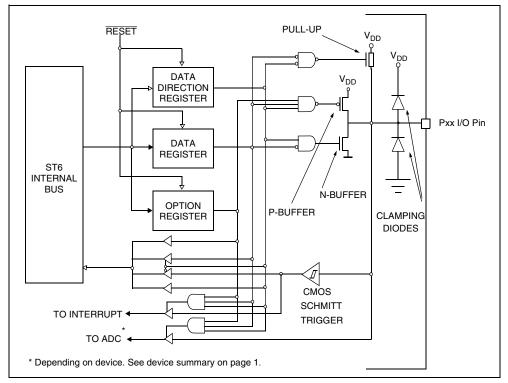

# Figure 23. I/O Port Block Diagram

# Table 8. I/O Port Configurations

| DDR | OR | DR | Mode   | Option                                       |  |  |  |

|-----|----|----|--------|----------------------------------------------|--|--|--|

| 0   | 0  | 0  | Input  | Input With pull-up, no interrupt             |  |  |  |

| 0   | 0  | 1  | Input  | ut No pull-up, no interrupt                  |  |  |  |

| 0   | 1  | 0  | Input  | With pull-up and with interrupt              |  |  |  |

| 0   | 1  | 1  | Input  | Analog input (when available)                |  |  |  |

| 1   | 0  | х  | Output | Open-drain output (20mA sink when available) |  |  |  |

| 1   | 1  | х  | Output | Push-pull output (20mA sink when available)  |  |  |  |

Note: x = Don't care

67/

# I/O PORTS (Cont'd)

### 7.5 REGISTER DESCRIPTION

#### DATA REGISTER (DR)

Port x Data Register DRx with x = A or B. Address DRA: 0C0h - Read/Write Address DRB: 0C1h - Read/Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7:0 = D[7:0] Data register bits.

Reading the DR register returns either the DR register latch content (pin configured as output) or the digital value applied to the I/O pin (pin configured as input).

**Caution:** In input mode, modifying this register will modify the I/O port configuration (see Table 8).

Do not use the Single bit instructions on I/O port data registers. See (Section 7.2.5).

# DATA DIRECTION REGISTER (DDR)

Port x Data Direction Register DDRx with x = A or B.

Address DDRA: 0C4h - Read/Write Address DDRB: 0C5h - Read/Write Reset Value: 0000 0000 (00h)

| /   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DD7 | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

#### Table 10. I/O Port Register Map and Reset Values

#### Bit 7:0 = DD[7:0] Data direction register bits.

The DDR register gives the input/output direction configuration of the pins. Each bit is set and cleared by software. 0: Input mode 1: Output mode

#### **OPTION REGISTER (OR)**

Port x Option Register ORx with x = A or B.

Address ORA: 0CCh - Read/Write Address ORB: 0CDh - Read/Write Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| 07 | O6 | O5 | O4 | O3 | 02 | 01 | 00 |

Bit 7:0 = **O**[7:0] Option register bits.

The OR register allows to distinguish in output mode if the push-pull or open drain configuration is selected.

#### Output mode:

0: Open drain output(with P-Buffer deactivated) 1: Push-pull Output

Input mode: See Table 8.

Each bit is set and cleared by software.

**Caution:** Modifying this register, will also modify the I/O port configuration in input mode. (see Table 8).

| Address<br>(Hex.) | Register<br>Label        | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0   |     |

|-------------------|--------------------------|-------|-----|---|---|---|---|---|-----|-----|

|                   | t Value<br>ort registers | 0     | 0   | 0 | 0 | 0 | 0 | 0 | 0   |     |

| 0C0h              | DRA                      | MCD   | MSB |   |   |   |   |   |     | LSB |

| 0C1h              | DRB                      | WIGD  |     |   |   |   |   |   | LOD |     |

| 0C4h              | DDRA                     | MSB   |     |   |   |   |   |   | LSB |     |

| 0C5h              | DDRB                     | IVISB |     |   |   |   |   |   | LOD |     |

| 0CCh              | ORA                      | MSB   |     |   |   |   |   |   | LSB |     |

| 0CDh              | ORB                      | NISD  |     |   |   |   |   |   | LOD |     |

# WATCHDOG TIMER (Cont'd)

# 8.1.7 Register Description

# WATCHDOG REGISTER (WDGR)

Address: 0D8h - Read/Write

Reset Value: 1111 1110 (FEh)

| 7  |    |    |    |    |    |    | 0 |

|----|----|----|----|----|----|----|---|

| то | T1 | T2 | Т3 | T4 | T5 | SR | С |

# Bits 7:2 = T[5:0] Downcounter bits

**Caution:** These bits are reversed and shifted with respect to the physical counter: bit-7 (T0) is the LSB of the Watchdog downcounter and bit-2 (T5) is the MSB.

#### Bit 1 = SR: Software Reset bit

Software can generate a reset by clearing this bit while the C bit is set. When C = 0 (Watchdog deactivated) the SR bit is the MSB of the 7-bit timer. 0: Generate (write)

1: No software reset generated, MSB of 7-bit timer

#### Bit 0 = **C** Watchdog Control bit.

If the hardware option is selected (WDACT bit in Option byte), this bit is forced high and cannot be changed by the user (the Watchdog is always active). When the software option is selected (WDACT bit in Option byte), the Watchdog function is activated by setting the C bit, and cannot then be deactivated (except by resetting the MCU).

When C is kept cleared the counter can be used as a 7-bit timer.

0: Watchdog deactivated

1: Watchdog activated

# 9 INSTRUCTION SET

# 9.1 ST6 ARCHITECTURE

The ST6 architecture has been designed for maximum efficiency while keeping byte usage to a minimum; in short, to provide byte-efficient programming. The ST6 core has the ability to set or clear any register or RAM location bit in Data space using a single instruction. Furthermore, programs can branch to a selected address depending on the status of any bit in Data space.

#### 9.2 ADDRESSING MODES

The ST6 has nine addressing modes, which are described in the following paragraphs. Three different address spaces are available: Program space, Data space, and Stack space. Program space contains the instructions which are to be excuted, plus the data for immediate mode instructions. Data space contains the Accumulator, the X, Y, V and W registers, peripheral and Input/Output registers, the RAM locations and Data ROM locations (for storage of tables and constants). Stack space contains six 12-bit RAM cells used to stack the return addresses for subroutines and interrupts.

**Immediate**. In immediate addressing mode, the operand of the instruction follows the opcode location. As the operand is a ROM byte, the immediate addressing mode is used to access constants which do not change during program execution (e.g., a constant used to initialize a loop counter).

**Direct.** In direct addressing mode, the address of the byte which is processed by the instruction is stored in the location which follows the opcode. Direct addressing allows the user to directly address the 256 bytes in Data Space memory with a single two-byte instruction.

**Short Direct**. The core can address the four RAM registers X, Y, V, W (locations 80h, 81h, 82h, 83h) in short-direct addressing mode. In this case, the instruction is only one byte and the selection of the location to be processed is contained in the op-code. Short direct addressing is a subset of direct addressing mode. (Note that 80h and 81h are also indirect registers).

**Extended**. In extended addressing mode, the 12bit address needed to define the instruction is obtained by concatenating the four least significant bits of the opcode with the byte following the opcode. The instructions (JP, CALL) which use extended addressing mode are able to branch to any address in the 4 Kbyte Program space.

Extended addressing mode instructions are two bytes long.

Program Counter Relative. Relative addressing mode is only used in conditional branch instructions. The instruction is used to perform a test and, if the condition is true, a branch with a span of -15 to +16 locations next to the address of the relative instruction. If the condition is not true, the instruction which follows the relative instruction is executed. Relative addressing mode instructions are one byte long. The opcode is obtained by adding the three most significant bits which characterize the test condition, one bit which determines whether it is a forward branch (when it is 0) or backward branch (when it is 1) and the four least significant bits which give the span of the branch (0h to Fh) which must be added or subtracted from the address of the relative instruction to obtain the branch destination address.

**Bit Direct.** In bit direct addressing mode, the bit to be set or cleared is part of the opcode, and the byte following the opcode points to the address of the byte in which the specified bit must be set or cleared. Thus, any bit in the 256 locations of Data space memory can be set or cleared.

**Bit Test & Branch**. Bit test and branch addressing mode is a combination of direct addressing and relative addressing. Bit test and branch instructions are three bytes long. The bit identification and the test condition are included in the opcode byte. The address of the byte to be tested is given in the next byte. The third byte is the jump displacement, which is in the range of -127 to +128. This displacement can be determined using a label, which is converted by the assembler.

**Indirect**. In indirect addressing mode, the byte processed by the register-indirect instruction is at the address pointed to by the content of one of the indirect registers, X or Y (80h, 81h). The indirect register is selected by bit 4 of the opcode. Register indirect instructions are one byte long.

**Inherent**. In inherent addressing mode, all the information necessary for executing the instruction is contained in the opcode. These instructions are one byte long.

## **INSTRUCTION SET** (Cont'd)

Arithmetic and Logic. These instructions are used to perform arithmetic calculations and logic operations. In AND, ADD, CP, SUB instructions one operand is always the accumulator while, depending on the addressing mode, the other can be either a data space memory location or an imme-diate value. In CLR, DEC, INC instructions the op-erand can be any of the 256 data space address-es. In COM, RLC, SLA the operand is always the accumulator.

#### Table 16. Arithmetic & Logic Instructions

| Instruction | Addressing Mede | Butes | Cualas | Fla      | igs |

|-------------|-----------------|-------|--------|----------|-----|

| instruction | Addressing Mode | Bytes | Cycles | Z        | С   |

| ADD A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| ADD A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| ADD A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| ADDI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

| AND A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| AND A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| AND A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| ANDI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

| CLR A       | Short Direct    | 2     | 4      | Δ        | Δ   |

| CLR r       | Direct          | 3     | 4      | *        | *   |

| COM A       | Inherent        | 1     | 4      | Δ        | Δ   |

| CP A, (X)   | Indirect        | 1     | 4      | Δ        | Δ   |

| CP A, (Y)   | Indirect        | 1     | 4      | Δ        | Δ   |

| CP A, rr    | Direct          | 2     | 4      | Δ        | Δ   |

| CPI A, #N   | Immediate       | 2     | 4      | Δ        | Δ   |

| DEC X       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC Y       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC V       | Short Direct    | 1     | 4      | $\Delta$ | *   |

| DEC W       | Short Direct    | 1     | 4      | Δ        | *   |

| DEC A       | Direct          | 2     | 4      | Δ        | *   |

| DEC rr      | Direct          | 2     | 4      | Δ        | *   |

| DEC (X)     | Indirect        | 1     | 4      | $\Delta$ | *   |

| DEC (Y)     | Indirect        | 1     | 4      | Δ        | *   |

| INC X       | Short Direct    | 1     | 4      | Δ        | *   |

| INC Y       | Short Direct    | 1     | 4      | Δ        | *   |

| INC V       | Short Direct    | 1     | 4      | Δ        | *   |

| INC W       | Short Direct    | 1     | 4      | Δ        | *   |

| INC A       | Direct          | 2     | 4      | Δ        | *   |

| INC rr      | Direct          | 2     | 4      | $\Delta$ | *   |

| INC (X)     | Indirect        | 1     | 4      | Δ        | *   |

| INC (Y)     | Indirect        | 1     | 4      | Δ        | *   |

| RLC A       | Inherent        | 1     | 4      | Δ        | Δ   |

| SLA A       | Inherent        | 2     | 4      | Δ        | Δ   |

| SUB A, (X)  | Indirect        | 1     | 4      | Δ        | Δ   |

| SUB A, (Y)  | Indirect        | 1     | 4      | Δ        | Δ   |

| SUB A, rr   | Direct          | 2     | 4      | Δ        | Δ   |

| SUBI A, #N  | Immediate       | 2     | 4      | Δ        | Δ   |

#### Notes:

X,Y Index Registers V, W Short Direct Registers

Affected Λ

# Immediate data (stored in ROM memory)

Not Affected

rr Data space register

# **INSTRUCTION SET** (Cont'd)

Conditional Branch. Branch instructions perform a branch in the program when the selected condition is met.

Bit Manipulation Instructions. These instructions can handle any bit in Data space memory. One group either sets or clears. The other group (see Conditional Branch) performs the bit test branch operations.

# Table 17. Conditional Branch Instructions

Control Instructions. Control instructions control microcontroller operations during program execution.

Jump and Call. These two instructions are used to perform long (12-bit) jumps or subroutine calls to any location in the whole program space.

| Instruction   | Branch If | Bytes | Cycles | Flags |   |  |

|---------------|-----------|-------|--------|-------|---|--|

| instruction   | Dranch II | Bytes | Cycles | Z     | С |  |

| JRC e         | C = 1     | 1     | 2      | *     | * |  |

| JRNC e        | C = 0     | 1     | 2      | *     | * |  |

| JRZ e         | Z = 1     | 1     | 2      | *     | * |  |

| JRNZ e        | Z = 0     | 1     | 2      | *     | * |  |

| JRR b, rr, ee | Bit = 0   | 3     | 5      | *     | Δ |  |

| JRS b, rr, ee | Bit = 1   | 3     | 5      | *     | Δ |  |

#### Notes:

3-bit address b

5 bit signed displacement in the range -15 to +16 е

ee 8 bit signed displacement in the range -126 to +129

#### Table 18. Bit Manipulation Instructions

| Instruction | Addressing Mode | Bytes | Cycles | Flags |   |  |

|-------------|-----------------|-------|--------|-------|---|--|

| Instruction | Addressing Mode |       | Cycles | Z     | C |  |

| SET b,rr    | Bit Direct      | 2     | 4      | *     | * |  |

| RES b,rr    | Bit Direct      | 2     | 4      | *     | * |  |

rr

Δ

#### Notes:

b 3-bit address

Data space register rr

Bit Manipulation Instructions should not be used on Port Data Registers and any registers with read only and/or write only bits (see I/O port chapter)

#### Table 19. Control Instructions

| Instruction | Addressing Mode | Bytes | Cycles | Flags |   |  |

|-------------|-----------------|-------|--------|-------|---|--|

| Instruction | Addressing Mode | Dyies | Cycles | Z     | С |  |

| NOP         | Inherent        | 1     | 2      | *     | * |  |

| RET         | Inherent        | 1     | 2      | *     | * |  |

| RETI        | Inherent        | 1     | 2      | Δ     | Δ |  |

| STOP (1)    | Inherent        | 1     | 2      | *     | * |  |

| WAIT        | Inherent        | 1     | 2      | *     | * |  |

Notes:

This instruction is deactivated and a WAIT is automatically executed instead of a STOP if the watchdog function is selected. 1 Affected \*Not Affected Λ

#### Table 20. Jump & Call Instructions

| Instruction | Addressing Mode | Bytes Cycles Flags | Bytes Cycles Flags | Bytes Cycles Flags | igs |

|-------------|-----------------|--------------------|--------------------|--------------------|-----|

| instruction | Addressing Mode | Bytes              | Cycles             | Z                  | C   |

| CALL abc    | Extended        | 2                  | 4                  | *                  | *   |

| JP abc      | Extended        | 2                  | 4                  | *                  | *   |

Notes:

abc 12-bit address

Not Affected

Data space register

Not Affected

Affected. The tested bit is shifted into carry.

Not Affected

## **10.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 10.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                             | Maximum value                                | Unit |

|-----------------------------------|-----------------------------------------------------|----------------------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | Supply voltage                                      | 7                                            |      |

| V <sub>IN</sub>                   | Input voltage on any pin <sup>1) &amp; 2)</sup>     | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OUT</sub>                  | Output voltage on any pin <sup>1) &amp; 2)</sup>    | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | v    |

| V <sub>ESD(HBM)</sub>             | Electro-static discharge voltage (Human Body Model) | 3500                                         |      |

#### **10.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                               | Maximum value | Unit |

|----------------------------------------------|-----------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup> | 80            |      |

| I <sub>VSS</sub>                             | Total current out of V <sub>SS</sub> ground lines (sink) 3)           | 100           |      |

|                                              | Output current sunk by any standard I/O and control pin               | 20            |      |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/O pin                          | 40            | mA   |

|                                              | Output current source by any I/Os and control pin                     | 15            |      |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on RESET pin                                         | ±5            |      |

| 'INJ(PIN)                                    | Injected current on any other pin <sup>5)</sup>                       | ±5            |      |

#### **10.2.3 Thermal Characteristics**

| Symbol           | Ratings                                                               | Value       | Unit |

|------------------|-----------------------------------------------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range                                             | -60 to +150 | °C   |

| TJ               | Maximum junction temperature<br>(see THERMAL CHARACTERISTICS section) |             |      |

#### Notes:

- 1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7kΩ for I/Os). Unused I/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration.

- When the current limitation is not possible, the V<sub>IN</sub> absolute maximum rating must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

- 3. Power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) lines must always be connected to the external supply.

- 4. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken: Analog input pins must have a negative injection less than 1mA (assuming that the impedance of the analog voltage is lower than the specified limits).

- Pure digital pins must have a negative injection less than 1mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

5. For ROM versions, it is forbidden to inject current on the NMI pin.

# **OPERATING CONDITIONS** (Cont'd)

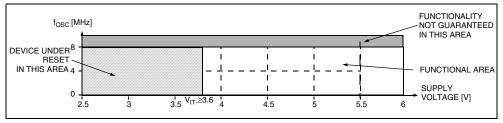

# 10.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$ .

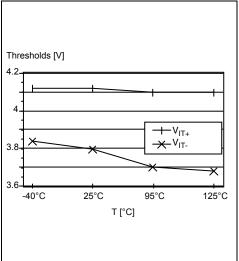

| Symbol              | Parameter                                         | Conditions                         | Min | Typ <sup>1)</sup> | Max | Unit |

|---------------------|---------------------------------------------------|------------------------------------|-----|-------------------|-----|------|

| V <sub>IT+</sub>    | Reset release threshold<br>(V <sub>DD</sub> rise) |                                    | 3.9 | 4.1               | 4.3 | v    |

| V <sub>IT-</sub>    | Reset generation threshold (V <sub>DD</sub> fall) |                                    | 3.6 | 3.8               | 4   | v    |

| V <sub>hys</sub>    | LVD voltage threshold hysteresis                  | V <sub>IT+</sub> -V <sub>IT-</sub> | 50  | 300               | 700 | mV   |

| Vt <sub>POR</sub>   | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                    |     |                   |     | mV/s |

| t <sub>g(VDD)</sub> | Filtered glitch delay on V <sub>DD</sub> 3)       | Not detected by the LVD            |     | 30                |     | ns   |

#### Notes:

1. LVD typical data are based on  $T_A=25^{\circ}C$ . They are given only as design guidelines and are not tested.

The minimum V<sub>DD</sub> rise time rate is needed to insure a correct device power-on and LVD reset. Not tested in production.

Data based on characterization results, not tested in production.

# Figure 33. LVD Threshold Versus V<sub>DD</sub> and f<sub>OSC</sub><sup>3)</sup>

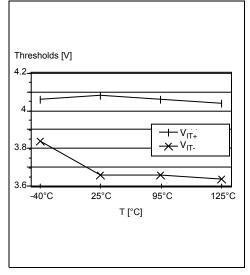

Figure 34. Typical LVD Thresholds Versus Temperature for OTP devices

# Figure 35. Typical LVD thresholds vs. Temperature for ROM devices

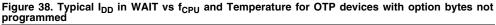

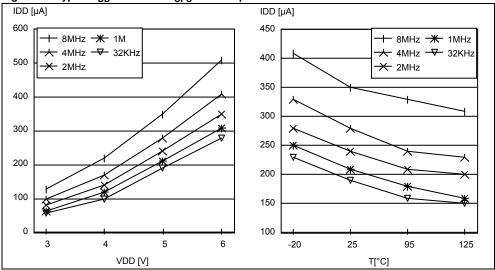

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

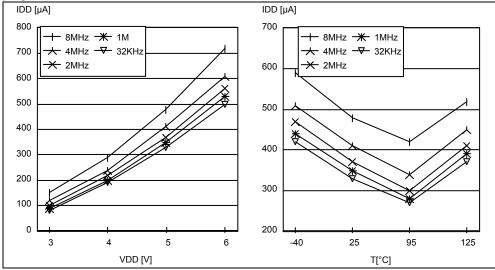

Figure 39. Typical  $I_{\text{DD}}$  in WAIT vs  $f_{\text{CPU}}$  and Temperature for OTP devices with option bytes programmed to 00H

57

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

# Figure 40. Typical $I_{\text{DD}}$ in WAIT vs $f_{\text{CPU}}$ and Temperature for ROM devices

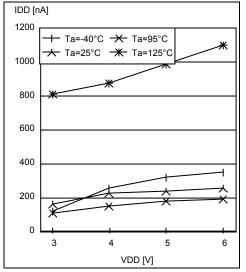

# SUPPLY CURRENT CHARACTERISTICS (Cont'd) 10.4.3 STOP Mode

| Symbol | Parameter                                 | Conditions  | Typ <sup>1)</sup> | Max                                  | Unit |

|--------|-------------------------------------------|-------------|-------------------|--------------------------------------|------|

|        | Supply current in STOP mode <sup>2)</sup> | OTP devices | 0.3               | 10 <sup>3)</sup><br>20 <sup>4)</sup> |      |

| IDD    | (see Figure 41 & Figure 42)               | ROM devices | 0.1               | 2 <sup>3)</sup><br>20 <sup>4)</sup>  | μA   |

#### Notes:

- 1. Typical data are based on  $V_{DD}$ =5.0V at T<sub>A</sub>=25°C.

- All I/O pins in input with pull-up mode (no load), all peripherals in reset state, OSG and LVD disabled, option bytes programmed to 00H. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- 3. Maximum STOP consumption for -40°C<Ta<90°C

- 4. Maximum STOP consumption for -40°C<Ta<125°C

# Figure 41. Typical $I_{\text{DD}}$ in STOP vs Temperature for OTP devices

# Figure 42. Typical $I_{\text{DD}}$ in STOP vs Temperature for ROM devices

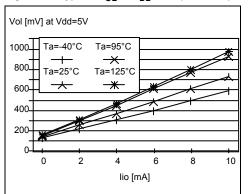

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 10.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                        | Parameter                                                              |                     | Conditions                                   | Min                                          | Max | Unit |  |

|-------------------------------|------------------------------------------------------------------------|---------------------|----------------------------------------------|----------------------------------------------|-----|------|--|

|                               |                                                                        |                     | I <sub>IO</sub> =+10µA, T <sub>A</sub> ⊴25°C |                                              | 0.1 |      |  |

|                               | Output low level voltage for a standard I/O pin                        |                     | I <sub>IO</sub> =+3mA, T <sub>A</sub> ⊴25°C  |                                              | 0.8 |      |  |

|                               | (see Figure 57 and Figure 60)                                          |                     | I <sub>IO</sub> =+5mA, T <sub>A</sub> \$5°C  |                                              | 0.8 |      |  |

|                               |                                                                        |                     | I <sub>IO</sub> =+10mA, T <sub>A</sub> \$5°C |                                              | 1.2 |      |  |

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a high sink I/O pin                       |                     |                                              | I <sub>IO</sub> =+10µA, T <sub>A</sub> ⊴25°C |     | 0.1  |  |

| VOL /                         |                                                                        | V <sub>DD</sub> =5V | I <sub>IO</sub> =+7mA, T <sub>A</sub> ⊴25°C  |                                              | 0.8 | v    |  |

|                               |                                                                        |                     | I <sub>IO</sub> =+10mA, T <sub>A</sub> \$5°C |                                              | 0.8 |      |  |

|                               | (see Figure 58 and Figure 61)                                          |                     | I <sub>IO</sub> =+15mA, T <sub>A</sub> ₫25°C |                                              | 1.3 |      |  |

|                               |                                                                        |                     | I <sub>IO</sub> =+20mA, T <sub>A</sub> \$5°C |                                              | 1.3 |      |  |

|                               |                                                                        |                     | I <sub>IO</sub> =+30mA, T <sub>A</sub> \$5°C |                                              | 2   |      |  |

|                               |                                                                        |                     | I <sub>IO</sub> =-10μΑ, Τ <sub>Α</sub> ⊴25°C | V <sub>DD</sub> -0.1                         |     |      |  |

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin (see Figure 59 and Figure 62) |                     | I <sub>IO</sub> =-3mA, T <sub>A</sub> ⊴25°C  | V <sub>DD</sub> -1.5                         |     |      |  |

|                               | (see Figure 39 and Figure 02)                                          |                     | I <sub>IO</sub> =-5mA, T <sub>A</sub> \$5°C  | V <sub>DD</sub> -1.5                         |     |      |  |

#### Notes:

- 1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 10.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 2. The I<sub>IO</sub> current source must always respect the absolute maximum rating specified in Section 10.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins does not have V<sub>OH</sub>.

# Figure 57. Typical V<sub>OL</sub> at V<sub>DD</sub> = 5V (standard)

# Vol [V] at Vdd=5V

Figure 58. Typical V<sub>OL</sub> at V<sub>DD</sub> = 5V (high-sink)

47/

Doc ID 4563 Rev 5

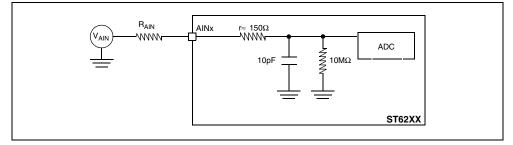

# 10.11 8-BIT ADC CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                   | Conditions                                       | Min             | <b>Typ</b> <sup>1)</sup> | Max              | Unit             |

|-------------------|---------------------------------------------|--------------------------------------------------|-----------------|--------------------------|------------------|------------------|

| fosc              | Clock frequency                             |                                                  | 1.2             |                          | fosc             | MHz              |

| V <sub>AIN</sub>  | Conversion range voltage <sup>2)</sup>      |                                                  | V <sub>SS</sub> |                          | V <sub>DD</sub>  | V                |

| R <sub>AIN</sub>  | External input resistor                     |                                                  |                 |                          | 10 <sup>3)</sup> | kΩ               |

| t <sub>ADC</sub>  | Total convertion time                       | f <sub>OSC</sub> =8MHz<br>f <sub>OSC</sub> =4MHz |                 | 70<br>140                |                  | μs               |

| +                 | Stabilization time 4)                       |                                                  |                 | 2                        | 4                | t <sub>CPU</sub> |

| t <sub>STAB</sub> |                                             | f <sub>OSC</sub> =8MHz                           |                 | 3.25                     | 6.5              | μs               |

| ADI               | Analog input current during conver-<br>sion |                                                  |                 |                          | 1.0              | μΑ               |

| AC <sub>IN</sub>  | Analog input capacitance                    |                                                  |                 | 2                        | 5                | pF               |

#### Notes:

- 1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$  and  $V_{DD}=5V$ .

- 2. The ADC refers to V<sub>DD</sub> and V<sub>SS</sub>.

- Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than 10kΩ). Data based on characterization results, not tested in production.

- 4. As a stabilization time for the AD converter is required, the first conversion after the enable can be wrong.

## Figure 66. Typical Application with ADC

Note: ADC not present on some devices. See device summary on page 1.

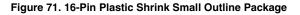

# PACKAGE MECHANICAL DATA (Cont'd)

#### inches mm Dim Min Min Тур Max Тур Max Α 3.78 0.149 G1 A1 0.38 0.015 0.36 0.56 0.014 0.018 0.022 в 0.46 B1 1.14 1.37 1.78 0.045 0.054 0.070 С 0.20 0.25 0.36 0.008 0.010 0.014 D 19.86 20.32 20.78 0.782 0.800 0.818 D1 17.78 0.700 0.277 0.295 0.313 E1 7.04 7.49 7.95 2.54 0.100 е G 6.35 6.60 6.86 0.250 0.260 0.270 F1 G1 9.47 9.73 9.98 0.373 0.383 0.393 G2 1.02 0.040 B1 L 2.92 3.30 3.81 0.115 0.130 0.150 D1 s 1.27 0.050 CDIP16W D ø 4.22 0.166 Number of Pins Ν 16

# Figure 70. 16-Pin Ceramic Side-Brazed Dual In-Line Package

57

# TRANSFER OF CUSTOMER CODE (Cont'd)

# 11.6.2 ROM VERSION

The ST6200C, 01C and 03C are mask programmed ROM version of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, selecting as ROM options the options defined in the programmable option byte of the OTP version.

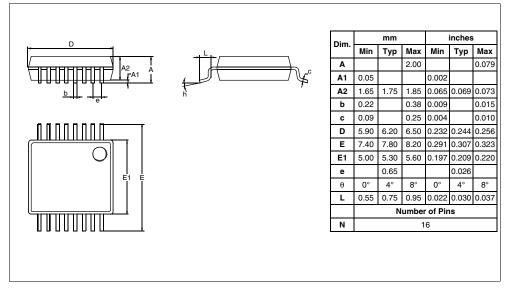

Note: ZPD15 is used for overvoltage protection

**ROM Readout Protection.** If the ROM READOUT PROTECTION option is selected, a protection fuse can be blown to prevent any access to the program memory content.

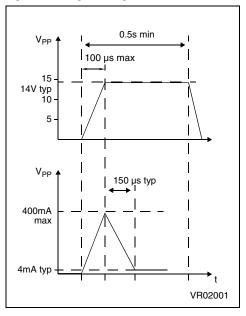

In case the user wants to blow this fuse, high voltage must be applied on the  $V_{\mbox{\scriptsize PP}}$  pin.

Figure 74. Programming wave form

# TRANSFER OF CUSTOMER CODE (Cont'd)

| Customer:<br>Address:<br>Contact:<br>Phone:<br>Reference: |                                        |                                                                                        |                                                                |

|-----------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Contact:<br>Phone:                                        |                                        |                                                                                        |                                                                |

| Phone:                                                    |                                        | • • • • • • • • • • • • • • • • • • • •                                                |                                                                |

| Phone:                                                    |                                        |                                                                                        |                                                                |

| Deference                                                 |                                        |                                                                                        |                                                                |

| nelelelice.                                               |                                        |                                                                                        |                                                                |

| STMicroelect                                              | tronics reference                      | es:                                                                                    |                                                                |

| Device:                                                   |                                        | [ ] ST6200C (1 KB)<br>[ ] ST6201C (2 KB)<br>[ ] ST6203C (1 KB)                         | [] ST62P00C (1 KB)<br>[] ST62P01C (2 KB)<br>[] ST62P03C (1 KB) |

| Package:                                                  |                                        | [ ] Dual in Line Plastic<br>[ ] Small Outline Plastic w<br>[ ] Shrink Small Outline Pl |                                                                |

| Conditioning of                                           | option:                                | [] Standard (Tube)                                                                     | <b>J</b>                                                       |

| Temperature I                                             | Range:                                 | [ ] Tape & Reel<br>[ ] 0°C to + 70°C<br>[ ] - 40°C to + 125°C                          | [] - 40°C to + 85°C                                            |

| Marking:                                                  |                                        | SO16 (6 char. m                                                                        | max):                                                          |

| Authorized ch                                             | aracters are lette                     | rs, digits, '.', '-', '/' and spaces only.                                             |                                                                |

| Oscillator Safe<br>Watchdog Sel                           | •                                      | [] Enabled<br>[] Software Activation                                                   | [] Disabled                                                    |

| NMI pull-up:<br>Oscillator Sele                           | ection:                                | [] Hardware Activation<br>[] Enabled<br>[] Quartz crystal / Cerami<br>[] RC network    | [] Disabled<br>c resonator                                     |

| Readout Prote                                             | ection:                                | FASTROM:<br>[] Enabled<br>ROM:                                                         | [] Disabled                                                    |

|                                                           |                                        | [] Enabled:<br>[] Fuse is blown                                                        | by STMicroelectronics<br>lown by the customer                  |

| Low Voltage E<br>External STOF<br>Identifier (FAS         | P Mode Control:                        | [] Enabled<br>[] Enabled<br>[] Enabled                                                 | [] Disabled<br>[] Disabled<br>[] Disabled                      |

|                                                           |                                        | []                                                                                     |                                                                |

| Comments:                                                 |                                        |                                                                                        |                                                                |

|                                                           | quency in the app<br>ting Range in the |                                                                                        |                                                                |

# **14 SUMMARY OF CHANGES**

Description of the changes between the current release of the specification and the previous one.

| Revision | Main Changes                                                                                                                                                                       | Date         |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3.3      | Removed references to 32768 clock cycle delay in Section 5 and in Section 6<br>Changed note 2 in Section 10.6.2 on page 72: added text on data retention and program-<br>mability. | October 2003 |

| 4        | Updated device summary on page 1<br>Replaced soldering information by ECOPACK <sup>®</sup> information in Section 11.3 on page 89<br>Updated disclaimer on last page               | January 2009 |

| 5        | Added note 5 to Section 10.2.2 on page 59                                                                                                                                          | October 2009 |

# **15 TO GET MORE INFORMATION**

To get the latest information on this product please use the STMicroelectronics web server.

→ http://www.st.com/