Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Obsolete                                                           |

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | -                                                                  |

| Peripherals                | LVD, POR, WDT                                                      |

| Number of I/O              | 9                                                                  |

| Program Memory Size        | 1KB (1K x 8)                                                       |

| Program Memory Type        | OTP                                                                |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 64 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | -                                                                  |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                     |

| Supplier Device Package    | -                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t03cm3 |

|                            |                                                                    |

## **Table of Contents**

| ST62         | 200C ST6201C ST6203C                            | 1   |

|--------------|-------------------------------------------------|-----|

| 1 INTR       | ODUCTION                                        | . 6 |

| 2 PIN [      | DESCRIPTION                                     | . 7 |

| з мем        | ORY MAPS, PROGRAMMING MODES AND OPTION BYTES    |     |

| 3.1          | MEMORY AND REGISTER MAPS                        |     |

|              | 3.1.1 Introduction                              |     |

|              | 3.1.2 Program Space                             |     |

|              | 3.1.4 Data Space                                |     |

|              | 3.1.5 Stack Space                               |     |

|              | 3.1.6 Data ROM Window                           |     |

| 3.2          |                                                 |     |

|              | 3.2.1 Program Memory                            |     |

| 3.3          | 3.2.2 EPROM Erasing                             |     |

|              |                                                 |     |

| 4 CEN<br>4.1 | TRAL PROCESSING UNIT INTRODUCTION               |     |

| 4.1          | MAIN FEATURES                                   |     |

| 4.2          | CPU REGISTERS                                   |     |

|              |                                                 |     |

|              | CKS, SUPPLY AND RESET                           |     |

| 5.1          | CLOCK SYSTEM                                    |     |

|              | 5.1.1 Main Oscillator                           |     |

|              | 5.1.3 Low Frequency Auxiliary Oscillator (LFAO) |     |

|              | 5.1.4 Register Description                      | 21  |

| 5.2          | LOW VOLTAGE DETECTOR (LVD)                      | 22  |

| 5.3          | RESET                                           | 23  |

|              | 5.3.1 Introduction                              |     |

|              | 5.3.2 RESET Sequence                            |     |

|              | 5.3.3 RESET Pin                                 |     |

|              | 5.3.5 LVD Reset                                 |     |

| 5.4          | INTERRUPTS                                      |     |

| 5.5          | INTERRUPT RULES AND PRIORITY MANAGEMENT         | 27  |

| 5.6          | INTERRUPTS AND LOW POWER MODES                  | 27  |

| 5.7          | NON MASKABLE INTERRUPT                          | 27  |

| 5.8          | PERIPHERAL INTERRUPTS                           |     |

| 5.9          | EXTERNAL INTERRUPTS (I/O PORTS)                 |     |

|              | 5.9.1 Notes on using External Interrupts        | 28  |

| 5.10         | INTERRUPT HANDLING PROCEDURE                    |     |

|              | 5.10.1 Interrupt Response Time                  | 29  |

## **Table of Contents**

| 5.11 REGISTER DESCRIPTION                                                        | <br>30 |

|----------------------------------------------------------------------------------|--------|

| 6 POWER SAVING MODES                                                             | <br>31 |

| 6.1 INTRODUCTION                                                                 | <br>31 |

| 6.2 WAIT MODE                                                                    | <br>32 |

| 6.3 STOP MODE                                                                    | <br>33 |

| 6.4 NOTES RELATED TO WAIT AND STOP MODES                                         | <br>35 |

| 6.4.1 Exit from Wait and Stop Modes                                              |        |

| 6.4.2 Recommended MCU Configuration                                              |        |

| 7 I/O PORTS                                                                      | <br>36 |

| 7.1 INTRODUCTION                                                                 | <br>36 |

| 7.2 FUNCTIONAL DESCRIPTION                                                       |        |

| 7.2.1 Digital Input Modes                                                        | <br>36 |

| 7.2.2 Analog Inputs                                                              |        |

| 7.2.3 Output Modes                                                               |        |

| 7.2.4 Alternate Functions                                                        |        |

| 7.2.5 Instructions NOT to be used to access Port Data registers (SET, RES, INC a | ,      |

| 7.2.6 Recommendations                                                            |        |

| 7.3 LOW POWER MODES                                                              |        |

| 7.4 INTERRUPTS                                                                   |        |

| 7.5 REGISTER DESCRIPTION                                                         | <br>40 |

| 8 ON-CHIP PERIPHERALS                                                            | <br>41 |

| 8.1 WATCHDOG TIMER (WDG)                                                         | <br>41 |

| 8.1.1 Introduction                                                               | <br>41 |

| 8.1.2 Main Features                                                              |        |

| 8.1.3 Functional Description                                                     |        |

| 8.1.4 Recommendations                                                            |        |

| 8.1.5 Low Power Modes                                                            |        |

| 8.1.7 Register Description                                                       |        |

| 8.2 8-BIT TIMER                                                                  |        |

| 8.2.1 Introduction                                                               |        |

| 8.2.2 Main Features                                                              |        |

| 8.2.3 Counter/Prescaler Description                                              | <br>46 |

| 8.2.4 Low Power Modes                                                            |        |

| 8.2.5 Interrupts                                                                 |        |

| 8.2.6 Register Description                                                       |        |

| 8.3 A/D CONVERTER (ADC)                                                          |        |

| 8.3.1 Introduction                                                               |        |

| 8.3.2 Main Features                                                              | -      |

| 8.3.4 Recommendations                                                            |        |

| 8.3.5 Low Power Modes                                                            |        |

| 8.3.6 Interrupts                                                                 | -      |

| 8.3.7 Register Description                                                       |        |

| 9 INSTRUCTION SET                                                                | <br>52 |

## **Table of Contents**

| 11 GENERAL INFORMATION                 | 86 |

|----------------------------------------|----|

| 11.1 PACKAGE MECHANICAL DATA           | 86 |

| 11.2 THERMAL CHARACTERISTICS           | 88 |

| 11.3 ECOPACK INFORMATION               | 89 |

| 11.4 PACKAGE/SOCKET FOOTPRINT PROPOSAL | 90 |

| 11.5 ORDERING INFORMATION              |    |

| 11.6 TRANSFER OF CUSTOMER CODE         |    |

| 11.6.1FASTROM version                  |    |

| 11.6.2ROM VERSION                      |    |

| 12 DEVELOPMENT TOOLS                   | 95 |

| 13 ST6 APPLICATION NOTES               | 97 |

| 14 SUMMARY OF CHANGES                  | 99 |

| 15 TO GET MORE INFORMATION             | 99 |

## **MEMORY MAP** (Cont'd)

## 3.1.6.2 Data ROM Window memory addressing

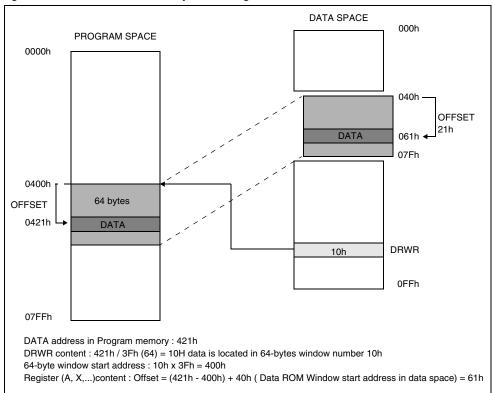

In cases where some data (look-up tables for example) are stored in program memory, reading these data requires the use of the Data ROM window mechanism. To do this:

- The DRWR register has to be loaded with the 64-byte block number where the data are located (in program memory). This number also gives the start address of the block.

- 2. Then, the offset address of the byte in the Data ROM Window (corresponding to the offset in the 64-byte block in program memory) has to be loaded in a register (A, X,...).

When the above two steps are completed, the data can be read.

To understand how to determine the DRWR and the content of the register, please refer to the example shown in Figure 6. In any case the calculation is automatically handled by the ST6 development tools.

Please refer to the user manual of the correspoding tool.

#### 3.1.6.3 Recommendations

Care is required when handling the DRWR register as it is write only. For this reason, the DRWR contents should not be changed while executing an interrupt service routine, as the service routine cannot save and then restore the register's previous contents. If it is impossible to avoid writing to the DRWR during the interrupt service routine, an image of the register must be saved in a RAM location, and each time the program writes to the DRWR, it must also write to the image register. The image register must be written first so that, if an interrupt occurs between the two instructions, the DRWR is not affected.

Figure 6. Data ROM Window Memory Addressing

57

## **CLOCK SYSTEM** (Cont'd)

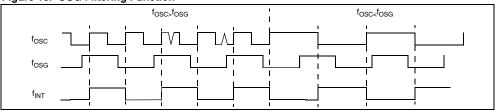

## 5.1.2 Oscillator Safeguard (OSG)

The Oscillator Safeguard (OSG) feature is a means of dramatically improving the operational integrity of the MCU. It is available when the OSG ENABLED option is selected in the option byte (refer to the Option Bytes section of this document).

The OSG acts as a filter whose cross-over frequency is device dependent and provides three basic functions:

- Filtering spikes on the oscillator lines which would result in driving the CPU at excessive frequencies

- Management of the Low Frequency Auxiliary Oscillator (LFAO), (useable as low cost internal clock source, backup clock in case of main oscillator failure or for low power consumption)

- Automatically limiting the f<sub>INT</sub> clock frequency as a function of supply voltage, to ensure correct operation even if the power supply drops.

## 5.1.2.1 Spike Filtering

Spikes on the oscillator lines result in an effectively increased internal clock frequency. In the absence of an OSG circuit, this may lead to an over frequency for a given power supply voltage. The OSG filters out such spikes (as illustrated in Figure 10). In all cases, when the OSG is active, the max-

imum internal clock frequency,  $f_{INT}$ , is limited to  $f_{OSG}$ , which is supply voltage dependent.

# 5.1.2.2 Management of Supply Voltage Variations

Over-frequency, at a given power supply level, is seen by the OSG as spikes; it therefore filters out some cycles in order that the internal clock frequency of the device is kept within the range the particular device can stand (depending on  $V_{\rm DD}$ ), and below  $f_{\rm OSG}$ : the maximum authorised frequency with OSG enabled.

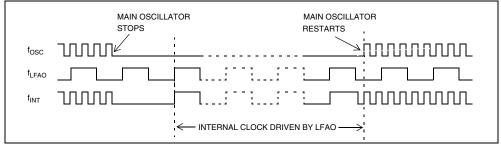

## 5.1.2.3 LFAO Management

When the OSG is enabled, the Low Frequency Auxiliary Oscillator can be used (see Section 5.1.3).

**Note:** The OSG should be used wherever possible as it provides maximum security for the application. It should be noted however, that it can increase power consumption and reduce the maximum operating frequency to f<sub>OSG</sub> (see Electrical Characteristics section).

**Caution:** Care has to be taken when using the OSG, as the internal frequency is defined between a minimum and a maximum value and may vary depending on both V<sub>DD</sub> and temperature. For precise timing measurements, it is not recommended to use the OSG.

Figure 10. OSG Filtering Function

Figure 11. LFAO Oscillator Function

## **CLOCK SYSTEM** (Cont'd)

# 5.1.3 Low Frequency Auxiliary Oscillator (LFAO)

The Low Frequency Auxiliary Oscillator has three main purposes. Firstly, it can be used to reduce power consumption in non timing critical routines. Secondly, it offers a fully integrated system clock, without any external components. Lastly, it acts as a backup oscillator in case of main oscillator failure.

This oscillator is available when the OSG ENA-BLED option is selected in the option byte (refer to the Option Bytes section of this document). In this case, it automatically starts one of its periods after the first missing edge of the main oscillator, whatever the reason for the failure (main oscillator defective, no clock circuitry provided, main oscillator switched off...). See Figure 11.

User code, normal interrupts, WAIT and STOP instructions, are processed as normal, at the reduced  $f_{LFAO}$  frequency. The A/D converter accuracy is decreased, since the internal frequency is below 1.2 MHz.

At power on, until the main oscillator starts, the reset delay counter is driven by the LFAO. If the main oscillator starts before the 2048 cycle delay has elapsed, it takes over.

The Low Frequency Auxiliary Oscillator is automatically switched off as soon as the main oscillator starts.

## 5.1.4 Register Description

## ADC CONTROL REGISTER (ADCR)

Address: 0D1h — Read/Write Reset value: 0100 0000 (40h)

| 7         |           |           |           |           |            | 0         |

|-----------|-----------|-----------|-----------|-----------|------------|-----------|

| ADCR<br>7 | ADCR<br>6 | ADCR<br>5 | ADCR<br>4 | ADCR<br>3 | OSC<br>OFF | ADCR<br>0 |

Bit 7:3, 1:0 = ADCR[7:3], ADCR[1:0] ADC Control Register.

These bits are used to control the A/D converter (if available on the device) otherwise they are not used.

## Bit 2 = OSCOFF Main Oscillator Off.

0: Main oscillator enabled

1: Main oscillator disabled

**Note:** The OSG must be enabled using the OS-GEN option in the Option Byte, otherwise the OS-COFF setting has no effect.

Doc ID 4563 Rev 5 21/100

## **5.11 REGISTER DESCRIPTION**

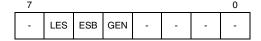

## INTERRUPT OPTION REGISTER (IOR)

Address: 0C8h — Write Only

Reset status: 00h

Caution: This register is write-only and cannot be accessed by single-bit operations (SET, RES, DEC,...).

Bit 7 = Reserved, must be cleared.

Bit 6 = LES Level/Edge Selection bit.

0: Falling edge sensitive mode is selected for interrupt vector #1

1: Low level sensitive mode is selected for interrupt vector #1

Bit 5 = **ESB** Edge Selection bit.

0: Falling edge mode on interrupt vector #2

1: Rising edge mode on interrupt vector #2

Bit 4 = **GEN** Global Enable Interrupt.

0: Disable all maskable interrupts

1: Enable all maskable interrupts

**Note:** When the GEN bit is cleared, the NMI interrupt is active but cannot be used to exit from STOP or WAIT modes.

Bits 3:0 = Reserved, must be cleared.

Table 7. Interrupt Mapping

| Vector<br>number | Source<br>Block | Description            | Register<br>Label | Flag     | Exit<br>from<br>STOP | Vector<br>Address | Priority<br>Order |

|------------------|-----------------|------------------------|-------------------|----------|----------------------|-------------------|-------------------|

|                  | RESET           | Reset                  | N/A               | N/A      | yes                  | FFEh-FFFh         |                   |

| Vector #0        | NMI             | Non Maskable Interrupt | N/A               | N/A      | yes                  | FFCh-FFDh         | Highest           |

|                  | •               | •                      | FFAh-FFBh         | Priority |                      |                   |                   |

|                  |                 | FF8h-FF9h              | 1 1               |          |                      |                   |                   |

| Vector #1        | Port A          | Ext. Interrupt Port A  | N/A               | N/A      | yes                  | FF6h-FF7h         | I ▼               |

| Vector #2        | Port B          | Ext. Interrupt Port B  | N/A               | N/A      | yes                  | FF4h-FF5h         | 1. '.             |

| Vector #3        | TIMER           | Timer underflow        | TSCR              | TMZ      | yes                  | FF2h-FF3h         | Lowest            |

| Vector #4        | ADC *           | End Of Conversion      | ADCR              | EOC      | no                   | FF0h-FF1h         | Priority          |

<sup>\*</sup> Depending on device. See device summary on page 1.

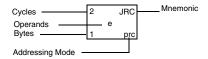

Opcode Man Summary. The following table contains an opcode man for the instructions used by the ST6

| LOW       |   | 0<br>0000        | u! | 1<br>0001          | ,110 | 2<br>0010   | ,,, | 3<br>0011       | <i>3</i> C | 4<br>010 |            | <del>ا ت</del> | 5<br>0101 |     |   | 6<br>0110 | ict       | J) | 7<br>0111    | LOW       |

|-----------|---|------------------|----|--------------------|------|-------------|-----|-----------------|------------|----------|------------|----------------|-----------|-----|---|-----------|-----------|----|--------------|-----------|

| HI        |   |                  |    |                    |      |             |     |                 |            | 010      |            |                | 0101      |     |   |           |           |    |              | Н         |

| 0<br>0000 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | JRR<br>b0,rr,ee | 2          | е        | JRZ<br>NOP |                | #         |     | 2 | JF<br>e   | RC        | 4  | LD<br>a,(x)  | 0<br>0000 |

|           | 1 | pcr<br>JRNZ      | 2  | ext<br>CALL        | 2    | pcr<br>JRNC | 5   | bt<br>JRS       | 2          |          | pcr<br>JRZ | 4              |           | INC | 2 |           | orc<br>RC | 1  | ind<br>LDI   |           |

| 1<br>0001 |   | е                |    | abc                |      | е           | -   | b0,rr,ee        |            | е        |            | -              | х         |     |   | е         |           |    | a,nn         | 1<br>0001 |

|           | 1 | pcr<br>JRNZ      | 2  | ext<br>CALL        | 2    | pcr<br>JRNC | 5   | bt<br>JRR       | 2          |          | pcr<br>JRZ | 1              |           | sd  | 2 |           | orc<br>RC | 2  | imm<br>CP    |           |

| 2<br>0010 | 1 | e                | 2  | abc                | 1    | e           | 3   | b4,rr,ee<br>bt  | 1          | е        |            |                | #         |     | 1 | е         | vro       | 1  | a,(x)        | 2<br>0010 |

| 3         | 2 | pcr<br>JRNZ<br>e | 4  | ext<br>CALL<br>abc | 2    | JRNC<br>e   | 5   | JRS<br>b4,rr,ee | 2<br>e     |          | pcr<br>JRZ | 4              | a,x       | LD  | 2 |           | -         | 4  | CPI<br>a,nn  | 3         |

| 0011      | 1 | pcr<br>JRNZ      | 2  | ext                | 1    | pcr<br>JRNC | 3   | bt<br>JRR       | 1          |          | pcr<br>JRZ | 1              | а,х       | sd  | 1 | ŗ         | _         | 2  | imm          | 0011      |

| 4<br>0100 |   | е                |    | CALL<br>abc        | 2    | е           | 5   | b2,rr,ee        | _          | е        |            |                | #         |     |   | е         | 3C        |    | a,(x)        | 4<br>0100 |

| 5         | 2 | JRNZ             | 4  | CALL               | 2    | JRNC        | 5   | JRS             | 2          |          | pcr<br>JRZ | 4              |           | INC | 2 | JF        | rc<br>RC  | 4  | ADDI         | 5         |

| 0101      | 1 | e<br>pcr         | 2  | abc<br>ext         | 1    | e<br>pcr    | 3   |                 | 1          | е        | pcr        | 1              | у         | sd  | 1 |           | -         | 2  | a,nn<br>imm  | 0101      |

| 6<br>0110 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | b6,rr,ee        | 2          | е        | JRZ        |                | #         |     | 2 | е         |           | 4  | INC<br>(x)   | 6<br>0110 |

|           | 2 | pcr<br>JRNZ      | 2  | ext<br>CALL        | 2    | pcr<br>JRNC | 5   | bt<br>JRS       | 2          |          | pcr<br>JRZ | 4              |           | LD  | 2 | p<br>JF   | orc<br>RC | 1  | ind          | _         |

| 7<br>0111 | 1 | e<br>pcr         | 2  | abc<br>ext         | 1    | e<br>pcr    | 3   | b6,rr,ee<br>bt  | 1          | е        | pcr        | 1              | а,у       | sd  | 1 | e         | orc       |    | #            | 7<br>0111 |

| 8<br>1000 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   |                 | 2          | е        | JRZ        |                | #         |     | 2 |           |           | 4  | LD<br>(x),a  | 8<br>1000 |

| 9         | 2 | pcr<br>JRNZ      | 4  | ext<br>CALL        | 2    | pcr<br>JRNC | 5   | JRS             | 2          |          | pcr<br>JRZ | 4              |           | INC | 2 | JF        | -         | 1  | ind          | 9         |

| 1001      | 1 | e<br>pcr         | 2  | abc<br>ext         | 1    | e<br>pcr    | 3   | b1,rr,ee<br>bt  | 1          | е        | pcr        | 1              | V         | sd  | 1 | e<br>r    | orc       |    | #            | 1001      |

| A<br>1010 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | JRR<br>b5,rr,ee | 2          | е        | JRZ        |                | #         |     | 2 | JF<br>e   | 3C        | 4  | AND<br>a,(x) | A<br>1010 |

| В         | 2 | pcr<br>JRNZ      | 4  | ext<br>CALL        | 2    | pcr<br>JRNC | 5   | JRS             | 2          |          | pcr<br>JRZ | 4              |           | LD  | 2 | JF        | rc<br>RC  | 4  | ind<br>ANDI  | В         |

| 1011      | 1 | e<br>pcr         | 2  | abc<br>ext         | 1    | e<br>pcr    | 3   | b5,rr,ee<br>bt  | 1          | е        | pcr        | 1              | a,v       | sd  | 1 |           |           | 2  | a,nn<br>imm  | 1011      |

| C<br>1100 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | JRR<br>b3,rr,ee | 2          | е        | JRZ        |                | #         |     | 2 | е         |           | 4  | SUB<br>a,(x) | C<br>1100 |

| D         | 2 | pcr<br>JRNZ<br>e | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | JRS<br>b3,rr,ee | 2          | e        | pcr<br>JRZ | 4              |           | INC | 2 |           | rc<br>RC  | 4  | SUBI<br>a,nn | D         |

| 1101      | 1 | pcr              | 2  | ext                | 1    | pcr         | 3   | bt              | 1          | е        | pcr        | 1              | W         | sd  | 1 | ŗ         |           | 2  | imm          | 1101      |

| E<br>1110 | 2 | JRNZ<br>e        | 4  | CALL<br>abc        | 2    | JRNC<br>e   | 5   | JRR<br>b7,rr,ee | 2          | е        | JRZ        |                | #         |     | 2 | е         | 3C        | 4  | DEC<br>(x)   | E<br>1110 |

| F         | 2 | pcr<br>JRNZ      | 4  | CALL               | 2    | JRNC        | 5   | JRS             | 2          |          | pcr<br>JRZ | 4              |           | LD  | 2 | JF        |           | 1  | ind          | F         |

| 1111      | 1 | e<br>pcr         | 2  | abc<br>ext         | 1    | e<br>pcr    | 3   | b7,rr,ee<br>bt  | 1          | е        | pcr        | 1              | a,w       | sd  | 1 | e<br>r    | orc       |    | #            | 1111      |

Abbreviations for Addressing Modes: Legend: Indicates Illegal Instructions

dir Direct sd Short Direct е Immediate imm b inh Inherent rr ext

1-byte Data space address Extended nn 1-byte immediate data Bit Direct abc 12-bit address Bit Test 8-bit displacement

ee

pcr ind Program Counter Relative

Indirect

b.d

bt

5-bit Displacement

3-bit Address

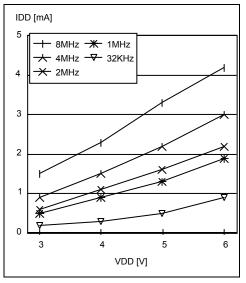

## 10.4 SUPPLY CURRENT CHARACTERISTICS

The following current consumption specified for the ST6 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for STOP mode for which the clock is stopped).

10.4.1 RUN Modes

| Symbol          | Parameter                                                            |                           | Conditions                                                                                                                      | Typ 1)                          | Max <sup>2)</sup>               | Unit |

|-----------------|----------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------|

| I <sub>DD</sub> | Supply current in RUN mode <sup>3)</sup> (see Figure 36 & Figure 37) | 4.5V≰ <sub>DD</sub> \$.0V | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 0.5<br>1.3<br>1.6<br>2.2<br>3.3 | 0.7<br>1.7<br>2.4<br>3.3<br>4.8 | mA   |

| -00             | Supply current in RUN mode <sup>3)</sup> (see Figure 36 & Figure 37) | . <sub>D</sub> 3          | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 0.3<br>0.6<br>0.9<br>1.0<br>1.8 | 0.4<br>0.8<br>1.2<br>1.5<br>2.3 |      |

#### Notes:

- 1. Typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (4.5V\$\frac{1}{2}\$\dots 0.0V range) and V<sub>DD</sub>=3.3V (3V\$\frac{1}{2}\$\dots 0.0V range).

- 2. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>OSC</sub> max.

- 3. CPU running with memory access, all I/O pins in input with pull-up mode (no load), all peripherals in reset state; clock input (OSC<sub>IN</sub>) driven by external square wave, OSG and LVD disabled, option bytes not programmed.

Figure 36. Typical I<sub>DD</sub> in RUN vs. f<sub>CPU</sub>

Figure 37. Typical  $I_{DD}$  in RUN vs. Temperature ( $V_{DD} = 5V$ )

## $\textbf{SUPPLY CURRENT CHARACTERISTICS} \ (\texttt{Cont'd})$

### 10.4.2 WAIT Modes

| Symbol          | Parameter                                                                                      |                           |             | Conditions                                                                                                                      | Typ 1)                          | Max 2)                          | Unit |

|-----------------|------------------------------------------------------------------------------------------------|---------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------|

|                 | Supply current in WAIT mode <sup>3)</sup> Option bytes not programmed (see Figure 38)          |                           | devices     | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 330<br>350<br>370<br>410<br>480 | 550<br>600<br>650<br>700<br>800 |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) |                           | OTP d       | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 18<br>26<br>41<br>57<br>70      | 60<br>80<br>120<br>180<br>200   |      |

|                 | Supply current in WAIT mode <sup>3)</sup> (see Figure 40)                                      | 4.5V≰ <sub>DD</sub> \$.0V | ROM devices | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 190<br>210<br>240<br>280<br>350 | 300<br>350<br>400<br>500<br>600 |      |

| I <sub>DD</sub> | Supply current in WAIT mode <sup>3)</sup> Option bytes not programmed (see Figure 38)          |                           | devices     | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 80<br>90<br>100<br>120<br>150   | 120<br>140<br>150<br>200<br>250 | μА   |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) |                           | OTP de      | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 5<br>8<br>16<br>18<br>20        | 30<br>40<br>50<br>60<br>100     |      |

|                 | Supply current in WAIT mode <sup>3)</sup> Option bytes not programmed (see Figure 40)          |                           | ROM devices | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz | 60<br>65<br>80<br>100<br>130    | 100<br>110<br>120<br>150<br>210 |      |

## Notes:

- 1. Typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (4.5V $\stackrel{\checkmark}{V}_{DD}$ \$.0V range) and V<sub>DD</sub>=3.3V (3V $\stackrel{\checkmark}{V}_{DD}$ \$.6V range).

- 2. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>OSC</sub> max.

- 3. All I/O pins in input with pull-up mode (no load), all peripherals in reset state; clock input (OSC<sub>IN</sub>) driven by external square wave, OSG and LVD disabled.

## **CLOCK AND TIMING CHARACTERISTICS (Cont'd)**

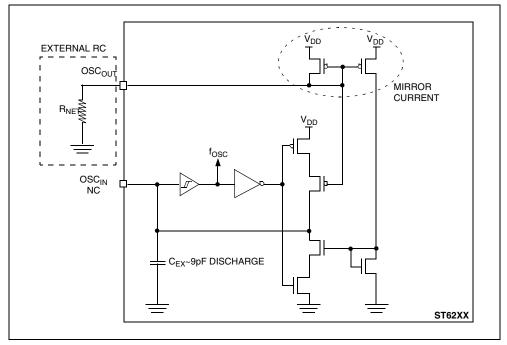

#### 10.5.4 RC Oscillator

The ST6 internal clock can be supplied with an external RC oscillator. Depending on the  $R_{NET}$  value, the accuracy of the frequency is about 20%, so it may not be suitable for some applications.

| Symbol           | Parameter                          |                           | Conditions                | Min | Тур  | Max | Unit    |

|------------------|------------------------------------|---------------------------|---------------------------|-----|------|-----|---------|

|                  |                                    | .00                       | R <sub>NET</sub> =22 kΩ   | 7.2 | 8.6  | 10  |         |

|                  |                                    | 9                         | $R_{NET}$ =47 k $\Omega$  | 5.1 | 5.7  | 6.5 |         |

|                  |                                    | 10,                       | R <sub>NET</sub> =100 kΩ  | 3.2 | 3.4  | 3.8 |         |

|                  |                                    | 4.5V≰∕ <sub>DD</sub> ≸.0V | R <sub>NET</sub> =220 kΩ  | 1.8 | 1.9  | 2   |         |

| fosc             | RC oscillator frequency 1)         |                           | $R_{NET}$ =470 k $\Omega$ | 0.9 | 0.95 | 1.1 | MHz     |

| iosc             | The oscillator frequency           | <b>&gt;</b> 0             | R <sub>NET</sub> =22 kΩ   | 3.7 | 4.3  | 4.9 | 1011 12 |

|                  |                                    | 8.6                       | R <sub>NET</sub> =47 kΩ   | 2.8 | 3    | 3.3 |         |

|                  |                                    | 3V <u>∜</u> D53.6V        | R <sub>NET</sub> =100 kΩ  | 1.8 | 1.9  | 2   |         |

|                  |                                    | ₹                         | R <sub>NET</sub> =220 kΩ  | 1   | 1.1  | 1.2 |         |

|                  |                                    |                           | R <sub>NET</sub> =470 kΩ  | 0.5 | 0.55 | 0.6 |         |

| R <sub>NET</sub> | RC Oscillator external resistor 2) |                           | see Figure 46 & Figure 47 | 22  |      | 870 | kΩ      |

#### Notes:

- Data based on characterization results, not tested in production. These measurements were done with the OSCin pin unconnected (only soldered on the PCB).

- 2. R<sub>NET</sub> must have a positive temperature coefficient (ppm/°C), carbon resistors should therefore not be used.

Figure 45. Typical Application with RC Oscillator

#### 10.7 EMC CHARACTERISTICS

Susceptibility tests are performed on a sample basis during product characterization.

#### 10.7.1 Functional EMS

(Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Neg 1) | Pos 1) | Unit |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|--------|------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | -2     | 2      |      |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz conforms to IEC 1000-4-4    | -2.5   | 3      | kV   |

#### Notes:

- 1. Data based on characterization results, not tested in production.

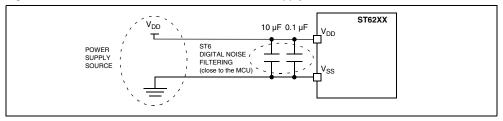

- 2. The suggested 10 μF and 0.1 μF decoupling capacitors on the power supply lines are proposed as a good price vs. EMC performance tradeoff. They have to be put as close as possible to the device power supply pins. Other EMC recommendations are given in other sections (I/Os, RESET, OSCx pin characteristics).

Figure 50. EMC Recommended Star Network Power Supply Connection 2)

纫

Doc ID 4563 Rev 5 73/100

## **EMC CHARACTERISTICS (Cont'd)**

## 10.7.2 Absolute Electrical Sensitivity

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the AN1181 application note.

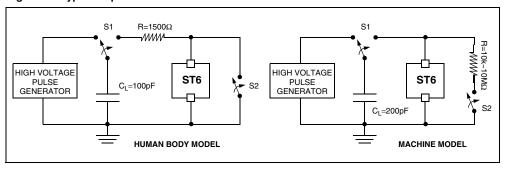

## 10.7.2.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends of the number of supply pins of the device (3 parts\*(n+1) supply pin). Two models are usually simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard. See Figure 51 and the following test sequences.

## **Human Body Model Test Sequence**

C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to R.

- A discharge from C<sub>L</sub> through R (body resistance) to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

## **Machine Model Test Sequence**

- C<sub>L</sub> is loaded through S1 by the HV pulse generator.

- S1 switches position from generator to ST6.

- A discharge from C<sub>I</sub> to the ST6 occurs.

- S2 must be closed 10 to 100ms after the pulse delivery period to ensure the ST6 is not left in charge state. S2 must be opened at least 10ms prior to the delivery of the next pulse.

- R (machine resistance), in series with S2, ensures a slow discharge of the ST6.

## **Absolute Maximum Ratings**

| Symbol                | Ratings                                             | Conditions            | Maximum value 1) | Unit |

|-----------------------|-----------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage (Human Body Model) | T <sub>A</sub> =+25°C | 2000             | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)    | T <sub>A</sub> =+25°C | 200              | V    |

#### Notes:

1. Data based on characterization results, not tested in production.

Figure 51. Typical Equivalent ESD Circuits

**477**

## EMC CHARACTERISTICS (Cont'd)

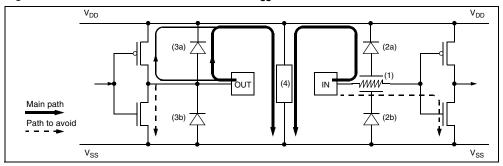

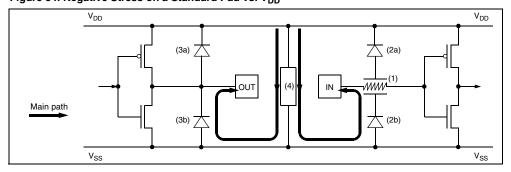

## 10.7.3 ESD Pin Protection Strategy

To protect an integrated circuit against Electro-Static Discharge the stress must be controlled to prevent degradation or destruction of the circuit elements. The stress generally affects the circuit elements which are connected to the pads but can also affect the internal devices when the supply pads receive the stress. The elements to be protected must not receive excessive current, voltage or heating within their structure.

An ESD network combines the different input and output ESD protections. This network works, by allowing safe discharge paths for the pins subjected to ESD stress. Two critical ESD stress cases are presented in Figure 53 and Figure 54 for standard pins.

#### Standard Pin Protection

To protect the output structure the following elements are added:

- A diode to V<sub>DD</sub> (3a) and a diode from V<sub>SS</sub> (3b)

- A protection device between  $V_{DD}$  and  $V_{SS}$  (4)

To protect the input structure the following elements are added:

- A resistor in series with the pad (1)

- A diode to V<sub>DD</sub> (2a) and a diode from V<sub>SS</sub> (2b)

- A protection device between V<sub>DD</sub> and V<sub>SS</sub> (4)

Figure 53. Positive Stress on a Standard Pad vs. V<sub>SS</sub>

Figure 54. Negative Stress on a Standard Pad vs. V<sub>DD</sub>

## **CONTROL PIN CHARACTERISTICS** (Cont'd)

## 10.10 TIMER PERIPHERAL CHARACTERISTICS

Subject to general operating conditions for  $\rm V_{DD}, f_{OSC},$  and  $\rm T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (TIMER).

## 10.10.1 Watchdog Timer

| Symbol              | Parameter                  | Conditions             | Min   | Тур | Max     | Unit             |

|---------------------|----------------------------|------------------------|-------|-----|---------|------------------|

| t <sub>w(WDG)</sub> | Watchdog time-out duration |                        | 3,072 |     | 196,608 | t <sub>INT</sub> |

|                     |                            | f <sub>CPU</sub> =4MHz | 0.768 |     | 49.152  | ms               |

|                     |                            | f <sub>CPU</sub> =8MHz | 0.384 |     | 24.576  | ms               |

#### 10.10.2 8-Bit Timer

| Symbol           | Parameter                      | Conditions | Min | Тур | Max                 | Unit |

|------------------|--------------------------------|------------|-----|-----|---------------------|------|

| f <sub>EXT</sub> | Timer external clock frequency |            | 0   |     | f <sub>INT</sub> /4 | MHz  |

| t <sub>w</sub>   | Pulse width at TIMER pin       | VDD>4.5V   | 125 |     |                     | ns   |

|                  |                                | VDD=3V     | 1   |     |                     | μs   |

57

83/100

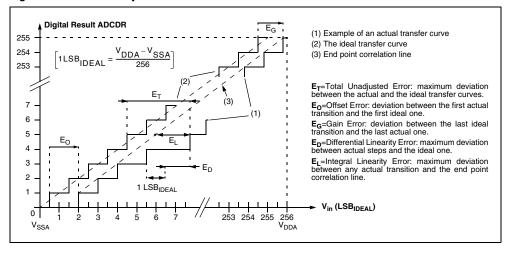

## 8-BIT ADC CHARACTERISTICS (Cont'd)

## **ADC Accuracy**

| Symbol            | Parameter                       | Conditions                        | Min | Тур.  | Max                               | Unit |

|-------------------|---------------------------------|-----------------------------------|-----|-------|-----------------------------------|------|

| IE <sub>T</sub> I | Total unadjusted error 1)       |                                   |     | 1.2   | ±2, fosc>1.2MHz<br>±4, fosc>32KHz |      |

| E <sub>O</sub>    | Offset error 1)                 | V <sub>DD</sub> =5V <sup>2)</sup> |     | 0.72  |                                   |      |

| E <sub>G</sub>    | Gain Error 1)                   | f <sub>OSC</sub> =8MHz            |     | -0.31 |                                   | LSB  |

| IE <sub>D</sub> I | Differential linearity error 1) |                                   |     | 0.54  |                                   |      |

| IE <sub>L</sub> I | Integral linearity error 1)     |                                   |     |       |                                   |      |

#### Notes:

- 1. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken: - Analog input pins must have a negative injection less than 1mA (assuming that the impedance of the analog voltage is lower than the specified limits).

- Pure digital pins must have a negative injection less than 1mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

- 2. Data based on characterization results over the whole temperature range, monitored in production.

Figure 67. ADC Accuracy Characteristics

Note: ADC not present on some devices. See device summary on page 1.

## 11 GENERAL INFORMATION

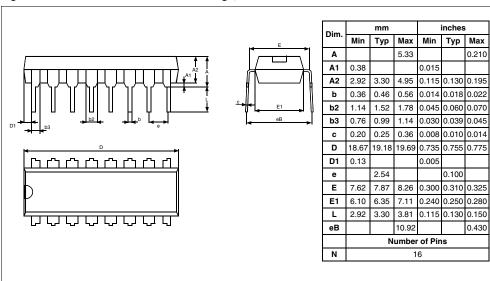

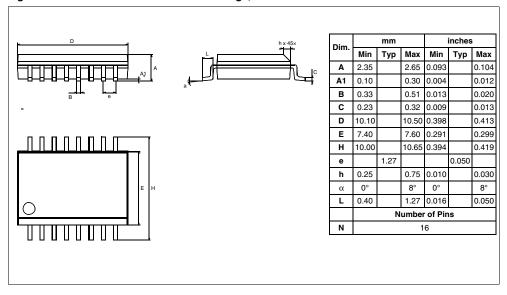

#### 11.1 PACKAGE MECHANICAL DATA

Figure 68. 16-Pin Plastic Dual In-Line Package, 300-mil Width

Figure 69. 16-Pin Plastic Small Outline Package, 300-mil Width

#### 11.6 TRANSFER OF CUSTOMER CODE

Customer code is made up of the ROM contents and the list of the selected FASTROM options. The ROM contents are to be sent on diskette, or by electronic means, with the hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected options are communicated to STMicroelectronics using the correctly filled OPTION LIST appended. See page 94.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

Listing Generation and Verification. When STMicroelectronics receives the user's ROM contents, a computer listing is generated from it. This listing refers exactly to the ROM contents and options which will be used to produce the specified MCU. The listing is then returned to the customer who must thoroughly check, complete, sign and return it to STMicroelectronics. The signed listing forms a part of the contractual agreement for the production of the specific customer MCU.

#### 11.6.1 FASTROM version

The ST62P00C, P01C and P03C are the Factory Advanced Service Technique ROM (FASTROM) versions of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, but they do not have to be programmed by the customer. The customer code must be sent to STMicroelectronics in the same way as for ROM devices. The FASTROM option list has the same options as defined in the programmable option byte of the OTP version. It also offers an identifier option. If this option is enabled, each FASTROM device is programmed with a unique 5-byte number which is mapped at addresses 0F9Bh-0F9Fh. The user must therefore leave these bytes blanked.

The identification number is structured as follows:

| 0F9Bh | T0      |

|-------|---------|

| 0F9Ch | T1      |

| 0F9Dh | T2      |

| 0F9Eh | T3      |

| 0F9Fh | Test ID |

with T0, T1, T2, T3 = time in seconds since 01/01/1970 and Test ID = Tester Identifier.

# TRANSFER OF CUSTOMER CODE (Cont'd) 11.6.2 ROM VERSION

The ST6200C, 01C and 03C are mask programmed ROM version of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, selecting as ROM options the options defined in the programmable option byte of the OTP version.

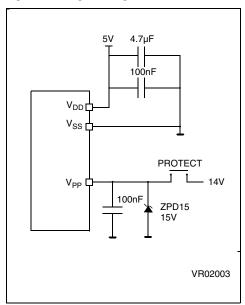

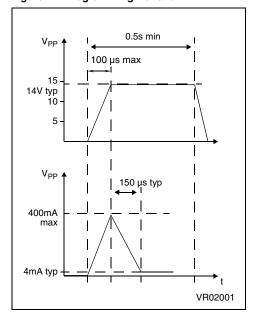

Figure 73. Programming Circuit

Note: ZPD15 is used for overvoltage protection

**ROM Readout Protection.** If the ROM READOUT PROTECTION option is selected, a protection fuse can be blown to prevent any access to the program memory content.

In case the user wants to blow this fuse, high voltage must be applied on the  $V_{PP}$  pin.

Figure 74. Programming wave form

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOM-MENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLI-CATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com