# E·XFL

Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| 2012                       |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST6                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, WDT                                                         |

| Number of I/O              | 9                                                                     |

| Program Memory Size        | 1KB (1K x 8)                                                          |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                               |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t03cm6-tr |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|    | 9.1  | ST6 ARCHITECTURE                                                               | 52       |

|----|------|--------------------------------------------------------------------------------|----------|

|    | 9.2  | ADDRESSING MODES                                                               | 52       |

|    | 9.3  | INSTRUCTION SET                                                                | 53       |

| 10 | ELE  | CTRICAL CHARACTERISTICS                                                        | 58       |

|    | 10.1 | PARAMETER CONDITIONS                                                           | 58       |

|    |      | 10.1.1 Minimum and Maximum Values                                              |          |

|    |      | 10.1.2Typical Values                                                           | 58       |

|    |      | 10.1.3Typical Curves                                                           |          |

|    |      | 10.1.5Pin Input Voltage                                                        |          |

|    |      | ABSOLUTE MAXIMUM RATINGS                                                       |          |

|    |      | 10.2.1 Voltage Characteristics                                                 | 59       |

|    |      | 10.2.2Current Characteristics                                                  |          |

|    | 10.3 | 10.2.3Thermal Characteristics                                                  |          |

|    |      | 10.3.1 General Operating Conditions                                            |          |

|    |      | 10.3.20perating Conditions with Low Voltage Detector (LVD)                     |          |

|    | 10.4 | SUPPLY CURRENT CHARACTERISTICS                                                 | 62       |

|    |      | 10.4.1 RUN Modes                                                               |          |

|    |      | 10.4.2WAIT Modes                                                               |          |

|    |      | 10.4.3STOP Mode                                                                |          |

|    |      | 10.4.5On-Chip Peripherals                                                      |          |

|    |      | CLOCK AND TIMING CHARACTERISTICS                                               |          |

|    |      | 10.5.1 General Timings                                                         |          |

|    |      | 10.5.2External Clock Source                                                    | 68       |

|    |      | 10.5.3Crystal and Ceramic Resonator Oscillators         10.5.4RC Oscillator    | 69<br>70 |

|    |      | 10.5.5Oscillator Safeguard (OSG) and Low Frequency Auxiliary Oscillator (LFAO) |          |

|    |      | MEMORY CHARACTERISTICS                                                         |          |

|    |      | 10.6.1 RAM and Hardware Registers                                              |          |

|    |      | 10.6.2EPROM Program Memory                                                     |          |

|    |      | EMC CHARACTERISTICS                                                            |          |

|    |      | 10.7.1 Functional EMS         10.7.2 Absolute Electrical Sensitivity           |          |

|    |      | 10.7.3ESD Pin Protection Strategy                                              |          |

|    |      | I/O PORT PIN CHARACTERISTICS                                                   |          |

|    |      | 10.8.1 General Characteristics                                                 |          |

|    | 40.0 | 10.8.20utput Driving Current                                                   | 78       |

|    |      |                                                                                |          |

|    |      | 10.9.1 Asynchronous RESET Pin                                                  |          |

|    | 10.1 | 0 TIMER PERIPHERAL CHARACTERISTICS                                             |          |

|    |      | 10.10.1Watchdog Timer                                                          | 83       |

|    |      | 10.10.28-Bit Timer                                                             | 83       |

|    | 10.1 | 1 8-BIT ADC CHARACTERISTICS                                                    | 84       |

# **1 INTRODUCTION**

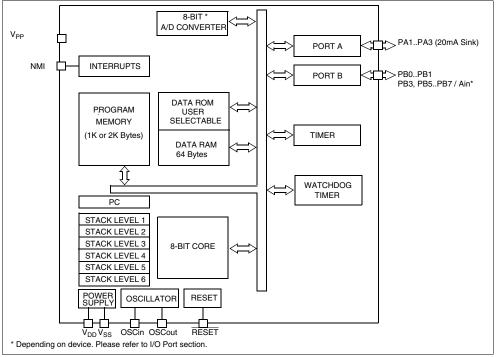

The ST6200C, 01C and 03C devices are low cost members of the ST62xx 8-bit HCMOS family of microcontrollers, which is targeted at low to medium complexity applications. All ST62xx devices are based on a building block approach: a common core is surrounded by a number of on-chip peripherals.

The ST62E01C is the erasable EPROM version of the ST62T00C, T01 and T03C devices, which may be used during the development phase for the ST62T00C, T01 and T03C target devices, as well as the respective ST6200C, 01C and 03C ROM devices.

OTP and EPROM devices are functionally identical. OTP devices offer all the advantages of user programmability at low cost, which make them the ideal choice in a wide range of applications where frequent code changes, multiple code versions or last minute programmability are required.

The ROM based versions offer the same functionality, selecting the options defined in the programmable option bytes of the OTP/EPROM versions in the ROM option list (See Section 11.6 on page 92).

The ST62P00C, P01C and P03C are the Factory Advanced Service Technique ROM (FASTROM) versions of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, but they do not have to be programmed by the customer (See Section 11 on page 86).

These compact low-cost devices feature a Timer comprising an 8-bit counter with a 7-bit programmable prescaler, an 8-bit A/D Converter with 4 analog inputs (depending on device, see device summary on page 1) and a Digital Watchdog timer, making them well suited for a wide range of automotive, appliance and industrial applications.

For easy reference, all parametric data are located in Section 10 on page 58.

Figure 1. Block Diagram

### CPU REGISTERS (Cont'd)

The 12-bit length allows the direct addressing of 4096 bytes in Program Space.

However, if the program space contains more than 4096 bytes, the additional memory in program space can be addressed by using the Program ROM Page register.

The PC value is incremented after reading the address of the current instruction. To execute relative jumps, the PC and the offset are shifted through the ALU, where they are added; the result is then shifted back into the PC. The program counter can be changed in the following ways:

- CALL instruction

PC = Call address

- Relative Branch InstructionPC = PC +/- offset

| <ul> <li>Interrupt</li> </ul> | PC = Interrupt vector |

|-------------------------------|-----------------------|

| - Reset                       | PC = Reset vector     |

- RET & RETI instructions PC = Pop (stack)

- Normal instruction PC = PC + 1

Flags (C, Z). The ST6 CPU includes three pairs of flags (Carry and Zero), each pair being associated with one of the three normal modes of operation: Normal mode, Interrupt mode and Non Maskable Interrupt mode. Each pair consists of a CARRY flag and a ZERO flag. One pair (CN, ZN) is used during Normal operation, another pair is used during Interrupt mode (CI, ZI), and a third pair is used in the Non Maskable Interrupt mode (CNMI, ZN-MI).

The ST6 CPU uses the pair of flags associated with the current mode: as soon as an interrupt (or a Non Maskable Interrupt) is generated, the ST6 CPU uses the Interrupt flags (or the NMI flags) instead of the Normal flags. When the RETI instruction is executed, the previously used set of flags is restored. It should be noted that each flag set can only be addressed in its own context (Non Maskable Interrupt, Normal Interrupt or Main routine). The flags are not cleared during context switching and thus retain their status.

#### C : Carry flag.

This bit is set when a carry or a borrow occurs during arithmetic operations; otherwise it is cleared. The Carry flag is also set to the value of the bit tested in a bit test instruction; it also participates in the rotate left instruction.

0: No carry has occured

1: A carry has occured

#### Z : Zero flag

This flag is set if the result of the last arithmetic or logical operation was equal to zero; otherwise it is cleared.

- 0: The result of the last operation is different from zero

- 1: The result of the last operation is zero

Switching between the three sets of flags is performed automatically when an NMI, an interrupt or a RETI instruction occurs. As NMI mode is automatically selected after the reset of the MCU, the ST6 core uses the NMI flags first.

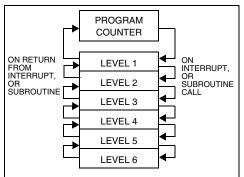

Stack. The ST6 CPU includes a true LIFO (Last In First Out) hardware stack which eliminates the need for a stack pointer. The stack consists of six separate 12-bit RAM locations that do not belong to the data space RAM area. When a subroutine call (or interrupt request) occurs, the contents of each level are shifted into the next level down, while the content of the PC is shifted into the first level (the original contents of the sixth stack level are lost). When a subroutine or interrupt return occurs (RET or RETI instructions), the first level register is shifted back into the PC and the value of each level is popped back into the previous level.

#### Figure 8. Stack manipulation

Since the accumulator, in common with all other data space registers, is not stored in this stack, management of these registers should be performed within the subroutine.

**Caution:** The stack will remain in its "deepest" position if more than 6 nested calls or interrupts are executed, and consequently the last return address will be lost.

It will also remain in its highest position if the stack is empty and a RET or RETI is executed. In this case the next instruction will be executed.

# **5 CLOCKS, SUPPLY AND RESET**

#### 5.1 CLOCK SYSTEM

The main oscillator of the MCU can be driven by any of these clock sources:

- external clock signal

- external AT-cut parallel-resonant crystal

- external ceramic resonator

- external RC network (R<sub>NET</sub>).

In addition, an on-chip Low Frequency Auxiliary Oscillator (LFAO) is available as a back-up clock system or to reduce power consumption.

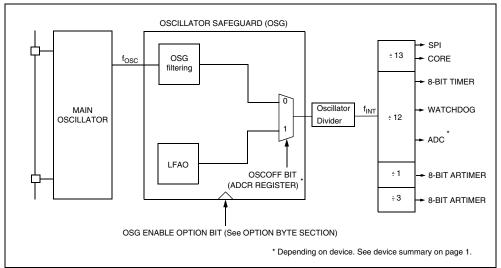

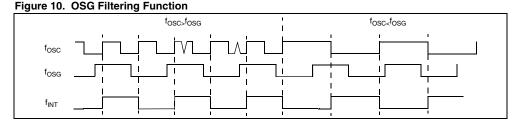

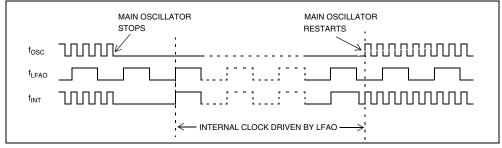

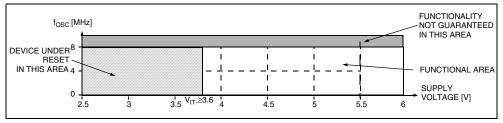

An optional Oscillator Safeguard (OSG) filters spikes from the oscillator lines, and switches to the LFAO backup oscillator in the event of main oscillator failure. It also automatically limits the internal clock frequency ( $f_{\rm INT}$ ) as a function of  $V_{DD}$ , in order to guarantee correct operation. These functions are illustrated in Figure 10, and Figure 11.

Table 5 illustrates various possible oscillator configurations using an external crystal or ceramic resonator, an external clock input, an external resistor ( $R_{NET}$ ), or the lowest cost solution using only the LFAO.

For more details on configuring the clock options, refer to the Option Bytes section of this document.

The internal MCU clock frequency ( $f_{INT}$ ) is divided by 12 to drive the Timer, the Watchdog timer and the A/D converter, by 13 to drive the CPU core and the SPI and by 1 or 3 to drive the ARTIMER, as shown in Figure 9.

With an 8 MHz oscillator, the fastest CPU cycle is therefore  $1.625\mu s$ .

A CPU cycle is the smallest unit of time needed to execute any operation (for instance, to increment the Program Counter). An instruction may require two, four, or five CPU cycles for execution.

47/

### Figure 9. Clock Circuit Block Diagram

### CLOCK SYSTEM (Cont'd)

#### 5.1.2 Oscillator Safeguard (OSG)

The Oscillator Safeguard (OSG) feature is a means of dramatically improving the operational integrity of the MCU. It is available when the OSG ENABLED option is selected in the option byte (refer to the Option Bytes section of this document).

The OSG acts as a filter whose cross-over frequency is device dependent and provides three basic functions:

- Filtering spikes on the oscillator lines which would result in driving the CPU at excessive frequencies

- Management of the Low Frequency Auxiliary Oscillator (LFAO), (useable as low cost internal clock source, backup clock in case of main oscillator failure or for low power consumption)

- Automatically limiting the f<sub>INT</sub> clock frequency as a function of supply voltage, to ensure correct operation even if the power supply drops.

#### 5.1.2.1 Spike Filtering

Spikes on the oscillator lines result in an effectively increased internal clock frequency. In the absence of an OSG circuit, this may lead to an over frequency for a given power supply voltage. The OSG filters out such spikes (as illustrated in Figure 10). In all cases, when the OSG is active, the maximum internal clock frequency,  $f_{INT}$ , is limited to  $f_{OSG}$ , which is supply voltage dependent.

# 5.1.2.2 Management of Supply Voltage Variations

Over-frequency, at a given power supply level, is seen by the OSG as spikes; it therefore filters out some cycles in order that the internal clock frequency of the device is kept within the range the particular device can stand (depending on  $V_{DD}$ ), and below  $f_{OSG}$ : the maximum authorised frequency with OSG enabled.

#### 5.1.2.3 LFAO Management

When the OSG is enabled, the Low Frequency Auxiliary Oscillator can be used (see Section 5.1.3).

**Note:** The OSG should be used wherever possible as it provides maximum security for the application. It should be noted however, that it can increase power consumption and reduce the maximum operating frequency to f<sub>OSG</sub> (see Electrical Characteristics section).

**Caution:** Care has to be taken when using the OSG, as the internal frequency is defined between a minimum and a maximum value and may vary depending on both  $V_{DD}$  and temperature. For precise timing measurements, it is not recommended to use the OSG.

#### Figure 11. LFAO Oscillator Function

#### RESET (Cont'd)

#### 5.3.4 Watchdog Reset

The MCU provides a Watchdog timer function in order to be able to recover from software hangups. If the Watchdog register is not refreshed before an end-of-count condition is reached, a Watchdog reset is generated.

After a Watchdog reset, the MCU restarts in the same way as if a Reset was generated by the  $\overline{\text{RE-SET}}$  pin.

**Note:** When a watchdog reset occurs, the **RESET** pin is tied low for very short time period, to flag the reset phase. This time is not long enough to reset external circuits.

For more details refer to the Watchdog Timer chapter.

#### 5.3.5 LVD Reset

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

During an LVD reset, the  $\overline{\text{RESET}}$  pin is pulled low when  $V_{DD} < V_{TT+}$  (rising edge) or  $V_{DD} < V_{TT-}$  (falling edge).

For more details, refer to the LVD chapter.

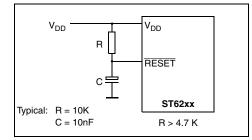

**<u>Caution</u>**: Do not externally connect directly the RESET pin to  $V_{DD}$ , this may cause damage to the component in case of internal RESET (Watchdog or LVD).

#### Figure 15. Simple External Reset Circuitry

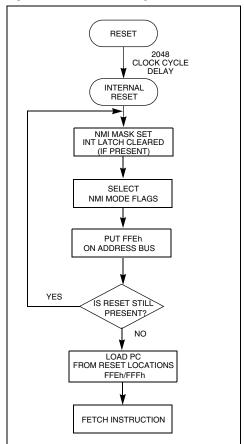

#### Figure 16. Reset Processing

#### 5.5 INTERRUPT RULES AND PRIORITY MANAGEMENT

- A Reset can interrupt the NMI and peripheral interrupt routines

- The Non Maskable Interrupt request has the highest priority and can interrupt any peripheral interrupt routine at any time but cannot interrupt another NMI interrupt.

- No peripheral interrupt can interrupt another. If more than one interrupt request is pending, these are processed by the processor core according to their priority level: vector #1 has the highest priority while vector #4 the lowest. The priority of each interrupt source is fixed by hardware (see Interrupt Mapping table).

#### 5.6 INTERRUPTS AND LOW POWER MODES

All interrupts cause the processor to exit from WAIT mode. Only the external and some specific interrupts from the on-chip peripherals cause the processor to exit from STOP mode (refer to the "Exit from STOP" column in the Interrupt Mapping Table).

#### 5.7 NON MASKABLE INTERRUPT

This interrupt is triggered when a falling edge occurs on the NMI pin regardless of the state of the GEN bit in the IOR register. An interrupt request on NMI vector #0 is latched by a flip flop which is automatically reset by the core at the beginning of the NMI service routine.

#### **5.8 PERIPHERAL INTERRUPTS**

Different peripheral interrupt flags in the peripheral control registers are able to cause an interrupt when they are active if both:

- The GEN bit of the IOR register is set

- The corresponding enable bit is set in the peripheral control register.

Peripheral interrupts are linked to vectors #3 and #4. Interrupt requests are flagged by a bit in their corresponding control register. This means that a request cannot be lost, because the flag bit must be cleared by user software.

# 6.3 STOP MODE

STOP mode is the lowest power consumption mode of the MCU (see Figure 22).

The MCU goes into STOP mode as soon as the STOP instruction is executed. This has the following effects:

- Program execution is stopped, the microcontroller can be considered as being "frozen".

- The contents of RAM and the peripheral registers are kept safely as long as the power supply voltage is higher than the RAM retention voltage.

- The oscillator is stopped, so peripherals cannot work except the those that can be driven by an external clock.

## Exit from STOP Mode

The MCU remains in STOP mode until one of the following events occurs:

- RESET (Watchdog, LVD or RESET pin)

- A peripheral interrupt (assuming this peripheral can be driven by an external clock)

- An external interrupt (I/O port, NMI)

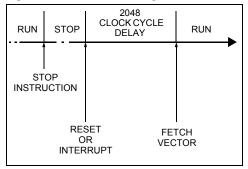

In all cases a delay of 2048 clock cycles ( $f_{\text{INT}}$ ) is generated to make sure the oscillator has started properly.

The Program Counter then points to the starting address of the interrupt or RESET service routine (see Figure 21).

#### STOP Mode and Watchdog

When the Watchdog is active (hardware or software activation), the STOP instruction is disabled and a WAIT instruction will be executed in its place unless the EXCTNL option bit is set to 1 in the option bytes and a a high level is present on the NMI pin. In this case, the STOP instruction will be executed and the Watchdog will be frozen.

#### Figure 21. STOP Mode Timing Overview

#### I/O PORTS (Cont'd)

#### 7.5 REGISTER DESCRIPTION

#### DATA REGISTER (DR)

Port x Data Register DRx with x = A or B. Address DRA: 0C0h - Read/Write Address DRB: 0C1h - Read/Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7:0 = D[7:0] Data register bits.

Reading the DR register returns either the DR register latch content (pin configured as output) or the digital value applied to the I/O pin (pin configured as input).

**Caution:** In input mode, modifying this register will modify the I/O port configuration (see Table 8).

Do not use the Single bit instructions on I/O port data registers. See (Section 7.2.5).

#### DATA DIRECTION REGISTER (DDR)

Port x Data Direction Register DDRx with x = A or B.

Address DDRA: 0C4h - Read/Write Address DDRB: 0C5h - Read/Write Reset Value: 0000 0000 (00h)

| /   | 7   |     |     |     |     |     |     |  |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|--|

| DD7 | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |  |

#### Table 10. I/O Port Register Map and Reset Values

#### Bit 7:0 = DD[7:0] Data direction register bits.

The DDR register gives the input/output direction configuration of the pins. Each bit is set and cleared by software. 0: Input mode 1: Output mode

#### **OPTION REGISTER (OR)**

Port x Option Register ORx with x = A or B.

Address ORA: 0CCh - Read/Write Address ORB: 0CDh - Read/Write Reset Value: 0000 0000 (00h)

| 7  | 7  |    |    |    |    |    |    |  |

|----|----|----|----|----|----|----|----|--|

| 07 | O6 | O5 | O4 | O3 | 02 | 01 | 00 |  |

Bit 7:0 = **O**[7:0] Option register bits.

The OR register allows to distinguish in output mode if the push-pull or open drain configuration is selected.

#### Output mode:

0: Open drain output(with P-Buffer deactivated) 1: Push-pull Output

Input mode: See Table 8.

Each bit is set and cleared by software.

**Caution:** Modifying this register, will also modify the I/O port configuration in input mode. (see Table 8).

| Address<br>(Hex.)                        | Register<br>Label | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0   |     |

|------------------------------------------|-------------------|------|-----|---|---|---|---|---|-----|-----|

| Reset Value<br>of all I/O port registers |                   | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0   |     |

| 0C0h                                     | DRA               | MSB  | MCB |   |   |   |   |   |     | LSB |

| 0C1h                                     | DRB               |      |     |   |   |   |   |   | LOD |     |

| 0C4h                                     | DDRA              | MSB  |     |   |   |   |   |   | LSB |     |

| 0C5h                                     | DDRB              | NISD |     |   |   |   |   |   | LOD |     |

| 0CCh                                     | ORA               | MSB  |     |   |   |   |   |   | LSB |     |

| 0CDh                                     | ORB               | NISD |     |   |   |   |   |   | LOD |     |

# 9 INSTRUCTION SET

#### 9.1 ST6 ARCHITECTURE

The ST6 architecture has been designed for maximum efficiency while keeping byte usage to a minimum; in short, to provide byte-efficient programming. The ST6 core has the ability to set or clear any register or RAM location bit in Data space using a single instruction. Furthermore, programs can branch to a selected address depending on the status of any bit in Data space.

#### 9.2 ADDRESSING MODES

The ST6 has nine addressing modes, which are described in the following paragraphs. Three different address spaces are available: Program space, Data space, and Stack space. Program space contains the instructions which are to be excuted, plus the data for immediate mode instructions. Data space contains the Accumulator, the X, Y, V and W registers, peripheral and Input/Output registers, the RAM locations and Data ROM locations (for storage of tables and constants). Stack space contains six 12-bit RAM cells used to stack the return addresses for subroutines and interrupts.

**Immediate**. In immediate addressing mode, the operand of the instruction follows the opcode location. As the operand is a ROM byte, the immediate addressing mode is used to access constants which do not change during program execution (e.g., a constant used to initialize a loop counter).

**Direct.** In direct addressing mode, the address of the byte which is processed by the instruction is stored in the location which follows the opcode. Direct addressing allows the user to directly address the 256 bytes in Data Space memory with a single two-byte instruction.

**Short Direct**. The core can address the four RAM registers X, Y, V, W (locations 80h, 81h, 82h, 83h) in short-direct addressing mode. In this case, the instruction is only one byte and the selection of the location to be processed is contained in the op-code. Short direct addressing is a subset of direct addressing mode. (Note that 80h and 81h are also indirect registers).

**Extended**. In extended addressing mode, the 12bit address needed to define the instruction is obtained by concatenating the four least significant bits of the opcode with the byte following the opcode. The instructions (JP, CALL) which use extended addressing mode are able to branch to any address in the 4 Kbyte Program space.

Extended addressing mode instructions are two bytes long.

Program Counter Relative. Relative addressing mode is only used in conditional branch instructions. The instruction is used to perform a test and, if the condition is true, a branch with a span of -15 to +16 locations next to the address of the relative instruction. If the condition is not true, the instruction which follows the relative instruction is executed. Relative addressing mode instructions are one byte long. The opcode is obtained by adding the three most significant bits which characterize the test condition, one bit which determines whether it is a forward branch (when it is 0) or backward branch (when it is 1) and the four least significant bits which give the span of the branch (0h to Fh) which must be added or subtracted from the address of the relative instruction to obtain the branch destination address.

**Bit Direct.** In bit direct addressing mode, the bit to be set or cleared is part of the opcode, and the byte following the opcode points to the address of the byte in which the specified bit must be set or cleared. Thus, any bit in the 256 locations of Data space memory can be set or cleared.

**Bit Test & Branch**. Bit test and branch addressing mode is a combination of direct addressing and relative addressing. Bit test and branch instructions are three bytes long. The bit identification and the test condition are included in the opcode byte. The address of the byte to be tested is given in the next byte. The third byte is the jump displacement, which is in the range of -127 to +128. This displacement can be determined using a label, which is converted by the assembler.

**Indirect**. In indirect addressing mode, the byte processed by the register-indirect instruction is at the address pointed to by the content of one of the indirect registers, X or Y (80h, 81h). The indirect register is selected by bit 4 of the opcode. Register indirect instructions are one byte long.

**Inherent**. In inherent addressing mode, all the information necessary for executing the instruction is contained in the opcode. These instructions are one byte long.

# **OPERATING CONDITIONS** (Cont'd)

# 10.3.2 Operating Conditions with Low Voltage Detector (LVD)

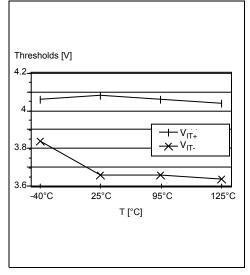

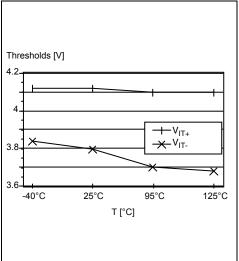

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$ .

| Symbol              | Parameter                                         | Conditions                         | Min | Typ <sup>1)</sup> | Max | Unit |

|---------------------|---------------------------------------------------|------------------------------------|-----|-------------------|-----|------|

| V <sub>IT+</sub>    | Reset release threshold<br>(V <sub>DD</sub> rise) |                                    | 3.9 | 4.1               | 4.3 | v    |

| V <sub>IT-</sub>    | Reset generation threshold (V <sub>DD</sub> fall) |                                    | 3.6 | 3.8               | 4   | v    |

| V <sub>hys</sub>    | LVD voltage threshold hysteresis                  | V <sub>IT+</sub> -V <sub>IT-</sub> | 50  | 300               | 700 | mV   |

| Vt <sub>POR</sub>   | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                    |     |                   |     | mV/s |

| t <sub>g(VDD)</sub> | Filtered glitch delay on V <sub>DD</sub> 3)       | Not detected by the LVD            |     | 30                |     | ns   |

#### Notes:

1. LVD typical data are based on  $T_A=25^{\circ}C$ . They are given only as design guidelines and are not tested.

The minimum V<sub>DD</sub> rise time rate is needed to insure a correct device power-on and LVD reset. Not tested in production.

Data based on characterization results, not tested in production.

# Figure 33. LVD Threshold Versus V<sub>DD</sub> and f<sub>OSC</sub><sup>3)</sup>

Figure 34. Typical LVD Thresholds Versus Temperature for OTP devices

# Figure 35. Typical LVD thresholds vs. Temperature for ROM devices

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

#### 10.4.2 WAIT Modes

| Symbol          | Parameter                                                                                      |                          |                                    | Conditions                                                                                                                                                     | Typ 1)                          | Max <sup>2)</sup>               | Unit |

|-----------------|------------------------------------------------------------------------------------------------|--------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------|

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 38)    |                          | devices                            | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz                                | 330<br>350<br>370<br>410<br>480 | 550<br>600<br>650<br>700<br>800 |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) | 4.5VÝ <sub>DD</sub> ⑤.0V | .5V≰⁄ <sub>DD</sub> ≸.0V<br>OTP de | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 18<br>26<br>41<br>57<br>70      | 60<br>80<br>120<br>180<br>200   |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>(see Figure 40)                                   |                          | ROM devices                        | $\begin{array}{l} f_{OSC}=32kHz\\ f_{OSC}=1MHz\\ f_{OSC}=2MHz\\ f_{OSC}=2MHz\\ f_{OSC}=4MHz\\ f_{OSC}=8MHz \end{array}$                                        | 190<br>210<br>240<br>280<br>350 | 300<br>350<br>400<br>500<br>600 |      |

| I <sub>DD</sub> | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 38)    |                          | devices                            | f <sub>OSC</sub> =32kHz<br>f <sub>OSC</sub> =1MHz<br>f <sub>OSC</sub> =2MHz<br>f <sub>OSC</sub> =4MHz<br>f <sub>OSC</sub> =8MHz                                | 80<br>90<br>100<br>120<br>150   | 120<br>140<br>150<br>200<br>250 | μA   |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes programmed to 00H<br>(see Figure 39) | 3V≰⁄ <sub>DD</sub> 3.6V  | OTP d                              | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 5<br>8<br>16<br>18<br>20        | 30<br>40<br>50<br>60<br>100     |      |

|                 | Supply current in WAIT mode <sup>3)</sup><br>Option bytes not programmed<br>(see Figure 40)    |                          | ROM devices                        | $\begin{array}{l} f_{OSC} = 32 \text{kHz} \\ f_{OSC} = 1 \text{MHz} \\ f_{OSC} = 2 \text{MHz} \\ f_{OSC} = 4 \text{MHz} \\ f_{OSC} = 8 \text{MHz} \end{array}$ | 60<br>65<br>80<br>100<br>130    | 100<br>110<br>120<br>150<br>210 |      |

#### Notes:

67/

1. Typical data are based on T<sub>A</sub>=25°C, V<sub>DD</sub>=5V (4.5V $\$V_{DD}$ \$.0V range) and V<sub>DD</sub>=3.3V (3V $\$V_{DD}$ \$.6V range).

Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>OSC</sub> max.

All I/O pins in input with pull-up mode (no load), all peripherals in reset state; clock input (OSC<sub>IN</sub>) driven by external square wave, OSG and LVD disabled.

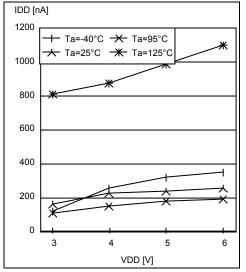

### SUPPLY CURRENT CHARACTERISTICS (Cont'd) 10.4.3 STOP Mode

| Symbol | Parameter                                 | Conditions  | Typ <sup>1)</sup> | Max                                  | Unit |

|--------|-------------------------------------------|-------------|-------------------|--------------------------------------|------|

|        | Supply current in STOP mode <sup>2)</sup> | OTP devices | 0.3               | 10 <sup>3)</sup><br>20 <sup>4)</sup> |      |

| IDD    | (see Figure 41 & Figure 42)               | ROM devices | 0.1               | 2 <sup>3)</sup><br>20 <sup>4)</sup>  | μA   |

#### Notes:

- 1. Typical data are based on  $V_{DD}$ =5.0V at T<sub>A</sub>=25°C.

- All I/O pins in input with pull-up mode (no load), all peripherals in reset state, OSG and LVD disabled, option bytes programmed to 00H. Data based on characterization results, tested in production at V<sub>DD</sub> max. and f<sub>CPU</sub> max.

- 3. Maximum STOP consumption for -40°C<Ta<90°C

- 4. Maximum STOP consumption for -40°C<Ta<125°C

# Figure 41. Typical $I_{\text{DD}}$ in STOP vs Temperature for OTP devices

# Figure 42. Typical $I_{\text{DD}}$ in STOP vs Temperature for ROM devices

#### **10.7 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

#### 10.7.1 Functional EMS

(Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed.

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                     | Neg <sup>1)</sup> | Pos <sup>1)</sup> | Unit |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|-------------------|------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | -2                | 2                 |      |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{DD}$ pins to induce a functional disturbance | $V_{DD}$ =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz conforms to IEC 1000-4-4           | -2.5              | 3                 | kV   |

#### Notes:

1. Data based on characterization results, not tested in production.

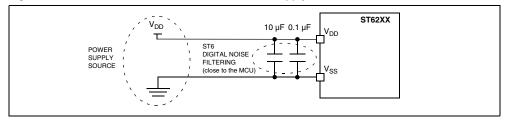

The suggested 10 μF and 0.1 μF decoupling capacitors on the power supply lines are proposed as a good price vs. EMC performance tradeoff. They have to be put as close as possible to the device power supply pins. Other EMC recommendations are given in other sections (I/Os, RESET, OSCx pin characteristics).

#### Figure 50. EMC Recommended Star Network Power Supply Connection<sup>2)</sup>

# CONTROL PIN CHARACTERISTICS (Cont'd)

## 10.10 TIMER PERIPHERAL CHARACTERISTICS

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (TIMER).

#### 10.10.1 Watchdog Timer

| Symbol              | Parameter                  | Conditions             | Min   | Тур | Max     | Unit             |

|---------------------|----------------------------|------------------------|-------|-----|---------|------------------|

| t <sub>w(WDG)</sub> | Watchdog time-out duration |                        | 3,072 |     | 196,608 | t <sub>INT</sub> |

|                     |                            | f <sub>CPU</sub> =4MHz | 0.768 |     | 49.152  | ms               |

|                     |                            | f <sub>CPU</sub> =8MHz | 0.384 |     | 24.576  | ms               |

#### 10.10.2 8-Bit Timer

| Symbol           | Parameter                      | Conditions | Min | Тур | Max                 | Unit |

|------------------|--------------------------------|------------|-----|-----|---------------------|------|

| f <sub>EXT</sub> | Timer external clock frequency |            | 0   |     | f <sub>INT</sub> /4 | MHz  |

| t <sub>w</sub>   | Pulse width at TIMER pin       | VDD>4.5V   | 125 |     |                     | ns   |

|                  |                                | VDD=3V     | 1   |     |                     | μs   |

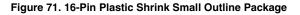

# PACKAGE MECHANICAL DATA (Cont'd)

#### inches mm Dim Min Min Тур Max Тур Max Α 3.78 0.149 G1 A1 0.38 0.015 0.36 0.56 0.014 0.018 0.022 в 0.46 B1 1.14 1.37 1.78 0.045 0.054 0.070 С 0.20 0.25 0.36 0.008 0.010 0.014 D 19.86 20.32 20.78 0.782 0.800 0.818 D1 17.78 0.700 0.277 0.295 0.313 E1 7.04 7.49 7.95 2.54 0.100 е G 6.35 6.60 6.86 0.250 0.260 0.270 F1 G1 9.47 9.73 9.98 0.373 0.383 0.393 G2 1.02 0.040 B1 L 2.92 3.30 3.81 0.115 0.130 0.150 D1 s 1.27 0.050 CDIP16W D ø 4.22 0.166 Number of Pins Ν 16

## Figure 70. 16-Pin Ceramic Side-Brazed Dual In-Line Package

57

#### **11.3 ECOPACK INFORMATION**

In order to meet environmental requirements, ST offers these devices in different grades of ECO-PACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

# TRANSFER OF CUSTOMER CODE (Cont'd)

### 11.6.2 ROM VERSION

The ST6200C, 01C and 03C are mask programmed ROM version of ST62T00C, T01 and T03C OTP devices.

They offer the same functionality as OTP devices, selecting as ROM options the options defined in the programmable option byte of the OTP version.

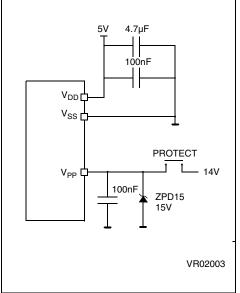

Note: ZPD15 is used for overvoltage protection

**ROM Readout Protection.** If the ROM READOUT PROTECTION option is selected, a protection fuse can be blown to prevent any access to the program memory content.

In case the user wants to blow this fuse, high voltage must be applied on the  $V_{\mbox{\scriptsize PP}}$  pin.

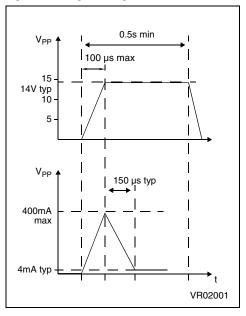

Figure 74. Programming wave form

# TRANSFER OF CUSTOMER CODE (Cont'd)

| Customer:<br>Address:<br>Contact:<br>Phone:       |                                        |                                                                |                                                                                                                            |  |  |

|---------------------------------------------------|----------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Contact:<br>Phone:                                |                                        |                                                                |                                                                                                                            |  |  |

| Phone:                                            |                                        | • • • • • • • • • • • • • • • • • • • •                        |                                                                                                                            |  |  |

| Phone:                                            |                                        |                                                                |                                                                                                                            |  |  |

|                                                   |                                        |                                                                |                                                                                                                            |  |  |

| Reference:                                        |                                        |                                                                |                                                                                                                            |  |  |

| STMicroelect                                      | tronics reference                      | es:                                                            |                                                                                                                            |  |  |

| Device:                                           |                                        | [ ] ST6200C (1 KB)<br>[ ] ST6201C (2 KB)<br>[ ] ST6203C (1 KB) | [ ] ST62P00C (1 KB)<br>[ ] ST62P01C (2 KB)<br>[ ] ST62P03C (1 KB)                                                          |  |  |

| Package:                                          |                                        |                                                                | [] Dual in Line Plastic<br>[] Small Outline Plastic with conditioning<br>[] Shrink Small Outline Plastic with conditioning |  |  |

| Conditioning option:                              |                                        | [] Standard (Tube)                                             | 5                                                                                                                          |  |  |

| Temperature Range:                                |                                        | [ ] Tape & Reel<br>[ ] 0°C to + 70°C<br>[ ] - 40°C to + 125°C  | [] - 40°C to + 85°C                                                                                                        |  |  |

| Marking:                                          |                                        | SO16 (6 char. m                                                | max):                                                                                                                      |  |  |

| Authorized ch                                     | aracters are lette                     | rs, digits, '.', '-', '/' and spaces only.                     |                                                                                                                            |  |  |

| Oscillator Safe<br>Watchdog Sel                   | •                                      | [] Enabled [] Software Activation                              | [] Disabled                                                                                                                |  |  |

| NMI pull-up:<br>Oscillator Selection:             |                                        | [] Enabled                                                     | [] Quartz crystal / Ceramic resonator                                                                                      |  |  |

| Readout Prote                                     | ection:                                | FASTROM:<br>[] Enabled<br>ROM:                                 | [] Disabled                                                                                                                |  |  |

|                                                   |                                        | [] Enabled:<br>[] Fuse is blown                                | by STMicroelectronics<br>plown by the customer                                                                             |  |  |

| Low Voltage E<br>External STOF<br>Identifier (FAS | P Mode Control:                        | [] Enabled<br>[] Enabled<br>[] Enabled                         | [] Disabled<br>[] Disabled<br>[] Disabled                                                                                  |  |  |

|                                                   |                                        | []                                                             | []=                                                                                                                        |  |  |

| Comments:                                         |                                        |                                                                |                                                                                                                            |  |  |

|                                                   | quency in the app<br>ting Range in the |                                                                |                                                                                                                            |  |  |

# **12 DEVELOPMENT TOOLS**

STMicroelectronics offers a range of hardware and software development tools for the ST6 microcontroller family. Full details of tools available for the ST6 from third party manufacturers can be obtain from the STMicroelectronics Internet site: → http://www.st.com.

| Third Party <sup>1)</sup> | Designation                                                                                                                                                                                                                                                                                                       | CT Coles Tures     | Web eite eddrec -                                   |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------|--|

| Inira Party "             | Designation                                                                                                                                                                                                                                                                                                       | ST Sales Type      | Web site address                                    |  |

| ACTUM                     | ST-REALIZER II: Graphical Schematic<br>based Development available from<br>STMicroelectronics.                                                                                                                                                                                                                    | STREALIZER-II      | http://www.actum.com/                               |  |

| CEIBO                     | Low cost emulator available from CEI-<br>BO.                                                                                                                                                                                                                                                                      |                    | http://www.ceibo.com/                               |  |

| RAISONANCE                | This tool includes in the same environ-<br>ment: an assembler, linker, C compiler,<br>debugger and simulator. The assembler<br>package (plus limited C compiler) is free<br>and can be downloaded from raisonance<br>web site. The full version is available<br>both from STMicroelectronics and Raiso-<br>nance. | ST6RAIS-SWC/<br>PC | http://www.raisonance.com/                          |  |

| SOFTEC                    | High end emulator available from SOFTEC.                                                                                                                                                                                                                                                                          |                    | http://www.softecmicro.com/                         |  |

|                           | Gang programmer available from<br>SOFTEC.                                                                                                                                                                                                                                                                         |                    |                                                     |  |

| ADVANCED EQUIPMENT        |                                                                                                                                                                                                                                                                                                                   |                    | http://www.aec.com.tw/                              |  |

| ADVANCED TRANSDATA        |                                                                                                                                                                                                                                                                                                                   |                    | http://www.adv-transdata.com/                       |  |

| BP MICROSYSTEMS           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.bpmicro.com/                             |  |

| DATA I/O                  |                                                                                                                                                                                                                                                                                                                   |                    | http://www.data-io.com/                             |  |

| DATAMAN                   |                                                                                                                                                                                                                                                                                                                   |                    | http://www.dataman.com/                             |  |

| EE TOOLS                  |                                                                                                                                                                                                                                                                                                                   |                    | http://www.eetools.com/                             |  |

| ELNEC                     |                                                                                                                                                                                                                                                                                                                   |                    | http://www.elnec.com/                               |  |

| HI-LO SYSTEMS             |                                                                                                                                                                                                                                                                                                                   |                    | http://www.hilosystems.com.tw/                      |  |

| ICE TECHNOLOGY            |                                                                                                                                                                                                                                                                                                                   |                    | http://www.icetech.com/                             |  |

| LEAP                      | Single and gang programmers                                                                                                                                                                                                                                                                                       |                    | http://www.leap.com.tw/                             |  |

| LLOYD RESEARCH            |                                                                                                                                                                                                                                                                                                                   |                    | http://www.lloyd-research.com/                      |  |

| LOGICAL DEVICES           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.chipprogram-<br>mers.com/                |  |

| MQP ELECTRONICS           |                                                                                                                                                                                                                                                                                                                   |                    | http://www.mqp.com/                                 |  |

| NEEDHAMS<br>ELECTRONICS   |                                                                                                                                                                                                                                                                                                                   |                    | http://www.needhams.com/                            |  |

| STAG PROGRAMMERS          |                                                                                                                                                                                                                                                                                                                   |                    | http://www.stag.co.uk/                              |  |

|                           |                                                                                                                                                                                                                                                                                                                   | 1                  |                                                     |  |

| SYSTEM GENERAL CORP       |                                                                                                                                                                                                                                                                                                                   |                    | http://www.sg.com.tw                                |  |

| TRIBAL MICROSYSTEMS       |                                                                                                                                                                                                                                                                                                                   |                    | http://www.sg.com.tw<br>http://www.tribalmicro.com/ |  |

Note 1: For latest information on third party tools, please visit our Internet site: → http://www.st.com.