Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| - · ·                      |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j11-i-pt |

### 3.2 Control Registers

The OSCCON register (Register 3-1) controls the main aspects of the device clock's operation. It selects the oscillator type to be used, which of the power-managed modes to invoke and the output frequency of the INTOSC source. It also provides status on the oscillators.

The OSCTUNE register (Register 3-2) controls the tuning and operation of the internal oscillator block. It also implements the PLLEN bits which control the operation of the Phase Locked Loop (PLL) in Internal Oscillator modes (see Section 3.4.3 "PLL Frequency Multiplier").

### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0       | R/W-1                | R/W-0                | R/W-0                | R <sup>(1)</sup> | R-0  | R/W-0               | R/W-0               |

|-------------|----------------------|----------------------|----------------------|------------------|------|---------------------|---------------------|

| IDLEN       | IRCF2 <sup>(2)</sup> | IRCF1 <sup>(2)</sup> | IRCF0 <sup>(2)</sup> | OSTS             | IOFS | SCS1 <sup>(4)</sup> | SCS0 <sup>(4)</sup> |

| bit 7 bit 0 |                      |                      |                      |                  |      |                     |                     |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7 IDLEN: Idle Enable bit

1 = Device enters an Idle mode when a SLEEP instruction is executed

0 = Device enters Sleep mode when a SLEEP instruction is executed

bit 6-4 IRCF<2:0>: INTOSC Source Frequency Select bits<sup>(2)</sup>

111 = 8 MHz (INTOSC drives clock directly)

110 = 4 MHz

101 = 2 MHz

100 = 1 MHz (default)

011 = 500 kHz

010 = 250 kHz

001 = 125 kHz

000 = 31 kHz (from either INTOSC/256 or INTRC)(3)

bit 3 OSTS: Oscillator Start-up Time-out Status bit (1)

1 = Oscillator Start-up Timer (OST) time-out has expired; primary oscillator is running

0 = Oscillator Start-up Timer (OST) time-out is running; primary oscillator is not ready

bit 2 IOFS: INTOSC Frequency Stable bit

1 = Fast RC oscillator frequency is stable

0 = Fast RC oscillator frequency is not stable

bit 1-0 SCS<1:0>: System Clock Select bits<sup>(4)</sup>

11 = Internal oscillator block

10 = Primary oscillator

01 = Timer1 oscillator

When FOSC2 = 1:

00 = Primary oscillator

When FOSC2 = 0:

00 = Internal oscillator

- Note 1: Reset state depends on the state of the IESO Configuration bit.

- 2: Modifying these bits will cause an immediate clock frequency switch if the internal oscillator is providing the device clocks.

- 3: Source selected by the INTSRC bit (OSCTUNE<7>), see text.

- 4: Modifying these bits will cause an immediate clock source switch.

### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|----------------------|-------|-------|-------|-------|-------|-------|

| INTSRC    | PLLEN <sup>(1)</sup> | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 bit |                      |       |       |       |       |       |       |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 7 INTSRC: Internal Oscillator Low-Frequency Source Select bit

1 = 31.25 kHz device clock derived from 8 MHz INTOSC source (divide-by-256 enabled)

0 = 31 kHz device clock derived from INTRC 31 kHz oscillator

bit 6 PLLEN: Frequency Multiplier PLL Enable bit<sup>(1)</sup>

1 = PLL is enabled 0 = PLL is disabled

bit 5-0 **TUN<5:0>:** Fast RC Oscillator (INTOSC) Frequency Tuning bits

011111 = Maximum frequency

•

000001

000000 = Center frequency. Fast RC oscillator is running at the calibrated frequency.

111111

•

100000 = Minimum frequency

Note 1: Available only for ECPLL and HSPLL oscillator configurations; otherwise, this bit is unavailable and reads as '0'.

## 3.3 Clock Sources and Oscillator Switching

Essentially, PIC18F85J11 family devices have three independent clock sources:

- · Primary oscillators

- · Secondary oscillators

- · Internal oscillator

The **primary oscillators** can be thought of as the main device oscillators. These are any external oscillators connected to the OSC1 and OSC2 pins, and include the External Crystal and Resonator modes and the External Clock modes. In some circumstances, the internal oscillator block may be considered a primary oscillator. The particular mode is defined by the FOSC Configuration bits. The details of these modes are covered in **Section 3.4** "External Oscillator Modes".

The **secondary oscillators** are external clock sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F85J11 family devices offer the Timer1 oscillator as a secondary oscillator source. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock. The Timer1 oscillator is discussed in greater detail in **Section 13.3** "Timer1 Oscillator"

In addition to being a primary clock source in some circumstances, the **internal oscillator** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor. The internal oscillator block is discussed in more detail in **Section 3.5** "Internal Oscillator Block".

The PIC18F85J11 family includes features that allow the device clock source to be switched from the main oscillator, chosen by device configuration, to one of the alternate clock sources. When an alternate clock source is enabled, various power-managed operating modes are available.

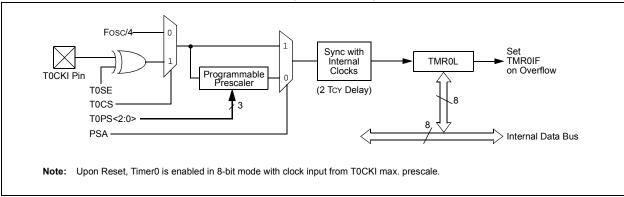

### 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter. The mode is selected with the T0CS bit (T0CON<5>). In Timer mode (T0CS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>). Clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the

internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

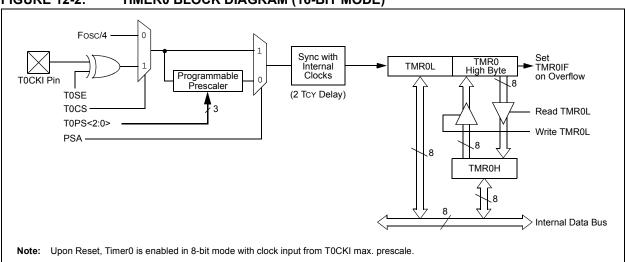

## 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 12-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

### FIGURE 12-2: TIMERO BLOCK DIAGRAM (16-BIT MODE)

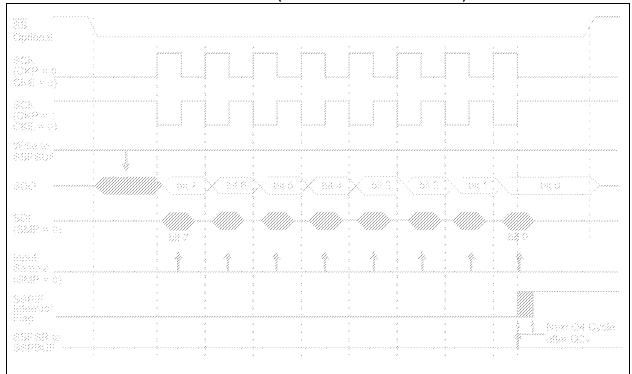

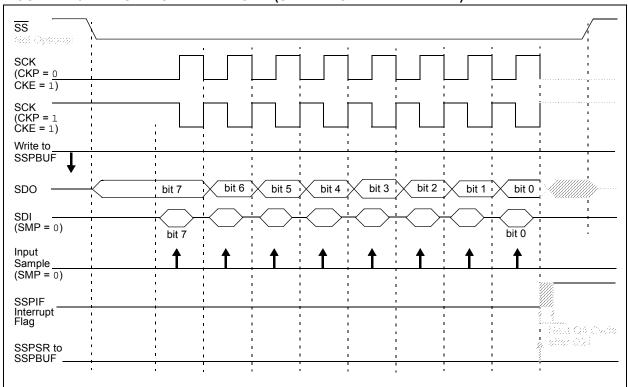

FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

FIGURE 17-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

# 19.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is very similar in function to the Enhanced USART module discussed in the previous chapter. It is provided as an additional channel for serial communication with external devices for those situations that do not require Auto-Baud Detection or LIN/J2602 bus support.

The AUSART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

The pins of the AUSART module are multiplexed with the functions of PORTG (RG1/TX2/CK2 and RG2/RX2/DT2, respectively). In order to configure these pins as an AUSART:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISG<1> bit must be set (= 1) for Synchronous Slave mode

**Note:** The AUSART control will automatically reconfigure the pin from input to output as needed.

The driver for the TX2 output pin can also be optionally configured as an open-drain output. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, and allows the output to communicate with external circuits without the need for additional level shifters.

The open-drain output option is controlled by the U2OD bit (LATG<7>). Setting this bit configures the pin for open-drain operation.

### 19.1 Control Registers

The operation of the Addressable USART module is controlled through two registers, TXSTA2 and RCSTA2. These are detailed in Register 19-1 and Register 19-2, respectively.

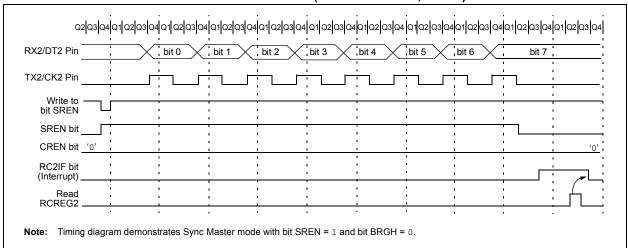

## 19.4.2 AUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA2<5>), or the Continuous Receive Enable bit, CREN (RCSTA2<4>). Data is sampled on the RX2 pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- Initialize the SPBRG2 register for the appropriate baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RC2IE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RC2IF, will be set when reception is complete and an interrupt will be generated if the enable bit, RC2IE, was set.

- Read the RCSTA2 register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG2 register.

- If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set

### FIGURE 19-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### TABLE 19-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name   | Bit 7                   | Bit 6       | Bit 5        | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------|-------------------------|-------------|--------------|--------|-------|--------|--------|-------|----------------------------|

| INTCON | GIE/GIEH                | PEIE/GIEL   | TMR0IE       | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 57                         |

| PIR3   | _                       | _           | RC2IF        | TX2IF  | _     | CCP2IF | CCP1IF | _     | 59                         |

| PIE3   | _                       | _           | RC2IE        | TX2IE  | _     | CCP2IE | CCP1IE | _     | 59                         |

| IPR3   | _                       | _           | RC2IP        | TX2IP  | _     | CCP2IP | CCP1IP | _     | 59                         |

| RCSTA2 | SPEN                    | RX9         | SREN         | CREN   | ADDEN | FERR   | OERR   | RX9D  | 61                         |

| RCREG2 | AUSART Receive Register |             |              |        |       |        |        | 61    |                            |

| TXSTA2 | CSRC                    | TX9         | TXEN         | SYNC   | _     | BRGH   | TRMT   | TX9D  | 61                         |

| SPBRG2 | AUSART B                | aud Rate Ge | enerator Req | gister |       |        |        |       | 61                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

### 20.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 20-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor Chold. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 20-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

CHOLD = 25 pF Rs =  $2.5 \text{ k}\Omega$ Conversion Error  $\leq$  1/2 LSb

VDD =  $3V \rightarrow Rss = 2 \text{ k}\Omega$ Temperature =  $85^{\circ}\text{C}$  (system max.)

### **EQUATION 20-1: A/D ACQUISITION TIME**

```

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

```

### **EQUATION 20-2: A/D MINIMUM CHARGING TIME**

```

VHOLD = (VREF - (VREF/2048)) \cdot (1 - e^{(-TC/CHOLD(RIC + RSS + RS))})

or

TC = -(CHOLD)(RIC + RSS + RS) \ln(1/2048)

```

### **EQUATION 20-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME**

```

\begin{aligned} TACQ &= TAMP + TC + TCOFF \\ TAMP &= 0.2 \ \mu s \\ TCOFF &= (Temp - 25^{\circ}C)(0.02 \ \mu s/^{\circ}C) \\ &(85^{\circ}C - 25^{\circ}C)(0.02 \ \mu s/^{\circ}C) \\ &1.2 \ \mu s \end{aligned}  Temperature coefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 ms.  TC &= -(CHOLD)(RIC + RSS + RS) \ln(1/2048) \ \mu s \\ &-(25 \ pF) \ (1 \ k\Omega + 2 \ k\Omega + 2.5 \ k\Omega) \ln(0.0004883) \ \mu s \\ &1.05 \ \mu s \end{aligned}  TACQ  = 0.2 \ \mu s + 1 \ \mu s + 1.2 \ \mu s \\ &2.4 \ \mu s

```

## 23.0 SPECIAL FEATURES OF THE CPU

PIC18F85J11 family devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- · Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Fail-Safe Clock Monitor

- · Two-Speed Start-up

- · Code Protection

- · In-Circuit Serial Programming

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0** "Oscillator Configurations".

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, the PIC18F85J11 family of devices have a configurable Watchdog Timer which is controlled in software.

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

### 23.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h. A complete list is shown in Table 23-2. A detailed explanation of the various bit functions is provided in Register 23-1 through Register 23-6.

## 23.1.1 CONSIDERATIONS FOR CONFIGURING THE PIC18F85J11 FAMILY DEVICES

Unlike some previous PIC18 microcontrollers, devices of the PIC18F85J11 family do not use persistent memory registers to store configuration information. The Configuration registers, CONFIG1L through CONFIG4H, are implemented as volatile memory.

Immediately after power-up, or after a device Reset, the microcontroller hardware automatically loads the CONFIG1L through CONFIG4L registers with configuration data stored in nonvolatile Flash program memory. The last four words of Flash program memory, known as the Flash Configuration Words (FCW), are used to store the configuration data. Table 23-1 provides the Flash program memory, which will be loaded into the corresponding Configuration register.

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The volatile memory cells used for the Configuration bits always reset to '1' on Power-on Resets. For all other types of Reset events, the previously programmed values are maintained and used without reloading from program memory.

The four Most Significant bits of CONFIG1H, CONFIG2H and CONFIG3H in program memory should also be '1111'. This makes these Configuration Words appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

To prevent inadvertent configuration changes during code execution, all programmable Configuration bits are write-once. After a bit is initially programmed during a power cycle, it cannot be written to again. Changing a device configuration requires that power to the device be cycled.

TABLE 23-1: MAPPING OF THE FLASH

CONFIGURATION WORDS TO

THE CONFIGURATION

REGISTERS

| Configuration<br>Byte | Code Space<br>Address | Configuration<br>Register<br>Address |

|-----------------------|-----------------------|--------------------------------------|

| CONFIG1L              | XXXF8h                | 300000h                              |

| CONFIG1H              | XXXF9h                | 300001h                              |

| CONFIG2L              | XXXFAh                | 300002h                              |

| CONFIG2H              | XXXFBh                | 300003h                              |

| CONFIG3L              | XXXFCh                | 300004h                              |

| CONFIG3H              | XXXFDh                | 300005h                              |

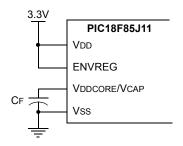

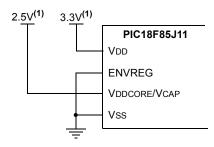

### 23.3 On-Chip Voltage Regulator

All of the PIC18F85J11 family devices power their core digital logic at a nominal 2.5V. For designs that are required to operate at a higher typical voltage, such as 3.3V, all devices in the PIC18F85J11 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is controlled by the ENVREG pin. Tying VDD to the pin enables the regulator, which in turn, provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR filter capacitor must be connected to the VDDCORE/VCAP pin (Figure 23-2). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Section 26.3 "DC Characteristics: PIC18F85J11 Family (Industrial)".

If ENVREG is tied to Vss, the regulator is disabled. In this case, separate power for the core logic at a nominal 2.5V must be supplied to the device on the VDDCORE/VCAP pin to run the I/O pins at higher voltage levels, typically 3.3V. Alternatively, the VDDCORE/VCAP and VDD pins can be tied together to operate at a lower nominal voltage. Refer to Figure 23-2 for possible configurations.

## 23.3.1 VOLTAGE REGULATION AND LOW-VOLTAGE DETECTION

When it is enabled, the on-chip regulator provides a constant voltage of 2.5V nominal to the digital core logic. The regulator can provide this level from a VDD of about 2.5V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 2.5V.

In order to prevent "brown-out" conditions, the regulator enters Tracking mode when the voltage drops too low for the regulator. In Tracking mode, the regulator output follows VDD, with a typical voltage drop of 100 mV.

The on-chip regulator includes a simple Low-Voltage Detect (LVD) circuit. If VDD drops too low to maintain approximately 2.45V on VDDCORE, the circuit sets the Low-Voltage Detect Interrupt Flag, LVDIF (PIR2<2>), and clears the REGSLP (WDTCON<7>) bit if it was set.

This can be used to generate an interrupt and put the application into a low-power operational mode or to trigger an orderly shutdown. Low-Voltage Detection is only available when the regulator is enabled.

## FIGURE 23-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

### Regulator Enabled (ENVREG tied to VDD):

### Regulator Disabled (ENVREG tied to ground):

### Regulator Disabled (VDD tied to VDDCORE):

Note 1: These are typical operating voltages. Refer to Section 26.1 "DC Characteristics: Supply Voltage" for the full operating ranges of VDD and VDDCORE.

### ADDWFC ADD W and Carry bit to f

Syntax: ADDWFC f  $\{,d \{,a\}\}$ Operands:  $0 \le f \le 255$

> $d \in [0, 1]$  $a \in [0, 1]$

Operation: (W) + (f) + (C)  $\rightarrow$  dest

Status Affected: N, OV, C, DC, Z

Encoding: 0010 00da fffff ffff

Description: Add W, the Carry flag and data memory

location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: ADDWFC REG, 0, 1

Before Instruction

Carry bit = 1 REG = 02h W = 4Dh

After Instruction

Carry bit = 0REG = 02hW = 50h ANDLW AND Literal with W

Syntax: ANDLW k Operands:  $0 \le k \le 255$

Operation: (W) .AND.  $k \rightarrow W$

Status Affected: N, Z

Encoding: 0000 1011 kkkk kkkk

Description: The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in W.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4       |

|--------|--------------|---------|----------|

| Decode | Read literal | Process | Write to |

|        | 'k'          | Data    | W        |

Example: ANDLW 05Fh

03h

Before Instruction

W = A3h

After Instruction

W

| GOTO                                                | Unconditional Branch                                                                                                                                                     |                             |                            |                                        |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|----------------------------------------|

| Syntax:                                             | GOTO k                                                                                                                                                                   |                             |                            |                                        |

| Operands:                                           | $0 \le k \le 10$                                                                                                                                                         | 48575                       |                            |                                        |

| Operation:                                          | $k \rightarrow PC < 20:1 >$                                                                                                                                              |                             |                            |                                        |

| Status Affected:                                    | None                                                                                                                                                                     |                             |                            |                                        |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                             | 1111<br>k <sub>19</sub> kkk | k <sub>7</sub> kkk<br>kkkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |

| Description:                                        | GOTO allows an unconditional branch anywhere within entire 2-Mbyte memory range. The 20-bit value, 'k', is loaded into PC<20:1>. GOTO is always a two-cycle instruction. |                             |                            |                                        |

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1           | Q2                     | Q3              | Q4                                        |

|--------------|------------------------|-----------------|-------------------------------------------|

| Decode       | Read literal 'k'<7:0>, | No<br>operation | Read literal<br>'k'<19:8>,<br>Write to PC |

| No operation | No operation           | No operation    | No operation                              |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF              | Increment                                                                                         | f                                                                                                                                                 |                                                    |                                             |  |

|-------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|--|

| Syntax:           | INCF f {,d {                                                                                      | ,a}}                                                                                                                                              |                                                    |                                             |  |

| Operands:         | 0 ≤ f ≤ 255                                                                                       |                                                                                                                                                   |                                                    |                                             |  |

|                   | d ∈ [0, 1]<br>a ∈ [0, 1]                                                                          |                                                                                                                                                   |                                                    |                                             |  |

| Operation:        | $(f) + 1 \rightarrow de$                                                                          | est                                                                                                                                               |                                                    |                                             |  |

| Status Affected:  | C, DC, N,                                                                                         | OV, Z                                                                                                                                             |                                                    |                                             |  |

| Encoding:         | 0010                                                                                              | 10da ff                                                                                                                                           | ff                                                 | ffff                                        |  |

| Description:      | incremente<br>placed in W                                                                         | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f'. |                                                    |                                             |  |

|                   | If 'a' is '0', the Access Bank is selected If 'a' is '1', the BSR is used to select the GPR bank. |                                                                                                                                                   |                                                    |                                             |  |

|                   | set is enab<br>in Indexed<br>mode wher<br>Section 25<br>Bit-Oriente                               | nd the extend<br>led, this instru<br>Literal Offset A<br>never f ≤ 95 (5<br>.2.3 "Byte-Oi<br>ed Instruction<br>set Mode" for                      | ction of<br>Addres<br>Fh). S<br>riented<br>is in I | operates<br>ssing<br>see<br>d and<br>ndexed |  |

| Words:            | 1                                                                                                 |                                                                                                                                                   |                                                    |                                             |  |

| Cycles:           | 1                                                                                                 |                                                                                                                                                   |                                                    |                                             |  |

| Q Cycle Activity: |                                                                                                   |                                                                                                                                                   |                                                    |                                             |  |

| Q1                | Q2                                                                                                | Q3                                                                                                                                                |                                                    | Q4                                          |  |

| Decode            | Read                                                                                              | Process                                                                                                                                           | W                                                  | rite to                                     |  |

| Example:                                                  | INCF    |               | CNT, | 1, | 0 |

|-----------------------------------------------------------|---------|---------------|------|----|---|

| Before Instruc<br>CNT<br>Z<br>C<br>DC<br>After Instructio | = = =   | FFh<br>0<br>? |      |    |   |

| CNT<br>Z<br>C                                             | = = = = | 00h<br>1<br>1 |      |    |   |

register 'f'

Data

destination

| RETURN            | Return from Subroutine                                                                                                                                                                                                                                                                                   |            |   |    |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|----|--|--|--|

| Syntax:           | RETURN -                                                                                                                                                                                                                                                                                                 | RETURN (s) |   |    |  |  |  |

| Operands:         | $s\in [0,1]$                                                                                                                                                                                                                                                                                             |            |   |    |  |  |  |

| Operation:        | $(TOS) \rightarrow PC;$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged                                                                                                                                            |            |   |    |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                     |            |   |    |  |  |  |

| Encoding:         | 0000 0000 0001 001s                                                                                                                                                                                                                                                                                      |            |   |    |  |  |  |

| Description:      | Return from subroutine. The stack is popped and the top of the stack (TOS) is loaded into the program counter. If 's'= 1, the contents of the shadow registers, WS, STATUSS and BSRS, are loaded into their corresponding registers, W, STATUS and BSR. If 's' = 0, no update of these registers occurs. |            |   |    |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                        |            |   |    |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                                                                                                                        |            |   |    |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                          |            |   |    |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                       | Q          | 3 | Q4 |  |  |  |

No

operation

No

operation

Process

Data

No

operation

POP PC

from stack

No

operation

Example: RETURN

After Instruction: PC = TOS

Decode

No

operation

| RLCF                    | Rotate Lef                                                                                                                                                                                                                                                        | t f throug     | gh Carry | y                             |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|-------------------------------|--|--|--|

| Syntax:                 | RLCF f {,d                                                                                                                                                                                                                                                        | {,a}}          |          |                               |  |  |  |

| Operands:               | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                                                                    | $d \in [0, 1]$ |          |                               |  |  |  |

| Operation:              | $(f < n >) \rightarrow de$<br>$(f < 7 >) \rightarrow C$<br>$(C) \rightarrow dest$                                                                                                                                                                                 | ,              | >,       |                               |  |  |  |

| Status Affected:        | C, N, Z                                                                                                                                                                                                                                                           |                |          |                               |  |  |  |

| Encoding:               | 0011                                                                                                                                                                                                                                                              | 01da           | ffff     | ffff                          |  |  |  |

| Description:            | The contents of register 'f' are rotated one bit to the left through the Carry flag. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.                                                                          |                |          |                               |  |  |  |

|                         |                                                                                                                                                                                                                                                                   |                |          | is selected.<br>to select the |  |  |  |

|                         | If 'a' is '0' and the extended instruction set is enabled, this instruction operate in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 25.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                |          |                               |  |  |  |

| Manda.                  | 4                                                                                                                                                                                                                                                                 |                |          |                               |  |  |  |

| Words:                  | 1                                                                                                                                                                                                                                                                 |                |          |                               |  |  |  |

| Cycles:                 | I                                                                                                                                                                                                                                                                 |                |          |                               |  |  |  |

| Q Cycle Activity:<br>Q1 | Q2                                                                                                                                                                                                                                                                | Q              | 3        | Q4                            |  |  |  |

| Decode                  | Read<br>register 'f'                                                                                                                                                                                                                                              | Proce<br>Dat   | ess      | Write to destination          |  |  |  |

REG = 1110 0110 W = 1100 1100 C = 1

#### 26.2 **DC Characteristics: Power-Down and Supply Current** PIC18F85J11 Family (Industrial) (Continued)

| PIC18F8<br>(Indu |                                     |      | <b>erating</b><br>nperatur |       | inless otherwise sta $TA \le +85^{\circ}C$ for indust | •                                             |                                          |  |

|------------------|-------------------------------------|------|----------------------------|-------|-------------------------------------------------------|-----------------------------------------------|------------------------------------------|--|

| Param<br>No.     | Device                              | Тур  | Max                        | Units | Conditions                                            |                                               |                                          |  |

|                  | Supply Current (IDD) <sup>(2)</sup> |      |                            |       |                                                       |                                               |                                          |  |

|                  | All devices                         | 50   | 120                        | μΑ    | -40°C                                                 | \/pp = 2.0\/                                  |                                          |  |

|                  |                                     | 51   | 120                        | μΑ    | +25°C                                                 | $V_{DD} = 2.0V,$<br>$V_{DDCORE} = 2.0V^{(4)}$ |                                          |  |

|                  |                                     | 54   | 130                        | μΑ    | +85°C                                                 | VBBOOKE 2.0V                                  |                                          |  |

|                  | All devices                         | 223  | 480                        | μΑ    | -40°C                                                 | \/pp = 0.5\/                                  | Fosc = 1 MHz                             |  |

|                  |                                     | 134  | 300                        | μΑ    | +25°C                                                 | $V_{DD} = 2.5V,$<br>$V_{DDCORE} = 2.5V^{(4)}$ | (PRI_IDLE mode,                          |  |

|                  |                                     | 110  | 270                        | μΑ    | +85°C                                                 | VBBOOKE 2.0V                                  | EC oscillator)                           |  |

|                  | All devices                         | 307  | 550                        | μΑ    | -40°C                                                 |                                               |                                          |  |

|                  |                                     | 254  | 500                        | μΑ    | +25°C                                                 | $V_{DD} = 3.3V^{(5)}$                         |                                          |  |

|                  |                                     | 194  | 460                        | μΑ    | +85°C                                                 |                                               |                                          |  |

|                  | All devices                         | 307  | 850                        | μΑ    | -40°C                                                 | \/ 0.0\/                                      |                                          |  |

|                  |                                     | 200  | 850                        | μΑ    | +25°C                                                 | $V_{DD} = 2.0V,$<br>$V_{DDCORE} = 2.0V^{(4)}$ |                                          |  |

|                  |                                     | 202  | 800                        | μΑ    | +85°C                                                 | VBBOOKE 2.01                                  |                                          |  |

|                  | All devices                         | 483  | 950                        | μΑ    | -40°C                                                 | \/pp = 0.5\/                                  | Fosc = 4 MHz                             |  |

|                  |                                     | 318  | 950                        | μΑ    | +25°C                                                 |                                               | (PRI_IDLE mode,                          |  |

|                  |                                     | 343  | 900                        | μΑ    | +85°C                                                 | VBBOOKE 2.0V                                  | EC oscillator)                           |  |

|                  | All devices                         | 0.52 | 1.3                        | mA    | -40°C                                                 |                                               |                                          |  |

|                  |                                     | 0.47 | 1.2                        | mA    | +25°C                                                 | $V_{DD} = 3.3V^{(5)}$                         |                                          |  |

|                  |                                     | 0.47 | 1.2                        | mA    | +85°C                                                 |                                               |                                          |  |

|                  | All devices                         | 2.38 | 8                          | mA    | -40°C                                                 | \/DD = 2 E\/                                  |                                          |  |

|                  |                                     | 2.04 | 8                          | mA    | +25°C                                                 | $VDD = 2.5V,$ $VDDCORE = 2.5V^{(4)}$          | E                                        |  |

|                  |                                     | 2.52 | 9                          | mA    | +85°C                                                 |                                               | Fosc = 40 MHz<br>( <b>PRI IDLE</b> mode, |  |

|                  | All devices                         | 3.02 | 10                         | mA    | -40°C                                                 | _                                             | EC oscillator)                           |  |

|                  |                                     | 2.99 | 10                         | mA    | +25°C                                                 | $V_{DD} = 3.3V^{(5)}$                         | ,                                        |  |

|                  |                                     | 4.23 | 11                         | mA    | +85°C                                                 |                                               |                                          |  |

- The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is Note 1: measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: Voltage regulator disabled (ENVREG tied to Vss).

- 5: Voltage regulator enabled (ENVREG tied to VDD).

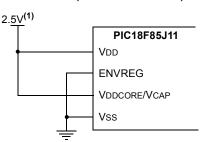

FIGURE 26-15: **EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)**

TABLE 26-17: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                                                           |                   | Min           | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------------------------------------|-------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | , $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |                   | 3 Tcy         | _   | ns    |            |

| 70A          | TssL2WB               | SS to Write to SSPBUF                                                    |                   | 3 Tcy         | _   | ns    |            |

| 71           | TscH                  | SCK Input High Time                                                      | Continuous        | 1.25 Tcy + 30 | _   | ns    |            |

| 71A          |                       | (Slave mode)                                                             | Single byte       | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                                                       | Continuous        | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                                                             | Single byte       | 40            | _   | ns    | (Note 1)   |

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDI Data Input to SCK Edge                                 |                   | 20            | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First Clo                               | ck Edge of Byte 2 | 1.5 Tcy + 40  | -   | ns    | (Note 2)   |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDI Data Input to SCK Edge                                  |                   | 40            |     | ns    |            |

| 75           | TDOR                  | SDO Data Output Rise Time                                                |                   | _             | 25  | ns    |            |

| 76           | TDOF                  | SDO Data Output Fall Time                                                |                   | _             | 25  | ns    |            |

| 77           | TssH2DoZ              | SS ↑ to SDO Output High-Impedance                                        |                   | 10            | 50  | ns    |            |

| 78           | TscR                  | SCK Output Rise Time (Master mode)                                       |                   | _             | 25  | ns    |            |

| 79           | TscF                  | SCK Output Fall Time (Master mode)                                       |                   | _             | 25  | ns    |            |

| 80           | TscH2DoV,<br>TscL2DoV | SDO Data Output Valid After SCK Edge                                     |                   | _             | 50  | ns    |            |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ After SCK Edge                                                      |                   | 1.5 Tcy + 40  | _   | ns    |            |

Note 1: Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

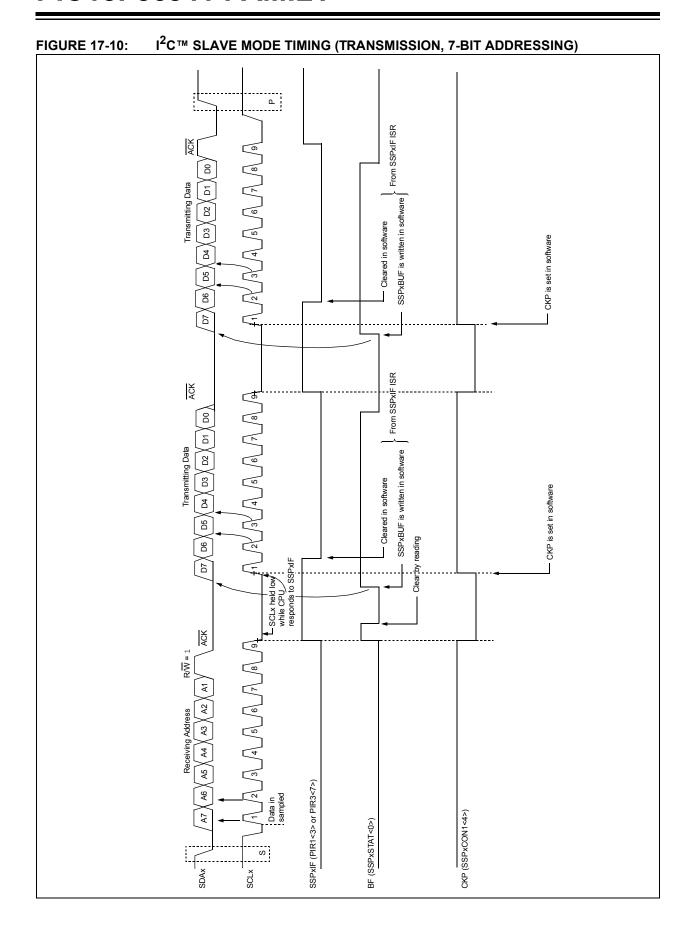

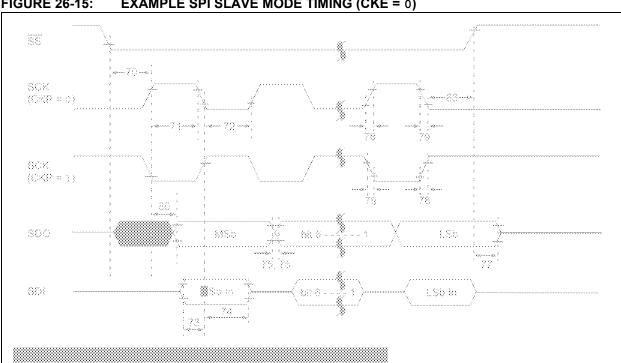

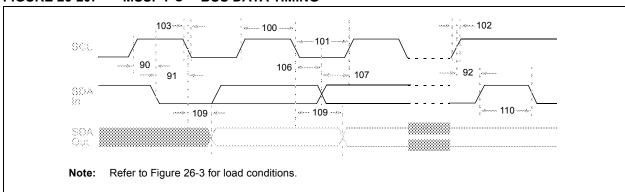

FIGURE 26-19: MSSP I<sup>2</sup>C™ BUS START/STOP BITS TIMING WAVEFORMS

TABLE 26-21: MSSP I<sup>2</sup>C™ BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Characteristic  |                             | Min              | Max | Units | Conditions             |   |                      |

|---------------|---------|-----------------|-----------------------------|------------------|-----|-------|------------------------|---|----------------------|

| 90            | Tsu:sta | Start Condition | 100 kHz mode                | 2(Tosc)(BRG + 1) |     | ns    | Only relevant for      |   |                      |

|               |         | Setup Time      | 400 kHz mode                | 2(Tosc)(BRG + 1) | _   |       | Repeated Start         |   |                      |

|               |         |                 | 1 MHz mode <sup>(1,2)</sup> | 2(Tosc)(BRG + 1) | _   |       | condition              |   |                      |

| 91            | THD:STA | Start Condition | 100 kHz mode                | 2(Tosc)(BRG + 1) | _   | ns    | After this period, the |   |                      |

|               |         | Hold Time       | 400 kHz mode                | 2(Tosc)(BRG + 1) | _   |       |                        | • | first clock pulse is |

|               |         |                 | 1 MHz mode <sup>(1,2)</sup> | 2(Tosc)(BRG + 1) | _   |       | generated              |   |                      |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode                | 2(Tosc)(BRG + 1) | _   | ns    |                        |   |                      |

|               |         | Setup Time      | 400 kHz mode                | 2(Tosc)(BRG + 1) | _   |       |                        |   |                      |

|               |         |                 | 1 MHz mode <sup>(1,2)</sup> | 2(Tosc)(BRG + 1) | _   |       |                        |   |                      |

| 93            | THD:STO | Stop Condition  | 100 kHz mode                | 2(Tosc)(BRG + 1) | _   | ns    |                        |   |                      |

|               |         | Hold Time       | 400 kHz mode                | 2(Tosc)(BRG + 1) | _   |       |                        |   |                      |

|               |         |                 | 1 MHz mode <sup>(1,2)</sup> | 2(Tosc)(BRG + 1) | _   |       |                        |   |                      |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

2: A minimum 16 MHz Fosc is required for 1 MHz I<sup>2</sup>C.

FIGURE 26-20: MSSP I<sup>2</sup>C™ BUS DATA TIMING

### **INDEX**

| A                                              |        | Baud Rate Generator (BRG)                 |     |

|------------------------------------------------|--------|-------------------------------------------|-----|

| A/D                                            | 250    | Associated Registers                      | 248 |

| A/D Converter Interrupt, Configuring           |        | Baud Rate Error, Calculating              | 248 |

| Acquisition Requirements                       |        | Baud Rates, Asynchronous Modes            | 249 |

| ADCAL Bit                                      |        | High Baud Rate Select (BRGH Bit)          | 248 |

| ADCON0 Register                                |        | Operation in Power-Managed Modes          | 248 |

| ADCON0 Register                                |        | Sampling                                  | 248 |

|                                                |        | Control Registers                         | 245 |

| ADDESIL Posister                               |        | Synchronous Master Mode                   |     |

| ADREST Register                                |        | Associated Registers, Receive             |     |

| Apples Port Pipe Configuring                   |        | Associated Registers, Transmit            |     |

| Analog Port Pins, Configuring                  |        | Reception                                 | 256 |

| Associated Registers                           |        | Reception Setup                           |     |

| Automatic Acquisition Time                     |        | Transmission                              |     |

| Configuring the Module                         |        | Transmission Setup                        |     |

| Conversion Clock (TAD)                         |        | Synchronous Slave Mode                    |     |

| Conversion Requirements                        |        | Associated Registers, Receive             |     |

| Conversion Status (GO/DONE Bit)                |        | Associated Registers, Transmit            |     |

| Conversions                                    |        | Reception                                 |     |

| Converter Calibration                          |        | Reception Setup                           |     |

| Converter Characteristics                      |        | Transmission                              |     |

| Operation in Power-Managed Modes               |        | Transmission Setup                        |     |

| Special Event Trigger (CCP2)                   |        | Auto-Wake-up on Sync Break Character      |     |

| Use of the CCP2 Trigger                        |        | _                                         |     |

| Absolute Maximum Ratings                       |        | В                                         |     |

| AC (Timing) Characteristics                    | 364    | Baud Rate Generator                       | 209 |

| Load Conditions for Device Timing              |        | BC                                        | 307 |

| Specifications                                 |        | BCF                                       | 308 |

| Parameter Symbology                            |        | BF                                        | 213 |

| Temperature and Voltage Specifications         |        | BF Status Flag                            | 213 |

| Timing Conditions                              |        | Block Diagrams                            |     |

| ACKSTAT                                        |        | 16-Bit Byte Select Mode                   | 105 |

| ACKSTAT Status Flag                            |        | 16-Bit Byte Write Mode                    |     |

| ADCAL Bit                                      |        | 16-Bit Word Write Mode                    |     |

| ADCON0 Register                                |        | 8-Bit Multiplexed Mode                    | 107 |

| GO/DONE Bit                                    |        | A/D                                       |     |

| ADCON1 Register                                |        | Analog Input Model                        |     |

| ADCON2 Register                                |        | AUSART Receive                            | 252 |

| ADDFSR                                         |        | AUSART Transmit                           | 250 |

| ADDLW                                          | 305    | Baud Rate Generator                       | 209 |

| Addressable Universal Synchronous Asynchronous |        | Capture Mode Operation                    | 172 |

| Receiver Transmitter (AUSART). See AUSART.     | 0.40   | Comparator Analog Input Model             |     |

| ADDULNK                                        |        | Comparator I/O Operating Modes            | 270 |

| ADDWF                                          |        | Comparator Output                         | 272 |

| ADDWFC                                         |        | Comparator Voltage Reference              |     |

| ADRESH Register                                |        | Comparator Voltage Reference Output       |     |

| ADRESL Register                                | 9, 262 | Buffer Example                            | 277 |

| Analog-to-Digital Converter. See A/D.          | 000    | Compare Mode Operation                    |     |

| ANDLW                                          |        | Connections for On-Chip Voltage Regulator |     |

| ANDWF                                          | 307    | Device Clock                              |     |

| Assembler                                      | 000    | EUSART Receive                            | 235 |

| MPASM Assembler                                | 296    | EUSART Transmit                           | 233 |

| AUSART                                         | 050    | External Power-on Reset Circuit           |     |

| Asynchronous Mode                              |        | (Slow VDD Power-up)                       | 53  |

| Associated Registers, Receive                  |        | Fail-Safe Clock Monitor                   |     |

| Associated Registers, Transmit                 |        | Generic I/O Port Operation                |     |

| Receiver                                       |        | Interrupt Logic                           |     |

| Reception Setup                                |        | MSSP (I <sup>2</sup> C Master Mode)       |     |

| Setting up 9-Bit Mode with Address Detect      | 252    | MSSP (I <sup>2</sup> C Mode)              |     |

| Reception with Address Detect                  | 050    | MSSP (SPI Mode)                           |     |

| Enable Setup                                   |        | On-Chip Reset Circuit                     |     |

| Transmission Setup                             |        | PIC18F6XJ11                               |     |

| Transmitter                                    | 250    | PIC18F8XJ11                               |     |

|                                                |        |                                           |     |

| PLL                                   | 40  | Code Examples                            |     |

|---------------------------------------|-----|------------------------------------------|-----|

| PORTD and PORTE (Parallel Slave Port) | 150 | 16 x 16 Signed Multiply Routine          | 112 |

| PWM Operation (Simplified)            | 175 | 16 x 16 Unsigned Multiply Routine        | 112 |

| Reads From Flash Program Memory       | 93  | 8 x 8 Signed Multiply Routine            | 111 |

| Single Comparator                     | 271 | 8 x 8 Unsigned Multiply Routine          | 111 |

| Table Read Operation                  |     | Changing Between Capture Prescalers      |     |

| Table Write Operation                 | 90  | Computed GOTO Using an Offset Value      | 69  |

| Table Writes to Flash Program Memory  |     | Erasing a Flash Program Memory Block     |     |

| Timer0 in 16-Bit Mode                 |     | Fast Register Stack                      |     |

| Timer0 in 8-Bit Mode                  |     | How to Clear RAM (Bank 1) Using Indirect |     |

| Timer1 (16-Bit Read/Write Mode)       |     | Addressing                               | 82  |

| Timer1 (8-Bit Mode)                   |     | Implementing a Real-Time Clock Using a   |     |

| Timer2                                |     | Timer1 Interrupt Service                 | 161 |

| Timer3 (16-Bit Read/Write Mode)       |     | Initializing PORTA                       |     |

| Timer3 (8-Bit Mode)                   |     | Initializing PORTB                       |     |

| Watchdog Timer                        |     | Initializing PORTC                       |     |

| BN                                    |     | Initializing PORTD                       |     |

|                                       |     | <u> </u>                                 |     |

| BNC                                   |     | Initializing PORTE                       |     |

| BNN                                   |     | Initializing PORTF                       |     |

| BNOV                                  |     | Initializing PORTG                       |     |

| BNZ                                   | 310 | Initializing PORTH                       |     |

| BOR. See Brown-out Reset.             |     | Initializing PORTJ                       |     |

| BOV                                   |     | Loading the SSPBUF (SSPSR) Register      |     |

| BRA                                   | 311 | Reading a Flash Program Memory Word      | 93  |

| BRG. See Baud Rate Generator.         |     | Saving STATUS, WREG and BSR              |     |

| BRGH Bit                              |     | Registers in RAM                         | 128 |

| TXSTA1 Register                       |     | Writing to Flash Program Memory          | 96  |

| TXSTA2 Register                       | 248 | Code Protection                          | 279 |

| Brown-out Reset (BOR)                 | 53  | COMF                                     | 316 |

| and On-Chip Voltage Regulator         | 289 | Comparator                               | 269 |

| Detecting                             | 53  | Analog Input Connection Considerations   | 273 |

| BSF                                   | 311 | Associated Registers                     | 273 |

| BTFSC                                 | 312 | Configuration                            |     |

| BTFSS                                 | 312 | Effects of a Reset                       |     |

| BTG                                   |     | Interrupts                               | 272 |

| BZ                                    |     | Operation                                |     |

|                                       |     | Operation During Sleep                   |     |

| C                                     |     | Outputs                                  |     |

| C Compilers                           |     | Reference                                |     |

| MPLAB C18                             | 296 | External Signal                          |     |

| CALL                                  |     | Internal Signal                          |     |

| CALLW                                 |     | Response Time                            |     |

| Capture (CCP Module)                  |     | Comparator Specifications                |     |

| Associated Registers                  |     | Comparator Voltage Reference             |     |

| CCPR2H:CCPR2L Registers               |     |                                          |     |

| CCPx Pin Configuration                |     | Accuracy and Error Associated Registers  |     |

| Software Interrupt                    |     |                                          |     |

| Timer1/Timer3 Mode Selection          |     | Configuring                              |     |

|                                       |     | Connection Considerations                |     |

| Capture/Compare/PWM (CCP)             | 109 | Effects of a Reset                       |     |

| Capture Mode. See Capture.            | 470 | Operation During Sleep                   |     |

| CCPRxH Register                       |     | Compare (CCP Module)                     |     |

| CCPRxL Register                       |     | Associated Registers                     |     |

| CCPx Mode and Timer Resources         | 170 | CCPR2 Register                           |     |

| Compare Mode. See Compare.            |     | CCPx Pin Configuration                   |     |

| Configuration                         | 170 | Software Interrupt                       |     |

| Interaction of CCP1 and CCP2 for      |     | Special Event Trigger                    |     |

| Timer Resources                       |     | Timer1/Timer3 Mode Selection             | 173 |

| Interconnect Configurations           | 170 | Compare (CCP2 Module)                    |     |

| Clock Sources                         |     | Special Event Trigger                    | 266 |

| Default System Clock on Reset         | 38  | Computed GOTO                            | 69  |

| Selection Using OSCCON Register       | 38  | Configuration Bits                       |     |

| CLRF                                  |     | Configuration Bits, Device IDs           |     |

| CLRWDT                                | 315 | Associated Registers                     | 280 |

|                                       |     | Configuration Register Protection        |     |

|                                       |     | - <del>-</del>                           |     |

| Core Features                                         |

|-------------------------------------------------------|

| Easy Migration10                                      |

| Extended Instruction Set9                             |

| External Memory Bus9                                  |

| Memory Options9                                       |

| nanoWatt Technology9                                  |

| Oscillator Options and Features9                      |

| CPFSEQ                                                |

| CPFSGT                                                |

| CPFSLT                                                |

| Crystal Oscillator/Ceramic Resonator39                |

| Customer Change Notification Service405               |

| Customer Notification Service405                      |

| Customer Support405                                   |

| _                                                     |

| D                                                     |

| Data Addressing Modes82                               |

| Comparing Addressing Modes with the                   |

| Extended Instruction Set Enabled                      |

| Direct                                                |

| Indexed Literal Offset                                |

| BSR87                                                 |

| Instructions Affected                                 |

| Mapping Access Bank87                                 |

| Indirect                                              |

| Inherent and Literal82                                |

| Data Memory                                           |

| •                                                     |

| Access Bank                                           |

| Bank Select Register (BSR)                            |

| Extended Instruction Set                              |

| General Purpose Registers75                           |

| Memory Maps                                           |