Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | •                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Di                    | n Name | Pin Number | Pin        | Buffer    | Description                                                                                                          |  |  |

|-----------------------|--------|------------|------------|-----------|----------------------------------------------------------------------------------------------------------------------|--|--|

| <b>F</b> 11           |        | TQFP       | Туре       | Туре      | Description                                                                                                          |  |  |

|                       |        |            |            |           | PORTH is a bidirectional I/O port.                                                                                   |  |  |

| RH0/A16<br>RH0<br>A16 |        | 79         | I/O<br>I/O | ST<br>TTL | Digital I/O.<br>External memory address/data 16.                                                                     |  |  |

| RH1/A17<br>RH1<br>A17 |        | 80         | I/O<br>I/O | ST<br>TTL | Digital I/O.<br>External memory address/data 17.                                                                     |  |  |

| RH2/A18<br>RH2<br>A18 |        | 1          | I/O<br>I/O | ST<br>TTL | Digital I/O.<br>External memory address/data 18.                                                                     |  |  |

| RH3/A19<br>RH3<br>A19 |        | 2          | I/O<br>I/O | ST<br>TTL | Digital I/O.<br>External memory address/data 19.                                                                     |  |  |

| RH4                   |        | 22         | I/O        | ST        | Digital I/O.                                                                                                         |  |  |

| RH5                   |        | 21         | I/O        | ST        | Digital I/O.                                                                                                         |  |  |

| RH6                   |        | 20         | I/O        | ST        | Digital I/O.                                                                                                         |  |  |

| RH7                   |        | 19         | I/O        | ST        | Digital I/O.                                                                                                         |  |  |

| Legend:               |        |            | with C     | MOS leve  | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |

# TABLE 1-4: PIC18F8XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared (80-pin devices, Extended Microcontroller mode only).

**2:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

**3:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

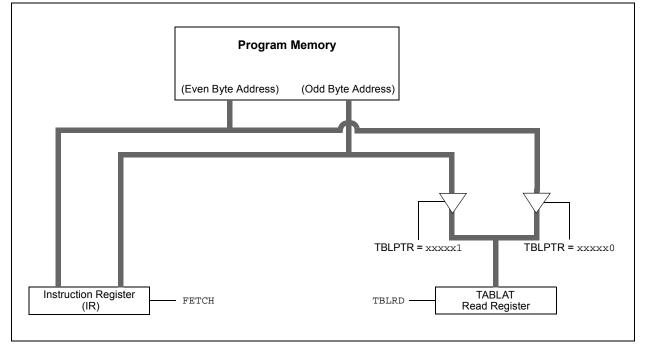

## 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

#### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU | ; Load TBLPTR with the base<br>; address of the word |

|-----------|----------------|----------------------------|------------------------------------------------------|

|           | MOVLW          | CODE ADDR HIGH             | , dddrobb or one word                                |

|           | MOVWF          | TBLPTRH                    |                                                      |

|           |                |                            |                                                      |

|           | MOVLW          | CODE_ADDR_LOW              |                                                      |

|           | MOVWF          | TBLPTRL                    |                                                      |

| READ_WORD |                |                            |                                                      |

|           | TBLRD*+        |                            | ; read into TABLAT and increment                     |

|           | MOVF           | TABLAT, W                  | ; get data                                           |

|           | MOVWF          | WORD_EVEN                  |                                                      |

|           | TBLRD*+        |                            | ; read into TABLAT and increment                     |

|           | MOVF           | TABLAT, W                  | ; get data                                           |

|           | MOVF           | WORD_ODD                   |                                                      |

|           |                |                            |                                                      |

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

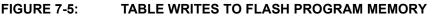

## 7.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

- Note 1: Unlike previous PIC<sup>®</sup> MCUs, members of the PIC18F85J11 family do not reset the holding registers after a write occurs. The holding registers must be cleared or overwritten before a programming sequence.

- 2: To maintain the endurance of the program memory cells, each Flash byte should not be programmed more than one time between erase operations. Before attempting to modify the contents of the target cell a second time, a block erase of the target block, or a bulk erase of the entire memory, must be performed.

#### 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 1024 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load the Table Pointer register with the address of the first byte being written, minus 1.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the WREN bit (EECON1<2>) to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit; this will begin the write cycle.

- 12. The CPU will stall for the duration of the write for Tiw (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 through 13 until all 1024 bytes are written to program memory.

- 15. Verify the memory (table read).

An example of the required code is shown in Example 7-3.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

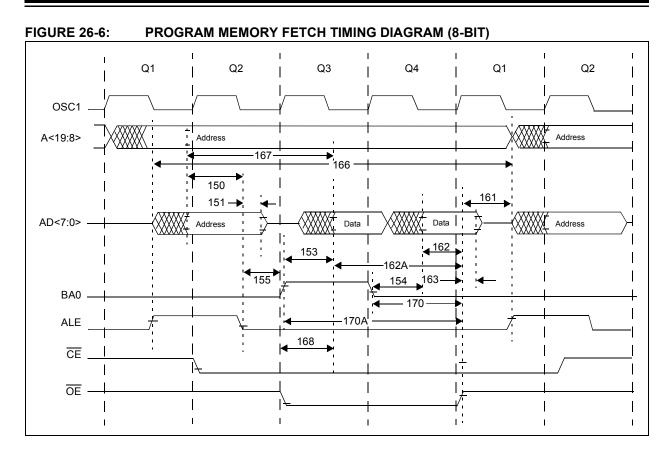

## 8.2 Address and Data Width

The PIC18F85J11 family of devices can be independently configured for different address and data widths on the same memory bus. Both address and data width are set by Configuration bits in the CONFIG3L register. As Configuration bits, this means that these options can only be configured by programming the device and are not controllable in software.

The BW bit selects an 8-bit or 16-bit data bus width. Setting this bit (default) selects a data width of 16 bits.

The EMB<1:0> bits determine both the Program Memory mode and the address bus width. The available options are 20-bit, 16-bit and 12-bit, as well as the default Microcontroller mode (external bus disabled). Selecting a 16-bit or 12-bit width makes a corresponding number of high-order lines available for I/O functions; these pins are no longer affected by the setting of the EBDIS bit. For example, selecting a 16-Bit Address mode (EMB<1:0> = 01) disables A<19:16> and allows PORTH<3:0> to function without interruptions from the bus. Using the smaller address widths allows users to tailor the memory bus to the size of the external memory space for a particular design while freeing up pins for dedicated I/O operation.

Because the EMB bits have the effect of disabling pins for memory bus operations, it is important to always select an address width at least equal to the data width. If a 12-bit address width is used with a 16-bit data width, the upper four bits of data will not be available on the bus.

All combinations of address and data widths require multiplexing of address and data information on the same lines. The address and data multiplexing, as well as I/O ports made available by the use of smaller address widths, are summarized in Table 8-2.

# 8.2.1 ADDRESS SHIFTING ON THE EXTERNAL BUS

By default, the address presented on the external bus is the value of the PC. In practical terms, this means that addresses in the external memory device below the top of on-chip memory are unavailable to the microcontroller. To access these physical locations, the glue logic between the microcontroller and the external memory must somehow translate addresses.

To simplify the interface, the external bus offers an extension of Extended Microcontroller mode that automatically performs address shifting. This feature is controlled by the EASHFT Configuration bit. Setting this bit offsets addresses on the bus by the size of the microcontroller's on-chip program memory and sets the bottom address at 0000h. This allows the device to use the entire range of physical addresses of the external memory.

#### 8.2.2 21-BIT ADDRESSING

As an extension of 20-bit address width operation, the external memory bus can also fully address a 2-Mbyte memory space. This is done by using the Bus Address bit 0 (BA0) control line as the Least Significant bit of the address. The UB and LB control signals may also be used with certain memory devices to select the upper and lower bytes within a 16-bit wide data word.

This addressing mode is available in both 8-bit and certain 16-Bit Data Width modes. Additional details are provided in Section 8.6.3 "16-Bit Byte Select Mode" and Section 8.7 "8-Bit Data Width Mode".

| SLE 6-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS |               |                                                                    |                                                    |                             |  |  |  |  |  |

|-----------------------------------------------------------------------|---------------|--------------------------------------------------------------------|----------------------------------------------------|-----------------------------|--|--|--|--|--|

| Data Width                                                            | Address Width | Multiplexed Data and<br>Address Lines (and<br>Corresponding Ports) | Address-Only<br>Lines (and<br>Corresponding Ports) | Ports Available<br>for I/O  |  |  |  |  |  |

| 8-bit                                                                 | 12-bit        |                                                                    | AD<11:8><br>(PORTE<3:0>)                           | PORTE<7:4>,<br>All of PORTH |  |  |  |  |  |

|                                                                       | 16-bit        | AD<7:0><br>(PORTD<7:0>)                                            | AD<15:8><br>(PORTE<7:0>)                           | All of PORTH                |  |  |  |  |  |

|                                                                       | 20-bit        |                                                                    | A<19:16>, AD<15:8><br>(PORTH<3:0>,<br>PORTE<7:0>)  | _                           |  |  |  |  |  |

| 16-bit                                                                | 16-bit        | AD<15:0>                                                           | _                                                  | All of PORTH                |  |  |  |  |  |

|                                                                       | 20-bit        | (PORTD<7:0>,<br>PORTE<7:0>)                                        | A<19:16><br>(PORTH<3:0>)                           | _                           |  |  |  |  |  |

#### TABLE 8-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Reset on CCPx Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:    |                      |                                                                                     |                                           |                   |  |  |  |  |  |

|------------|----------------------|-------------------------------------------------------------------------------------|-------------------------------------------|-------------------|--|--|--|--|--|

| R = Reada  | able bit             | W = Writable bit                                                                    | U = Unimplemented bit,                    | read as '0'       |  |  |  |  |  |

| -n = Value | at POR               | '1' = Bit is set                                                                    | '0' = Bit is cleared                      | x = Bit is unknow |  |  |  |  |  |

| bit 7      |                      | 6-Bit Read/Write Mode Enab                                                          |                                           |                   |  |  |  |  |  |

|            |                      | bles register read/write of Tlr<br>bles register read/write of Tir                  | •                                         |                   |  |  |  |  |  |

| bit 6      | T1RUN:               | Timer1 System Clock Status                                                          | bit                                       |                   |  |  |  |  |  |

|            |                      | ce clock is derived from Tim<br>ce clock is derived from ano                        |                                           |                   |  |  |  |  |  |

| bit 5-4    | T1CKPS               | <1:0>: Timer1 Input Clock P                                                         | rescale Select bits                       |                   |  |  |  |  |  |

|            | 10 = 1:4<br>01 = 1:2 | Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                |                                           |                   |  |  |  |  |  |

| bit 3      | T1OSCE               | T1OSCEN: Timer1 Oscillator Enable bit                                               |                                           |                   |  |  |  |  |  |

|            |                      | r1 oscillator is enabled<br>r1 oscillator is shut off                               |                                           |                   |  |  |  |  |  |

|            | The osci             | lator inverter and feedback r                                                       | esistor are turned off to elimina         | ate power drain.  |  |  |  |  |  |

| bit 2      | T1SYNC               | : Timer1 External Clock Inpu                                                        | t Synchronization Select bit              |                   |  |  |  |  |  |

|            | 1 <b>= Do n</b>      | <u>/IR1CS = 1:</u><br>ot synchronize external clocł<br>hronize external clock input | < input                                   |                   |  |  |  |  |  |

|            |                      | <u>/IR1CS = 0:</u><br>s ignored. Timer1 uses the in                                 | iternal clock when TMR1CS =               | 0.                |  |  |  |  |  |

| bit 1      | 1 = Exte             | Timer1 Clock Source Sele<br>rnal clock from the RC0/T1C<br>nal clock (Fosc/4)       | ct bit<br>0SO/T13CKI pin (on the rising e | edge)             |  |  |  |  |  |

| bit 0      | TMR10                | I: Timer1 On bit<br>bles Timer1                                                     |                                           |                   |  |  |  |  |  |

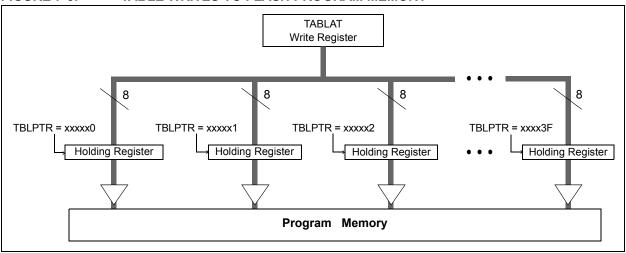

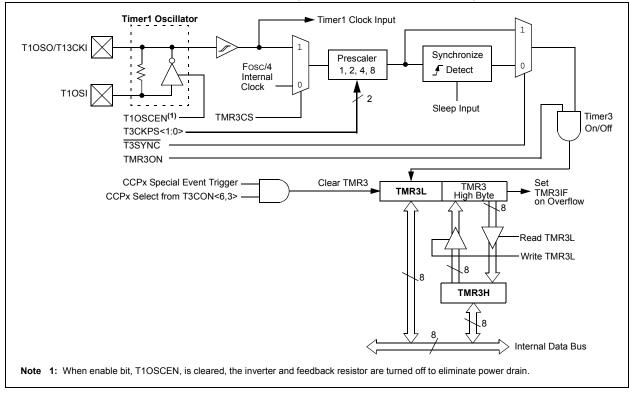

## 15.1 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

As with Timer1, the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs when the Timer1 oscillator is enabled. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

## FIGURE 15-1: TIMER3 BLOCK DIAGRAM (8-BIT MODE)

## FIGURE 15-2: TIMER3 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

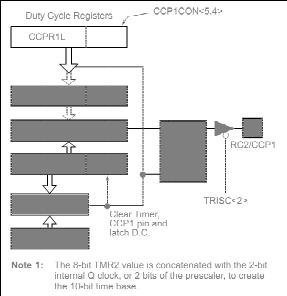

### 16.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP2 pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTB, PORTC or PORTE data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force   |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the RB3, RC1 or RE7 output latch           |  |  |  |  |  |  |  |  |  |

|       | (depending on device configuration) to the |  |  |  |  |  |  |  |  |  |

|       | default low level. This is not the PORTB,  |  |  |  |  |  |  |  |  |  |

|       | PORTC or PORTE I/O data latch.             |  |  |  |  |  |  |  |  |  |

Figure 16-4 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 16.4.3** "Setup for PWM Operation".

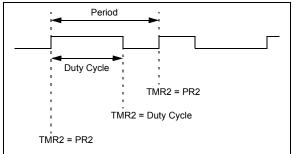

A PWM output (Figure 16-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 16-5: PWM OUTPUT

#### 16.4.1 PWM PERIOD

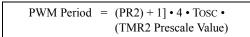

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 16-1:

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP2 pin is set (exception: if PWM duty cycle = 0%, the CCP2 pin will not be set)

- The PWM duty cycle is latched from CCPR2L into CCPR2H

#### 17.3.6 MASTER MODE

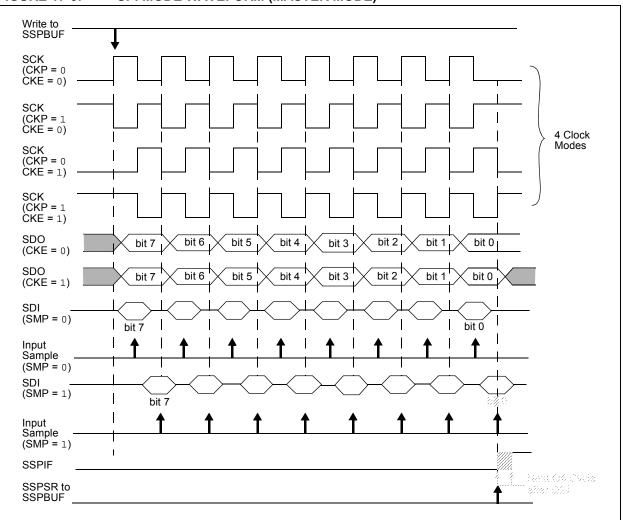

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 17-2) will broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode. The clock polarity is selected by appropriately programming the CKP bit (SSPCON1<4>). This, then, would give waveforms for SPI communication as shown in Figure 17-3, Figure 17-5 and Figure 17-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user-programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum data rate (at 40 MHz) of 10.00 Mbps.

Figure 17-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 17-3: SPI MODE WAVEFORM (MASTER MODE)

| R/W-0        | R/W-0                                                 | R/W-0                                                                                                                                                        | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |  |  |  |  |  |

|--------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|--|--|--|--|--|

| GCEN         | ACKSTAT                                               | ACKDT <sup>(1)</sup>                                                                                                                                         | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |  |  |  |  |  |

| bit 7        |                                                       |                                                                                                                                                              |                      |                             |                    |                     | bit                |  |  |  |  |  |

|              |                                                       |                                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

| Legend:      |                                                       |                                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

| R = Readab   |                                                       | W = Writable                                                                                                                                                 |                      | U = Unimplem                |                    | d as '0'            |                    |  |  |  |  |  |

| -n = Value a | at POR                                                | '1' = Bit is set                                                                                                                                             |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                |  |  |  |  |  |

| bit 7        | GCEN: Conc                                            | eral Call Enable                                                                                                                                             | bit                  |                             |                    |                     |                    |  |  |  |  |  |

|              | Unused in Ma                                          |                                                                                                                                                              | bit                  |                             |                    |                     |                    |  |  |  |  |  |

| bit 6        |                                                       |                                                                                                                                                              | atus hit (Maste      | r Transmit mode             | only)              |                     |                    |  |  |  |  |  |

| Sit 0        |                                                       | edge was not re                                                                                                                                              |                      |                             | c only)            |                     |                    |  |  |  |  |  |

|              |                                                       | edge was receiv                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

| bit 5        | ACKDT: Ack                                            | <b>ACKDT:</b> Acknowledge Data bit (Master Receive mode only) <sup>(1)</sup>                                                                                 |                      |                             |                    |                     |                    |  |  |  |  |  |

|              | 1 = Not Ackn                                          |                                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

|              | 0 = Acknowle                                          | •                                                                                                                                                            |                      |                             |                    |                     |                    |  |  |  |  |  |

| bit 4        | ACKEN: Acknowledge Sequence Enable bit <sup>(2)</sup> |                                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

|              |                                                       | •                                                                                                                                                            | quence on SD         | A and SCL pins              | and transmit       | ACKDT data bit;     | automatical        |  |  |  |  |  |

|              |                                                       | by hardware.<br>edge sequence                                                                                                                                | Idle                 |                             |                    |                     |                    |  |  |  |  |  |

| bit 3        |                                                       | •                                                                                                                                                            |                      | e mode only) <sup>(2)</sup> |                    |                     |                    |  |  |  |  |  |

|              |                                                       | <b>RCEN:</b> Receive Enable bit (Master Receive mode only) <sup>(2)</sup><br>1 = Enables Receive mode for I <sup>2</sup> C                                   |                      |                             |                    |                     |                    |  |  |  |  |  |

|              | 0 = Receive                                           |                                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

| bit 2        | PEN: Stop C                                           | ondition Enable                                                                                                                                              | bit <sup>(2)</sup>   |                             |                    |                     |                    |  |  |  |  |  |

|              |                                                       | •                                                                                                                                                            | SDA and SCL          | pins; automati              | cally cleared l    | oy hardware.        |                    |  |  |  |  |  |

|              | 0 = Stop con                                          |                                                                                                                                                              |                      | (2)                         |                    |                     |                    |  |  |  |  |  |

| bit 1        |                                                       | RSEN: Repeated Start Condition Enable bit <sup>(2)</sup>                                                                                                     |                      |                             |                    |                     |                    |  |  |  |  |  |

|              |                                                       | <ul> <li>1 = Initiate Repeated Start condition on SDA and SCL pins; automatically cleared by hardware.</li> <li>0 = Repeated Start condition Idle</li> </ul> |                      |                             |                    |                     |                    |  |  |  |  |  |

| bit 0        | •                                                     | ondition Enable                                                                                                                                              |                      |                             |                    |                     |                    |  |  |  |  |  |

|              |                                                       |                                                                                                                                                              |                      | _ pins; automati            | cally cleared l    | hy hardware         |                    |  |  |  |  |  |

|              | 1 = Initiate Si<br>0 = Start con                      |                                                                                                                                                              |                      | - pino, automati            | carry ocareu i     | oy naraware.        |                    |  |  |  |  |  |

| Noto 1:      | /alua that will be                                    | transmitted wh                                                                                                                                               | on the user ini      | tiatos an Ackas             | wlodao socur       | nco at the end of   |                    |  |  |  |  |  |

|              | /alue that will be                                    |                                                                                                                                                              |                      |                             | <b>-</b> ·         |                     |                    |  |  |  |  |  |

2: If the l<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

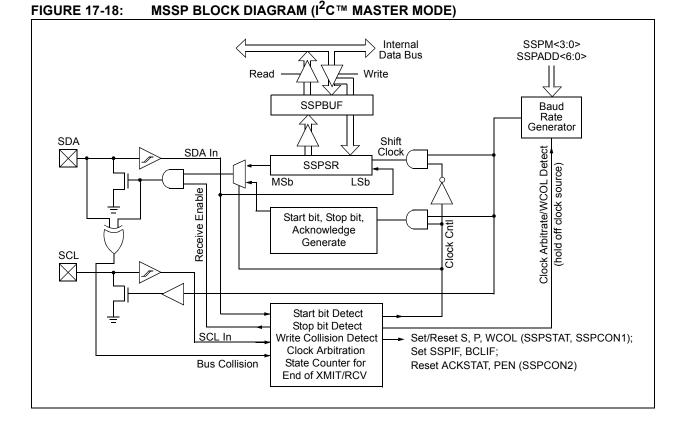

#### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- Start Condition

- Stop Condition

- Data Transfer Byte Transmitted/Received

- Acknowledge Transmit

- Repeated Start

#### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF bit is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

## 17.4.10.2 WCOL Status Flag

If the user writes to the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur) 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL is clear after each write to SSPBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

### 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

# 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The MSSP module must be in an Idle state   |

|-------|--------------------------------------------|

|       | before the RCEN bit is set or the RCEN bit |

|       | will be disregarded.                       |

The Baud Rate Generator begins counting, and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

## 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 19.5 AUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA2<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK2 pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 19.5.1 AUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG2 and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG2 register.

- c) Flag bit, TX2IF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREG2 register will transfer the second word to the TSR and flag bit, TX2IF, will now be set.

- e) If enable bit, TX2IE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TX2IE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG2 register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name   | Bit 7                               | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------|-------------------------------------|--------------|--------|--------|-------|--------|--------|-------|----------------------------|

| INTCON | GIE/GIEH                            | PEIE/GIEL    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 57                         |

| PIR3   | —                                   | —            | RC2IF  | TX2IF  | —     | CCP2IF | CCP1IF | —     | 59                         |

| PIE3   | —                                   | —            | RC2IE  | TX2IE  | _     | CCP2IE | CCP1IE | _     | 59                         |

| IPR3   |                                     | _            | RC2IP  | TX2IP  | —     | CCP2IP | CCP1IP | —     | 59                         |

| RCSTA2 | SPEN                                | RX9          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D  | 61                         |

| TXREG2 | AUSART T                            | ransmit Regi | ster   |        |       |        |        |       | 61                         |

| TXSTA2 | CSRC                                | TX9          | TXEN   | SYNC   | —     | BRGH   | TRMT   | TX9D  | 61                         |

| SPBRG2 | AUSART Baud Rate Generator Register |              |        |        |       |        |        |       |                            |

| LATG   | U2OD                                | U10D         |        | LATG4  | LATG3 | LATG2  | LATG1  | LATG0 | 60                         |

#### TABLE 19-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

### 20.2 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This occurs when the ACQT<2:0> bits (ADCON2<5:3>) remain in their Reset state ('000') and is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQT bits can be set to select a programmable <u>acquisition</u> time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

#### 20.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable.

There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible but greater than the minimum TAD (see parameter 130 in Table 26-26 for more information).

Table 20-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### TABLE 20-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S        | Maximum   |                         |

|-------------------|-----------|-------------------------|

| Operation         | ADCS<2:0> | Device<br>Frequency     |

| 2 Tosc            | 000       | 2.86 MHz                |

| 4 Tosc            | 100       | 5.71 MHz                |

| 8 Tosc            | 001       | 11.43 MHz               |

| 16 Tosc           | 101       | 22.86 MHz               |

| 32 Tosc           | 010       | 40.0 MHz                |

| 64 Tosc           | 110       | 40.0 MHz                |

| RC <sup>(1)</sup> | x11       | 1.00 MHz <sup>(2)</sup> |

Note 1: The RC source has a typical TAD time of  $4 \ \mu$ s.

2: For device frequencies above 1 MHz, the device must be in Sleep mode for the entire conversion or the A/D accuracy may be out of specification.

# 20.4 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

#### TABLE 23-2: CONFIGURATION BITS AND DEVICE IDs

| File    | e Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value <sup>(1)</sup> |

|---------|-------------------------|-------|-------|--------|-------|--------|--------|--------|--------|--------------------------------------------------|

| 300000h | CONFIG1L                | DEBUG | XINST | STVREN | _     | _      | _      | _      | WDTEN  | 1111                                             |

| 300001h | CONFIG1H                | _(2)  | (2)   | _(2)   | (2)   | _(3)   | CP0    | _      | _      | 01                                               |

| 300002h | CONFIG2L                | IESO  | FCMEN | —      | _     | _      | FOSC2  | FOSC1  | FOSC0  | 11111                                            |

| 300003h | CONFIG2H                | (2)   | (2)   | (2)    | (2)   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | 1111                                             |

| 300004h | CONFIG3L <sup>(4)</sup> | WAIT  | BW    | EMB1   | EMB0  | EASHFT | _      |        | _      | 1111 1                                           |

| 300005h | CONFIG3H                | (2)   | (2)   | (2)    | (2)   | _      | _      | _      | CCP2MX | 1                                                |

| 3FFFFEh | DEVID1                  | DEV2  | DEV1  | DEV0   | REV4  | REV3   | REV2   | REV1   | REV0   | xxxx xxxx <sup>(5)</sup>                         |

| 3FFFFFh | DEVID2                  | DEV10 | DEV9  | DEV8   | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 10x1 <sup>(5)</sup>                         |

Legend: x = unknown, — = unimplemented. Shaded cells are unimplemented, read as '0'.

**Note 1:** Values reflect the unprogrammed state as received from the factory and following Power-on Resets. In all other Reset states, the configuration bytes maintain their previously programmed states.

2: The value of these bits in program memory should always be 'l'. This ensures that the location is executed as a NOP if it is accidentally executed.

**3:** This bit should always be maintained as '0'.

4: CONFIG3L is implemented in 80-pin devices only.

5: See Register 23-7 and Register 23-8 for DEVID values. These registers are read-only and cannot be programmed by the user.

| TABLE 25-2: | PIC18F85J11 FAMILY INSTRUCTION SET |

|-------------|------------------------------------|

|-------------|------------------------------------|

| Mnemonic, |                                 | Description                              |            | 16-bit Instruction Word |      |      | Vord | Status          |            |

|-----------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|-----------------|------------|

| Opera     | nds                             | Description                              | Cycles     | MSb                     |      |      | LSb  | Affected        | Notes      |

| BYTE-OR   | ENTED                           | OPERATIONS                               |            |                         |      |      |      |                 |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff | Z, N            | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff | Z               | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff | None            | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff | None            | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff | None            | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff | None            | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff | None            | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff | None            | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff | Z, N            | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff | ffff | ffff | None            |            |

|           |                                 | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff | ffff | ffff |                 |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff | None            |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff | None            | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff | C, Z, N         | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff | Z, N            |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff | C, Z, N         |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff | Z, N            |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff | None            | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB    |                                 | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff |      | C, DC, Z, OV, N |            |

|           |                                 | Borrow                                   |            |                         |      |      |      |                 | _          |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    |      | ffff | ffff | None            | 4          |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff | None            | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da | ffff | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

# PIC18F85J11 FAMILY

| CPFS        | SGT                | Compare f                                                    | npare f with W, Skip if f > W                                                                                                                                                                                                                       |             |  |  |  |  |

|-------------|--------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| Synta       | ax:                | CPFSGT f                                                     | {,a}                                                                                                                                                                                                                                                |             |  |  |  |  |

| -           | ands:              | $0 \leq f \leq 255$                                          | $0 \le f \le 255$                                                                                                                                                                                                                                   |             |  |  |  |  |

| Oper        | ation:             | a ∈ [0, 1]<br>(f) – (W),<br>skip if (f) ><br>(unsigned o     | (W)<br>comparison)                                                                                                                                                                                                                                  |             |  |  |  |  |

| Statu       | s Affected:        | None                                                         | • •                                                                                                                                                                                                                                                 |             |  |  |  |  |

| Enco        |                    | 0110                                                         | 010a fff                                                                                                                                                                                                                                            | f ffff      |  |  |  |  |

|             | ription:           |                                                              |                                                                                                                                                                                                                                                     |             |  |  |  |  |

| Desc        |                    | location 'f' t                                               | the contents of<br>to the contents<br>an unsigned s                                                                                                                                                                                                 | of the W by |  |  |  |  |

|             |                    | contents of<br>instruction i                                 | nts of 'f' are gro<br>WREG, then t<br>is discarded ar<br>istead, making<br>istruction.                                                                                                                                                              | he fetched  |  |  |  |  |

|             |                    |                                                              | he Access Bar<br>he BSR is use                                                                                                                                                                                                                      |             |  |  |  |  |

|             |                    | set is enabl<br>in Indexed<br>mode wher<br><b>Section 25</b> | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |             |  |  |  |  |

| 10/0        | I                  |                                                              | Set Would Tor                                                                                                                                                                                                                                       | uetalis.    |  |  |  |  |

| Word        |                    | 1                                                            |                                                                                                                                                                                                                                                     |             |  |  |  |  |

| Cycle       |                    |                                                              | cycles if skip ar<br>a 2-word instru                                                                                                                                                                                                                |             |  |  |  |  |

| QC          | ycle Activity:     | -                                                            |                                                                                                                                                                                                                                                     |             |  |  |  |  |

|             | Q1                 | Q2                                                           | Q3                                                                                                                                                                                                                                                  | Q4          |  |  |  |  |

|             | Decode             | Read                                                         | Process                                                                                                                                                                                                                                             | No          |  |  |  |  |

|             | -                  | register 'f'                                                 | Data                                                                                                                                                                                                                                                | operation   |  |  |  |  |

| lf sk       |                    | 00                                                           | 00                                                                                                                                                                                                                                                  | 04          |  |  |  |  |

| 1           | Q1<br>No           | Q2<br>No                                                     | Q3<br>No                                                                                                                                                                                                                                            | Q4<br>No    |  |  |  |  |

|             | operation          | operation                                                    | operation                                                                                                                                                                                                                                           | operation   |  |  |  |  |

| lf sk       | ip and followe     |                                                              |                                                                                                                                                                                                                                                     | oporation   |  |  |  |  |

|             | Q1                 | Q2                                                           | Q3                                                                                                                                                                                                                                                  | Q4          |  |  |  |  |

|             | No                 | No                                                           | No                                                                                                                                                                                                                                                  | No          |  |  |  |  |

|             | operation          | operation                                                    | operation                                                                                                                                                                                                                                           | operation   |  |  |  |  |

|             | No                 | No                                                           | No                                                                                                                                                                                                                                                  | No          |  |  |  |  |

|             | operation          | operation                                                    | operation                                                                                                                                                                                                                                           | operation   |  |  |  |  |

| <u>Exan</u> |                    | HERE<br>NGREATER<br>GREATER                                  | CPFSGT RE<br>:<br>:                                                                                                                                                                                                                                 | G, 0        |  |  |  |  |

|             | Before Instruc     |                                                              |                                                                                                                                                                                                                                                     | ,<br>,      |  |  |  |  |

|             | PC<br>W            | = Ad<br>= ?                                                  | dress (HERE                                                                                                                                                                                                                                         | )           |  |  |  |  |

|             | After Instructio   | -                                                            |                                                                                                                                                                                                                                                     |             |  |  |  |  |

|             | If REG             | > W;                                                         |                                                                                                                                                                                                                                                     |             |  |  |  |  |

|             | PC<br>If REG<br>PC | ≤ W;                                                         | dress (GREAT                                                                                                                                                                                                                                        |             |  |  |  |  |

|             |                    |                                                              |                                                                                                                                                                                                                                                     |             |  |  |  |  |

| Syntax:CPFSLT f {.a}Operands: $0 \le f \le 255$<br>$a \in [0, 1]$ Operation:(f) - (W),<br>skip if (f) < (W)<br>(unsigned comparison)Status Affected:NoneEncoding: $0110$ $000a$ ffffDescription:Compares the contents of data memory<br>location 'f' to the contents of W by<br>performing an unsigned subtraction.<br>If the contents of 'f are less than the<br>contents of W, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.Words:1Cycles:1(2)<br>Note:Q Cycle Activity:Q1Q1Q2Q3Q4NoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoQ1Q2Q3Q4NoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoQ1Q2Q3Q4NoQ1Q2Q3Q4                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| a $\in [0, 1]$ Operation: $(f) - (W)$ ,<br>skip if $(f) < (W)$<br>(unsigned comparison)Status Affected:NoneEncoding: $0110$ $000a$ ffffDescription:Compares the contents of data memory<br>location 'f' to the contents of W by<br>performing an unsigned subtraction.<br>If the contents of 'f' are less than the<br>contents of W, then the fetched<br>instruction is discarded and a NOP is<br>executed instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.Words:1Cycles:1(2)<br>Note:Q Cycle Activity:Q1Q2Q3Q4DecodeReadProcess<br>No<br>operationIf skip:Q1Q1Q2Q3Q4NoNo<br>operationIf skip and followed by 2-word instruction:<br>Q1Q1Q2Q3Q4No<br>operationNo<br>operationNo<br>operationIf skip and followed by 2-word instruction:<br>Q1Q1Q2Q3Q4                                                                                                                                                                                                                                                           |  |  |  |  |