Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

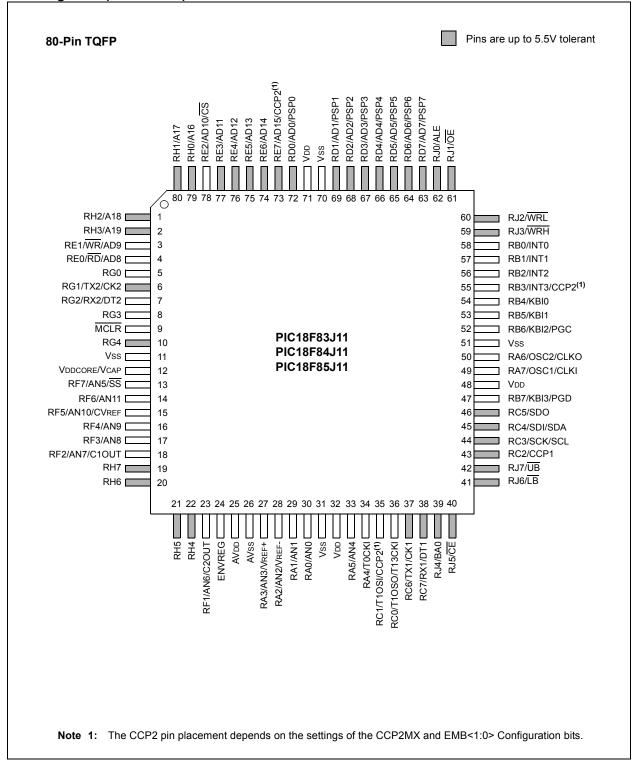

| Number of I/O              | 67                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

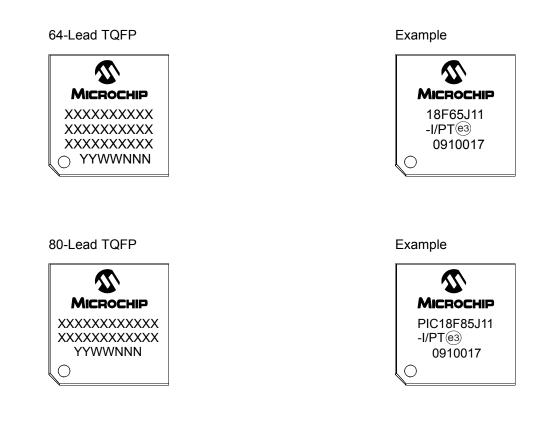

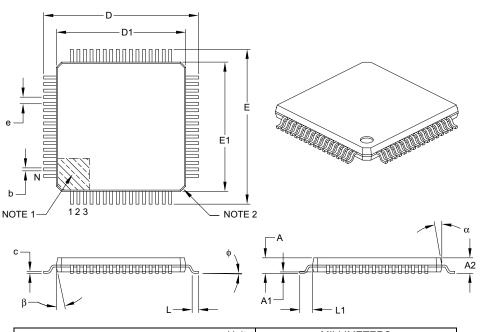

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f84j11-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pin Diagrams (Continued)**

| R/W-0                                                                                 | R/W-0                | R/W-0            | R/W-0          | R/W-0              | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|---------------------------------------------------------------------------------------|----------------------|------------------|----------------|--------------------|-----------------|-----------------|-------|--|--|--|

| INTSRC                                                                                | PLLEN <sup>(1)</sup> | TUN5             | TUN4           | TUN3               | TUN2            | TUN1            | TUN0  |  |  |  |

| bit 7                                                                                 |                      |                  |                |                    |                 |                 | bit 0 |  |  |  |

|                                                                                       |                      |                  |                |                    |                 |                 |       |  |  |  |

| Legend:                                                                               |                      |                  |                |                    |                 |                 |       |  |  |  |

| R = Readable                                                                          | e bit                | W = Writable     | bit            | U = Unimplen       | nented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at                                                                         | POR                  | '1' = Bit is set |                | '0' = Bit is clea  | ared            | x = Bit is unkn | iown  |  |  |  |

|                                                                                       |                      |                  |                |                    |                 |                 |       |  |  |  |

| bit 7                                                                                 | INTSRC: Inte         | rnal Oscillator  | Low-Frequenc   | y Source Selec     | t bit           |                 |       |  |  |  |

|                                                                                       | 1 = 31.25 kH         | z device clock   | derived from 8 | MHz INTOSC         | source (divide  | -by-256 enabled | d)    |  |  |  |

|                                                                                       | 0 = 31 kHz de        | evice clock der  | ived from INT  | RC 31 kHz osci     | llator          |                 |       |  |  |  |

| bit 6                                                                                 | PLLEN: Freq          | uency Multiplie  | r PLL Enable   | bit <sup>(1)</sup> |                 |                 |       |  |  |  |

|                                                                                       | 1 = PLL is en        | abled            |                |                    |                 |                 |       |  |  |  |

|                                                                                       | 0 = PLL is dis       | sabled           |                |                    |                 |                 |       |  |  |  |

| bit 5-0                                                                               | TUN<5:0>: Fa         | ast RC Oscillat  | or (INTOSC) F  | Frequency Tunir    | ng bits         |                 |       |  |  |  |

|                                                                                       | 011111 <b>= Ma</b>   | ximum frequer    | псу            |                    |                 |                 |       |  |  |  |

|                                                                                       | •                    | •                |                |                    |                 |                 |       |  |  |  |

|                                                                                       | •                    | •                |                |                    |                 |                 |       |  |  |  |

|                                                                                       | 000001               |                  |                |                    |                 |                 |       |  |  |  |

| 000000 = Center frequency. Fast RC oscillator is running at the calibrated frequency. |                      |                  |                |                    |                 |                 |       |  |  |  |

|                                                                                       | 111111<br>•          | •                |                |                    |                 |                 |       |  |  |  |

|                                                                                       | •                    | •                |                |                    |                 |                 |       |  |  |  |

|                                                                                       | 100000 <b>= Mi</b> r | nimum frequen    | су             |                    |                 |                 |       |  |  |  |

|                                                                                       |                      |                  | -              |                    |                 |                 |       |  |  |  |

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

**Note 1:** Available only for ECPLL and HSPLL oscillator configurations; otherwise, this bit is unavailable and reads as '0'.

#### 3.3 Clock Sources and Oscillator Switching

Essentially, PIC18F85J11 family devices have three independent clock sources:

- · Primary oscillators

- · Secondary oscillators

- Internal oscillator

The **primary oscillators** can be thought of as the main device oscillators. These are any external oscillators connected to the OSC1 and OSC2 pins, and include the External Crystal and Resonator modes and the External Clock modes. In some circumstances, the internal oscillator block may be considered a primary oscillator. The particular mode is defined by the FOSC Configuration bits. The details of these modes are covered in **Section 3.4 "External Oscillator Modes**".

The **secondary oscillators** are external clock sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode. PIC18F85J11 family devices offer the Timer1 oscillator as a secondary oscillator source. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock. The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**

In addition to being a primary clock source in some circumstances, the **internal oscillator** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor. The internal oscillator block is discussed in more detail in **Section 3.5** "Internal Oscillator **Block**".

The PIC18F85J11 family includes features that allow the device clock source to be switched from the main oscillator, chosen by device configuration, to one of the alternate clock sources. When an alternate clock source is enabled, various power-managed operating modes are available.

#### 3.4 External Oscillator Modes

# 3.4.1 CRYSTAL OSCILLATOR/CERAMIC RESONATORS (HS MODES)

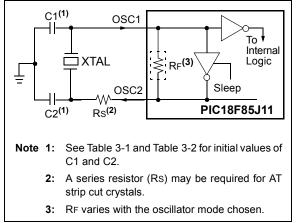

In HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-2 shows the pin connections.

The oscillator design requires the use of a parallel resonant crystal.

| Note: | Use of a series resonant crystal may give a |

|-------|---------------------------------------------|

|       | frequency out of the crystal manufacturer's |

|       | specifications.                             |

# TABLE 3-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |                     |                |                |  |  |  |  |  |

|--------------------------------|---------------------|----------------|----------------|--|--|--|--|--|

| Mode                           | Mode Freq. OSC1 OSC |                |                |  |  |  |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |  |  |

Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator-specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC<sup>®</sup> Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following Table 3-2 for additional information.

# TABLE 3-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|------------------|-------------------------------------|-------|--|--|

|          | Fled.            | C1                                  | C2    |  |  |

| HS       | 4 MHz            | 27 pF                               | 27 pF |  |  |

|          | 8 MHz            | 22 pF                               | 22 pF |  |  |

|          | 20 MHz           | 15 pF                               | 15 pF |  |  |

Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

Refer to the Microchip application notes cited in Table 3-1 for oscillator-specific information. Also see the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required to avoid overdriving crystals with low drive level specification.

- 4: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

#### FIGURE 3-2:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

#### 3.6 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In RC\_RUN and RC\_IDLE modes, the internal oscillator provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 23.2 "Watchdog Timer (WDT)" through Section 23.5 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock (RTC). Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTn pins and others). Peripherals that may add significant current consumption are listed in Section 26.2 "DC Characteristics: Power-Down and Supply Current".

# 3.7 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.6 "Power-up Timer (PWRT)**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 26-12). It is always enabled.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval TCSD (parameter 38, Table 26-12), following POR, while the controller becomes ready to execute instructions.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| EC, ECPLL       | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| HS, HSPLL       | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

| INTOSC          | I/O pin, RA6, direction controlled by TRISA<6>        | I/O pin, RA7, direction controlled by TRISA<7>        |

TABLE 3-3:

OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 5-2 in Section 5.0 "Reset" for time-outs due to Sleep and MCLR Reset.

# 4.0 POWER-MANAGED MODES

The PIC18F85J11 family devices provide the ability to manage power consumption by simply managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. For the sake of managing power in an application, there are three primary modes of operation:

- Run mode

- Idle mode

- · Sleep mode

These modes define which portions of the device are clocked and at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> MCUs. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC MCUs, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and which clock source is to be used. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

## 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<2:0> Configuration bits

- the secondary clock (Timer1 oscillator)

- · the internal oscillator

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode -   | oso         | CON bits | Modul           | e Clocking |                                                                                  |  |  |  |

|----------|-------------|----------|-----------------|------------|----------------------------------------------------------------------------------|--|--|--|

|          | IDLEN<7>(1) | SCS<1:0> | CPU Peripherals |            | Available Clock and Oscillator Source                                            |  |  |  |

| Sleep    | 0           | N/A      | Off             | Off        | None – All clocks are disabled                                                   |  |  |  |

| PRI_RUN  | N/A         | 10       | Clocked         | Clocked    | Primary – HS, EC, HSPLL, ECPLL;<br>this is the normal, full-power execution mode |  |  |  |

| SEC_RUN  | N/A         | 01       | Clocked         | Clocked    | Secondary – Timer1 Oscillator                                                    |  |  |  |

| RC_RUN   | N/A         | 11       | Clocked         | Clocked    | Internal Oscillator                                                              |  |  |  |

| PRI_IDLE | 1           | 10       | Off             | Clocked    | Primary – HS, EC, HSPLL, ECPLL                                                   |  |  |  |

| SEC_IDLE | 1           | 01       | Off             | Clocked    | Secondary – Timer1 Oscillator                                                    |  |  |  |

| RC_IDLE  | 1           | 11       | Off             | Clocked    | Internal Oscillator                                                              |  |  |  |

| TABLE 4-1: | POWER-MANAGED MODES |

|------------|---------------------|

|------------|---------------------|

**Note 1:** IDLEN reflects its value when the **SLEEP** instruction is executed.

| IABLE 3-2: | INTHALIZA                   | TION CONDI  | TIONS FOR ALL RE                   | GIGTERS                                                                             |                                 |  |

|------------|-----------------------------|-------------|------------------------------------|-------------------------------------------------------------------------------------|---------------------------------|--|

| Register   | Register Applicable Devices |             | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>S <u>tac</u> k Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| TOSU       | PIC18F6XJ11                 | PIC18F8XJ11 | 0 0000                             | 0 0000                                                                              | 0 uuuu <b>(1)</b>               |  |

| TOSH       | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu <sup>(1)</sup>        |  |

| TOSL       | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu <b>(1)</b>            |  |

| STKPTR     | PIC18F6XJ11                 | PIC18F8XJ11 | uu-0 0000                          | 00-0 0000                                                                           | uu-u uuuu <b>(1)</b>            |  |

| PCLATU     | PIC18F6XJ11                 | PIC18F8XJ11 | 0 0000                             | 0 0000                                                                              | u uuuu                          |  |

| PCLATH     | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| PCL        | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU    | PIC18F6XJ11                 | PIC18F8XJ11 | 00 0000                            | 00 0000                                                                             | uu uuuu                         |  |

| TBLPTRH    | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| TBLPTRL    | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| TABLAT     | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| PRODH      | PIC18F6XJ11                 | PIC18F8XJ11 | xxxx xxxx                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| PRODL      | PIC18F6XJ11                 | PIC18F8XJ11 | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| INTCON     | PIC18F6XJ11                 | PIC18F8XJ11 | 0000 000x                          | 0000 000u                                                                           | uuuu uuuu <sup>(3)</sup>        |  |

| INTCON2    | PIC18F6XJ11                 | PIC18F8XJ11 | 1111 1111                          | 1111 1111                                                                           | uuuu uuuu <sup>(3)</sup>        |  |

| INTCON3    | PIC18F6XJ11                 | PIC18F8XJ11 | 1100 0000                          | 1100 0000                                                                           | uuuu uuuu <b>(3)</b>            |  |

| INDF0      | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTINC0   | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTDEC0   | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| PREINC0    | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| PLUSW0     | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| FSR0H      | PIC18F6XJ11                 | PIC18F8XJ11 | xxxx                               | uuuu                                                                                | uuuu                            |  |

| FSR0L      | PIC18F6XJ11                 | PIC18F8XJ11 | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| WREG       | PIC18F6XJ11                 | PIC18F8XJ11 | xxxx xxxx                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| INDF1      | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTINC1   | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTDEC1   | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| PREINC1    | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| PLUSW1     | PIC18F6XJ11                 | PIC18F8XJ11 | N/A                                | N/A                                                                                 | N/A                             |  |

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 5-1 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

| Pin Name    | Function            | TRIS<br>Setting | I/O | I/O<br>Type      | Description                                                                              |

|-------------|---------------------|-----------------|-----|------------------|------------------------------------------------------------------------------------------|

| RC0/T1OSO/  | RC0                 | 0               | 0   | DIG              | LATC<0> data output.                                                                     |

| T13CKI      |                     | 1               | I   | ST               | PORTC<0> data input.                                                                     |

|             | T10SO               | x               | 0   | ANA              | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O.  |

|             | T13CKI              | 1               | I   | ST               | Timer1/Timer3 counter input.                                                             |

| RC1/T1OSI/  | RC1                 | 0               | 0   | DIG              | LATC<1> data output.                                                                     |

| CCP2        |                     | 1               | Ι   | ST               | PORTC<1> data input.                                                                     |

|             | T10SI               | x               | Ι   | ANA              | Timer1 oscillator input; enabled when Timer1 oscillator enabled. Disables digital I/O.   |

|             | CCP2 <sup>(1)</sup> | 0               | 0   | DIG              | CCP2 compare output and CCP2 PWM output; takes priority over port data.                  |

|             |                     | 1               | Ι   | ST               | CCP2 capture input.                                                                      |

| RC2/CCP1    | RC2                 | 0               | 0   | DIG              | LATC<2> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<2> data input.                                                                     |

|             | CCP1                | 0               | 0   | DIG              | CCP1 compare output and CCP1 PWM output; takes priority over port data.                  |

|             |                     | 1               | Ι   | ST               | CCP1 capture input.                                                                      |

| RC3/SCK/SCL | RC3                 | 0               | 0   | DIG              | LATC<3> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<3> data input.                                                                     |

|             | SCK                 | 0               | 0   | DIG              | SPI clock output (MSSP module); takes priority over port data.                           |

| -           |                     | 1               |     | ST               | SPI clock input (MSSP module).                                                           |

|             | SCL                 | 0               | 0   | DIG              | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data. |

|             |                     | 1               | Ι   | I <sup>2</sup> C | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting.        |

| RC4/SDI/SDA | RC4                 | 0               | 0   | DIG              | LATC<4> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<4> data input.                                                                     |

|             | SDI                 | 1               | Ι   | ST               | SPI data input (MSSP module).                                                            |

|             | SDA                 | 1               | 0   | DIG              | I <sup>2</sup> C data output (MSSP module); takes priority over port data.               |

|             |                     | 1               | Ι   | l <sup>2</sup> C | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.         |

| RC5/SDO     | RC5                 | 0               | 0   | DIG              | LATC<5> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<5> data input.                                                                     |

|             | SDO                 | 0               | 0   | DIG              | SPI data output (MSSP module); takes priority over port data.                            |

| RC6/TX1/CK1 | RC6                 | 0               | 0   | DIG              | LATC<6> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<6> data input.                                                                     |

|             | TX1                 | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data            |

|             | CK1                 | 1               | 0   | DIG              | Synchronous serial data input (EUSART module). User must configure as an input.          |

|             |                     | 1               | Ι   | ST               | Synchronous serial clock input (EUSART module).                                          |

| RC7/RX1/DT1 | RC7                 | 0               | 0   | DIG              | LATC<7> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<7> data input.                                                                     |

|             | RX1                 | 1               | I   | ST               | Asynchronous serial receive data input (EUSART module).                                  |

|             | DT1                 | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data.           |

|             |                     | 1               | —   | ST               | Synchronous serial data input (EUSART module). User must configure as an input.          |

TABLE 11-7:PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for CCP2 when CCP2MX Configuration bit is set.

| Pin Name    | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                      |  |

|-------------|----------|-----------------|-----|-------------|----------------------------------------------------------------------------------|--|

| RG0         | RG0      | 0               | 0   | DIG         | LATG<0> data output.                                                             |  |

|             |          | 1               | I   | ST          | PORTG<0> data input.                                                             |  |

| RG1/TX2/CK2 | R21      | 0               | 0   | DIG         | LATG<1> data output.                                                             |  |

|             |          | 1               | Ι   | ST          | PORTG<1> data input.                                                             |  |

|             | TX2      | 1               | 0   | DIG         | Synchronous serial data output (AUSART2 module); takes priority over port data.  |  |

|             | CK2      | 1               | 0   | DIG         | Synchronous serial data input (AUSART2 module). User must configure as an input. |  |

|             |          | 1               | Ι   | ST          | Synchronous serial clock input (AUSART2 module).                                 |  |

| RG2/RX2/DT2 | RG2      | 0               | 0   | DIG         | LATG<2> data output.                                                             |  |

|             |          | 1               | Ι   | ST          | PORTG<2> data input.                                                             |  |

|             | RX2      | 1               | Ι   | ST          | Asynchronous serial receive data input (AUSART2 module).                         |  |

|             | DT2      | 1               | 0   | DIG         | Synchronous serial data output (AUSART2 module); takes priority over port data.  |  |

|             |          | 1               | Ι   | ST          | Synchronous serial data input (AUSART2 module). User must configure as an input. |  |

| RG3         | RG3      | 0               | 0   | DIG         | LATG<3> data output.                                                             |  |

|             |          | 1               | I   | ST          | PORTG<3> data input.                                                             |  |

| RG4         | RG4      | 0               | 0   | DIG         | LATG<4> data output.                                                             |  |

|             |          | 1               | I   | ST          | PORTG<4> data input.                                                             |  |

### TABLE 11-15: PORTG FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name  | Bit 7 | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|-------|-------|--------|---------------------|--------|--------|--------|--------|--------|----------------------------|

| PORTG | RDPU  | REPU   | RJPU <sup>(1)</sup> | RG4    | RG3    | RG2    | RG1    | RG0    | 60                         |

| LATG  | U2OD  | U10D   | —                   | LATG4  | LATG3  | LATG2  | LATG1  | LATG0  | 60                         |

| TRISG | SPIOD | CCP2OD | CCP10D              | TRISG4 | TRISG3 | TRISG2 | TRISG1 | TRISG0 | 60                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTG.

Note 1: Unimplemented on 64-pin devices, read as '0'.

NOTES:

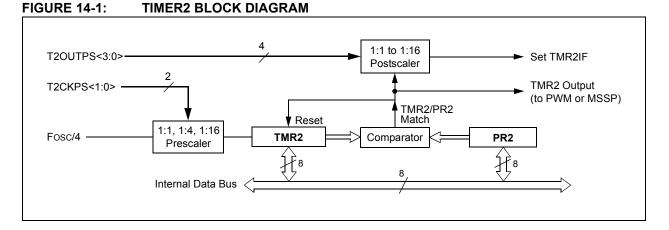

# 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

# 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 17.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7       | Bit 6        | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|-------------|--------------|----------|----------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH    | PEIE/GIEL    | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 57                         |

| PIR1   | PSPIF       | ADIF         | RC1IF    | TX1IF    | SSPIF    | _      | TMR2IF  | TMR1IF  | 59                         |

| PIE1   | PSPIE       | ADIE         | RC1IE    | TX1IE    | SSPIE    | —      | TMR2IE  | TMR1IE  | 59                         |

| IPR1   | PSPIP       | ADIP         | RC1IP    | TX1IP    | SSPIP    | —      | TMR2IP  | TMR1IP  | 59                         |

| TMR2   | Timer2 Reg  | jister       |          |          |          |        |         |         | 58                         |

| T2CON  | _           | T2OUTPS3     | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 58                         |

| PR2    | Timer2 Peri | iod Register |          |          |          |        |         |         | 58                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

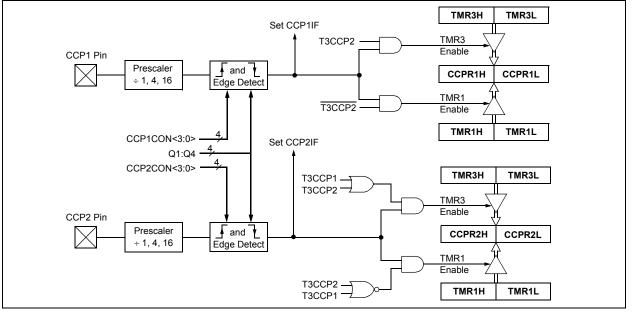

## 16.2 Capture Mode

In Capture mode, the CCPR2H:CCPR2L register pair captures the 16-bit value of the TMR1 or TMR3 register when an event occurs on the CCP2 pin (RB3, RC1 or RE7, depending on device configuration). An event is defined as one of the following:

- every falling edge

- every rising edge

- · every 4th rising edge

- · every 16th rising edge

The event is selected by the mode select bits, CCP2M<3:0> (CCP2CON<3:0>). When a capture is made, the interrupt request flag bit, CCP2IF (PIR3<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR2 is read, the old captured value is overwritten by the new captured value.

#### 16.2.1 CCPx PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

**Note:** If RB3/INT3/CCP2, RC1/T1OSI/CCP2 or RE7/CCP2 is configured as an output, a write to the port can cause a capture condition.

#### 16.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 16.1.1 "CCP Modules and Timer Resources").

#### 16.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP2IE bit (PIE3<2>) clear to avoid false interrupts and should clear the flag bit, CCP2IF, following any such change in operating mode.

#### 16.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCP2M<3:0>). Whenever the CCP2 module is turned off, or the CCP2 module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ; Turn CCP module off |

|-----------------------|

| ; Load WREG with the  |

| ; new prescaler mode  |

| ; value and CCP ON    |

| ; Load CCP2CON with   |

| ; this value          |

|                       |

### FIGURE 16-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

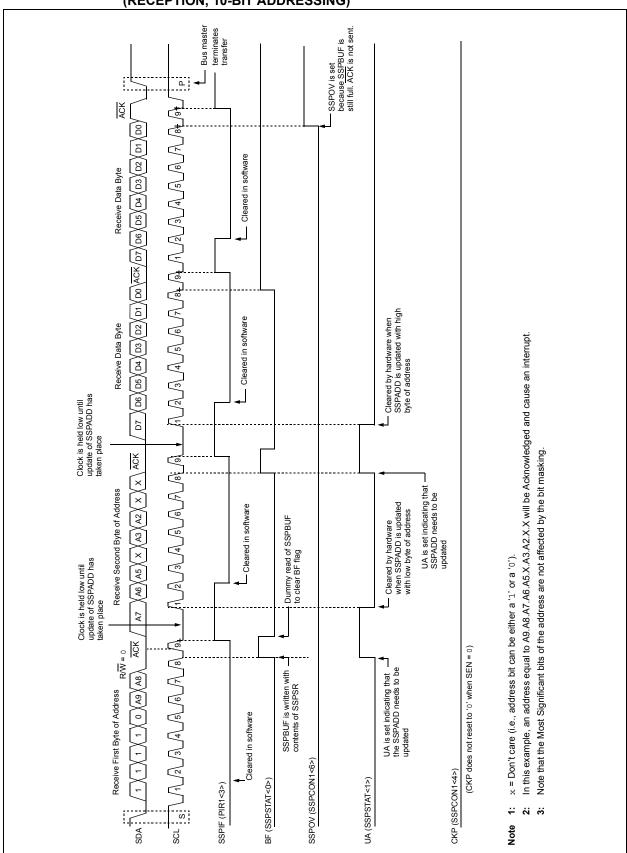

#### FIGURE 17-12: I<sup>2</sup>C<sup>™</sup> SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01001 (RECEPTION, 10-BIT ADDRESSING)

#### 17.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 17.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

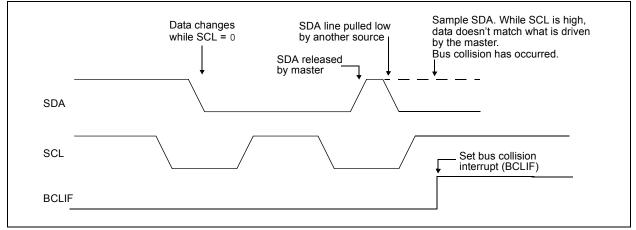

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high, and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 17-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 17-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

#### 18.2.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 18-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX1 signal, the RX1 signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN/J2602 bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG1 begins counting up, using the preselected clock source on the first rising edge of RX1. After eight bits on the RX1 pin, or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH1:SPBRG1 register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON1<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 18-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock can be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG1 and SPBRGH1 as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH1 register. Refer to Table 18-4 for counter clock rates to the BRG. While the ABD sequence takes place, the EUSART state machine is held in Idle. The RC1IF interrupt is set once the fifth rising edge on RX1 is detected. The value in the RCREG1 needs to be read to clear the RC1IF interrupt. The contents of RCREG1 should be discarded.

| Note 1: | If the WUE bit is set with the ABDEN bit, |

|---------|-------------------------------------------|

|         | Auto-Baud Rate Detection will occur on    |

|         | the byte following the Break character.   |

2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

#### TABLE 18-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

**Note:** During the ABD sequence, SPBRG1 and SPBRGH1 are both used as a 16-bit counter, independent of the BRG16 setting.

#### 18.2.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG1 cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation. NOTES:

| CALI  | LW                                                                                             | Subroutine                                                                                                               | Subroutine Call Using WREG                                                                                                                                                                        |                                                                                                          |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Synta | ax:                                                                                            | CALLW                                                                                                                    |                                                                                                                                                                                                   |                                                                                                          |  |  |  |  |  |

| Oper  | ands:                                                                                          | None                                                                                                                     |                                                                                                                                                                                                   |                                                                                                          |  |  |  |  |  |

| Oper  | ation:                                                                                         | (W) → PCL<br>(PCLATH) -                                                                                                  | $\begin{array}{l} (\text{PC + 2}) \rightarrow \text{TOS}, \\ (\text{W}) \rightarrow \text{PCL}, \\ (\text{PCLATH}) \rightarrow \text{PCH}, \\ (\text{PCLATU}) \rightarrow \text{PCU} \end{array}$ |                                                                                                          |  |  |  |  |  |

| Statu | s Affected:                                                                                    | None                                                                                                                     | None                                                                                                                                                                                              |                                                                                                          |  |  |  |  |  |

| Enco  | ding:                                                                                          | 0000                                                                                                                     | 0000 000                                                                                                                                                                                          | 01 0100                                                                                                  |  |  |  |  |  |

| Desc  | ription                                                                                        | pushed onto<br>contents of<br>existing valu<br>contents of<br>latched into<br>respectively<br>executed as<br>new next in | turn address (I<br>o the return sta<br>W are written<br>ue is discarded<br>PCLATH and I<br>PCH and PCU<br>/. The second (<br>s a NOP instruct<br>struction is feto<br>L, there is no c            | ack. Next, the<br>to PCL; the<br>J. Then, the<br>PCLATU are<br>J,<br>cycle is<br>tion while the<br>ched. |  |  |  |  |  |

|       |                                                                                                | update W, S                                                                                                              | Unlike CALL, there is no option to update W, STATUS or BSR.                                                                                                                                       |                                                                                                          |  |  |  |  |  |

| Word  |                                                                                                |                                                                                                                          | 1                                                                                                                                                                                                 |                                                                                                          |  |  |  |  |  |

| Cycle |                                                                                                | 2                                                                                                                        |                                                                                                                                                                                                   |                                                                                                          |  |  |  |  |  |

| QC    | ycle Activity:                                                                                 |                                                                                                                          |                                                                                                                                                                                                   |                                                                                                          |  |  |  |  |  |

|       | Q1                                                                                             | Q2                                                                                                                       | Q3                                                                                                                                                                                                | Q4                                                                                                       |  |  |  |  |  |

|       | Decode                                                                                         | Read<br>WREG                                                                                                             | Push PC to<br>stack                                                                                                                                                                               | No<br>operation                                                                                          |  |  |  |  |  |

|       | No                                                                                             | No                                                                                                                       | No                                                                                                                                                                                                | No                                                                                                       |  |  |  |  |  |

|       | operation                                                                                      | operation                                                                                                                | operation                                                                                                                                                                                         | operation                                                                                                |  |  |  |  |  |

|       | nple:<br>PC<br>PCLATH<br>PCLATU<br>W<br>After Instructio<br>PC<br>TOS<br>PCLATH<br>PCLATU<br>W | = address<br>= 10h<br>= 00h<br>= 06h<br>m<br>= 001006i<br>= address<br>= 10h                                             | 、 <i>,</i>                                                                                                                                                                                        | )                                                                                                        |  |  |  |  |  |

| моу                                                  | SF                                                                                                              | Move Inde                                                                                                                                  | xed to f                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                        |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------|--|--|--|--|

| Synta                                                | ax:                                                                                                             | MOVSF [z,                                                                                                                                  | MOVSF [z <sub>s</sub> ], f <sub>d</sub>                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                                        |  |  |  |  |

|                                                      | ands:                                                                                                           | $0 \le z_s \le 12^{\circ}$                                                                                                                 | $\begin{array}{l} 0 \leq z_s \leq 127 \\ 0 \leq f_d \leq 4095 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                        |              |                                        |  |  |  |  |

| Oper                                                 | ation:                                                                                                          | ((FSR2) + 2                                                                                                                                | $((FSR2) + z_s) \rightarrow f_d$                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                        |  |  |  |  |

| Statu                                                | s Affected:                                                                                                     | None                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                                        |  |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) |                                                                                                                 | 1110<br>1111                                                                                                                               | 1011<br>ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ozzz<br>ffff | zzzz <sub>s</sub><br>ffff <sub>d</sub> |  |  |  |  |

| Description:                                         |                                                                                                                 | moved to d<br>actual addr<br>determined<br>offset, ' $z_s$ ',<br>of FSR2. Th<br>register is s<br>'f <sub>d</sub> ', in the s<br>can be any | The contents of the source register are<br>moved to destination register, 'f <sub>d</sub> '. The<br>actual address of the source register is<br>determined by adding the 7-bit literal<br>offset, ' $z_s$ ', in the first word to the value<br>of FSR2. The address of the destination<br>register is specified by the 12-bit literal,<br>'f <sub>d</sub> ', in the second word. Both addresses<br>can be anywhere in the 4096-byte data<br>space (000h to FFFh). |              |                                        |  |  |  |  |

|                                                      |                                                                                                                 | PCL, TOSI                                                                                                                                  | The MOVSF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register.                                                                                                                                                                                                                                                                                                                                                                         |              |                                        |  |  |  |  |

|                                                      |                                                                                                                 | If the resultant source address points to<br>an Indirect Addressing register, the<br>value returned will be 00h.                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                                        |  |  |  |  |

| Word                                                 | ls:                                                                                                             | 2                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                                        |  |  |  |  |

| Cycle                                                | es:                                                                                                             | 2                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                        |  |  |  |  |

| QC                                                   | ycle Activity:                                                                                                  |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                                        |  |  |  |  |

|                                                      | Q1                                                                                                              | Q2                                                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3            | Q4                                     |  |  |  |  |

|                                                      | Decode                                                                                                          | Determine source addr                                                                                                                      | Determ<br>source                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | Read<br>ource reg                      |  |  |  |  |

|                                                      | Decode                                                                                                          | No<br>operation<br>No dummy<br>read                                                                                                        | No<br>operat                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | Write<br>egister 'f'<br>(dest)         |  |  |  |  |

| <u>Exan</u>                                          | <u>nple:</u>                                                                                                    | MOVSF                                                                                                                                      | [05h],                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REG2         |                                        |  |  |  |  |

|                                                      | Before Instruct<br>FSR2<br>Contents<br>of 85h<br>REG2<br>After Instructio<br>FSR2<br>Contents<br>of 85h<br>REG2 | = 80<br>= 33<br>= 11<br>on<br>= 80                                                                                                         | ih<br>h<br>ih                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                                        |  |  |  |  |

#### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F85J11 Family (Industrial) (Continued)

|                  | <b>5J11 Family</b><br>strial) | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |               |                |          |                                       |                                 |  |

|------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|----------|---------------------------------------|---------------------------------|--|