Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 67                                                                          |

| Program Memory Size        | 16KB (8K × 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f84j11t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1.6 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members or even jumping from 64-pin to 80-pin devices.

The PIC18F85J11 family is also largely pin compatible with other PIC18 general purpose families, such as the PIC18F8720 and PIC18F8722. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining a similar feature set.

# 1.2 Other Special Features

- Communications: The PIC18F85J11 family incorporates a range of serial communication peripherals, including an Addressable USART, a separate Enhanced USART that supports LIN Specification LIN/J2602, and one Master SSP (MSSP) module capable of both SPI and I<sup>2</sup>C™ (Master and Slave) modes of operation.

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules. Up to four different time bases may be used to perform several different operations at once.

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 26.0 "Electrical Characteristics" for time-out periods.

# 1.3 Details on Individual Family Members

Devices in the PIC18F85J11 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in four ways:

- Flash program memory (three sizes, ranging from 8 Kbytes for PIC18FX3J11 devices to 32 Kbytes for PIC18FX5J11 devices).

- Data RAM (1024 bytes for PIC18FX3J11 and PIC18FX4J11 devices, 2048 bytes for PIC18FX5J11 devices).

- I/O ports (7 bidirectional ports on 64-pin devices, 9 bidirectional ports on 80-pin devices).

- 4. External Memory Bus (implemented in 80-pin devices only).

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

| Pin Name                                                                                                                                                                                                                     | Pin Number | Pin        | Buffer    | Description                                                   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|---------------------------------------------------------------|--|--|--|

| Fill Naille                                                                                                                                                                                                                  | TQFP       | Туре       | Туре      | Description                                                   |  |  |  |

|                                                                                                                                                                                                                              |            |            |           | PORTE is a bidirectional I/O port.                            |  |  |  |

| RE0/RD<br>RE0<br>RD                                                                                                                                                                                                          | 2          | I/O<br>I   | ST<br>TTL | Digital I/O.<br>Read control for Parallel Slave Port.         |  |  |  |

| RE1/WR<br>RE1<br>WR                                                                                                                                                                                                          | 1          | I/O<br>I   | ST<br>TTL | Digital I/O.<br>Write control for Parallel Slave Port.        |  |  |  |

| RE2/CS<br>RE2<br>CS                                                                                                                                                                                                          | 64         | I/O<br>I   | ST<br>TTL | Digital I/O.<br>Chip select control for Parallel Slave Port.  |  |  |  |

| RE3                                                                                                                                                                                                                          | 63         | I/O        | ST        | Digital I/O.                                                  |  |  |  |

| RE4                                                                                                                                                                                                                          | 62         | I/O        | ST        | Digital I/O.                                                  |  |  |  |

| RE5                                                                                                                                                                                                                          | 61         | I/O        | ST        | Digital I/O.                                                  |  |  |  |

| RE6                                                                                                                                                                                                                          | 60         | I/O        | ST        | Digital I/O.                                                  |  |  |  |

| RE7/CCP2<br>RE7<br>CCP2 <sup>(2)</sup>                                                                                                                                                                                       | 59         | I/O<br>I/O | ST<br>ST  | Digital I/O.<br>Capture 2 input/Compare 2 output/PWM2 output. |  |  |  |

| Legend:TTL= TTL compatible inputCMOS= CMOS compatible input or outputST= Schmitt Trigger input with CMOS levelsAnalog= Analog inputI= InputO= OutputP= PowerOD= Open-Drain (no P diode to VDD) $I^2 C^{TM} = I^2 C/SMBus$ II |            |            |           |                                                               |  |  |  |

# TABLE 1-3: PIC18F6XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

| Pin Name                                                                               | Pin Number      | Pin               | Buffer           | Description                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------------|-----------------|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Fill Naille                                                                            | TQFP            | Туре              | Туре             | Description                                                                                                          |  |  |  |

| RD0/AD0/PSP0<br>RD0<br>AD0<br>PSP0                                                     | 72              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | PORTD is a bidirectional I/O port.<br>Digital I/O.<br>External memory address/data 0.<br>Parallel Slave Port data.   |  |  |  |

| RD1/AD1/PSP1<br>RD1<br>AD1<br>PSP1                                                     | 69              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 1.<br>Parallel Slave Port data.                                         |  |  |  |

| RD2/AD2/PSP2<br>RD2<br>AD2<br>PSP2                                                     | 68              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 2.<br>Parallel Slave Port data.                                         |  |  |  |

| RD3/AD3/PSP3<br>RD3<br>AD3<br>PSP3                                                     | 67              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 3.<br>Parallel Slave Port data.                                         |  |  |  |

| RD4/AD4/PSP4<br>RD4<br>AD4<br>PSP4                                                     | 66              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 4.<br>Parallel Slave Port data.                                         |  |  |  |

| RD5/AD5/PSP5<br>RD5<br>AD5<br>PSP5                                                     | 65              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 5.<br>Parallel Slave Port data.                                         |  |  |  |

| RD6/AD6/PSP6<br>RD6<br>AD6<br>PSP6                                                     | 64              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 6.<br>Parallel Slave Port data.                                         |  |  |  |

| RD7/AD7/PSP7<br>RD7<br>AD7<br>PSP7                                                     | 63              | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>External memory address/data 7.<br>Parallel Slave Port data.                                         |  |  |  |

| Legend: TTL = TTL cc<br>ST = Schmit<br>I = Input<br>P = Power<br>$I^2C^{TM} = I^2C/SM$ | t Trigger input | with Cl           | MOS leve         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |  |

# TABLE 1-4: PIC18F8XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared (80-pin devices, Extended Microcontroller mode only).

2: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

**3:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

| Din Norre                                            | Pin Number           | Pin        | Buffer    | Description                                                                       |

|------------------------------------------------------|----------------------|------------|-----------|-----------------------------------------------------------------------------------|

| Pin Name                                             | TQFP                 | Туре       | Туре      | Description                                                                       |

|                                                      |                      |            |           | PORTE is a bidirectional I/O port.                                                |

| RE0/RD/AD8                                           | 4                    |            |           |                                                                                   |

| RE0<br>RD                                            |                      | 1/O        | ST<br>TTL | Digital I/O.<br>Read control for Parallel Slave Port.                             |

| AD8                                                  |                      | 1/O        | TTL       | External memory address/data 8.                                                   |

| RE1/WR/AD9                                           | 3                    |            |           |                                                                                   |

| RE1                                                  | Ū                    | I/O        | ST        | Digital I/O.                                                                      |

| WR                                                   |                      |            |           | Write control for Parallel Slave Port.                                            |

| AD9                                                  |                      | I/O        | TTL       | External memory address/data 9.                                                   |

| RE2/AD10/CS<br>RE2                                   | 78                   | I/O        | ST        | Digital I/O.                                                                      |

| AD10                                                 |                      | 1/O        | TTL       | External memory address/data 10.                                                  |

| CS                                                   |                      | I          | TTL       | Chip select control for Parallel Slave Port.                                      |

| RE3/AD11                                             | 77                   |            |           |                                                                                   |

| RE3<br>AD11                                          |                      | 1/O<br>1/O | ST<br>TTL | Digital I/O.<br>External memory address/data 11.                                  |

| RE4/AD12                                             |                      | 1/0        | 115       |                                                                                   |

| RE4/AD12<br>RE4                                      | 76                   | I/O        | ST        | Digital I/O.                                                                      |

| AD12                                                 |                      | I/O        | TTL       | External memory address/data 12.                                                  |

| RE5/AD13                                             | 75                   |            |           |                                                                                   |

| RE5                                                  |                      | I/O        | ST        | Digital I/O.                                                                      |

| AD13                                                 |                      | I/O        | TTL       | External memory address/data 13.                                                  |

| RE6/AD14<br>RE6                                      | 74                   | I/O        | ST        | Digital I/O.                                                                      |

| AD14                                                 |                      | 1/O        | TTL       | External memory address/data 14.                                                  |

| RE7/AD15/CCP2                                        | 73                   |            |           |                                                                                   |

| RE7                                                  |                      | I/O        | ST        | Digital I/O.                                                                      |

| AD15<br>CCP2 <sup>(3)</sup>                          |                      | 1/O<br>1/O | TTL<br>ST | External memory address/data 15.<br>Capture 2 input/Compare 2 output/PWM2 output. |

| Legend: TTL = TTL co                                 | I<br>pmpatible input | 10         | 01        | CMOS = CMOS compatible input or output                                            |

| ST = Schmi                                           | tt Trigger input     | with C     | MOS leve  |                                                                                   |

| I = Input                                            |                      |            |           | O = Output                                                                        |

| P = Power<br>I <sup>2</sup> C™ = I <sup>2</sup> C/SN |                      |            |           | OD = Open-Drain (no P diode to VDD)                                               |

### TABLE 1-4: PIC18F8XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared (80-pin devices, Extended Microcontroller mode only).

2: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

3: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

| Pin Name                               | Pin Number                          | Pin           | Buffer                 | Description                                                                   |

|----------------------------------------|-------------------------------------|---------------|------------------------|-------------------------------------------------------------------------------|

| Pin Name                               | TQFP                                | Туре          | Туре                   | Description                                                                   |

|                                        |                                     |               |                        | PORTF is a bidirectional I/O port.                                            |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 23                                  | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                       |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 18                                  | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                       |

| RF3/AN8<br>RF3<br>AN8                  | 17                                  | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 8.                                               |

| RF4/AN9<br>RF4<br>AN9                  | 16                                  | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 9.                                               |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 15                                  | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.      |

| RF6/AN11<br>RF6<br>AN11                | 14                                  | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 11.                                              |

| RF7/AN5/SS<br>RF7<br>AN5<br>SS         | 13                                  | I/O<br>O<br>I | ST<br>Analog<br>TTL    | Digital I/O.<br>Analog Input 5.<br>SPI slave select input.                    |

|                                        | ompatible input<br>tt Trigger input | with C        | MOS leve               | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output |

#### **TABLE 1-4**: PIC18F8XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

= Power Ρ

$I^2C^{TM} = I^2C/SMBus$

Note 1: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared (80-pin devices, Extended Microcontroller mode only).

OD

2: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

3: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

= Open-Drain (no P diode to VDD)

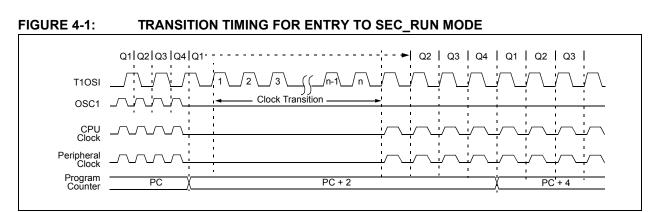

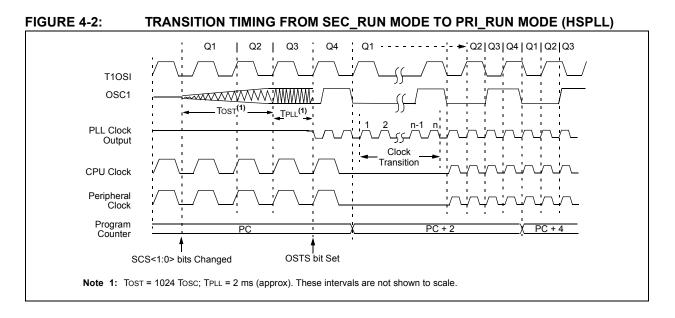

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS<1:0> bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result. On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

# 4.3 Sleep Mode

The power-managed Sleep mode is identical to the legacy Sleep mode offered in all other PIC microcontrollers. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

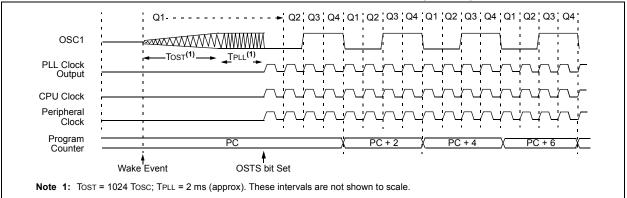

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator if either the Two-Speed Start-up or the Fail-Safe Clock Monitor is enabled (see **Section 23.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

### 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 26-12) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

FIGURE 4-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

| Q1 Q2 Q3 Q4 Q         |          |        | - :    | -;     |        |          | ;      | i <del>i</del> - |          |

|-----------------------|----------|--------|--------|--------|--------|----------|--------|------------------|----------|

|                       |          | 1<br>1 | 1      | 1      | 1<br>1 | 1        | 1<br>1 | · ·              |          |

|                       |          | 1      | 1      | 1      | 1      | 1        | 1      |                  |          |

|                       | <br>     | 1      |        | 1      | 1<br>T | 1<br>T   | 1      | 1 I<br>T I       | !        |

| Peripheral            |          | 1      | 1<br>1 | 1<br>1 | 1      | 1        | 1<br>1 |                  | ļ        |

|                       |          | 1      |        | 1      | 1      | r<br>1   | 1      | · · ·            |          |

| Sleep /               | <u> </u> |        |        |        |        | <u>1</u> | ı      | <u> </u>         | /        |

|                       |          | i      |        | 1      |        | 1        | 1      | · ·              |          |

| Program<br>Counter PC | PC + 2   |        |        |        |        |          |        |                  | _►<br>_► |

# PIC18F85J11 FAMILY

| TABLE 5-2:          | INITIALIZA                  | GISTERS (CONTINU | ED)                                |                                                                                     |                                 |  |

|---------------------|-----------------------------|------------------|------------------------------------|-------------------------------------------------------------------------------------|---------------------------------|--|

| Register            | Register Applicable Devices |                  | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>S <u>tac</u> k Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| FSR1H               | PIC18F6XJ11                 | PIC18F8XJ11      | xxxx                               | uuuu                                                                                | uuuu                            |  |

| FSR1L               | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| BSR                 | PIC18F6XJ11                 | PIC18F8XJ11      | 0000                               | 0000                                                                                | uuuu                            |  |

| INDF2               | PIC18F6XJ11                 | PIC18F8XJ11      | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTINC2            | PIC18F6XJ11                 | PIC18F8XJ11      | N/A                                | N/A                                                                                 | N/A                             |  |

| POSTDEC2            | PIC18F6XJ11                 | PIC18F8XJ11      | N/A                                | N/A                                                                                 | N/A                             |  |

| PREINC2             | PIC18F6XJ11                 | PIC18F8XJ11      | N/A                                | N/A                                                                                 | N/A                             |  |

| PLUSW2              | PIC18F6XJ11                 | PIC18F8XJ11      | N/A                                | N/A                                                                                 | N/A                             |  |

| FSR2H               | PIC18F6XJ11                 | PIC18F8XJ11      | xxxx                               | uuuu                                                                                | uuuu                            |  |

| FSR2L               | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| STATUS              | PIC18F6XJ11                 | PIC18F8XJ11      | x xxxx                             | u uuuu                                                                              | u uuuu                          |  |

| TMR0H               | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| TMR0L               | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| TOCON               | PIC18F6XJ11                 | PIC18F8XJ11      | 1111 1111                          | 1111 1111                                                                           | uuuu uuuu                       |  |

| OSCCON              | PIC18F6XJ11                 | PIC18F8XJ11      | 0100 q000                          | 0100 q000                                                                           | uuuu quuu                       |  |

| WDTCON              | PIC18F6XJ11                 | PIC18F8XJ11      | 00                                 | 00                                                                                  | uu                              |  |

| RCON <sup>(4)</sup> | PIC18F6XJ11                 | PIC18F8XJ11      | 0-11 11q0                          | 0-uq qquu                                                                           | u-uu qquu                       |  |

| TMR1H               | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| TMR1L               | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | uuuu uuuu                       |  |

| T1CON               | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | u0uu uuuu                                                                           | uuuu uuuu                       |  |

| TMR2                | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| PR2                 | PIC18F6XJ11                 | PIC18F8XJ11      | 1111 1111                          | 1111 1111                                                                           | 1111 1111                       |  |

| T2CON               | PIC18F6XJ11                 | PIC18F8XJ11      | -000 0000                          | -000 0000                                                                           | -uuu uuuu                       |  |

| SSPBUF              | PIC18F6XJ11                 | PIC18F8XJ11      | XXXX XXXX                          | uuuu uuuu                                                                           | սսսս սսսս                       |  |

| SSPADD              | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| SSPSTAT             | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

| SSPCON1             | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | սսսս սսսս                       |  |

| SSPCON2             | PIC18F6XJ11                 | PIC18F8XJ11      | 0000 0000                          | 0000 0000                                                                           | uuuu uuuu                       |  |

# TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

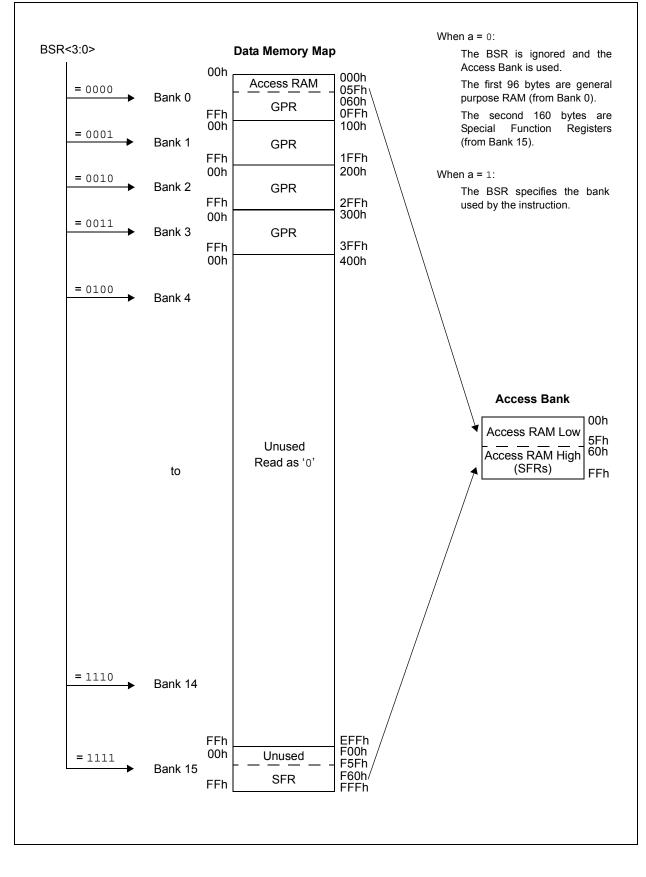

# FIGURE 6-7: DATA MEMORY MAP FOR PIC18FX3J11/X4J11 DEVICES

# 8.3 Wait States

While it may be assumed that external memory devices will operate at the microcontroller clock rate, this is often not the case. In fact, many devices require longer times to write or retrieve data than the time allowed by the execution of table read or table write operations.

To compensate for this, the external memory bus can be configured to add a fixed delay to each table operation using the bus. Wait states are enabled by setting the WAIT Configuration bit. When enabled, the amount of delay is set by the WAIT<1:0> bits (MEMCON<5:4>). The delay is based on multiples of microcontroller instruction cycle time and are added following the instruction cycle when the table operation is executed. The range is from no delay to 3 Tcy (default value).

# 8.4 Port Pin Weak Pull-ups

With the exception of the upper address lines, A<19:16>, the pins associated with the external memory bus are equipped with weak pull-ups. The pull-ups are controlled by the upper three bits of the PORTG register. They are named RDPU, REPU and RJPU and control pull-ups on PORTD, PORTE and PORTJ, respectively. Setting one of these bits enables the corresponding pull-ups for that port. All pull-ups are disabled by default on all device Resets.

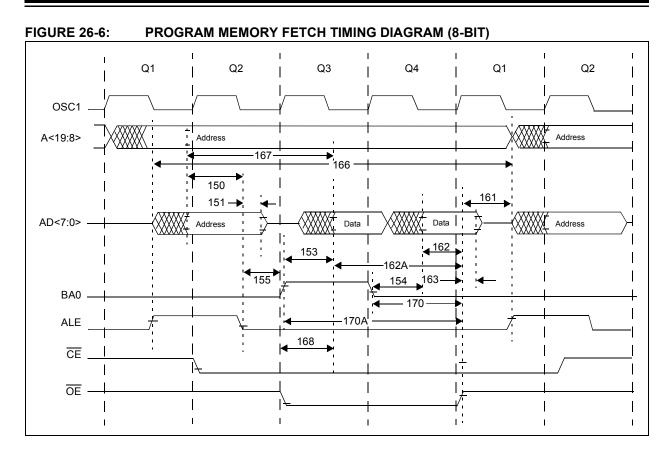

# 8.5 Program Memory Modes and the External Memory Bus

The PIC18F85J11 family of devices are capable of operating in one of two Program Memory modes, using combinations of on-chip and external program memory. The functions of the multiplexed port pins depend on the Program Memory mode selected, as well as the setting of the EBDIS bit.

In **Microcontroller Mode**, the bus is not active and the pins have their port functions only. Writes to the MEMCOM register are not permitted. The Reset value of EBDIS ('0') is ignored and EMB pins behave as I/O ports.

In **Extended Microcontroller Mode**, the external program memory bus shares I/O port functions on the pins. When the device is fetching or doing table read/table write operations on the external program memory space, the pins will have the external bus function.

If the device is fetching and accessing internal program memory locations only, the EBDIS control bit will change the pins from external memory to I/O port functions. When EBDIS = 0, the pins function as the external bus. When EBDIS = 1, the pins function as I/O ports.

If the device fetches or accesses external memory while EBDIS = 1, the pins will switch to the external bus. If the EBDIS bit is set by a program executing from external memory, the action of setting the bit will be delayed until the program branches into the internal memory. At that time, the pins will change from external bus to I/O ports.

If the device is executing out of internal memory when EBDIS = 0, the memory bus address/data and control pins will not be active. They will go to a state where the active address/data pins are tri-state; the  $\overline{CE}$ ,  $\overline{OE}$ ,  $\overline{WRH}$ ,  $\overline{WRL}$ ,  $\overline{UB}$  and  $\overline{LB}$  signals are '1' and ALE and BA0 are '0'. Note that only those pins associated with the current address width are forced to tri-state; the other pins continue to function as I/O. In the case of 16-bit address width, for example, only AD<15:0> (PORTD and PORTE) are affected; A<19:16> (PORTH<3:0>) continue to function as I/O.

In all External Memory modes, the bus takes priority over any other peripherals that may share pins with it. This includes the Parallel Slave Port and serial communication modules which would otherwise take priority over the I/O port.

# 8.6 16-Bit Data Width Modes

In 16-Bit Data Width mode, the external memory interface can be connected to external memories in three different configurations:

- 16-Bit Byte Write

- 16-Bit Word Write

- 16-Bit Byte Select

The configuration to be used is determined by the WM<1:0> bits in the MEMCON register (MEMCON<1:0>). These three different configurations allow the designer maximum flexibility in using both 8-bit and 16-bit devices with 16-bit data.

For all 16-Bit Data Width modes, the Address Latch Enable (ALE) pin indicates that the address bits, AD<15:0>, are available on the external memory interface bus. Following the address latch, the Output Enable signal ( $\overline{OE}$ ) will enable both bytes of program memory at once to form a 16-bit instruction word. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing. It is inactive (asserted high) whenever the device is in Sleep mode.

In Byte Select mode, JEDEC standard Flash memories will require BA0 for the byte address line and one I/O line to select between Byte and Word mode. The other 16-Bit Data Width modes do not need BA0. JEDEC standard static RAM memories will use the UB or LB signals for byte selection.

| Pin Name    | Function            | TRIS<br>Setting | I/O | I/O<br>Type      | Description                                                                              |

|-------------|---------------------|-----------------|-----|------------------|------------------------------------------------------------------------------------------|

| RC0/T1OSO/  | RC0                 | 0               | 0   | DIG              | LATC<0> data output.                                                                     |

| T13CKI      |                     | 1               | I   | ST               | PORTC<0> data input.                                                                     |

|             | T10SO               | x               | 0   | ANA              | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O.  |

|             | T13CKI              | 1               | I   | ST               | Timer1/Timer3 counter input.                                                             |

| RC1/T1OSI/  | RC1                 | 0               | 0   | DIG              | LATC<1> data output.                                                                     |

| CCP2        |                     | 1               | Ι   | ST               | PORTC<1> data input.                                                                     |

|             | T10SI               | x               | Ι   | ANA              | Timer1 oscillator input; enabled when Timer1 oscillator enabled. Disables digital I/O.   |

|             | CCP2 <sup>(1)</sup> | 0               | 0   | DIG              | CCP2 compare output and CCP2 PWM output; takes priority over port data.                  |

|             |                     | 1               | Ι   | ST               | CCP2 capture input.                                                                      |

| RC2/CCP1    | RC2                 | 0               | 0   | DIG              | LATC<2> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<2> data input.                                                                     |

|             | CCP1                | 0               | 0   | DIG              | CCP1 compare output and CCP1 PWM output; takes priority over port data.                  |

|             |                     | 1               | Ι   | ST               | CCP1 capture input.                                                                      |

| RC3/SCK/SCL | RC3                 | 0               | 0   | DIG              | LATC<3> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<3> data input.                                                                     |

|             | SCK                 | 0               | 0   | DIG              | SPI clock output (MSSP module); takes priority over port data.                           |

|             |                     | 1               |     | ST               | SPI clock input (MSSP module).                                                           |

|             | SCL                 | 0               | 0   | DIG              | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data. |

|             |                     | 1               | Ι   | I <sup>2</sup> C | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting.        |

| RC4/SDI/SDA | RC4                 | 0               | 0   | DIG              | LATC<4> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<4> data input.                                                                     |

|             | SDI                 | 1               | Ι   | ST               | SPI data input (MSSP module).                                                            |

|             | SDA                 | 1               | 0   | DIG              | I <sup>2</sup> C data output (MSSP module); takes priority over port data.               |

|             |                     | 1               | Ι   | l <sup>2</sup> C | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.         |

| RC5/SDO     | RC5                 | 0               | 0   | DIG              | LATC<5> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<5> data input.                                                                     |

|             | SDO                 | 0               | 0   | DIG              | SPI data output (MSSP module); takes priority over port data.                            |

| RC6/TX1/CK1 | RC6                 | 0               | 0   | DIG              | LATC<6> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<6> data input.                                                                     |

|             | TX1                 | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data            |

|             | CK1                 | 1               | 0   | DIG              | Synchronous serial data input (EUSART module). User must configure as an input.          |

|             |                     | 1               | Ι   | ST               | Synchronous serial clock input (EUSART module).                                          |

| RC7/RX1/DT1 | RC7                 | 0               | 0   | DIG              | LATC<7> data output.                                                                     |

|             |                     | 1               | Ι   | ST               | PORTC<7> data input.                                                                     |

|             | RX1                 | 1               | I   | ST               | Asynchronous serial receive data input (EUSART module).                                  |

|             | DT1                 | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data.           |

|             |                     | 1               | —   | ST               | Synchronous serial data input (EUSART module). User must configure as an input.          |

TABLE 11-7:PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for CCP2 when CCP2MX Configuration bit is set.

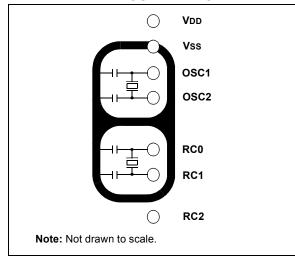

### 13.3.2 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 13-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator (such as the CCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as shown in Figure 13-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

#### FIGURE 13-4: OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

# 13.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# 13.5 Resetting Timer1 Using the CCPx Special Event Trigger

If CCP1 or CCP2 is configured to use Timer1 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

| Note: | The Special Event Triggers from the CCPx |

|-------|------------------------------------------|

|       | module will not set the TMR1IF interrupt |

|       | flag bit (PIR1<0>).                      |

# 13.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 13.3 "Timer1 Oscillator"** above) gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 13-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine which increments the seconds counter by one. Additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

# 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

# 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

# 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

# 15.5 Resetting Timer3 Using the CCPx Special Event Trigger

If CCP1 or CCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCPx module, the write will take precedence.

**Note:** The Special Event Triggers from the CCPx module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name    | Bit 7                        | Bit 6         | Bit 5    | Bit 4   | Bit 3   | Bit 2         | Bit 1  | Bit 0  | Reset<br>Values<br>on page |  |  |

|---------|------------------------------|---------------|----------|---------|---------|---------------|--------|--------|----------------------------|--|--|

| INTCON  | GIE/GIEH                     | PEIE/GIEL     | TMR0IE   | INT0IE  | RBIE    | TMR0IF        | INT0IF | RBIF   | 57                         |  |  |

| PIR2    | OSCFIF                       | CMIF          | _        | —       | BCLIF   | LVDIF         | TMR3IF | _      | 59                         |  |  |

| PIE2    | OSCFIE                       | CMIE          | _        | —       | BCLIE   | LVDIE         | TMR3IE | _      | 59                         |  |  |

| IPR2    | OSCFIP                       | CMIP          | _        | —       | BCLIP   | LVDIP         | TMR3IP | —      | 59                         |  |  |

| TMR3L   | R3L Timer3 Register Low Byte |               |          |         |         |               |        |        |                            |  |  |

| TMR3H   | Timer3 Reg                   | gister High B | yte      |         |         |               |        |        | 59                         |  |  |

| T1CON   | RD16                         | T1RUN         | T1CKPS1  | T1CKPS0 | T10SCEN | T1SYNC        | TMR1CS | TMR10N | 58                         |  |  |

| T3CON   | RD16                         | T3CCP2        | T3CKPS1  | T3CKPS0 | T3CCP1  | <b>T3SYNC</b> | TMR3CS | TMR3ON | 59                         |  |  |

| Lawards |                              |               | 1 (1) 01 |         |         |               | 0 1 1  |        |                            |  |  |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

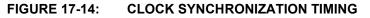

# 17.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has

already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2$ C bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 17-14).

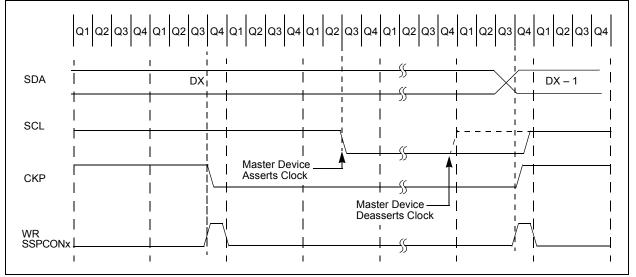

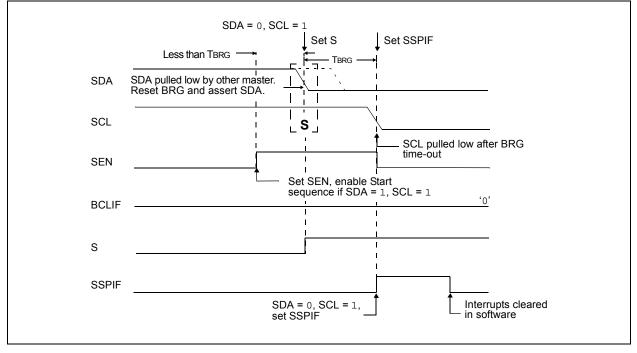

# 17.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-Bit Addressing mode or the default first address in 10-Bit Addressing mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-Bit Addressing mode) or eight bits of data (7-Bit Addressing mode).

# 17.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 17-22: REPEATED START CONDITION WAVEFORM

# 18.2 EUSART Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON1<3>) selects 16-bit mode.

The SPBRGH1:SPBRG1 register pair controls the period of a free-running timer. In Asynchronous mode, BRGH (TXSTA1<2>) and BRG16 (BAUDCON1<3>) bits also control the baud rate. In Synchronous mode, BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different EUSART modes that only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGH1:SPBRG1 registers can be calculated using the formulas in Table 18-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 18-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 18-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH1:SPBRG1 registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate. When operated in the Synchronous mode, SPBRGH:SPBRG values of 0000h and 0001h are not supported. In the Asynchronous mode, all BRG values may be used.

# 18.2.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG1 register pair.

# 18.2.2 SAMPLING

The data on the RX1 pin is sampled three times by a majority detect circuit to determine if a high or low level is present at the RX1 pin.

| C    | Configuration Bits |      | BRG/EUSART Mode     | Baud Rate Formula   |  |  |

|------|--------------------|------|---------------------|---------------------|--|--|

| SYNC | BRG16              | BRGH | BRG/EUSART Mode     | Baud Rate Formula   |  |  |

| 0    | 0                  | 0    | 8-Bit/Asynchronous  | Fosc/[64 (n + 1)]   |  |  |

| 0    | 0                  | 1    | 8-Bit/Asynchronous  | $F_{000}/[16(n+1)]$ |  |  |

| 0    | 1                  | 0    | 16-Bit/Asynchronous | Fosc/[16 (n + 1)]   |  |  |

| 0    | 1                  | 1    | 16-Bit/Asynchronous |                     |  |  |

| 1    | 0                  | x    | 8-Bit/Synchronous   | Fosc/[4 (n + 1)]    |  |  |

| 1    | 1                  | x    | 16-Bit/Synchronous  |                     |  |  |

TABLE 18-1: BAUD RATE FORMULAS

Legend: x = Don't care, n = Value of SPBRGH1:SPBRG1 register pair

# 21.0 COMPARATOR MODULE

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RF1 through RF6, as well as the on-chip voltage reference (see Section 22.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 21-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 21-1.

### REGISTER 21-1: CMCON: COMPARATOR MODULE CONTROL REGISTER

| R-0   | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| C2OUT | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                                                         |                    |                                    |                    |  |  |

|-----------------------------------------------------------------|--------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit                               |                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at PO                                                | c '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

|                                                                 |                    |                                    |                    |  |  |

|                                                                 |                    |                                    |                    |  |  |

| bit 7 <b>C2OUT</b> : Comparator 2 Output bit<br>When C2INV = 0: |                    |                                    |                    |  |  |

|         | When $C2INV = 0$ :<br>1 = C2 VIN+ > C2 VIN-<br>0 = C2 VIN+ < C2 VIN-                             |

|---------|--------------------------------------------------------------------------------------------------|

|         | $\frac{When C2INV = 1:}{1 = C2 VIN+ < C2 VIN-}$<br>0 = C2 VIN+ > C2 VIN-                         |

| bit 6   | C1OUT: Comparator 1 Output bit                                                                   |

|         | $\frac{\text{When C1INV} = 0:}{1 = C1 \text{VIN} + > C1 \text{VIN}}$<br>0 = C1 VIN+ < C1 VIN-    |

|         | $\frac{\text{When C1INV} = 1:}{1 = C1 \text{ VIN} + < C1 \text{ VIN}}$<br>0 = C1 VIN + > C1 VIN- |

| bit 5   | C2INV: Comparator 2 Output Inversion bit                                                         |

|         | <ul> <li>1 = C2 output is inverted</li> <li>0 = C2 output is not inverted</li> </ul>             |

| bit 4   | <b>C1INV</b> : Comparator 1 Output Inversion bit<br>1 = C1 output is inverted                    |

|         | 0 = C1 output is not inverted                                                                    |

| bit 3   | CIS: Comparator Input Switch bit                                                                 |

|         | When CM<2:0> = 110:<br>1 = C1 VIN- connects to RF5/AN10/CVREF,<br>C2 VIN- connects to RF3/AN8    |

|         | 0 = C1 VIN- connects to RF6/AN11,<br>C2 VIN- connects to RF4/AN9                                 |

| bit 2-0 | CM<2:0>: Comparator Mode bits                                                                    |

|         | Figure 21-1 shows the Comparator modes and the CM<2:0> bit settings.                             |

|         |                                                                                                  |

# PIC18F85J11 FAMILY

| LFSF                                            | २              | Load FSR                                                           | Load FSR                                                                             |                            |                                         |  |  |  |

|-------------------------------------------------|----------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------|-----------------------------------------|--|--|--|

| Syntax:                                         |                | LFSR f, k                                                          | LFSR f, k                                                                            |                            |                                         |  |  |  |

| Operands:                                       |                | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 4095 \end{array}$                 |                            |                                         |  |  |  |

| Oper                                            | ation:         | $k\toFSRf$                                                         | $k \rightarrow FSRf$                                                                 |                            |                                         |  |  |  |

| Statu                                           | s Affected:    | None                                                               | None                                                                                 |                            |                                         |  |  |  |

| Encoding:                                       |                | 1110<br>1111                                                       | 1110<br>0000                                                                         | 00ff<br>k <sub>7</sub> kkk | k <sub>11</sub> kkk<br>kkkk             |  |  |  |

| Description:                                    |                |                                                                    | The 12-bit literal 'k' is loaded into the<br>File Select Register pointed to by 'f'. |                            |                                         |  |  |  |

| Words:                                          |                | 2                                                                  |                                                                                      |                            |                                         |  |  |  |

| Cycle                                           | es:            | 2                                                                  | 2                                                                                    |                            |                                         |  |  |  |

| QC                                              | ycle Activity: |                                                                    |                                                                                      |                            |                                         |  |  |  |

|                                                 | Q1             | Q2                                                                 | Q3                                                                                   |                            | Q4                                      |  |  |  |

|                                                 | Decode         | Read literal<br>'k' MSB                                            | Proce<br>Data                                                                        |                            | Write<br>literal 'k'<br>MSB to<br>FSRfH |  |  |  |

|                                                 | Decode         | Read literal<br>'k' LSB                                            | Proce<br>Data                                                                        |                            | /rite literal<br>to FSRfL               |  |  |  |

| <u>Exan</u>                                     | nple:          | LFSR 2,                                                            | 3ABh                                                                                 |                            |                                         |  |  |  |

| After Instruction<br>FSR2H = 03h<br>FSR2L = ABh |                |                                                                    |                                                                                      |                            |                                         |  |  |  |

| MOVF               | Move f                                                                     |                                                                                                                                                                                                                                                                                          |            |  |  |  |

|--------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Syntax:            | MOVF f {,d                                                                 | {,a}}                                                                                                                                                                                                                                                                                    |            |  |  |  |

| Operands:          | $0 \leq f \leq 255$                                                        |                                                                                                                                                                                                                                                                                          |            |  |  |  |

|                    | d ∈ [0, 1]                                                                 |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Operation          | a ∈ [0, 1]<br>f → dest                                                     |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Operation:         |                                                                            |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Status Affected:   |                                                                            | N, Z                                                                                                                                                                                                                                                                                     |            |  |  |  |

| Encoding:          | 0101                                                                       | 00da ffi                                                                                                                                                                                                                                                                                 |            |  |  |  |

| Description:       | a destinatio<br>status of 'd'<br>placed in W<br>placed back<br>can be anyw | The contents of register 'f' are moved to<br>a destination dependent upon the<br>status of 'd'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. Location 'f'<br>can be anywhere in the<br>256-byte bank.                       |            |  |  |  |

|                    |                                                                            | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.                                                                                                                                                                                 |            |  |  |  |

|                    | set is enabl<br>in Indexed I<br>mode when<br>Section 25<br>Bit-Oriente     | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |            |  |  |  |

| Words:             | 1                                                                          |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Cycles:            | 1                                                                          |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Q Cycle Activity:  |                                                                            |                                                                                                                                                                                                                                                                                          |            |  |  |  |

| Q1                 | Q2                                                                         | Q3                                                                                                                                                                                                                                                                                       | Q4         |  |  |  |

| Decode             | Read                                                                       | Process<br>Data                                                                                                                                                                                                                                                                          | Write<br>W |  |  |  |