Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 512 x 8                                                                         |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 115°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-VQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha0e14a-mzt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 15.13.17 Peripheral Identification 2

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID2<br>0x1FE8<br>0x00000009<br>- |    |    |      |              |    |    |

|--------|-----------------------------------------|-----------------------------------|----|----|------|--------------|----|----|

| Bit    | 31                                      | 30                                | 29 | 28 | 27   | 26           | 25 | 24 |

|        |                                         |                                   |    |    |      |              |    |    |

| Access |                                         |                                   |    |    |      |              |    |    |

| Reset  |                                         |                                   |    |    |      |              |    |    |

| Bit    | 23                                      | 22                                | 21 | 20 | 19   | 18           | 17 | 16 |

|        |                                         |                                   |    |    |      |              |    |    |

| Access |                                         |                                   |    |    |      |              |    |    |

| Reset  |                                         |                                   |    |    |      |              |    |    |

| Bit    | 15                                      | 14                                | 13 | 12 | 11   | 10           | 9  | 8  |

|        |                                         |                                   |    |    |      |              |    |    |

| Access |                                         |                                   |    |    |      |              |    |    |

| Reset  |                                         |                                   |    |    |      |              |    |    |

| Bit    | 7                                       | 6                                 | 5  | 4  | 3    | 2            | 1  | 0  |

|        |                                         | REVISION[3:0]                     |    |    | JEPU | JEPIDCH[2:0] |    |    |

| Access | R                                       | R                                 | R  | R  | R    | R            | R  | R  |

| Reset  | 0                                       | 0                                 | 0  | 0  | 1    | 0            | 0  | 1  |

#### Bits 7:4 – REVISION[3:0] Revision Number

Revision of the peripheral. Starts at 0x0 and increments by one at both major and minor revisions.

#### Bit 3 – JEPU JEP-106 Identity Code is used

This bit will always return one when read, indicating that JEP-106 code is used.

#### Bits 2:0 – JEPIDCH[2:0] JEP-106 Identity Code High

These bits will always return 0x1 when read, (JEP-106 identity code is 0x1F).

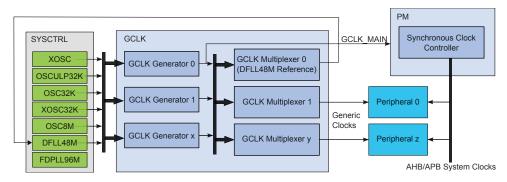

# 16. Clock System

This chapter summarizes the clock distribution and terminology in the SAMHA0/1 device. It will not explain every detail of its configuration. For in-depth documentation, see the respective peripherals descriptions and the *Generic Clock* documentation.

#### **Related Links**

GCLK - Generic Clock Controller

### 16.1 Clock Distribution

#### Figure 16-1. Clock distribution

The clock system on the SAMHA0/1 consists of:

- Clock sources, controlled by SYSCTRL

- A clock source provides a time base that is used by other components, such as Generic Clock Generators. Example clock sources are the internal 8MHz oscillator (OSC8M), External crystal oscillator (XOSC) and the Digital frequency locked loop (DFLL48M).

- Generic Clock Controller (GCLK) which controls the clock distribution system, made up of:

- Generic Clock Generators: These are programmable prescalers that can use any of the system clock sources as a time base. The Generic Clock Generator 0 generates the clock signal GCLK\_MAIN, which is used by the Power Manager, which in turn generates synchronous clocks.

- *Generic Clocks:* These are clock signals generated by Generic Clock Generators and output by the Generic Clock Multiplexer, and serve as clocks for the peripherals of the system. Multiple instances of a peripheral will typically have a separate Generic Clock for each instance. Generic Clock 0 serves as the clock source for the DFLL48M clock input (when multiplying another clock source).

- Power Manager (PM)

- The PM generates and controls the synchronous clocks on the system. This includes the CPU, bus clocks (APB, AHB) as well as the synchronous (to the CPU) user interfaces of the peripherals. It contains clock masks that can turn on/off the user interface of a peripheral as well as prescalers for the CPU and bus clocks.

The next figure shows an example where SERCOM0 is clocked by the DFLL48M in open loop mode. The DFLL48M is enabled, the Generic Clock Generator 1 uses the DFLL48M as its clock source and feeds into Peripheral Channel 20. The Generic Clock 20, also called GCLK\_SERCOM0\_CORE, is connected to

The oscillator is disabled by writing a zero to the Enable bit (XOSC32K.ENABLE) in the 32kHz External Crystal Oscillator Control register while keeping the other bits unchanged. Writing to the XOSC32K.ENABLE bit while writing to other bits may result in unpredictable behavior. The oscillator remains enabled in all sleep modes if it has been enabled beforehand. The start-up time of the 32kHz External Crystal Oscillator is selected by writing to the Oscillator Start-Up Time bit group (XOSC32K.STARTUP) in the in the 32kHz External Crystal Oscillator Control register. The SYSCTRL masks the oscillator output during the start-up time to ensure that no unstable clock propagates to the digital logic. The 32kHz External Crystal Oscillator Ready bit (PCLKSR.XOSC32KRDY) in the Power and Clock Status register is set when the user-selected startup time is over. An interrupt is generated on a zero-to-one transition of PCLKSR.XOSC32KRDY if the 32kHz External Crystal Oscillator Ready bit (INTENSET.XOSC32KRDY) in the Interrupt Enable Set Register is set.

As a crystal oscillator usually requires a very long start-up time (up to one second), the 32kHz External Crystal Oscillator will keep running across resets, except for power-on reset (POR).

XOSC32K can provide two clock outputs when connected to a crystal. The XOSC32K has a 32.768kHz output enabled by writing a one to the 32kHz External Crystal Oscillator 32kHz Output Enable bit (XOSC32K.EN32K) in the 32kHz External Crystal Oscillator Control register. XOSC32K.EN32K is only usable when XIN32 is connected to a crystal, and not when an external digital clock is applied on XIN32.

**Note:** Do not enter standby mode when an oscillator is in start-up: Wait for the OSCxRDY bit in SYSCTRL.PCLKSR register to be set before going into standby mode.

#### **Related Links**

GCLK - Generic Clock Controller

#### 19.6.4 32kHz Internal Oscillator (OSC32K) Operation

The OSC32K provides a tunable, low-speed and low-power clock source.

The OSC32K can be used as a source for the generic clock generators, as described in the *GCLK* – *Generic Clock Controller*.

The OSC32K is disabled by default. The OSC32K is enabled by writing a one to the 32kHz Internal Oscillator Enable bit (OSC32K.ENABLE) in the 32kHz Internal Oscillator Control register. It is disabled by writing a zero to OSC32K.ENABLE. The OSC32K has a 32.768kHz output enabled by writing a one to the 32kHz Internal Oscillator 32kHz Output Enable bit (OSC32K.EN32K).

The frequency of the OSC32K oscillator is controlled by the value in the 32kHz Internal Oscillator Calibration bits (OSC32K.CALIB) in the 32kHz Internal Oscillator Control register. The OSC32K.CALIB value must be written by the user. Flash Factory Calibration values are stored in the NVM Software Calibration Area (refer to *NVM Software Calibration Area Mapping*). When writing to the Calibration bits, the user must wait for the PCLKSR.OSC32KRDY bit to go high before the value is committed to the oscillator.

#### **Related Links**

GCLK - Generic Clock Controller NVM Software Calibration Area Mapping

### 19.6.5 32kHz Ultra Low Power Internal Oscillator (OSCULP32K) Operation

The OSCULP32K provides a tunable, low-speed and ultra-low-power clock source. The OSCULP32K is factory-calibrated under typical voltage and temperature conditions. The OSCULP32K should be preferred to the OSC32K whenever the power requirements are prevalent over frequency stability and accuracy.

# ATSAMHAXEXXA SYSCTRL – System Controller

| Offset | Name          | Bit Pos. |          |          |          |         |         |         |             |        |

|--------|---------------|----------|----------|----------|----------|---------|---------|---------|-------------|--------|

| 0x26   |               |          |          |          |          |         |         |         |             |        |

|        | Reserved      |          |          |          |          |         |         |         |             |        |

| 0x27   |               |          |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          |          |          | FINE    | E[7:0]  |         |             |        |

|        |               | 15:8     |          |          | COAR     | SE[5:0] |         |         | FINE        | [9:8]  |

| 0x28   | DFLLVAL       | 23:16    |          |          |          | DIFF    | [7:0]   |         |             |        |

|        |               | 31:24    |          |          |          | DIFF    | [15:8]  |         |             |        |

|        |               | 7:0      |          |          |          | MUL     | .[7:0]  |         |             |        |

|        |               | 15:8     |          |          |          | MUL     | [15:8]  |         |             |        |

| 0x2C   | DFLLMUL       | 23:16    |          |          |          |         | P[7:0]  |         |             |        |

|        |               | 31:24    |          |          | CSTE     | P[5:0]  |         |         | FSTE        | P[9:8] |

| 0x30   | DFLLSYNC      | 7:0      | READREQ  |          |          |         |         |         |             |        |

| 0x31   |               |          |          |          |          |         |         |         |             |        |

|        | Reserved      |          |          |          |          |         |         |         |             |        |

| 0x33   |               |          |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          | RUNSTDBY |          | ACTIC   | DN[1:0] | HYST    | ENABLE      |        |

|        |               | 15:8     |          | PSE      | L[3:0]   |         |         |         | CEN         | MODE   |

| 0x34   | BOD33         | 23:16    |          |          |          |         | LEVE    | L[5:0]  |             |        |

|        |               | 31:24    |          |          |          |         |         |         |             |        |

| 0x38   |               |          |          |          |          |         |         |         |             |        |

|        | Reserved      |          |          |          |          |         |         |         |             |        |

| 0x3B   |               |          |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          | RUNSTDBY |          |         |         |         |             |        |

| 0x3C   | VREG          | 15:8     |          |          | FORCELDO |         |         |         |             |        |

| 0x3E   |               |          |          |          |          |         |         |         |             |        |

|        | Reserved      |          |          |          |          |         |         |         |             |        |

| 0x3F   |               |          |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          |          |          |         |         | BGOUTEN |             |        |

|        |               | 15:8     |          |          |          |         |         |         |             |        |

| 0x40   | VREF          | 23:16    |          |          |          | CALI    | B[7:0]  |         |             |        |

|        |               | 31:24    |          |          |          |         |         |         | CALIB[10:8] |        |

| 0x44   | DPLLCTRLA     | 7:0      | ONDEMAND |          |          |         |         |         | ENABLE      |        |

| 0x45   |               |          |          |          |          |         |         |         |             |        |

|        | Reserved      |          |          |          |          |         |         |         |             |        |

| 0x47   |               |          |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          |          |          | LDR     | [7:0]   |         |             |        |

|        |               | 15:8     |          |          |          |         | -       | LDR[    | [11:8]      |        |

| 0x48   | DPLLRATIO     | 23:16    |          |          |          |         |         | LDRFR   |             |        |

|        |               | 31:24    |          |          |          |         |         |         |             |        |

|        |               | 7:0      |          |          | REFC     | LK[1:0] | WUF     | LPEN    | FILTE       | R[1:0] |

|        |               | 15:8     |          |          |          | LBYPASS |         |         | LTIME[2:0]  |        |

| 0x4C   | DPLLCTRLB     | 23:16    |          |          |          |         | [7:0]   |         | -[]         |        |

|        |               | 31:24    |          |          |          | 211     |         |         | DIV[10:8]   |        |

| 0x50   | DPLLSTATUS    | 7:0      |          |          |          |         | DIV     | ENABLE  | CLKRDY      | LOCK   |

| 0,000  | 5. 220 1/1/00 | 1.0      |          |          |          |         |         |         | SERVET      | 2001   |

# ATSAMHAXEXXA SYSCTRL – System Controller

| PRESC[1:0] | Description |

|------------|-------------|

| 0x0        | 1           |

| 0x1        | 2           |

| 0x2        | 4           |

| 0x3        | 8           |

#### Bit 7 – ONDEMAND On Demand Control

The On Demand operation mode allows an oscillator to be enabled or disabled depending on peripheral clock requests.

In On Demand operation mode, i.e., if the ONDEMAND bit has been previously written to one, the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active if the OSC8M.RUNSTDBY bit is one. If OSC8M.RUNSTDBY is zero, the oscillator is disabled.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

#### Bit 6 – RUNSTDBY Run in Standby

This bit controls how the OSC8M behaves during standby sleep mode:

| Value | Description                                                                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is disabled in standby sleep mode.                                                                                                                                                                                                    |

| 1     | The oscillator is not stopped in standby sleep mode. If OSC8M.ONDEMAND is one, the clock source will be running when a peripheral is requesting the clock. If OSC8M.ONDEMAND is zero, the clock source will always be running in standby sleep mode. |

#### Bit 1 – ENABLE Oscillator Enable

The user must ensure that the OSC8M is fully disabled before enabling it, and that the OSC8M is fully enabled before disabling it by reading OSC8M.ENABLE.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The oscillator is disabled or being enabled. |

| 1     | The oscillator is enabled or being disabled. |

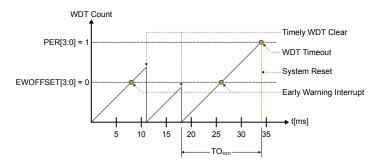

(INTENCLR.EW). If the Early Warning Interrupt is enabled, an interrupt is generated prior to a WDT timeout condition. In Normal mode, the Early Warning Offset bits in the Early Warning Interrupt Control register, EWCTRL.EWOFFSET, define the time when the early warning interrupt occurs. The Normal mode operation is illustrated in the figure Normal-Mode Operation.

#### Figure 20-2. Normal-Mode Operation

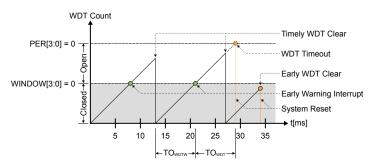

#### 20.6.2.5 Window Mode

In Window mode operation, the WDT uses two different time specifications: the WDT can only be cleared by writing 0xA5 to the CLEAR register *after* the closed window time-out period ( $TO_{WDTW}$ ), during the subsequent Normal time-out period ( $TO_{WDTW}$ ). If the WDT is cleared before the time window opens (before  $TO_{WDTW}$  is over), the WDT will issue a system reset. Both parameters  $TO_{WDTW}$  and  $TO_{WDT}$  are periods in a range from 8ms to 16s, so the total duration of the WDT time-out period is the sum of the two parameters. The closed window period is defined by the Window Period bits in the Configuration register (CONFIG.WINDOW), and the open window period is defined by the Period bits in the Configuration register (CONFIG.PER).

By default, the Early Warning interrupt is disabled. If it is desired, the Early Warning Interrupt Enable bit in the Interrupt Enable register (INTENSET.EW) must be written to '1'. The Early Warning Interrupt is disabled again by writing a '1' to the Early Warning Interrupt bit in the Interrupt Enable Clear (INTENCLR.EW) register. If the Early Warning interrupt is enabled in Window mode, the interrupt is generated at the start of the open window period, i.e. after TO<sub>WDTW</sub>. The Window mode operation is illustrated in figure Window-Mode Operation.

#### Figure 20-3. Window-Mode Operation

#### 20.6.3 Additional Features

#### 20.6.3.1 Always-On Mode

The Always-On mode is enabled by setting the Always-On bit in the Control register (CTRLA.ALWAYSON=1). When the Always-On mode is enabled, the WDT runs continuously, regardless of the state of CTRL.ENABLE. Once written, the Always-On bit can only be cleared by a power-on reset.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before the RTC is enabled, it must be configured, as outlined by the following steps:

- 1. RTC operation mode must be selected by writing the Operating Mode bit group in the Control register (CTRL.MODE)

- 2. Clock representation must be selected by writing the Clock Representation bit in the Control register (CTRL.CLKREP)

- 3. Prescaler value must be selected by writing the Prescaler bit group in the Control register (CTRL.PRESCALER)

The RTC prescaler divides the source clock for the RTC counter.

**Note:** In Clock/Calendar mode, the prescaler must be configured to provide a 1Hz clock to the counter for correct operation.

The frequency of the RTC clock (CLK\_RTC\_CNT) is given by the following formula:

$$f_{\text{CLK}_{\text{RTC}_{\text{CNT}}}} = \frac{f_{\text{GCLK}_{\text{RTC}}}}{2^{\text{PRESCALER}}}$$

The frequency of the generic clock, GCLK\_RTC, is given by  $f_{GCLK_RTC}$ , and  $f_{CLK_RTC_CNT}$  is the frequency of the internal prescaled RTC clock, CLK\_RTC\_CNT.

#### 21.6.2.2 Enabling, Disabling and Resetting

The RTC is enabled by setting the Enable bit in the Control register (CTRL.ENABLE=1). The RTC is disabled by writing CTRL.ENABLE=0.

The RTC is reset by setting the Software Reset bit in the Control register (CTRL.SWRST=1). All registers in the RTC, except DEBUG, will be reset to their initial state, and the RTC will be disabled. The RTC must be disabled before resetting it.

#### 21.6.3 Operating Modes

The RTC counter supports three RTC operating modes: 32-bit Counter, 16-bit Counter and Clock/ Calendar. The operating mode is selected by writing to the Operating Mode bit group in the Control register (CTRL.MODE).

#### 21.6.3.1 32-Bit Counter (Mode 0)

When the RTC Operating Mode bits in the Control register are zero (CTRL.MODE=00), the counter operates in 32-bit Counter mode. The block diagram of this mode is shown in Figure 21-1. When the RTC is enabled, the counter will increment on every 0-to-1 transition of CLK\_RTC\_CNT. The counter will increment until it reaches the top value of 0xFFFFFFF, and then wrap to 0x00000000. This sets the Overflow Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF).

The RTC counter value can be read from or written to the Counter Value register (COUNT) in 32-bit format.

The counter value is continuously compared with the 32-bit Compare register (COMP0). When a compare match occurs, the Compare 0interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next 0-to-1 transition of CLK\_RTC\_CNT.

If the Clear on Match bit in the Control register (CTRL.MATCHCLR) is '1', the counter is cleared on the next counter cycle when a compare match with COMP0 occurs. This allows the RTC to generate periodic interrupts or events with longer periods than are possible with the prescaler events. Note that when CTRL.MATCHCLR is '1', INTFLAG.CMP0 and INTFLAG.OVF will both be set simultaneously on a compare match with COMP0.

SWRST

PEREO0

CMPEO0 CMP0 CMP0 CMP0

DBGRUN

#### 21.7 **Register Summary**

The register mapping depends on the Operating Mode bits in the Control register (CTRL.MODE). The register summary is presented for each of the three modes.

| Table 21 | I-1. MODE0 - | Mode R      | egister Su | mmary   |        |        |            |        |           |  |  |  |

|----------|--------------|-------------|------------|---------|--------|--------|------------|--------|-----------|--|--|--|

| Offset   | Name         | Bit<br>Pos. |            |         |        |        |            |        |           |  |  |  |

| 0x00     | CTRL         | 7:0         | MATCHCLR   |         |        |        | MODI       | E[1:0] | ENABLE    |  |  |  |

| 0x01     | UIRL         | 15:8        |            |         |        |        |            | PRESCA | ALER[3:0] |  |  |  |

| 0x02     |              | 7:0         |            |         |        |        | ADDF       | R[5:0] |           |  |  |  |

| 0x03     | READREQ      | 15:8        | RREQ       | RCONT   |        |        |            |        |           |  |  |  |

| 0x04     |              | 7:0         | PEREO7     | PEREO6  | PEREO5 | PEREO4 | PEREO3     | PEREO2 | PEREO1    |  |  |  |

| 0x05     | EVCTRL       | 15:8        | OVFEO      |         |        |        |            |        |           |  |  |  |

| 0x06     | INTENCLR     | 7:0         | OVF        | SYNCRDY |        |        |            |        |           |  |  |  |

| 0x07     | INTENSET     | 7:0         | OVF        | SYNCRDY |        |        |            |        |           |  |  |  |

| 0x08     | INTFLAG      | 7:0         | OVF        | SYNCRDY |        |        |            |        |           |  |  |  |

| 0x09     | Reserved     |             |            |         |        |        |            |        |           |  |  |  |

| 0x0A     | STATUS       | 7:0         | SYNCBUSY   |         |        |        |            |        |           |  |  |  |

| 0x0B     | DBGCTRL      | 7:0         |            |         |        |        |            |        |           |  |  |  |

| 0x0C     | FREQCORR     | 7:0         | SIGN       |         |        |        | VALUE[6:0] |        |           |  |  |  |

| 0x0D     |              |             |            |         |        |        |            |        |           |  |  |  |

|          | Reserved     |             |            |         |        |        |            |        |           |  |  |  |

| 0x0F     |              |             |            |         |        |        |            |        |           |  |  |  |

| 0x10     |              | 7:0         |            |         |        | COUN   | NT[7:0]    |        | :         |  |  |  |

| 0x11     | COUNT        | 15:8        |            |         |        | COUN   | T[15:8]    |        |           |  |  |  |

| 0x12     | COUNT        | 23:16       |            |         |        | COUN   | Г[23:16]   |        |           |  |  |  |

| 0x13     |              | 31:24       |            |         |        | COUN   | Г[31:24]   |        |           |  |  |  |

| 0x14     |              |             |            |         |        |        |            |        |           |  |  |  |

| <br>0x17 | Reserved     |             |            |         |        |        |            |        |           |  |  |  |

| 0x18     |              | 7:0         |            |         |        | COM    | P[7:0]     | 1      | 1         |  |  |  |

| 0x19     |              | 15:8        |            |         |        | COMF   | P[15:8]    |        |           |  |  |  |

| 0x1A     | COMP0        | 23:16       |            |         |        | COMP   | [23:16]    |        |           |  |  |  |

|          | _            |             |            |         |        |        |            |        |           |  |  |  |

Та

#### Table 21-2. MODE1 - Mode Register Summary

31:24

0x1B

| Offset | Name     | Bit<br>Pos. |        |         |        |        |                |        |        |        |

|--------|----------|-------------|--------|---------|--------|--------|----------------|--------|--------|--------|

| 0x00   | CTRL     | 7:0         |        |         |        |        | MOD            | E[1:0] | ENABLE | SWRST  |

| 0x01   | CIRL     | 15:8        |        |         |        |        | PRESCALER[3:0] |        |        |        |

| 0x02   |          |             |        |         | R[5:0] |        |                |        |        |        |

| 0x03   | READREQ  | 15:8        | RREQ   | RCONT   |        |        |                |        |        |        |

| 0x04   | EVCTRL   | 7:0         | PEREO7 | PEREO6  | PEREO5 | PEREO4 | PEREO3         | PEREO2 | PEREO1 | PEREO0 |

| 0x05   | EVCIRL   | 15:8        | OVFEO  |         |        |        |                |        | CMPEO1 | CMPEO0 |

| 0x06   | INTENCLR | 7:0         | OVF    | SYNCRDY |        |        |                |        | CMP1   | CMP0   |

| 0x07   | INTENSET | 7:0         | OVF    | SYNCRDY |        |        |                |        | CMP1   | CMP0   |

COMP[31:24]

#### 21.8.4 Read Request

|        | Name:<br>Offset:<br>Reset:<br>Property: | READREQ<br>0x02<br>0x0010<br>- |           |    |    |    |   |   |  |

|--------|-----------------------------------------|--------------------------------|-----------|----|----|----|---|---|--|

| Bit    | 15                                      | 14                             | 13        | 12 | 11 | 10 | 9 | 8 |  |

|        | RREQ                                    | RCONT                          |           |    |    |    |   |   |  |

| Access | W                                       | R/W                            |           |    |    |    |   |   |  |

| Reset  | 0                                       | 0                              |           |    |    |    |   |   |  |

|        |                                         |                                |           |    |    |    |   |   |  |

| Bit    | 7                                       | 6                              | 5         | 4  | 3  | 2  | 1 | 0 |  |

|        |                                         |                                | ADDR[5:0] |    |    |    |   |   |  |

| Access |                                         | ÷                              | R         | R  | R  | R  | R | R |  |

| Reset  |                                         |                                | 0         | 1  | 0  | 0  | 0 | 0 |  |

#### Bit 15 - RREQ Read Request

Writing a zero to this bit has no effect.

Writing a one to this bit requests synchronization of the register pointed to by the Address bit group (READREQ.ADDR) and sets the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY).

#### Bit 14 – RCONT Read Continuously

Writing a zero to this bit disables continuous synchronization.

Writing a one to this bit enables continuous synchronization of the register pointed to by READREQ.ADDR. The register value will be synchronized automatically every time the register is updated. READREQ.RCONT prevents READREQ.RREQ from clearing automatically.

This bit is cleared when an RTC register is written.

#### Bits 5:0 - ADDR[5:0] Address

These bits select the offset of the register that needs read synchronization. In the RTC only COUNT and CLOCK, which share the same address, are available for read synchronization. Therefore, ADDR is a read-only constant of 0x10.

#### Bits 3:0 – ID[3:0] Channel ID

These bits store the lowest channel number with pending interrupts. The number is valid if Suspend (SUSP), Transfer Complete (TCMPL) or Transfer Error (TERR) bits are set. The Channel ID field is refreshed when a new channel (with channel number less than the current one) with pending interrupts is detected, or when the application clears the corresponding channel interrupt sources. When no pending channels interrupts are available, these bits will always return zero value when read.

When the bits are written, indirect access to the corresponding Channel Interrupt Flag register is enabled.

#### 23.6.2 Basic Operation

#### 23.6.2.1 Initialization

The EIC must be initialized in the following order:

- 1. Enable CLK\_EIC\_APB

- 2. If edge detection or filtering is required, GCLK\_EIC must be enabled

- 3. Write the EIC configuration registers (EVCTRL, WAKEUP, CONFIGy)

- 4. Enable the EIC

To use NMI, GCLK\_EIC must be enabled after EIC configuration (NMICTRL).

#### 23.6.2.2 Enabling, Disabling and Resetting

The EIC is enabled by writing a '1' the Enable bit in the Control register (CTRL.ENABLE). The EIC is disabled by writing CTRL.ENABLE to '0'.

The EIC is reset by setting the Software Reset bit in the Control register (CTRL.SWRST). All registers in the EIC will be reset to their initial state, and the EIC will be disabled.

Refer to the CTRL register description for details.

#### 23.6.3 External Pin Processing

Each external pin can be configured to generate an interrupt/event on edge detection (rising, falling or both edges) or level detection (high or low). The sense of external interrupt pins is configured by writing the Input Sense x bits in the Config n register (CONFIGn.SENSEx). The corresponding interrupt flag (INTFLAG.EXTINT[x]) in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition is met.

When the interrupt flag has been cleared in edge-sensitive mode, INTFLAG.EXTINT[x] will only be set if a new interrupt condition is met. In level-sensitive mode, when interrupt has been cleared, INTFLAG.EXTINT[x] will be set immediately if the EXTINTx pin still matches the interrupt condition.

Each external pin can be filtered by a majority vote filtering, clocked by GCLK\_EIC. Filtering is enabled if bit Filter Enable x in the Configuration n register (CONFIGn.FILTENx) is written to '1'. The majority vote filter samples the external pin three times with GCLK\_EIC and outputs the value when two or more samples are equal.

#### Table 23-1. Majority Vote Filter

| Samples [0, 1, 2] | Filter Output |

|-------------------|---------------|

| [0,0,0]           | 0             |

| [0,0,1]           | 0             |

| [0,1,0]           | 0             |

| [0,1,1]           | 1             |

| [1,0,0]           | 0             |

| [1,0,1]           | 1             |

| [1,1,0]           | 1             |

| [1,1,1]           | 1             |

When an external interrupt is configured for level detection, or if filtering is disabled, detection is made asynchronously, and GCLK\_EIC is not required.

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x10<br>0x00000000<br>- |         |         |         |         |         |         |

|--------|-----------------------------------------|------------------------------------|---------|---------|---------|---------|---------|---------|

| Bit    | 31                                      | 30                                 | 29      | 28      | 27      | 26      | 25      | 24      |

|        |                                         |                                    |         |         |         |         |         |         |

| Access |                                         |                                    |         |         |         |         |         |         |

| Reset  |                                         |                                    |         |         |         |         |         |         |

|        |                                         |                                    |         |         |         |         |         |         |

| Bit    | 23                                      | 22                                 | 21      | 20      | 19      | 18      | 17      | 16      |

|        |                                         |                                    |         |         |         |         | EXTINTx | EXTINTx |

| Access |                                         | -                                  | •       | •       |         |         | R/W     | R/W     |

| Reset  |                                         |                                    |         |         |         |         | 0       | 0       |

|        |                                         |                                    |         |         |         |         |         |         |

| Bit    | 15                                      | 14                                 | 13      | 12      | 11      | 10      | 9       | 8       |

|        | EXTINTx                                 | EXTINTx                            | EXTINTx | EXTINTx | EXTINTx | EXTINTx | EXTINTx | EXTINTx |

| Access | R/W                                     | R/W                                | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| Reset  | 0                                       | 0                                  | 0       | 0       | 0       | 0       | 0       | 0       |

|        |                                         |                                    |         |         |         |         |         |         |

| Bit    | 7                                       | 6                                  | 5       | 4       | 3       | 2       | 1       | 0       |

|        | EXTINTx                                 | EXTINTx                            | EXTINTx | EXTINTx | EXTINTx | EXTINTx | EXTINTx | EXTINTx |

| Access | R/W                                     | R/W                                | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |

| Reset  | 0                                       | 0                                  | 0       | 0       | 0       | 0       | 0       | 0       |

|        |                                         |                                    |         |         |         |         |         |         |

#### 23.8.8 Interrupt Flag Status and Clear

**Bits 17,16,15,14,13,12,11,10,9,8,7,6,5,4,3,2,1,0 – EXTINTx** External Interrupt x [x=17..0] This flag is cleared by writing a one to it.

This flag is set when EXTINTx pin matches the external interrupt sense configuration and will generate an interrupt request if INTENCLR/SET.EXTINT[x] is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the External Interrupt x flag.

## 26.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Refer to Register Access Protection.

| Value | Description               |

|-------|---------------------------|

| 0x0   | USART with external clock |

| 0x1   | USART with internal clock |

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable Synchronization Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

Writing '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded. Any register write access during the ongoing reset will result in an APB error. Reading any register will return the reset value of the register.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 28.8.5 Receive Pulse Length Register

| Name:     | RXPL                                   |

|-----------|----------------------------------------|

| Offset:   | 0x0E                                   |

| Reset:    | 0x00                                   |

| Property: | Enable-Protected, PAC Write-Protection |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

| Γ      |     |     |     | RXPI | _[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 7:0 – RXPL[7:0] Receive Pulse Length

When the encoding format is set to IrDA (CTRLB.ENC=1), these bits control the minimum pulse length that is required for a pulse to be accepted by the IrDA receiver with regards to the serial engine clock period  $SE_{per}$ .

$PULSE \geq (RXPL + 2) \cdot SE_{per}$

# ATSAMHAXEXXA SERCOM I2C – Inter-Integrated Circuit

#### Name: SYNCBUSY Offset: 0x1C Reset: 0x00000000 Bit 30 29 26 25 31 28 27 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset Bit 9 15 14 13 12 11 10 8 Access Reset Bit 7 6 5 4 3 2 1 0 SYSOP ENABLE SWRST Access R R R 0 0 0 Reset

#### 30.10.8 Synchronization Busy

#### Bit 2 – SYSOP System Operation Synchronization Busy

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | System operation synchronization is not busy. |

| 1     | System operation synchronization is busy.     |

#### Bit 1 – ENABLE SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

Bit 0 – SWRST Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

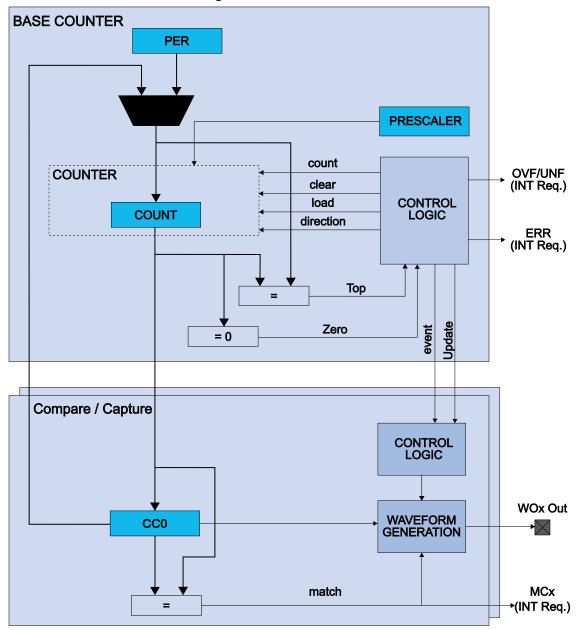

# 31. TC – Timer/Counter

## 31.1 Overview

The TC consists of a counter, a prescaler, compare/capture channels and control logic. The counter can be set to count events, or it can be configured to count clock pulses. The counter, together with the compare/capture channels, can be configured to timestamp input events, allowing capture of frequency and pulse width. It can also perform waveform generation, such as frequency generation and pulse-width modulation (PWM).

### 31.2 Features

- Selectable configuration

- Up to five 16-bit Timer/Counters (TC), each configurable as:

- 8-bit TC with two compare/capture channels

- 16-bit TC with two compare/capture channels

- 32-bit TC with two compare/capture channels, by using two TCs

- Waveform generation

- Frequency generation

- Single-slope pulse-width modulation

- Input capture

- Event capture

- Frequency capture

- Pulse-width capture

- One input event

- Interrupts/output events on:

- Counter overflow/underflow

- Compare match or capture

- Internal prescaler

- Can be used with DMA and to trigger DMA transactions

## 31.3 Block Diagram

Figure 31-1. Timer/Counter Block Diagram

# 31.4 Signal Description

| Signal Name | Туре           | Description     |

|-------------|----------------|-----------------|

| WO[1:0]     | Digital output | Waveform output |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

#### 31.8.8 Interrupt Enable Clear

Name:INTENCLROffset:0x0CReset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5   | 4   | 3       | 2 | 1   | 0   |

|--------|---|---|-----|-----|---------|---|-----|-----|

|        |   |   | MCx | MCx | SYNCRDY |   | ERR | OVF |

| Access |   |   | R/W | R/W | R/W     |   | R/W | R/W |

| Reset  |   |   | 0   | 0   | 0       |   | 0   | 0   |

**Bits 5,4 – MCx** Match or Capture Channel x Interrupt Enable [x = 1..0] Writing a '0' to these bits has no effect.

Writing a '1' to MCx will clear the corresponding Match or Capture Channel x Interrupt Enable bit, which disables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 3 – SYNCRDY Synchronization Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a one to this bit will clear the Synchronization Ready Interrupt Disable/Enable bit, which disables the Synchronization Ready interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The Synchronization Ready interrupt is disabled. |

| 1     | The Synchronization Ready interrupt is enabled.  |

#### Bit 1 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### Bit 0 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

# **ATSAMHAXEXXA** Electrical Characteristics

# 37.11.6 Analog Comparator Characteristics

## Table 37-34. Electrical and Timing

| Parameter                      | Conditions                                                                              | Symbol               | Min.  | Тур.  | Max.               | Unit |

|--------------------------------|-----------------------------------------------------------------------------------------|----------------------|-------|-------|--------------------|------|

| Positive input voltage range   |                                                                                         |                      | 0     | -     | V <sub>DDANA</sub> | V    |

| Negative input voltage range   |                                                                                         |                      | 0     | -     | V <sub>DDANA</sub> | V    |

| Offset                         | Hysteresis = 0, Fast mode                                                               |                      | -26   | 0     | 26                 | mV   |

| Oliset                         | Hysteresis = 0, Low power mode                                                          |                      | -28   | 0     | 28                 | mV   |

| Hysteresis                     | Hysteresis = 1, Fast mode                                                               |                      | 8     | 50    | 102                | mV   |

| Tysteresis                     | Hysteresis = 1, Low power mode                                                          |                      | 14    | 50    | 75                 | mV   |

| Dropogation dology             | Changes for V <sub>ACM</sub> = V <sub>DDANA</sub> /2<br>100mV overdrive, Fast mode      |                      |       | 90    | 180                | ns   |

| Propagation delay              | Changes for V <sub>ACM</sub> = V <sub>DDANA</sub> /2<br>100mV overdrive, Low power mode |                      |       | 302   | 534                | ns   |

| Startun tima                   | Enable to ready delay<br>Fast mode                                                      | +                    |       | 1     | 2                  | μs   |

| Startup time                   | Enable to ready delay<br>Low power mode                                                 | t <sub>STARTUP</sub> | -     | 14    | 23                 | μs   |

| INL <sup>(3)</sup>             |                                                                                         |                      | -1.4  | 0.201 | 1.4                | LSB  |

| DNL <sup>(3)</sup>             |                                                                                         | V                    | -0.9  | 0.022 | 0.9                | LSB  |

| Offset Error <sup>(1)(2)</sup> |                                                                                         | V <sub>SCALE</sub>   | -0.2  | 0.056 | 0.92               | LSB  |

| Gain Error <sup>(1)(2)</sup>   |                                                                                         |                      | -0.89 | 0.079 | 0.89               | LSB  |

1. According to the standard equation  $V(X) = V_{LSB} \times (X + 1)$ ;  $V_{LSB} = V_{DDANA}/64$

- 2. Data computed with the Best Fit method

- 3. Data computed using histogram

# 37.11.7 Internal 1.1V Bandgap Reference Characteristics

#### Table 37-35. Bandgap and Internal 1.1V Reference Characteristics

| Parameter                             | Conditions                                       | Symbol | Min. | Тур. | Max. | Unit |

|---------------------------------------|--------------------------------------------------|--------|------|------|------|------|

|                                       | After<br>calibration at<br>T= 25°C,              | INT1V  | 1.07 | 1.1  | 1.12 |      |

| Internal 1.1V<br>Bandgap<br>reference | over [–40,<br>+105]°C,<br>V <sub>DD</sub> = 3.3V |        |      |      |      | V    |

|                                       | Over voltage<br>at 25°C                          |        | 1.08 | 1.1  | 1.11 | V    |