Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 1K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 115°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-VQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha0e15a-mzt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ATSAMHAXEXXA DSU - Device Service Unit

# 15.12 Register Summary

| Offset             | Name     | Bit Pos. |                               |            |           |         |          |       |          |        |

|--------------------|----------|----------|-------------------------------|------------|-----------|---------|----------|-------|----------|--------|

| 0x00               | CTRL     | 7:0      |                               |            |           | CE      | MBIST    | CRC   |          | SWRST  |

| 0x01               | STATUSA  | 7:0      |                               |            |           | PERR    | FAIL     | BERR  | CRSTEXT  | DONE   |

| 0x02               | STATUSB  | 7:0      |                               |            |           | HPE     | DCCDx    | DCCDx | DBGPRES  | PROT   |

| 0x03               | Reserved |          |                               |            |           |         |          |       |          |        |

|                    |          | 7:0      |                               |            | ADD       | R[5:0]  | 1        |       | AMO      | D[1:0] |

| 0×04               |          | 15:8     |                               |            |           | ADD     | R[13:6]  |       |          |        |

| 0x04               | ADDR     | 23:16    |                               |            |           | ADDR    | [21:14]  |       |          |        |

|                    |          | 31:24    |                               |            |           | ADDR    | [29:22]  |       |          |        |

|                    |          | 7:0      |                               |            | LENG      | TH[5:0] |          |       |          |        |

| 0x08               | LENGTH   | 15:8     |                               |            |           | LENG    | H[13:6]  |       |          |        |

| 0x08               | LENGTH   | 23:16    |                               |            |           | LENGT   | H[21:14] |       |          |        |

|                    |          | 31:24    |                               |            |           | LENGT   | H[29:22] |       |          |        |

|                    |          | 7:0      |                               |            |           | DAT     | A[7:0]   |       |          |        |

|                    |          | 15:8     |                               |            |           | DATA    | [15:8]   |       |          |        |

| 0x0C               | DATA     | 23:16    |                               |            |           | DATA    | [23:16]  |       |          |        |

|                    |          | 31:24    |                               |            |           | DATA    | [31:24]  |       |          |        |

|                    |          | 7:0      |                               |            |           | DAT     | A[7:0]   |       |          |        |

|                    |          | 15:8     |                               | DATA[15:8] |           |         |          |       |          |        |

| 0x10               | DCC0     | 23:16    | DATA[23:16]                   |            |           |         |          |       |          |        |

|                    |          | 31:24    |                               |            |           |         | [31:24]  |       |          |        |

|                    |          | 7:0      | DATA[7:0]                     |            |           |         |          |       |          |        |

|                    |          | 15:8     | DATA[15:8]                    |            |           |         |          |       |          |        |

| 0x14               | DCC1     | 23:16    | DATA[23:16]                   |            |           |         |          |       |          |        |

|                    |          | 31:24    |                               |            |           |         | [31:24]  |       |          |        |

|                    |          | 7:0      |                               |            |           |         | EL[7:0]  |       |          |        |

|                    |          | 15:8     | DIE[3:0] REVISION[3:0]        |            |           |         |          |       |          |        |

| 0x18               | DID      | 23:16    | FAMILY[0:0] SERIES[5:0]       |            |           | ES[5:0] |          |       |          |        |

|                    |          | 31:24    |                               | PROCE      | SSOR[3:0] |         |          | FAM   | ILY[4:1] |        |

| 0x1C<br><br>0x0FFF | Reserved |          |                               |            |           |         |          |       |          |        |

|                    |          | 7:0      |                               |            |           |         |          |       | FMT      | EPRES  |

|                    |          | 15:8     |                               | Δηρά       | DFF[3:0]  |         |          |       |          | LINEO  |

| 0x1000             | ENTRY0   | 23:16    |                               |            | 511[0.0]  |         | =E[11·/] |       |          |        |

|                    |          | 31:24    | ADDOFF[11:4]<br>ADDOFF[19:12] |            |           |         |          |       |          |        |

|                    |          | 7:0      |                               |            |           | ADDOI   | 1[19.12] |       | FMT      | EPRES  |

|                    | ENTRY1   | 15:8     |                               | م م م      | OFF[3:0]  |         |          |       |          | LENEO  |

| 0x1004             |          | 23:16    |                               | ADDC       | 511[5.0]  | ٥٩٩٨    | F[11:4]  |       |          |        |

|                    |          | 31:24    |                               |            |           |         |          |       |          |        |

|                    |          |          |                               |            |           |         | F[19:12] |       |          |        |

|                    |          | 7:0      |                               |            |           |         | D[7:0]   |       |          |        |

| 0x1008             | END      | 15:8     | END[15:8]                     |            |           |         |          |       |          |        |

|                    |          | 23:16    |                               |            |           |         | 23:16]   |       |          |        |

|                    |          | 31:24    |                               |            |           | END     | 31:24]   |       |          |        |

## Bits 7:0 – DEVSEL[7:0] Device Selection

This bit field identifies a device within a product family and product series. Refer to the ordering information for device configurations and corresponding values for Flash memory density, pin count, and device variant.

#### Bit 6 – SERCOM4 SERCOM4 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM4 is stopped. |

| 1     | The APBC clock for the SERCOM4 is enabled. |

#### Bit 5 – SERCOM3 SERCOM3 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM3 is stopped. |

| 1     | The APBC clock for the SERCOM3 is enabled. |

#### Bit 4 – SERCOM2 SERCOM2 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM2 is stopped. |

| 1     | The APBC clock for the SERCOM2 is enabled. |

## Bit 3 – SERCOM1 SERCOM1 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM1 is stopped. |

| 1     | The APBC clock for the SERCOM1 is enabled. |

#### Bit 2 – SERCOM0 SERCOM0 APB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM0 is stopped. |

| 1     | The APBC clock for the SERCOM0 is enabled. |

#### Bit 1 – EVSYS EVSYS APB Clock Enable

| ſ | Value | Description                              |

|---|-------|------------------------------------------|

|   | 0     | The APBC clock for the EVSYS is stopped. |

|   | 1     | The APBC clock for the EVSYS is enabled. |

#### Bit 0 – PAC2 PAC2 APB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBC clock for the PAC2 is stopped. |

| 1     | The APBC clock for the PAC2 is enabled. |

- Writing to the BOD33 or BOD12 control register

- Reading the BOD33 or BOD12 control register that was written

The user can either poll PCLKSR.B12SRDY or PCLKSR.B33SRDY or use the INTENSET.B12SRDY or INTENSET.B33SRDY interrupts to check when the synchronization is complete. It is also possible to perform the next read/write operation and wait, as this next operation will be completed after the ongoing read/write operation is synchronized.

# **19.8 Register Description**

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

SYSCTRL – System Controller

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | OSC32K is not ready.                                     |

| 1     | OSC32K is stable and ready to be used as a clock source. |

#### Bit 1 – XOSC32KRDY XOSC32K Ready

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | XOSC32K is not ready.                                     |

| 1     | XOSC32K is stable and ready to be used as a clock source. |

## Bit 0 - XOSCRDY XOSC Ready

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | XOSC is not ready.                                     |

| 1     | XOSC is stable and ready to be used as a clock source. |

## Bit 2 – HYST Hysteresis

This bit indicates whether hysteresis is enabled for the BOD33 threshold voltage:

This bit is loaded from Flash User Row at start-up. Refer to NVM User Row Mapping for more details.

| Value | Description         |

|-------|---------------------|

| 0     | No hysteresis.      |

| 1     | Hysteresis enabled. |

#### Bit 1 – ENABLE Enable

This bit is loaded from Flash User Row at startup. Refer to NVM User Row Mapping for more details.

| Value | Description        |

|-------|--------------------|

| 0     | BOD33 is disabled. |

| 1     | BOD33 is enabled.  |

#### **Related Links**

**Electrical Characteristics**

#### 20.8.1 Control

| Name:     | CTRL                                                  |

|-----------|-------------------------------------------------------|

| Offset:   | 0x0                                                   |

| Reset:    | N/A - Loaded from NVM User Row at start-up            |

| Property: | Write-Protected, Enable-Protected, Write-Synchronized |

| Bit    | 7        | 6 | 5 | 4 | 3 | 2   | 1      | 0 |

|--------|----------|---|---|---|---|-----|--------|---|

| ĺ      | ALWAYSON |   |   |   |   | WEN | ENABLE |   |

| Access | R/W      |   |   |   |   | R/W | R/W    |   |

| Reset  | x        |   |   |   |   | x   | x      |   |

#### Bit 7 – ALWAYSON Always-On

This bit allows the WDT to run continuously. After being written to one, this bit cannot be written to zero, and the WDT will remain enabled until a power-on reset is received. When this bit is one, the Control register (CTRL), the Configuration register (CONFIG) and the Early Warning Control register (EWCTRL) will be read-only, and any writes to these registers are not allowed. Writing a zero to this bit has no effect.

This bit is not enable-protected.

These bits are loaded from NVM User Row at start-up. Refer to NVM User Row Mapping for more details.

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The WDT is enabled and disabled through the ENABLE bit.                |

| 1     | The WDT is enabled and can only be disabled by a power-on reset (POR). |

#### Bit 2 – WEN Watchdog Timer Window Mode Enable

The initial value of this bit is loaded from Flash Calibration.

This bit is loaded from NVM User Row at start-up. Refer to NVM User Row Mapping for more details.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Window mode is disabled (normal operation). |

| 1     | Window mode is enabled.                     |

#### Bit 1 – ENABLE Enable

This bit enables or disables the WDT. Can only be written while CTRL.ALWAYSON is zero.

Due to synchronization, there is delay from writing CTRL.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately, and the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set. STATUS.SYNCBUSY will be cleared when the operation is complete.

This bit is not enable-protected.

This bit is loaded from NVM User Row at start-up. Refer to NVM User Row Mapping for more details.

| Value | Description          |

|-------|----------------------|

| 0     | The WDT is disabled. |

| 1     | The WDT is enabled.  |

#### **Related Links**

#### 21.6.7 Sleep Mode Operation

The RTC will continue to operate in any sleep mode where the source clock is active. The RTC *interrupts* can be used to wake up the device from a sleep mode. RTC *events* can trigger other operations in the system without exiting the sleep mode.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering any interrupt. In this case, the CPU will continue executing right from the first instruction that followed the entry into sleep.

The periodic events can also wake up the CPU through the interrupt function of the Event System. In this case, the event must be enabled and connected to an event channel with its interrupt enabled. See *Event System* for more information.

Related Links EVSYS – Event System

#### 21.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

When executing an operation that requires synchronization, the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set immediately, and cleared when synchronization is complete. The Synchronization Ready interrupt can be used to signal when synchronization is complete. This can be accessed via the Synchronization Ready Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.SYNCRDY). If an operation that requires synchronization is executed while STATUS.SYNCBUSY is one, the bus will be stalled. All operations will complete successfully, but the CPU will be stalled and interrupts will be pending as long as the bus is stalled.

The following bits are synchronized when written:

- Software Reset bit in the Control register (CTRL.SWRST)

- Enable bit in the Control register (CTRL.ENABLE)

The following registers are synchronized when written:

- Counter Value register (COUNT)

- Clock Value register (CLOCK)

- Counter Period register (PER)

- Compare n Value registers (COMPn)

- Alarm n Value registers (ALARMn)

- Frequency Correction register (FREQCORR)

- Alarm n Mask register (MASKn)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

The following registers are synchronized when read:

- The Counter Value register (COUNT)

- The Clock Value register (CLOCK)

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

#### **Related Links**

© 2017 Microchip Technology Inc.

# PORT - I/O Pin Controller

| Value | Description                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the group will keep its configuration.                                    |

| 1     | The corresponding I/O pin output is driven high, or the input is connected to an internal pull-<br>up. |

#### 27.6.2 Basic Operation

#### 27.6.2.1 Initialization

The SERCOM must be configured to the desired mode by writing the Operating Mode bits in the Control A register (CTRLA.MODE). Refer to table SERCOM Modes for details.

#### Table 27-1. SERCOM Modes

| CTRLA.MODE | Description                       |

|------------|-----------------------------------|

| 0x0        | USART with external clock         |

| 0x1        | USART with internal clock         |

| 0x2        | SPI in slave operation            |

| 0x3        | SPI in master operation           |

| 0x4        | I <sup>2</sup> C slave operation  |

| 0x5        | I <sup>2</sup> C master operation |

| 0x6-0x7    | Reserved                          |

For further initialization information, see the respective SERCOM mode chapters:

### **Related Links**

SERCOM USART SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

#### 27.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

Refer to the CTRLA register description for details.

#### 27.6.2.3 Clock Generation – Baud-Rate Generator

The baud-rate generator, as shown in Figure 27-3, generates internal clocks for asynchronous and synchronous communication. The output frequency ( $f_{BAUD}$ ) is determined by the Baud register (BAUD) setting and the baud reference frequency ( $f_{ref}$ ). The baud reference clock is the serial engine clock, and it can be internal or external.

For asynchronous communication, the /16 (divide-by-16) output is used when transmitting, whereas the /1 (divide-by-1) output is used while receiving.

For synchronous communication, the /2 (divide-by-2) output is used.

This functionality is automatically configured, depending on the selected operating mode.

#### 28.8.4 Baud

| Name:     | BAUD                                   |

|-----------|----------------------------------------|

| Offset:   | 0x0C                                   |

| Reset:    | 0x0000                                 |

| Property: | Enable-Protected, PAC Write-Protection |

| Bit    | 15  | 14         | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|-----|------------|-----|------|--------|-----|-----|-----|

|        |     | BAUD[15:8] |     |      |        |     |     |     |

| Access | R/W | R/W        | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0          | 0   | 0    | 0      | 0   | 0   | 0   |

|        |     |            |     |      |        |     |     |     |

| Bit    | 7   | 6          | 5   | 4    | 3      | 2   | 1   | 0   |

|        |     |            |     | BAUI | D[7:0] |     |     |     |

| Access | R/W | R/W        | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0          | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 15:0 - BAUD[15:0] Baud Value

Arithmetic Baud Rate Generation (CTRLA.SAMPR[0]=0):

These bits control the clock generation, as described in the SERCOM Baud Rate section.

If Fractional Baud Rate Generation (CTRLA.SAMPR[0]=1) bit positions 15 to 13 are replaced by FP[2:0] Fractional Part:

#### • Bits 15:13 - FP[2:0]: Fractional Part

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

#### • Bits 12:0 - BAUD[12:0]: Baud Value

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

#### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

SERCOM I2C – Inter-Integrated Circuit

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0x0   | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1   | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2   | High-speed mode (Hs-mode) up to 3.4 MHz                           |

| 0x3   | Reserved                                                          |

### Bit 23 – SEXTTOEN Slave SCL Low Extend Time-Out

This bit enables the slave SCL low extend time-out. If SCL is cumulatively held low for greater than 25ms from the initial START to a STOP, the slave will release its clock hold if enabled and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. If the address was recognized, PREC will be set when a STOP is received.

This bit is not synchronized.

| Value | Description       |

|-------|-------------------|

| 0     | Time-out disabled |

| 1     | Time-out enabled  |

#### Bits 21:20 - SDAHOLD[1:0] SDA Hold Time

These bits define the SDA hold time with respect to the negative edge of SCL.

These bits are not synchronized.

| Value | Name | Description         |

|-------|------|---------------------|

| 0x0   | DIS  | Disabled            |

| 0x1   | 75   | 50-100ns hold time  |

| 0x2   | 450  | 300-600ns hold time |

| 0x3   | 600  | 400-800ns hold time |

#### Bit 16 - PINOUT Pin Usage

This bit sets the pin usage to either two- or four-wire operation:

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | 4-wire operation disabled |

| 1     | 4-wire operation enabled  |

#### Bit 7 – RUNSTDBY Run in Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Disabled – All reception is dropped. |

| 1     | Wake on address match, if enabled.   |

### Bits 4:2 - MODE[2:0] Operating Mode

These bits must be written to 0x04 to select the I<sup>2</sup>C slave serial communication interface of the SERCOM.

These bits are not synchronized.

ATSAMHAXEXXA TC – Timer/Counter

- If the prescaler is used, select a prescaler synchronization operation via the Prescaler and Counter Synchronization bit group in the Control A register (CTRLA.PRESYNC).

- 5. Select one-shot operation by writing a '1' to the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT).

- 6. If desired, configure the counting direction 'down' (starting from the TOP value) by writing a '1' to the Counter Direction bit in the Control B register (CTRLBSET.DIR).

- 7. For capture operation, enable the individual channels to capture in the Capture Channel x Enable bit group in the Control C register (CTRLC.CPTEN).

- 8. If desired, enable inversion of the waveform output or IO pin input signal for individual channels via the Waveform Output Invert Enable bit group in the Control C register (CTRLC.INVEN).

### 31.6.2.2 Enabling, Disabling and Resetting

The TC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TC is disbled by writing a zero to CTRLA.ENABLE.

The TC is reset by writing a one to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TC, except DBGCTRL, will be reset to their initial state, and the TC will be disabled. Refer to the CTRLA register for details.

The TC should be disabled before the TC is reset in order to avoid undefined behavior.

#### 31.6.2.3 Prescaler Selection

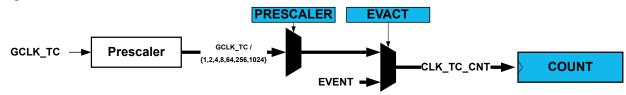

The GCLK\_TCx is fed into the internal prescaler.

The prescaler consists of a counter that counts up to the selected prescaler value, whereupon the output of the prescaler toggles.

If the prescaler value is higher than one, the counter update condition can be optionally executed on the next GCLK\_TCx clock pulse or the next prescaled clock pulse. For further details, refer to Prescaler (CTRLA.PRESCALER) and Counter Synchronization (CTRLA.PRESYNC) description.

Prescaler outputs from 1 to 1/1024 are available. For a complete list of available prescaler outputs, see the register description for the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

**Note:** When counting events, the prescaler is bypassed.

The joint stream of prescaler ticks and event action ticks is called CLK\_TC\_CNT.

#### Figure 31-2. Prescaler

#### 31.6.2.4 Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period register (PER). This register is used to store the period value that can be used as the top value for waveform generation.

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

# 33. ADC – Analog-to-Digital Converter

## 33.1 Overview

The Analog-to-Digital Converter (ADC) converts analog signals to digital values. The ADC has 12-bit resolution, and is capable of converting up to 350ksps. The input selection is flexible, and both differential and single-ended measurements can be performed. An optional gain stage is available to increase the dynamic range. In addition, several internal signal inputs are available. The ADC can provide both signed and unsigned results.

ADC measurements can be started by either application software or an incoming event from another peripheral in the device. ADC measurements can be started with predictable timing, and without software intervention.

Both internal and external reference voltages can be used.

The ADC has a compare function for accurate monitoring of user-defined thresholds, with minimum software intervention required.

The ADC may be configured for 8-, 10- or 12-bit results, reducing the conversion time. ADC conversion results are provided left- or right-adjusted, which eases calculation when the result is represented as a signed value. It is possible to use DMA to move ADC results directly to memory or peripherals when conversions are done.

# 33.2 Features

- 8-, 10- or 12-bit resolution

- Up to 350,000 samples per second (350ksps)

- Differential and single-ended inputs

- Up to analog input

- positive and negative, including internal and external

- internal inputs

- Bandgap

- DAC

- Scaled core supply

- Scaled I/O supply

- 1/2x to 16x gain

- Single, continuous and pin-scan conversion options

- Windowing monitor with selectable channel

- Conversion range:

- V<sub>ref</sub> [1v to V<sub>DDANA</sub> 0.6V]

- ADCx \* GAIN [0V to -V<sub>ref</sub>]

- Built-in internal reference and external reference options

- Four bits for reference selection

- Event-triggered conversion for accurate timing (one event input)

- Optional DMA transfer of conversion result

- Hardware gain and offset compensation

# ATSAMHAXEXXA AC – Analog Comparators

# 34.7 Register Summary

| Offset | Name      | Bit Pos. |          |       |         |          |      |          |             |         |

|--------|-----------|----------|----------|-------|---------|----------|------|----------|-------------|---------|

| 0x00   | CTRLA     | 7:0      | LPMUX    |       |         |          |      | RUNSTDBY | ENABLE      | SWRST   |

| 0x01   | CTRLB     | 7:0      |          |       |         |          |      |          | STARTx      | STARTx  |

| 0.00   | EV (OT DI | 7:0      |          |       |         | WINEO0   |      |          | COMPEOx     | COMPEOx |

| 0x02   | EVCTRL    | 15:8     |          |       |         |          |      |          | COMPEIx     | COMPEIx |

| 0x04   | INTENCLR  | 7:0      |          |       |         | WIN0     |      |          | COMPx       | COMPx   |

| 0x05   | INTENSET  | 7:0      |          |       |         | WIN0     |      |          | COMPx       | COMPx   |

| 0x06   | INTFLAG   | 7:0      |          |       |         | WIN0     |      |          | COMPx       | COMPx   |

| 0x07   | Reserved  |          |          |       |         |          |      |          |             |         |

| 0x08   | STATUSA   | 7:0      |          |       | WSTA    | TE0[1:0] |      |          | STATEx      | STATEx  |

| 0x09   | STATUSB   | 7:0      | SYNCBUSY |       |         |          |      |          | READYx      | READYx  |

| 0x0A   | STATUSC   | 7:0      |          |       | WSTA    | TE0[1:0] |      |          | STATEx      | STATEx  |

| 0x0B   | Reserved  |          |          |       |         |          |      |          |             |         |

| 0x0C   | WINCTRL   | 7:0      |          |       |         |          |      | WINTSI   | EL0[1:0]    | WEN0    |

| 0x0D   |           |          |          |       |         |          |      |          |             |         |

|        | Reserved  |          |          |       |         |          |      |          |             |         |

| 0x0F   |           |          |          |       |         |          |      |          |             |         |

|        |           | 7:0      |          | INTSI | EL[1:0] |          | SPEE | D[1:0]   | SINGLE      | ENABLE  |

| 0x10   | COMPCTRL0 | 15:8     | SWAP     |       | MUXP    | OS[1:0]  |      |          | MUXNEG[2:0] |         |

| 0,10   |           | 23:16    |          |       |         |          | HYST |          | OUT         | [1:0]   |

|        |           | 31:24    |          |       |         |          |      |          | FLEN[2:0]   |         |

|        |           | 7:0      |          | INTSI | EL[1:0] |          | SPEE | D[1:0]   | SINGLE      | ENABLE  |

| 0x14   | COMPCTRL1 | 15:8     | SWAP     |       | MUXP    | OS[1:0]  |      |          | MUXNEG[2:0] |         |

| 0.14   | COMPETIEL | 23:16    |          |       |         |          | HYST |          | OUT         | [1:0]   |

|        |           | 31:24    |          |       |         |          |      |          | FLEN[2:0]   |         |

| 0x18   |           |          |          |       |         |          |      |          |             |         |

|        | Reserved  |          |          |       |         |          |      |          |             |         |

| 0x1F   |           |          |          |       |         |          |      |          |             |         |

| 0x20   | SCALER0   | 7:0      |          |       |         |          | VALU | IE[5:0]  |             |         |

| 0x21   | SCALER1   | 7:0      |          |       |         |          | VALU | IE[5:0]  |             |         |

# 34.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to *Register Access Protection*.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to *Synchronization*.

© 2017 Microchip Technology Inc.

AC – Analog Comparators

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

DAC – Digital-to-Analog Converter

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | The DAC output is turned off.                                                   |

| 1     | The high-drive output buffer drives the DAC output to the V <sub>OUT</sub> pin. |

# **Electrical Characteristics**

| Parameter                | Conditions                                            | Symbol            | Min. | Тур.   | Max. | Unit |

|--------------------------|-------------------------------------------------------|-------------------|------|--------|------|------|

|                          | V <sub>DD</sub> = 3V-3.63V,<br>PORT.PINCFG.DRVSTR=0   |                   | -    | -      | 2    |      |

|                          | V <sub>DD</sub> = 2.7V-3V,<br>PORT.PINCFG.DRVSTR=1    | -                 | -    | -      | 2    |      |

|                          | V <sub>DD</sub> = 3V-3.63V,<br>PORT.PINCFG.DRVSTR=1   |                   | -    | -      | 7    |      |

| Rise time <sup>(1)</sup> | PORT.PINCFG.DRVSTR = 0load = 5pF,<br>$V_{DD}$ = 3.3V  | 4                 | -    | -      | 15   | ns   |

|                          | PORT.PINCFG.DRVSTR = 1load = 20pF,<br>$V_{DD}$ = 3.3V | t <sub>RISE</sub> | -    | -      | 15   |      |

| Fall time <sup>(1)</sup> | PORT.PINCFG.DRVSTR = 0load = 5pF,<br>$V_{DD}$ = 3.3V  | +                 | -    | -      | 15   |      |

| raii ume <sup>vn</sup>   | PORT.PINCFG.DRVSTR = 1load = 20pF,<br>$V_{DD}$ = 3.3V | t <sub>FALL</sub> | -    | -      | 15   | ns   |

| Input leakage current    | Pull-up resistors disabled                            | I <sub>LEAK</sub> | -1   | ±0.015 | 1    | μA   |

**Note:** These values are based on simulation. These values are not covered by test limits in production or characterization.

## 37.10.2 I<sup>2</sup>C Pins

Refer to the I/O Multiplexing and Considerations section to get the list of I<sup>2</sup>C pins.

# Table 37-17. I<sup>2</sup>C Pins Characteristics in I<sup>2</sup>C Configuration

| Parameter                            | Condition                                             | Symbol            | Min.                 | Тур. | Max.                | Unit |

|--------------------------------------|-------------------------------------------------------|-------------------|----------------------|------|---------------------|------|

| Pull-up - Pull-down resistance       |                                                       | R <sub>PULL</sub> | 20                   | 40   | 60                  | kΩ   |

| Input low-level voltage              | V <sub>DD</sub> = 2.7V-3.63V                          | V <sub>IL</sub>   | -                    | -    | $0.3 \times V_{DD}$ | V    |

| Input high-level voltage             | V <sub>DD</sub> = 2.7V-3.63V                          | V <sub>IH</sub>   | $0.55 \times V_{DD}$ | -    | -                   | V    |

| Hysteresis of Schmitt trigger inputs |                                                       | V <sub>HYS</sub>  | $0.08 \times V_{DD}$ | -    | -                   |      |

|                                      | V <sub>DD</sub> > 2.0V,<br>I <sub>OL</sub> = 3mA      | V <sub>OL</sub>   | -                    | -    | 0.4                 |      |

| Output low-level voltage             | $V_{DD} \le 2.0V$<br>,<br>$I_{OL} = 2mA$              |                   | -                    | -    | $0.2 \times V_{DD}$ |      |

| Capacitance for each I/O Pin         |                                                       | CI                |                      |      |                     | pF   |

| Output low-level current             | V <sub>OL</sub> = 0.4V<br>Standard, Fast and HS Modes | 1                 | 3                    |      |                     | mA   |

| Output low-level current             | V <sub>OL</sub> = 0.4V<br>Fast Mode +                 | I <sub>OL</sub>   | 20                   | _    | -                   | mA   |

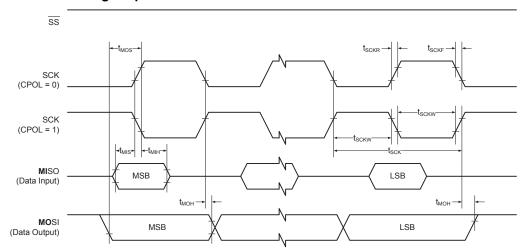

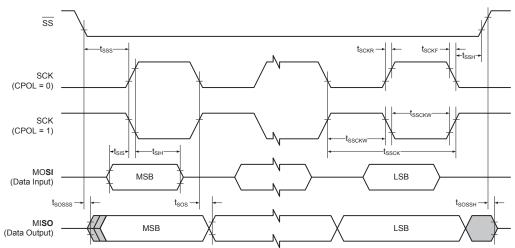

#### 37.15.2 SERCOM in SPI Mode Timing

Figure 37-13. SPI Timing Requirements in Master Mode

| Table 37-51. | SPI Timing | <b>Characteristics and</b> | Requirements <sup>(1)</sup> |

|--------------|------------|----------------------------|-----------------------------|

|--------------|------------|----------------------------|-----------------------------|

| Symbol            | Parameter                    | Conditions | Min.                   | Тур.                    | Max. | Units |

|-------------------|------------------------------|------------|------------------------|-------------------------|------|-------|

| t <sub>SCK</sub>  | SCK period                   | Master     |                        | 84                      |      | ns    |

| t <sub>SCKW</sub> | SCK high/low width           | Master     | -                      | 0.5*t <sub>SCK</sub>    | -    |       |

| t <sub>SCKR</sub> | SCK rise time <sup>(2)</sup> | Master     | -                      | -                       | -    |       |

| t <sub>SCKF</sub> | SCK fall time <sup>(2)</sup> | Master     | -                      | -                       | -    |       |

| t <sub>MIS</sub>  | MISO setup to SCK            | Master     | -                      | 21                      | -    |       |

| t <sub>MIH</sub>  | MISO hold after SCK          | Master     | -                      | 13                      | -    |       |

| t <sub>MOS</sub>  | MOSI setup SCK               | Master     | -                      | t <sub>SCK</sub> /2 - 3 | -    |       |

| t <sub>MOH</sub>  | MOSI hold after SCK          | Master     | -                      | 3                       | -    |       |

| t <sub>SSCK</sub> | Slave SCK Period             | Slave      | 1*t <sub>CLK_APB</sub> | -                       | -    |       |