Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 115°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-VQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha0e16a-mzt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ATSAMHAXEXXA

# **GCLK - Generic Clock Controller**

| GCLK<br>Generator ID | Reset Value after a User Reset                                                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x03                 | 0x00000003 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x04                 | 0x00000004 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one |

| 0x05                 | 0x0000005 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| 0x06                 | 0x0000006 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| 0x07                 | 0x0000007 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

| 0x08                 | 0x0000008 if the generator is not used by the RTC and not a source of a 'locked'<br>generic clock<br>No change if the generator is used by the RTC or used by a GCLK with a WRTLOCK as<br>one  |

# ATSAMHAXEXXA PM – Power Manager

# 18.7 Register Summary

| Offset | Name     | Bit Pos. |         |         |         |         |         |         |              |       |

|--------|----------|----------|---------|---------|---------|---------|---------|---------|--------------|-------|

| 0x00   | CTRL     | 7:0      |         |         |         |         |         |         |              |       |

| 0x01   | SLEEP    | 7:0      |         |         |         |         |         |         | IDLE         | [1:0] |

| 0x02   |          |          |         |         |         |         |         |         |              |       |

|        | Reserved |          |         |         |         |         |         |         |              |       |

| 0x07   |          |          |         |         |         |         |         |         |              |       |

| 0x08   | CPUSEL   | 7:0      |         |         |         |         |         |         | CPUDIV[2:0]  |       |

| 0x09   | APBASEL  | 7:0      |         |         |         |         |         |         | APBADIV[2:0] |       |

| 0x0A   | APBBSEL  | 7:0      |         |         |         |         |         |         | APBBDIV[2:0] |       |

| 0x0B   | APBCSEL  | 7:0      |         |         |         |         |         |         | APBCDIV[2:0] |       |

| 0x0C   |          |          |         |         |         |         |         |         |              |       |

|        | Reserved |          |         |         |         |         |         |         |              |       |

| 0x13   |          |          |         |         |         |         |         |         |              |       |

|        |          | 7:0      |         |         | DMAC    | NVMCTRL | DSU     | HPB2    | HPB1         | HPB0  |

| 0.14   |          | 15:8     |         |         |         |         |         |         |              |       |

| 0x14   | AHBMASK  | 23:16    |         |         |         |         |         |         |              |       |

|        |          | 31:24    |         |         |         |         |         |         |              |       |

|        |          | 7:0      |         | EIC     | RTC     | WDT     | GCLK    | SYSCTRL | PM           | PAC0  |

|        |          | 15:8     |         |         |         |         |         |         |              |       |

| 0x18   | APBAMASK | 23:16    |         |         |         |         |         |         |              |       |

|        |          | 31:24    |         |         |         |         |         |         |              |       |

|        |          | 7:0      |         |         |         | DMAC    | PORT    | NVMCTRL | DSU          | PAC1  |

|        |          | 15:8     |         |         |         |         |         |         |              |       |

| 0x1C   | APBBMASK | 23:16    |         |         |         |         |         |         |              |       |

|        |          | 31:24    |         |         |         |         |         |         |              |       |

|        |          | 7:0      | SERCOM5 | SERCOM4 | SERCOM3 | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS        | PAC2  |

|        |          | 15:8     | TC7     | TC6     | TC5     | TC4     | TC3     | TCC2    | TCC1         | TCC0  |

| 0x20   | APBCMASK | 23:16    |         |         |         |         | PTC     | DAC     | AC           | ADC   |

|        |          | 31:24    |         |         |         |         |         |         |              |       |

| 0x24   |          |          |         |         |         |         |         |         |              |       |

|        | Reserved |          |         |         |         |         |         |         |              |       |

| 0x33   |          |          |         |         |         |         |         |         |              |       |

| 0x34   | INTENCLR | 7:0      |         |         |         |         |         |         |              | CKRDY |

| 0x35   | INTENSET | 7:0      |         |         |         |         |         |         |              | CKRDY |

| 0x36   | INTFLAG  | 7:0      |         |         |         |         |         |         |              | CKRDY |

| 0x37   | Reserved |          |         |         |         |         |         |         |              |       |

| 0x38   | RCAUSE   | 7:0      |         | SYST    | WDT     | EXT     |         | BOD33   | BOD12        | POR   |

# 18.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

# 18.8.2 Sleep Mode

| Name:     | SLEEP           |

|-----------|-----------------|

| Offset:   | 0x01            |

| Reset:    | 0x00            |

| Property: | Write-Protected |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |

|--------|---|---|---|---|---|---|------|-------|

| [      |   |   |   |   |   |   | IDLE | [1:0] |

| Access |   |   |   |   |   |   | R/W  | R/W   |

| Reset  |   |   |   |   |   |   | 0    | 0     |

# Bits 1:0 – IDLE[1:0] Idle Mode Configuration

# These bits select the Idle mode configuration after a WFI instruction.

| IDLE[1:0] | Name | Description                                    |

|-----------|------|------------------------------------------------|

| 0x0       | CPU  | The CPU clock domain is stopped                |

| 0x1       | AHB  | The CPU and AHB clock domains are stopped      |

| 0x2       | APB  | The CPU, AHB and APB clock domains are stopped |

| 0x3       |      | Reserved                                       |

#### 18.8.8 APBA Mask

|        | Name:<br>Offset:<br>Reset:<br>Property: | APBAMASK<br>0x18<br>0x0000007F<br>Write-Protecte | ed  |     |      |         |     |      |

|--------|-----------------------------------------|--------------------------------------------------|-----|-----|------|---------|-----|------|

| Bit    | 31                                      | 30                                               | 29  | 28  | 27   | 26      | 25  | 24   |

|        |                                         |                                                  |     |     |      |         |     |      |

| Access |                                         |                                                  |     |     |      |         |     |      |

| Reset  |                                         |                                                  |     |     |      |         |     |      |

| Bit    | 23                                      | 22                                               | 21  | 20  | 19   | 18      | 17  | 16   |

|        |                                         |                                                  |     |     |      |         |     |      |

| Access |                                         |                                                  |     |     |      |         |     |      |

| Reset  |                                         |                                                  |     |     |      |         |     |      |

| Bit    | 15                                      | 14                                               | 13  | 12  | 11   | 10      | 9   | 8    |

|        |                                         |                                                  |     |     |      |         |     |      |

| Access |                                         |                                                  |     |     |      |         |     |      |

| Reset  |                                         |                                                  |     |     |      |         |     |      |

| Bit    | 7                                       | 6                                                | 5   | 4   | 3    | 2       | 1   | 0    |

|        |                                         | EIC                                              | RTC | WDT | GCLK | SYSCTRL | PM  | PAC0 |

| Access |                                         | R/W                                              | R/W | R/W | R/W  | R/W     | R/W | R/W  |

| Reset  |                                         | 1                                                | 1   | 1   | 1    | 1       | 1   | 1    |

#### Bit 6 – EIC EIC APB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBA clock for the EIC is stopped. |

| 1     | The APBA clock for the EIC is enabled. |

# Bit 5 - RTC RTC APB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBA clock for the RTC is stopped. |

| 1     | The APBA clock for the RTC is enabled. |

# Bit 4 – WDT WDT APB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBA clock for the WDT is stopped. |

| 1     | The APBA clock for the WDT is enabled. |

# Bit 3 – GCLK GCLK APB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBA clock for the GCLK is stopped. |

| 1     | The APBA clock for the GCLK is enabled. |

# ATSAMHAXEXXA

RTC – Real-Time Counter

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 21.8.13 Interrupt Enable Set - MODE2

| Name:     | INTENSET        |

|-----------|-----------------|

| Offset:   | 0x07            |

| Reset:    | 0x00            |

| Property: | Write-Protected |

| Bit    | 7   | 6       | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|-----|---------|---|---|---|---|---|--------|

|        | OVF | SYNCRDY |   |   |   |   |   | ALARM0 |

| Access | R/W | R/W     |   |   |   |   |   | R/W    |

| Reset  | 0   | 0       |   |   |   |   |   | 0      |

**Bit 7 – OVF** Overflow Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will set the Overflow Interrupt Enable bit and enable the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The overflow interrupt is disabled. |

| 1     | The overflow interrupt is enabled.  |

# Bit 6 – SYNCRDY Synchronization Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Synchronization Ready Interrupt bit and enable the Synchronization Ready interrupt.

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The synchronization ready interrupt is disabled. |

| 1     | The synchronization ready interrupt is enabled.  |

# Bit 0 – ALARM0 Alarm 0 Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Alarm 0 Interrupt Enable bit and enable the Alarm 0 interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The alarm 0 interrupt is disabled. |

| 1     | The alarm 0 interrupt is enabled.  |

# 22.8.11 Interrupt Status

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTSTATUS<br>0x24<br>0x00000000<br>- |    |      |         |       |         |    |

|--------|-----------------------------------------|--------------------------------------|----|------|---------|-------|---------|----|

| Bit    | 31                                      | 30                                   | 29 | 28   | 27      | 26    | 25      | 24 |

|        |                                         |                                      |    |      |         |       |         |    |

| Access |                                         |                                      |    |      |         |       |         |    |

| Reset  |                                         |                                      |    |      |         |       |         |    |

| Bit    | 23                                      | 22                                   | 21 | 20   | 19      | 18    | 17      | 16 |

|        |                                         |                                      |    |      |         |       |         |    |

| Access |                                         |                                      |    |      |         |       |         |    |

| Reset  |                                         |                                      |    |      |         |       |         |    |

| Bit    | 15                                      | 14                                   | 13 | 12   | 11      | 10    | 9       | 8  |

|        |                                         |                                      |    |      |         | CHINT | n[11:8] |    |

| Access |                                         |                                      |    |      | R       | R     | R       | R  |

| Reset  |                                         |                                      |    |      | 0       | 0     | 0       | 0  |

|        |                                         |                                      |    |      |         |       |         |    |

| Bit    | 7                                       | 6                                    | 5  | 4    | 3       | 2     | 1       | 0  |

|        |                                         |                                      |    | CHIN | Γn[7:0] |       |         |    |

| Access | R                                       | R                                    | R  | R    | R       | R     | R       | R  |

| Reset  | 0                                       | 0                                    | 0  | 0    | 0       | 0     | 0       | 0  |

Bits 11:0 – CHINTn[11:0] Channel n Pending Interrupt [n=11..0]

This bit is set when Channel n has a pending interrupt/the interrupt request is received.

This bit is cleared when the corresponding Channel n interrupts are disabled or the interrupts sources are cleared.

#### 23.8.1 Control

Name:CTRLOffset:0x00Reset:0x00Property:Write-Protected, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access |   |   |   |   |   |   | R/W    | R/W   |

| Reset  |   |   |   |   |   |   | 0      | 0     |

#### Bit 1 – ENABLE Enable

Due to synchronization, there is delay from writing CTRL.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately, and the Synchronization Busy bit in the Status register (STATUS.SYNCBUSY) will be set. STATUS.SYNCBUSY will be cleared when the operation is complete.

| Value | Description          |

|-------|----------------------|

| 0     | The EIC is disabled. |

| 1     | The EIC is enabled.  |

# Bit 0 – SWRST Software Reset

Writing a zero to this bit has no effect.

Writing a one to this bit resets all registers in the EIC to their initial state, and the EIC will be disabled.

Writing a one to CTRL.SWRST will always take precedence, meaning that all other writes in the same write operation will be discarded.

Due to synchronization, there is a delay from writing CTRL.SWRST until the reset is complete. CTRL.SWRST and STATUS.SYNCBUSY will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no ongoing reset operation. |

| 1     | The reset operation is ongoing.      |

#### 24.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x0CReset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     |

|--------|---|---|---|---|---|---|-------|-------|

|        |   |   |   |   |   |   | ERROR | READY |

| Access |   |   |   |   |   |   | R/W   | R/W   |

| Reset  |   |   |   |   |   |   | 0     | 0     |

**Bit 1 – ERROR** Error Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the ERROR interrupt enable.

This bit will read as the current value of the ERROR interrupt enable.

# Bit 0 – READY NVM Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the READY interrupt enable.

This bit will read as the current value of the READY interrupt enable.

# Bit 1 – LOAD NVM Page Buffer Active Loading

This bit indicates that the NVM page buffer has been loaded with one or more words. Immediately after an NVM load has been performed, this flag is set. It remains set until a page write or a page buffer clear (PBCLR) command is given.

This bit can be cleared by writing a '1' to its bit location.

# Bit 0 – PRM Power Reduction Mode

This bit indicates the current NVM power reduction state. The NVM block can be set in power reduction mode in two ways: through the command interface or automatically when entering sleep with SLEEPPRM set accordingly.

PRM can be cleared in three ways: through AHB access to the NVM block, through the command interface (SPRM and CPRM) or when exiting sleep with SLEEPPRM set accordingly.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | NVM is not in power reduction mode. |

| 1     | NVM is in power reduction mode.     |

# 25. PORT - I/O Pin Controller

# 25.1 Overview

The IO Pin Controller (PORT) controls the I/O pins of the device. The I/O pins are organized in a series of groups, collectively referred to as a PORT group. Each PORT group can have up to 32 pins that can be configured and controlled individually or as a group. The number of PORT groups on a device may depend on the package/number of pins. Each pin may either be used for general-purpose I/O under direct application control or be assigned to an embedded device peripheral. When used for general-purpose I/O, each pin can be configured as input or output, with highly configurable driver and pull settings.

All I/O pins have true read-modify-write functionality when used for general-purpose I/O; the direction or the output value of one or more pins may be changed (set, reset or toggled) explicitly without unintentionally changing the state of any other pins in the same port group by a single, atomic 8-, 16- or 32-bit write.

The PORT is connected to the high-speed bus matrix through an AHB/APB bridge. The Pin Direction, Data Output Value and Data Input Value registers may also be accessed using the low-latency CPU local bus (IOBUS; ARM<sup>®</sup> single-cycle I/O port).

# 25.2 Features

- Selectable input and output configuration for each individual pin

- Software-controlled multiplexing of peripheral functions on I/O pins

- Flexible pin configuration through a dedicated Pin Configuration register

- Configurable output driver and pull settings:

- Totem-pole (push-pull)

- Pull configuration

- Driver strength

- Configurable input buffer and pull settings:

- Internal pull-up or pull-down

- Input sampling criteria

- Input buffer can be disabled if not needed for lower power consumption

#### 26.8.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG    |

|-----------|------------|

| Offset:   | 0x18       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   |

|--------|------|------|------|------|------|------|------|------|

|        |      |      |      |      | EVDn | EVDn | EVDn | EVDn |

| Access |      |      |      |      | R/W  | R/W  | R/W  | R/W  |

| Reset  |      |      |      |      | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|        |      |      |      |      | OVRn | OVRn | OVRn | OVRn |

| Access |      |      |      |      | R/W  | R/W  | R/W  | R/W  |

| Reset  |      |      |      |      | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|        | EVDn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | OVRn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

**Bits 27,26,25,24,15,14,13,12,11,10,9,8 – EVDn** Channel n Event Detection [n=11..0] This flag is set on the next CLK\_EVSYS\_APB cycle when an event is being propagated through the channel, and an interrupt request will be generated if INTENCLR/SET.EVDn is one.

When the event channel path is asynchronous, the EVDn interrupt flag will not be set.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Event Detected Channel n interrupt flag.

#### Bits 19,18,17,16,7,6,5,4,3,2,1,0 – OVRn Channel n Overrun [n=11..0]

This flag is set on the next CLK\_EVSYS cycle after an overrun channel condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVRn is one.

When the event channel path is asynchronous, the OVRn interrupt flag will not be set.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Overrun Channel n interrupt flag.

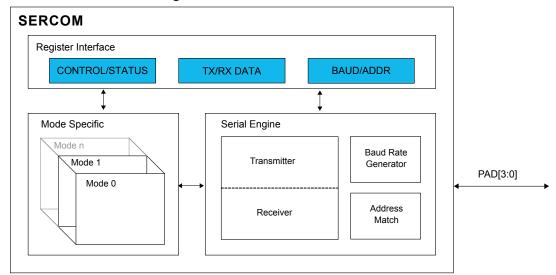

# 27.3 Block Diagram

Figure 27-1. SERCOM Block Diagram

# 27.4 Signal Description

See the respective SERCOM mode chapters for details.

# Related Links SERCOM USART SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

# 27.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 27.5.1 I/O Lines

Using the SERCOM I/O lines requires the I/O pins to be configured using port configuration (PORT).

The SERCOM has four internal pads, PAD[3:0], and the signals from I2C, SPI and USART are routed through these SERCOM pads via a multiplexer. The configuration of the multiplexer is available from the different SERCOM modes. Refer to the mode specific chapters for details.

# **Related Links**

SERCOM USART SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit PORT: IO Pin Controller Block Diagram

# 27.5.2 Power Management

The SERCOM can operate in any Sleep mode provided the selected clock source is running. SERCOM interrupts can be configured to wake the device from Sleep modes.

When a data packet is received or sent, INTFLAG.DRDY will be set. After receiving data, the I<sup>2</sup>C slave will send an acknowledge according to CTRLB.ACKACT.

# Case 1: Data received

INTFLAG.DRDY is set, and SCL is held low, pending for SW interaction.

# Case 2: Data sent

When a byte transmission is successfully completed, the INTFLAG.DRDY interrupt flag is set. If NACK is received, indicated by STATUS.RXNACK=1, the I<sup>2</sup>C slave must expect a stop or a repeated start to be received. The I<sup>2</sup>C slave must release the data line to allow the I<sup>2</sup>C master to generate a stop or repeated start. Upon detecting a stop condition, the Stop Received bit in the Interrupt Flag register (INTFLAG.PREC) will be set and the I<sup>2</sup>C slave will return to IDLE state.

# High-Speed Mode

When the I<sup>2</sup>C slave is configured in High-speed mode (*Hs*, CTRLA.SPEED=0x2) and CTRLA.SCLSM=1, switching between Full-speed and High-speed modes is automatic. When the slave recognizes a START followed by a master code transmission and a NACK, it automatically switches to High-speed mode and sets the High-speed status bit (STATUS.HS). The slave will then remain in High-speed mode until a STOP is received.

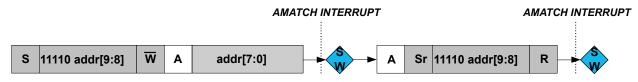

# 10-Bit Addressing

When 10-bit addressing is enabled (ADDR.TENBITEN=1), the two address bytes following a START will be checked against the 10-bit slave address recognition. The first byte of the address will always be acknowledged, and the second byte will raise the address interrupt flag, see 10-bit Addressing.

If the transaction is a write, then the 10-bit address will be followed by *N* data bytes.

If the operation is a read, the 10-bit address will be followed by a repeated START and reception of '11110 ADDR[9:8] 1', and the second address interrupt will be received with the DIR bit set. The slave matches on the second address as it it was addressed by the previous 10-bit address.

# Figure 30-12. 10-bit Addressing

# PMBus Group Command

When the PMBus Group Command bit in the CTRLB register is set (CTRLB.GCMD=1) and 7-bit addressing is used, INTFLAG.PREC will be set if the slave has been addressed since the last STOP condition. When CTRLB.GCMD=0, a STOP condition without address match will not be set INTFLAG.PREC.

The group command protocol is used to send commands to more than one device. The commands are sent in one continuous transmission with a single STOP condition at the end. When the STOP condition is detected by the slaves addressed during the group command, they all begin executing the command they received.

PMBus Group Command Example shows an example where this slave, bearing ADDRESS 1, is addressed after a repeated START condition. There can be multiple slaves addressed before and after this slave. Eventually, at the end of the group command, a single STOP is generated by the master. At this point a STOP interrupt is asserted.

- Error (ERROR)

- Slave on Bus (SB)

- Master on Bus (MB)

Each interrupt source has its own interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the interrupt condition is meet. Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request active until the interrupt flag is cleared, the interrupt is disabled or the I<sup>2</sup>C is reset. See the INTFLAG register for details on how to clear interrupt flags.

The value of INTFLAG indicates which interrupt is executed. Note that interrupts must be globally enabled for interrupt requests. Refer to *Nested Vector Interrupt Controller* for details.

# **Related Links**

Nested Vector Interrupt Controller

#### 30.6.4.3 Events

Not applicable.

#### 30.6.5 Sleep Mode Operation

#### I<sup>2</sup>C Master Operation

The generic clock (GCLK\_SERCOMx\_CORE) will continue to run in idle sleep mode. If the Run In Standby bit in the Control A register (CTRLA.RUNSTDBY) is '1', the GLK\_SERCOMx\_CORE will also run in standby sleep mode. Any interrupt can wake up the device.

If CTRLA.RUNSTDBY=0, the GLK\_SERCOMx\_CORE will be disabled after any ongoing transaction is finished. Any interrupt can wake up the device.

# I<sup>2</sup>C Slave Operation

Writing CTRLA.RUNSTDBY=1 will allow the Address Match interrupt to wake up the device.

When CTRLA.RUNSTDBY=0, all receptions will be dropped.

# 30.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Command bits in CTRLB register (CTRLB.CMD)

- Write to Bus State bits in the Status register (STATUS.BUSSTATE)

- Address bits in the Address register (ADDR.ADDR) when in master operation.

The following registers are synchronized when written:

• Data (DATA) when in master operation

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

# ATSAMHAXEXXA

SERCOM I2C – Inter-Integrated Circuit

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | General call address recognition disabled. |

| 1     | General call address recognition enabled.  |

- 1. Enable the TCC bus clock (CLK\_TCCx\_APB).

- 2. If Capture mode is required, enable the channel in capture mode by writing a '1' to the Capture Enable bit in the Control A register (CTRLA.CPTEN).

Optionally, the following configurations can be set before enabling TCC:

- 1. Select PRESCALER setting in the Control A register (CTRLA.PRESCALER).

- 2. Select Prescaler Synchronization setting in Control A register (CTRLA.PRESCSYNC).

- 3. If down-counting operation is desired, write the Counter Direction bit in the Control B Set register (CTRLBSET.DIR) to '1'.

- 4. Select the Waveform Generation operation in the WAVE register (WAVE.WAVEGEN).

- 5. Select the Waveform Output Polarity in the WAVE register (WAVE.POL).

- 6. The waveform output can be inverted for the individual channels using the Waveform Output Invert Enable bit group in the Driver register (DRVCTRL.INVEN).

# 32.6.2.2 Enabling, Disabling, and Resetting

The TCC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TCC is disabled by writing a zero to CTRLA.ENABLE.

The TCC is reset by writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TCC, except DBGCTRL, will be reset to their initial state, and the TCC will be disabled. Refer to Control A (CTRLA) register for details.

The TCC should be disabled before the TCC is reset to avoid undefined behavior.

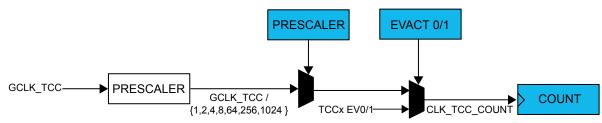

#### 32.6.2.3 Prescaler Selection

The GCLK\_TCCx clock is fed into the internal prescaler.

The prescaler consists of a counter that counts up to the selected prescaler value, whereupon the output of the prescaler toggles.

If the prescaler value is higher than one, the counter update condition can be optionally executed on the next GCLK\_TCC clock pulse or the next prescaled clock pulse. For further details, refer to the Prescaler (CTRLA.PRESCALER) and Counter Synchronization (CTRLA.PRESYNC) descriptions.

Prescaler outputs from 1 to 1/1024 are available. For a complete list of available prescaler outputs, see the register description for the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

Note: When counting events, the prescaler is bypassed.

The joint stream of prescaler ticks and event action ticks is called CLK\_TCC\_COUNT.

# Figure 32-2. Prescaler

# 32.6.2.4 Counter Operation

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TCC clock input (CLK\_TCC\_COUNT). A counter clear or reload mark the end of current counter cycle and the start of a new one.

#### 32.8.12 Interrupt Flag Status and Clear

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x2C<br>0x00000000<br>- |        |        |     |     |     |     |

|--------|-----------------------------------------|------------------------------------|--------|--------|-----|-----|-----|-----|

| Bit    | 23                                      | 22                                 | 21     | 20     | 19  | 18  | 17  | 16  |

|        |                                         |                                    |        |        | MCx | MCx | MCx | MCx |

| Access |                                         |                                    |        |        | R/W | R/W | R/W | R/W |

| Reset  |                                         |                                    |        |        | 0   | 0   | 0   | 0   |

|        |                                         |                                    |        |        |     |     |     |     |

| Bit    | 15                                      | 14                                 | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx                                  | FAULTx                             | FAULTB | FAULTA | DFS |     |     |     |

| Access | R/W                                     | R/W                                | R/W    | R/W    | R/W |     |     |     |

| Reset  | 0                                       | 0                                  | 0      | 0      | 0   |     |     |     |

|        |                                         |                                    |        |        |     |     |     |     |

| Bit    | 7                                       | 6                                  | 5      | 4      | 3   | 2   | 1   | 0   |

|        |                                         |                                    |        |        | ERR | CNT | TRG | OVF |

| Access |                                         | 1                                  |        | •      | R/W | R/W | R/W | R/W |

| Reset  |                                         |                                    |        |        | 0   | 0   | 0   | 0   |

Bits 19,18,17,16 – MCx Match or Capture Channel x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a match with the compare condition or once CCx register contain a valid capture value.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In Capture operation, this flag is automatically cleared when CCx register is read.

# Bits 15,14 – FAULTx Non-Recoverable Fault x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Non-Recoverable Fault x occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Non-Recoverable Fault x interrupt flag.

# Bit 13 – FAULTB Recoverable Fault B Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

# Bit 12 – FAULTA Recoverable Fault A Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

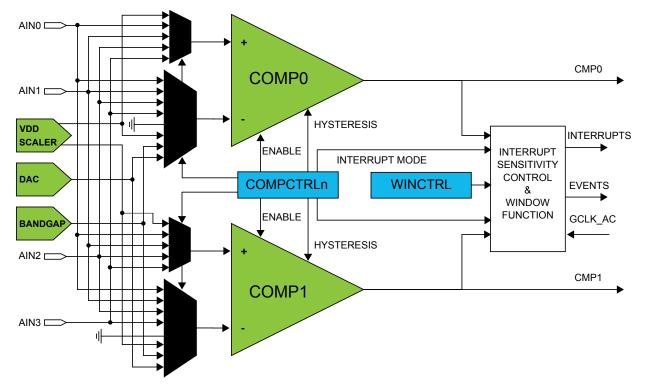

# 34.3 Block Diagram

Figure 34-1. Analog Comparator Block Diagram

# 34.4 Signal Description

| Signal  | Description    | Туре               |  |  |

|---------|----------------|--------------------|--|--|

| AIN[30] | Analog input   | Comparator inputs  |  |  |

| CMP[10] | Digital output | Comparator outputs |  |  |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

# **Related Links**

I/O Multiplexing and Considerations

# 34.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 34.5.1 I/O Lines

Using the AC's I/O lines requires the I/O pins to be configured. Refer to *PORT - I/O Pin Controller* for details.

#### **Related Links**

PORT - I/O Pin Controller

- CPU, AHB and APBn clocks undivided

- The Following AHB Module Clocks are Running: NVMCTRL, HPB2 Bridge, HPB1 Bridge, HPB0 Bridge

- All other AHB clocks stopped

- The Following Peripheral Clocks Running: PM, SYSCTRL

- All other peripheral clocks stopped

- I/Os are Inactive With Internal Pull-Up

- CPU in IDLE0 Mode

- Cache Enabled

- BOD33 Disabled

In these default conditions, the power consumption  $I_{default}$  is measured.

Operating mode for each peripheral in turn:

- Configure and Enable the Peripheral GCLK When Relevant (See Conditions)

- Unmask the Peripheral Clock

- Enable the Peripheral (When Relevant)

- Set CPU in IDLE0 Mode

- Measurement I<sub>periph</sub>

- Wake-Up CPU via EIC (Async: Level Detection, Filtering Disabled)

- Disable the Peripheral, When Relevant

- Mask the Peripheral Clock

- Disable the Peripheral GCLK When Relevant (See Conditions)

Each peripheral power consumption provided is the value ( $I_{periph} - I_{default}$ ), using the same measurement method as for global power consumption measurement

| Table 37-15. | Typical | Peripheral | Current | Consumption |

|--------------|---------|------------|---------|-------------|

|--------------|---------|------------|---------|-------------|

| Peripheral         | Conditions                                        | Typical | Unit |

|--------------------|---------------------------------------------------|---------|------|

| RTC                | fGCLK_RTC = 32kHz,<br>32bit counter mode          | 7.4     | μA   |

| WDT                | fGCLK_WDT = 32kHz,<br>normal mode with EW         | 5.5     |      |

| AC                 | Both fGCLK = 8MHz,<br>Enable both COMP            | 31.3    |      |

| TCx <sup>(1)</sup> | fGCLK = 8MHz, Enable<br>+ COUNTER in 8bit<br>mode | 50      |      |

| TCC2               | fGCLK = 8MHz, Enable<br>+ COUNTER                 | 95.5    |      |

| TCC1               | fGCLK = 8MHz, Enable<br>+ COUNTER                 | 167.5   |      |

| TCC0               | fGCLK = 8MHz, Enable<br>+ COUNTER                 | 180.3   |      |