Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 48MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus SBC, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 1K x 8                                                                          |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 0V ~ 3.8V                                                                       |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TC)                                                              |

| Mounting Type              | Surface Mount, Wettable Flank                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 32-VQFN (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamha1e15a-mbt-bvao |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 15. DSU - Device Service Unit

## 15.1 Overview

The Device Service Unit (DSU) provides a means of detecting debugger probes. It enables the ARM Debug Access Port (DAP) to have control over multiplexed debug pads and CPU reset. The DSU also provides system-level services to debug adapters in an ARM debug system. It implements a CoreSight Debug ROM that provides device identification as well as identification of other debug components within the system. Hence, it complies with the ARM Peripheral Identification specification. The DSU also provides system services to applications that need memory testing, as required for IEC60730 Class B compliance, for example. The DSU can be accessed simultaneously by a debugger and the CPU, as it is connected on the High-Speed Bus Matrix. For security reasons, some of the DSU features will be limited or unavailable when the device is protected by the NVMCTRL security bit.

### Related Links

System Services Availability when Accessed Externally and Device is Protected NVMCTRL – Nonvolatile Memory Controller Security Bit

## 15.2 Features

- CPU reset extension

- Debugger probe detection (Cold- and Hot-Plugging)

- Chip-Erase command and status

- 32-bit cyclic redundancy check (CRC32) of any memory accessible through the bus matrix

- ARM<sup>®</sup> CoreSight<sup>™</sup> compliant device identification

- Two debug communications channels

- Debug access port security filter

- Onboard memory built-in self-test (MBIST)

## 15.13.5 Length

| Name:     | LENGTH               |

|-----------|----------------------|

| Offset:   | 0x0008               |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

| Bit    | 31            | 30  | 29   | 28      | 27       | 26  | 25  | 24  |  |

|--------|---------------|-----|------|---------|----------|-----|-----|-----|--|

|        | LENGTH[29:22] |     |      |         |          |     |     |     |  |

| Access | R/W           | R/W | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0    | 0       | 0        | 0   | 0   | 0   |  |

|        |               |     |      |         |          |     |     |     |  |

| Bit    | 23            | 22  | 21   | 20      | 19       | 18  | 17  | 16  |  |

|        |               |     |      | LENGT   | H[21:14] |     |     |     |  |

| Access | R/W           | R/W | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0    | 0       | 0        | 0   | 0   | 0   |  |

|        |               |     |      |         |          |     |     |     |  |

| Bit    | 15            | 14  | 13   | 12      | 11       | 10  | 9   | 8   |  |

|        |               |     |      | LENGT   | H[13:6]  |     |     |     |  |

| Access | R/W           | R/W | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0    | 0       | 0        | 0   | 0   | 0   |  |

|        |               |     |      |         |          |     |     |     |  |

| Bit    | 7             | 6   | 5    | 4       | 3        | 2   | 1   | 0   |  |

|        |               |     | LENG | TH[5:0] |          |     |     |     |  |

| Access | R/W           | R/W | R/W  | R/W     | R/W      | R/W |     |     |  |

| Reset  | 0             | 0   | 0    | 0       | 0        | 0   |     |     |  |

## Bits 31:2 - LENGTH[29:0] Length

Length in words needed for memory operations.

## ATSAMHAXEXXA Clock System

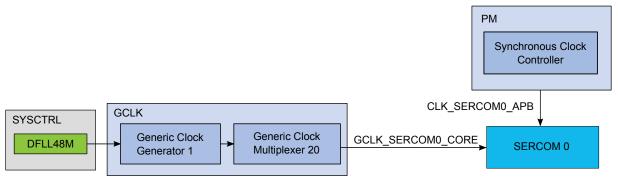

SERCOM0. The SERCOM0 interface, clocked by CLK\_SERCOM0\_APB, has been unmasked in the APBC Mask register in the PM.

### Figure 16-2. Example of SERCOM clock

## 16.2 Synchronous and Asynchronous Clocks

As the CPU and the peripherals can be in different clock domains, i.e. they are clocked from different clock sources and/or with different clock speeds, some peripheral accesses by the CPU need to be synchronized. In this case the peripheral includes a SYNCBUSY status register that can be used to check if a sync operation is in progress.

For a general description, see Register Synchronization. Some peripherals have specific properties described in their individual sub-chapter "Synchronization".

In the datasheet, references to Synchronous Clocks are referring to the CPU and bus clocks, while asynchronous clocks are generated by the Generic Clock Controller (GCLK).

## 16.3 Register Synchronization

There are two different register synchronization schemes implemented on this device: *common synchronizer register synchronization* and *distributed synchronizer register synchronization*.

The modules using a common synchronizer register synchronization are: GCLK, WDT, RTC, EIC, TC, ADC, AC and DAC.

The modules adopting a distributed synchronizer register synchronization are: SERCOM USART, SERCOM SPI, SERCOM I2C.

### 16.3.1 Common Synchronizer Register Synchronization

### 16.3.1.1 Overview

All peripherals are composed of one digital bus interface connected to the APB or AHB bus and running from a corresponding clock in the Main Clock domain, and one peripheral core running from the peripheral Generic Clock (GCLK).

Communication between these clock domains must be synchronized. This mechanism is implemented in hardware, so the synchronization process takes place even if the peripheral generic clock is running from the same clock source and on the same frequency as the bus interface.

All registers in the bus interface are accessible without synchronization. All registers in the peripheral core are synchronized when written. Some registers in the peripheral core are synchronized when read.

© 2017 Microchip Technology Inc.

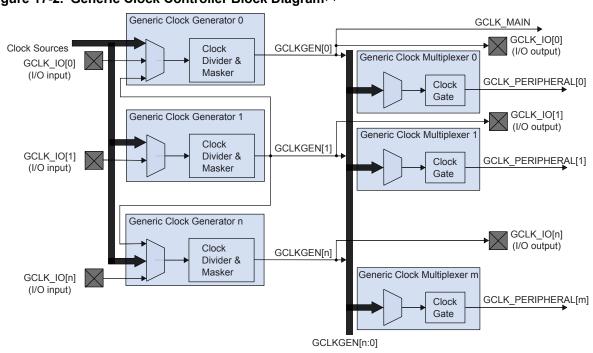

### Figure 17-2. Generic Clock Controller Block Diagram<sup>(1)</sup>

Note: 1. If GENCTRL.SRC=0x01(GCLKIN), the GCLK\_IO is set as an input.

# 17.4 Signal Description

### Table 17-1. Signal Description

| Signal Name Type         |  |  | Description                            |

|--------------------------|--|--|----------------------------------------|

| GCLK_IO[7:0] Digital I/O |  |  | Clock source for Generators when input |

|                          |  |  | Generic Clock signal when output       |

Refer to PORT Function Multiplexing table in I/O Multiplexing and Considerations for details on the pin mapping for this peripheral.

**Note:** One signal can be mapped on several pins.

### Related Links

I/O Multiplexing and Considerations

### 17.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 17.5.1 I/O Lines

Using the GCLK I/O lines requires the I/O pins to be configured.

#### **Related Links**

PORT - I/O Pin Controller

### 18.8.3 CPU Clock Select

| Name:     | CPUSEL          |

|-----------|-----------------|

| Offset:   | 0x08            |

| Reset:    | 0x00            |

| Property: | Write-Protected |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1           | 0   |

|--------|---|---|---|---|---|-----|-------------|-----|

|        |   |   |   |   |   |     | CPUDIV[2:0] |     |

| Access |   |   |   |   |   | R/W | R/W         | R/W |

| Reset  |   |   |   |   |   | 0   | 0           | 0   |

## Bits 2:0 – CPUDIV[2:0] CPU Prescaler Selection

These bits define the division ratio of the main clock prescaler (2<sup>n</sup>).

| CPUDIV[2:0] | Name   | Description   |

|-------------|--------|---------------|

| 0x0         | DIV1   | Divide by 1   |

| 0x1         | DIV2   | Divide by 2   |

| 0x2         | DIV4   | Divide by 4   |

| 0x3         | DIV8   | Divide by 8   |

| 0x4         | DIV16  | Divide by 16  |

| 0x5         | DIV32  | Divide by 32  |

| 0x6         | DIV64  | Divide by 64  |

| 0x7         | DIV128 | Divide by 128 |

The oscillator is disabled by writing a zero to the Enable bit (XOSC32K.ENABLE) in the 32kHz External Crystal Oscillator Control register while keeping the other bits unchanged. Writing to the XOSC32K.ENABLE bit while writing to other bits may result in unpredictable behavior. The oscillator remains enabled in all sleep modes if it has been enabled beforehand. The start-up time of the 32kHz External Crystal Oscillator is selected by writing to the Oscillator Start-Up Time bit group (XOSC32K.STARTUP) in the in the 32kHz External Crystal Oscillator Control register. The SYSCTRL masks the oscillator output during the start-up time to ensure that no unstable clock propagates to the digital logic. The 32kHz External Crystal Oscillator Ready bit (PCLKSR.XOSC32KRDY) in the Power and Clock Status register is set when the user-selected startup time is over. An interrupt is generated on a zero-to-one transition of PCLKSR.XOSC32KRDY if the 32kHz External Crystal Oscillator Ready bit (INTENSET.XOSC32KRDY) in the Interrupt Enable Set Register is set.

As a crystal oscillator usually requires a very long start-up time (up to one second), the 32kHz External Crystal Oscillator will keep running across resets, except for power-on reset (POR).

XOSC32K can provide two clock outputs when connected to a crystal. The XOSC32K has a 32.768kHz output enabled by writing a one to the 32kHz External Crystal Oscillator 32kHz Output Enable bit (XOSC32K.EN32K) in the 32kHz External Crystal Oscillator Control register. XOSC32K.EN32K is only usable when XIN32 is connected to a crystal, and not when an external digital clock is applied on XIN32.

**Note:** Do not enter standby mode when an oscillator is in start-up: Wait for the OSCxRDY bit in SYSCTRL.PCLKSR register to be set before going into standby mode.

### **Related Links**

GCLK - Generic Clock Controller

### 19.6.4 32kHz Internal Oscillator (OSC32K) Operation

The OSC32K provides a tunable, low-speed and low-power clock source.

The OSC32K can be used as a source for the generic clock generators, as described in the *GCLK* – *Generic Clock Controller*.

The OSC32K is disabled by default. The OSC32K is enabled by writing a one to the 32kHz Internal Oscillator Enable bit (OSC32K.ENABLE) in the 32kHz Internal Oscillator Control register. It is disabled by writing a zero to OSC32K.ENABLE. The OSC32K has a 32.768kHz output enabled by writing a one to the 32kHz Internal Oscillator 32kHz Output Enable bit (OSC32K.EN32K).

The frequency of the OSC32K oscillator is controlled by the value in the 32kHz Internal Oscillator Calibration bits (OSC32K.CALIB) in the 32kHz Internal Oscillator Control register. The OSC32K.CALIB value must be written by the user. Flash Factory Calibration values are stored in the NVM Software Calibration Area (refer to *NVM Software Calibration Area Mapping*). When writing to the Calibration bits, the user must wait for the PCLKSR.OSC32KRDY bit to go high before the value is committed to the oscillator.

### **Related Links**

GCLK - Generic Clock Controller NVM Software Calibration Area Mapping

### 19.6.5 32kHz Ultra Low Power Internal Oscillator (OSCULP32K) Operation

The OSCULP32K provides a tunable, low-speed and ultra-low-power clock source. The OSCULP32K is factory-calibrated under typical voltage and temperature conditions. The OSCULP32K should be preferred to the OSC32K whenever the power requirements are prevalent over frequency stability and accuracy.

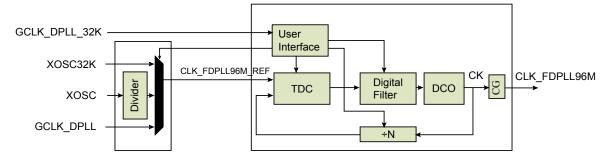

The XOSC source can be divided inside the FDPLL96M. The user must make sure that the programmable clock divider and XOSC frequency provides a valid CLK\_FDPLL96M\_REF clock frequency that meets the FDPLL96M input frequency range.

The output clock of the FDPLL96M is CLK\_FDPLL96M. The state of the CLK\_FDPLL96M clock only depends on the FDPLL96M internal control of the final clock gater CG.

The FDPLL96M requires a 32kHz clock from the GCLK when the FDPLL96M internal lock timer is used. This clock must be configured and enabled in the Generic Clock Controller before using the FDPLL96M. Refer to *GCLK* – *Generic Clock Controller* for details.

### Table 19-3. Generic Clock Input for FDPLL96M

| Generic Clock        | FDPLL96M                              |  |  |

|----------------------|---------------------------------------|--|--|

| FDPLL96M 32kHz clock | GCLK_DPLL_32K for internal lock timer |  |  |

| FDPLL96M             | GCLK_DPLL for CLK_FDPLL96M_REF        |  |  |

### **Related Links**

GCLK - Generic Clock Controller

### 19.6.8.2 Block Diagram

### 19.6.8.3 Principle of Operation

The task of the FDPLL96M is to maintain coherence between the input reference clock signal (CLK\_FDPLL96M\_REF) and the respective output frequency CK via phase comparison. The FDPLL96M supports three independent sources of clocks; XOSC32K, XOSC and GCLK\_DPLL. When the FDPLL96M is enabled, the relationship between the reference clock (CLK\_FDPLL96M\_REF) frequency and the output clock (CLK\_FDPLL96M) frequency is defined below.

$$f_{clk\_fdpll96m} = f_{clk\_fdpll96m\_ref} \times \left( LDR + 1 + \frac{LDRFRAC}{16} \right)$$

Where LDR is the loop divider ratio integer part, LDRFRAC is the loop divider ratio fractional part,  $f_{ckrx}$  is the frequency of the selected reference clock and  $f_{ck}$  is the frequency of the FDPLL96M output clock. As previously stated a clock divider exist between XOSC and CLK\_FDPLL96M\_REF. The frequency between the two clocks is defined below.

$$f_{clk\_fdpll96m\_ref} = f_{xosc} \times \left(\frac{1}{2 \times (DIV + 1)}\right)$$

When the FDPLL96M is disabled, the output clock is reset. If the loop divider ratio fractional part (DPLLRATIO.LDRFRAC) field is reset, the FDPLL96M works in integer mode, otherwise the fractional

© 2017 Microchip Technology Inc.

## **DMAC – Direct Memory Access Controller**

| TRIGACT[1:0] | Name        | Description                                 |

|--------------|-------------|---------------------------------------------|

| 0x2          | BEAT        | One trigger required for each beat transfer |

| 0x3          | TRANSACTION | One trigger required for each transaction   |

### Bits 13:8 – TRIGSRC[5:0] Trigger Source

These bits define the peripheral trigger which is source of the transfer. For details on trigger selection and trigger modes, refer to Transfer Triggers and Actions and CHCTRLB.TRIGACT.

| Value | Name       | Description                  |

|-------|------------|------------------------------|

| 0x00  | DISABLE    | Only software/event triggers |

| 0x01  | SERCOM0 RX | SERCOM0 RX Trigger           |

| 0x02  | SERCOM0 TX | SERCOM0 TX Trigger           |

| 0x03  | SERCOM1 RX | SERCOM1 RX Trigger           |

| 0x04  | SERCOM1 TX | SERCOM1 TX Trigger           |

| 0x05  | SERCOM2 RX | SERCOM2 RX Trigger           |

| 0x06  | SERCOM2 TX | SERCOM2 TX Trigger           |

| 0x07  | SERCOM3 RX | SERCOM3 RX Trigger           |

| 0x08  | SERCOM3 TX | SERCOM3 TX Trigger           |

| 0x09  | SERCOM4 RX | SERCOM4 RX Trigger           |

| 0x0A  | SERCOM4 TX | SERCOM4 TX Trigger           |

| 0x0B  | TCC0 OVF   | TCC0 Overflow Trigger        |

| 0x0C  | ТСС0 МС0   | TCC0 Match/Compare 0 Trigger |

| 0x0D  | TCC0 MC1   | TCC0 Match/Compare 1 Trigger |

| 0x0E  | TCC0 MC2   | TCC0 Match/Compare 2 Trigger |

| 0x0F  | TCC0 MC3   | TCC0 Match/Compare 3 Trigger |

| 0x10  | TCC1 OVF   | TCC1 Overflow Trigger        |

| 0x11  | TCC1 MC0   | TCC1 Match/Compare 0 Trigger |

| 0x12  | TCC1 MC1   | TCC1 Match/Compare 1 Trigger |

| 0x13  | TCC2 OVF   | TCC2 Overflow Trigger        |

| 0x14  | TCC2 MC0   | TCC2 Match/Compare 0 Trigger |

| 0x15  | TCC2 MC1   | TCC2 Match/Compare 1 Trigger |

| 0x16  | TC0 OVF    | TC0 Overflow Trigger         |

| 0x17  | TC0 MC0    | TC0 Match/Compare 0 Trigger  |

| 0x18  | TC0 MC1    | TC0 Match/Compare 1 Trigger  |

| 0x19  | TC1 OVF    | TC1 Overflow Trigger         |

| 0x1A  | TC1 MC0    | TC1 Match/Compare 0 Trigger  |

| 0x1B  | TC1 MC1    | TC1 Match/Compare 1 Trigger  |

| 0x1C  | TC2 OVF    | TC2 Overflow Trigger         |

| 0x1D  | TC2 MC0    | TC2 Match/Compare 0 Trigger  |

| 0x1E  | TC2 MC1    | TC2 Match/Compare 1 Trigger  |

| 0x1F  | TC3 OVF    | TC3 Overflow Trigger         |

| 0x20  | TC3 MC0    | TC3 Match/Compare 0 Trigger  |

| 0x21  | TC3 MC1    | TC3 Match/Compare 1 Trigger  |

| 0x22  | TC4 OVF    | TC4 Overflow Trigger         |

| 0x23  | TC4 MC0    | TC4 Match/Compare 0 Trigger  |

| 0x24  | TC4 MC1    | TC4 Match/Compare 1 Trigger  |

| 0x25  | ADC RESRDY | ADC Result Ready Trigger     |

### 25.9.2 Data Direction Clear

| Name:     | DIRCLR               |

|-----------|----------------------|

| Offset:   | 0x04                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to set one or more I/O pins as an input, without doing a read-modify-write operation. Changes in this register will also be reflected in the Data Direction (DIR), Data Direction Toggle (DIRTGL) and Data Direction Set (DIRSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31            | 30 | 29 | 28     | 27       | 26 | 25 | 24 |  |

|--------|---------------|----|----|--------|----------|----|----|----|--|

|        | DIRCLR[31:24] |    |    |        |          |    |    |    |  |

| Access | RW            | RW | RW | RW     | RW       | RW | RW | RW |  |

| Reset  | 0             | 0  | 0  | 0      | 0        | 0  | 0  | 0  |  |

|        |               |    |    |        |          |    |    |    |  |

| Bit    | 23            | 22 | 21 | 20     | 19       | 18 | 17 | 16 |  |

|        |               |    |    | DIRCLF | R[23:16] |    |    |    |  |

| Access | RW            | RW | RW | RW     | RW       | RW | RW | RW |  |

| Reset  | 0             | 0  | 0  | 0      | 0        | 0  | 0  | 0  |  |

|        |               |    |    |        |          |    |    |    |  |

| Bit    | 15            | 14 | 13 | 12     | 11       | 10 | 9  | 8  |  |

|        |               |    |    | DIRCL  | R[15:8]  |    |    |    |  |

| Access | RW            | RW | RW | RW     | RW       | RW | RW | RW |  |

| Reset  | 0             | 0  | 0  | 0      | 0        | 0  | 0  | 0  |  |

|        |               |    |    |        |          |    |    |    |  |

| Bit    | 7             | 6  | 5  | 4      | 3        | 2  | 1  | 0  |  |

|        | DIRCLR[7:0]   |    |    |        |          |    |    |    |  |

| Access | RW            | RW | RW | RW     | RW       | RW | RW | RW |  |

| Reset  | 0             | 0  | 0  | 0      | 0        | 0  | 0  | 0  |  |

|        |               |    |    |        |          |    |    |    |  |

### Bits 31:0 – DIRCLR[31:0] Port Data Direction Clear

Writing a '0' to a bit has no effect.

Writing a '1' to a bit will clear the corresponding bit in the DIR register, which configures the I/O pin as an input.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration. |

| 1     | The corresponding I/O pin in the PORT group is configured as input.      |

## **EVSYS – Event System**

| PATH[1:0] | Name           | Description         |

|-----------|----------------|---------------------|

| 0x0       | SYNCHRONOUS    | Synchronous path    |

| 0x1       | RESYNCHRONIZED | Resynchronized path |

| 0x2       | ASYNCHRONOUS   | Asynchronous path   |

| 0x3       |                | Reserved            |

### Bits 22:16 – EVGEN[6:0] Event Generator Selection

These bits are used to choose which event generator to connect to the selected channel.

| Value | Event Generator | Description                                  |

|-------|-----------------|----------------------------------------------|

| 0x00  | NONE            | No event generator selected                  |

| 0x01  | RTC CMP0        | Compare 0 (mode 0 and 1) or Alarm 0 (mode 2) |

| 0x02  | RTC CMP1        | Compare 1                                    |

| 0x03  | RTC OVF         | Overflow                                     |

| 0x04  | RTC PER0        | Period 0                                     |

| 0x05  | RTC PER1        | Period 1                                     |

| 0x06  | RTC PER2        | Period 2                                     |

| 0x07  | RTC PER3        | Period 3                                     |

| 0x08  | RTC PER4        | Period 4                                     |

| 0x09  | RTC PER5        | Period 5                                     |

| 0x0A  | RTC PER6        | Period 6                                     |

| 0x0B  | RTC PER7        | Period 7                                     |

| 0x0C  | EIC EXTINT0     |                                              |

| 0x0D  | EIC EXTINT1     | External Interrupt 1                         |

| 0x0E  | EIC EXTINT2     | External Interrupt 2                         |

| 0x0F  | EIC EXTINT3     | External Interrupt 3                         |

| 0x10  | EIC EXTINT4     | External Interrupt 4                         |

| 0x11  | EIC EXTINT5     | External Interrupt 5                         |

| 0x12  | EIC EXTINT6     | External Interrupt 6                         |

| 0x13  | EIC EXTINT7     | External Interrupt 7                         |

| 0x14  | EIC EXTINT8     | External Interrupt 8                         |

| 0x15  | EIC EXTINT9     | External Interrupt 9                         |

| 0x16  | EIC EXTINT10    | External Interrupt 10                        |

| 0x17  | EIC EXTINT11    | External Interrupt 11                        |

## ATSAMHAXEXXA SERCOM USART

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

# ATSAMHAXEXXA SERCOM I2C – Inter-Integrated Circuit

## 30.7 Register Summary - I2C Slave

| Offset | Name       | Bit Pos. |          |         |       |             |           |        |              |        |

|--------|------------|----------|----------|---------|-------|-------------|-----------|--------|--------------|--------|

|        |            | 7:0      | RUNSTDBY |         |       |             | MODE[2:0] |        | ENABLE       | SWRST  |

| 0x00   |            | 15:8     |          |         |       |             |           |        |              |        |

|        | CTRLA      | 23:16    | SEXTTOEN |         | SDAHO | DLD[1:0]    |           |        |              | PINOUT |

|        |            | 31:24    |          | LOWTOUT |       |             | SCLSM     |        | SPEE         | D[1:0] |

|        |            | 7:0      |          |         |       |             | _         |        |              |        |

|        |            | 15:8     | AMOE     | DE[1:0] |       |             |           | AACKEN | GCMD         | SMEN   |

| 0x04   | CTRLB      | 23:16    |          |         |       |             |           | ACKACT | CMD          | [1:0]  |

|        |            | 31:24    |          |         |       |             |           |        |              |        |

| 0x08   |            |          |          |         |       |             |           |        |              |        |

|        | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x13   |            |          |          |         |       |             |           |        |              |        |

| 0x14   | INTENCLR   | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x15   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x16   | INTENSET   | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x17   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x18   | INTFLAG    | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x19   | Reserved   |          |          |         |       |             |           |        |              |        |

| 0      | STATUS     | 7:0      | CLKHOLD  | LOWTOUT |       | SR          | DIR       | RXNACK | COLL         | BUSERR |

| 0x1A   |            | 15:8     |          |         |       |             | LENERR    | HS     | SEXTTOUT     |        |

|        |            | 7:0      |          |         |       |             |           |        | ENABLE       | SWRST  |

| 0.10   | OVALOPTION | 15:8     |          |         |       |             |           |        |              |        |

| 0x1C   | SYNCBUSY   | 23:16    |          |         |       |             |           |        |              |        |

|        |            | 31:24    |          |         |       |             |           |        |              |        |

| 0x20   |            |          |          |         |       |             |           |        |              |        |

|        | Reserved   |          |          |         |       |             |           |        |              |        |

| 0x23   |            |          |          |         |       |             |           |        |              |        |

|        |            | 7:0      |          |         |       | ADDR[6:0]   |           |        |              | GENCEN |

| 0x24   | ADDR       | 15:8     | TENBITEN |         |       |             |           |        | ADDR[9:7]    |        |

| 0724   | ADDR       | 23:16    |          |         | ŀ     | ADDRMASK[6: | 0]        |        |              |        |

|        |            | 31:24    |          |         |       |             |           |        | ADDRMASK[9:7 | 7]     |

| 0x28   | DATA       | 7:0      |          |         |       | DAT         | A[7:0]    |        |              |        |

| UXZO   | DATA       | 15:8     |          |         |       |             |           |        |              |        |

## **30.8 Register Description - I<sup>2</sup>C Slave**

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

### 30.10.7 Status

| Name:     | STATUS             |

|-----------|--------------------|

| Offset:   | 0x1A               |

| Reset:    | 0x0000             |

| Property: | Write-Synchronized |

| Bit    | 15      | 14      | 13    | 12       | 11 | 10     | 9        | 8        |

|--------|---------|---------|-------|----------|----|--------|----------|----------|

|        |         |         |       |          |    | LENERR | SEXTTOUT | MEXTTOUT |

| Access |         |         |       |          |    | R/W    | R/W      | R/W      |

| Reset  |         |         |       |          |    | 0      | 0        | 0        |

|        |         |         |       |          |    |        |          |          |

| Bit    | 7       | 6       | 5     | 4        | 3  | 2      | 1        | 0        |

|        | CLKHOLD | LOWTOUT | BUSST | ATE[1:0] |    | RXNACK | ARBLOST  | BUSERR   |

| Access | R       | R/W     | R/W   | R/W      |    | R      | R/W      | R/W      |

| Reset  | 0       | 0       | 0     | 0        |    | 0      | 0        | 0        |

### Bit 10 – LENERR Transaction Length Error

This bit is set when automatic length is used for a DMA transaction and the slave sends a NACK before ADDR.LEN bytes have been written by the master.

Writing '1' to this bit location will clear STATUS.LENERR. This flag is automatically cleared when writing to the ADDR register.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

### Bit 9 - SEXTTOUT Slave SCL Low Extend Time-Out

This bit is set if a slave SCL low extend time-out occurs.

This bit is automatically cleared when writing to the ADDR register.

Writing '1' to this bit location will clear SEXTTOUT. Normal use of the I<sup>2</sup>C interface does not require the SEXTTOUT flag to be cleared by this method.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

Bit 8 – MEXTTOUT Master SCL Low Extend Time-Out

This bit is set if a master SCL low time-out occurs.

Writing '1' to this bit location will clear STATUS.MEXTTOUT. This flag is automatically cleared when writing to the ADDR register.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

### Bit 7 – CLKHOLD Clock Hold

This bit is set when the master is holding the SCL line low, stretching the I<sup>2</sup>C clock. Software should consider this bit when INTFLAG.SB or INTFLAG.MB is set.

- 1. Enable the TCC bus clock (CLK\_TCCx\_APB).

- 2. If Capture mode is required, enable the channel in capture mode by writing a '1' to the Capture Enable bit in the Control A register (CTRLA.CPTEN).

Optionally, the following configurations can be set before enabling TCC:

- 1. Select PRESCALER setting in the Control A register (CTRLA.PRESCALER).

- 2. Select Prescaler Synchronization setting in Control A register (CTRLA.PRESCSYNC).

- 3. If down-counting operation is desired, write the Counter Direction bit in the Control B Set register (CTRLBSET.DIR) to '1'.

- 4. Select the Waveform Generation operation in the WAVE register (WAVE.WAVEGEN).

- 5. Select the Waveform Output Polarity in the WAVE register (WAVE.POL).

- 6. The waveform output can be inverted for the individual channels using the Waveform Output Invert Enable bit group in the Driver register (DRVCTRL.INVEN).

### 32.6.2.2 Enabling, Disabling, and Resetting

The TCC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TCC is disabled by writing a zero to CTRLA.ENABLE.

The TCC is reset by writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TCC, except DBGCTRL, will be reset to their initial state, and the TCC will be disabled. Refer to Control A (CTRLA) register for details.

The TCC should be disabled before the TCC is reset to avoid undefined behavior.

### 32.6.2.3 Prescaler Selection

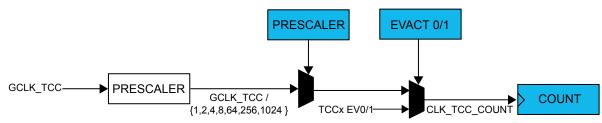

The GCLK\_TCCx clock is fed into the internal prescaler.

The prescaler consists of a counter that counts up to the selected prescaler value, whereupon the output of the prescaler toggles.

If the prescaler value is higher than one, the counter update condition can be optionally executed on the next GCLK\_TCC clock pulse or the next prescaled clock pulse. For further details, refer to the Prescaler (CTRLA.PRESCALER) and Counter Synchronization (CTRLA.PRESYNC) descriptions.

Prescaler outputs from 1 to 1/1024 are available. For a complete list of available prescaler outputs, see the register description for the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

Note: When counting events, the prescaler is bypassed.

The joint stream of prescaler ticks and event action ticks is called CLK\_TCC\_COUNT.

### Figure 32-2. Prescaler

### 32.6.2.4 Counter Operation

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TCC clock input (CLK\_TCC\_COUNT). A counter clear or reload mark the end of current counter cycle and the start of a new one.

### **RAMP1** Operation

This is the default PWM operation, described in Single-Slope PWM Generation.

### **RAMP2** Operation

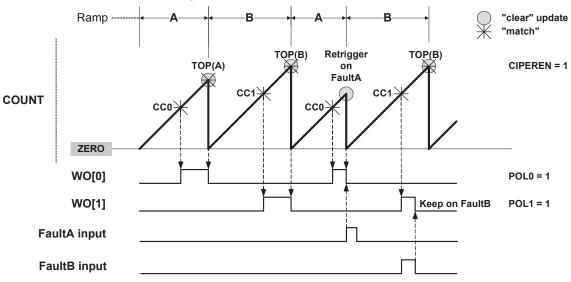

These operation modes are dedicated for power factor correction (PFC), Half-Bridge and Push-Pull SMPS topologies, where two consecutive timer/counter cycles are interleaved, see Figure 32-18. In cycle A, odd channel output is disabled, and in cycle B, even channel output is disabled. The ramp index changes after each update, but can be software modified using the Ramp index command bits in Control B Set register (CTRLBSET.IDXCMD).

### Standard RAMP2 (RAMP2) Operation

Ramp A and B periods are controlled by the PER register value. The PER value can be different on each ramp by the Circular Period buffer option in the Wave register (WAVE.CIPEREN=1). This mode uses a two-channel TCC to generate two output signals, or one output signal with another CC channel enabled in capture mode.

### Figure 32-18. RAMP2 Standard Operation

## Alternate RAMP2 (RAMP2A) Operation

Alternate RAMP2 operation is similar to RAMP2, but CC0 controls both WO[0] and WO[1] waveforms when the corresponding circular buffer option is enabled (CIPEREN=1). The waveform polarity is the same on both outputs. Channel 1 can be used in capture mode.

### 32.8.8 Debug control

| Name:     | DBGCTRL              |

|-----------|----------------------|

| Offset:   | 0x1E                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0      |

|--------|---|---|---|---|---|-------|---|--------|

|        |   |   |   |   |   | FDDBD |   | DBGRUN |

| Access |   |   |   |   |   | R/W   |   | R/W    |

| Reset  |   |   |   |   |   | 0     |   | 0      |

### Bit 2 – FDDBD Fault Detection on Debug Break Detection

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

By default this bit is zero, and the on-chip debug (OCD) fault protection is disabled. When this bit is written to '1', OCD break request from the OCD system will trigger non-recoverable fault. When this bit is set, OCD fault protection is enabled and OCD break request from the OCD system will trigger a non-recoverable fault.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | No faults are generated when TCC is halted in debug mode.                                     |

| 1     | A non recoverable fault is generated and FAULTD flag is set when TCC is halted in debug mode. |

### Bit 0 – DBGRUN Debug Running State

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

| Value | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| 0     | The TCC is halted when the device is halted in debug mode.                  |

| 1     | The TCC continues normal operation when the device is halted in debug mode. |

AC – Analog Comparators

| Value | Name                    |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

### Bits 17:16 - OUT[1:0] Output

These bits configure the output selection for comparator n. COMPCTRLn.OUT can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name  | Description                                                                           |

|-------|-------|---------------------------------------------------------------------------------------|

| 0x0   | OFF   | The output of COMPn is not routed to the COMPn I/O port                               |

| 0x1   | ASYNC | The asynchronous output of COMPn is routed to the COMPn I/O port                      |

| 0x2   | SYNC  | The synchronous output (including filtering) of COMPn is routed to the COMPn I/O port |

| 0x3   | N/A   | Reserved                                                                              |

### Bit 15 - SWAP Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

### Bits 13:12 - MUXPOS[1:0] Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | PIN0 | I/O pin 0   |

| 0x1   | PIN1 | I/O pin 1   |

| 0x2   | PIN2 | I/O pin 2   |

| 0x3   | PIN3 | I/O pin 3   |

Bits 10:8 – MUXNEG[2:0] Negative Input Mux Selection

These bits select which input will be connected to the negative input of comparator n. COMPCTRLn.MUXNEG can only be written while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | PIN0 | I/O pin 0   |

| 0x1   | PIN1 | I/O pin 1   |

| 0x2   | PIN2 | I/O pin 2   |

| 0x3   | PIN3 | I/O pin 3   |

## **Electrical Characteristics**

| No.  | Parameters                                           | Test Conditions                                   | Pin  | Symbol             | Min.                                | Тур. | Max.                      | Unit | Type' |  |

|------|------------------------------------------------------|---------------------------------------------------|------|--------------------|-------------------------------------|------|---------------------------|------|-------|--|

|      |                                                      | Switch from<br>unpowered to fail-safe<br>mode     | VS   | VVS_th_U_F_up      | 2.0                                 | 2.25 | 2.4                       | V    | A     |  |

| 1.10 | VS undervoltage<br>hysteresis                        |                                                   | VS   | VVS_hys_U          | 0.1                                 | 0.2  | 0.3                       | V    | A     |  |

| 3    | TXD input/output pin (only SBC)                      |                                                   |      |                    |                                     |      |                           |      |       |  |

| 3.1  | Low-level voltage input                              |                                                   | TXD  | VTXDL              | -0.3                                |      | +0.8                      | V    | A     |  |

| 3.2  | High-level voltage input                             |                                                   | TXD  | VTXDH              | 2                                   |      | V <sub>CC</sub><br>+ 0.3V | V    | A     |  |

| 3.3  | Pull-up resistor                                     | V <sub>TXD</sub> = 0V                             | TXD  | R <sub>TXD</sub>   | 40                                  | 70   | 100                       | kΩ   | А     |  |

| 3.4  | High-level leakage current                           | VTXD = VCC                                        | TXD  | ITXD               | -3                                  |      | +3                        | μA   | A     |  |

| 4    | EN input pin (only SBC                               | ;)                                                |      |                    |                                     |      |                           |      | 1     |  |

| 4.1  | Low-level voltage input                              |                                                   | EN   | V <sub>ENL</sub>   | -0.3                                |      | +0.8                      | V    | A     |  |

| 4.2  | High-level voltage input                             |                                                   | EN   | VENH               | 2                                   |      | VCC<br>+ 0.3V             | V    | A     |  |

| 4.3  | Pull-down resistor                                   | V <sub>EN</sub> = VCC                             | EN   | R <sub>EN</sub>    | 50                                  | 125  | 200                       | kΩ   | А     |  |

| 4.4  | Low-level input current                              | V <sub>EN</sub> = 0V                              | EN   | IEN                | -3                                  |      | +3                        | μA   | A     |  |

| 5    | NRES open drain outp                                 | ut pin                                            |      |                    |                                     |      |                           |      |       |  |

| 5.1  | Low-level output voltage                             | V <sub>S</sub> ≥5.5V<br>I <sub>NRES</sub> = 2mA   | NRES | VNRESL             |                                     | 0.2  | 0.4                       | V    | A     |  |

| 5.2  | Undervoltage reset time                              | V <sub>VS</sub> ≥5.5V<br>C <sub>NRES</sub> = 20pF | NRES | tReset             | 2                                   | 4    | 6                         | ms   | A     |  |

| 5.3  | Reset debounce time for falling edge                 | V <sub>VS</sub> ≥5.5V<br>C <sub>NRES</sub> = 20pF | NRES | <sup>t</sup> res_f | 0.5                                 |      | 10                        | μs   | A     |  |

| 5.4  | Switch off leakage current                           | V <sub>NRES</sub> = 5.5V                          | NRES | INRES_L            | -3                                  |      | +3                        | μA   | A     |  |

| 8    | VCC voltage regulator                                | 1                                                 |      |                    |                                     |      |                           |      |       |  |

| 8.1  | Output voltage VCC                                   | 4V < V <sub>S</sub> < 18V<br>(0mA to 50mA)        | VCC  | VCC <sub>nor</sub> | 3.234                               |      | 3.366                     | V    | A     |  |

|      |                                                      | 4.5V < V <sub>S</sub> < 18V<br>(0mA to 85mA)      | VCC  | VCC <sub>nor</sub> | 3.234                               |      | 3.366                     | V    | С     |  |

| 8.2  | Output voltage V <sub>CC</sub> at low V <sub>S</sub> | 3V < VS < 4V                                      | VCC  | VCClow             | V <sub>VS</sub> -<br>V <sub>D</sub> |      | 3.366                     | V    | A     |  |

| 8.3  | Regulator drop<br>voltage                            | VS > 3V, I <sub>VCC</sub> = –<br>15mA             | VCC  | V <sub>D1</sub>    |                                     | 100  | 150                       | mV   | A     |  |

| 8.4  | Regulator drop voltage                               | VS > 3V, I <sub>VCC</sub> = –<br>50mA             | VCC  | V <sub>D2</sub>    |                                     | 300  | 500                       | mV   | A     |  |

**Electrical Characteristics**

| Parameter                                                 |                                                                      |                   | onditio              | ons  | Symbol            | Min. | Тур.  | Max.       | Unit   |  |

|-----------------------------------------------------------|----------------------------------------------------------------------|-------------------|----------------------|------|-------------------|------|-------|------------|--------|--|

| Parasitic capacitor load                                  |                                                                      |                   |                      |      | C <sub>XIN</sub>  | -    | 5.9   | -          | pF     |  |

| Parasitic capacitor load                                  |                                                                      |                   |                      |      | C <sub>XOUT</sub> | -    | 3.2   | -          | pF     |  |

| Parameter Conditions                                      |                                                                      | Sym               | bol                  | Min. | Тур.              | N    | Max.  |            | nit    |  |

|                                                           | f = 2MHz,<br>$C_L = 20pF$ ,<br>XOSC.GAIN = 0,<br>ESR = 600 $\Omega$  |                   |                      | -    | 15.6K             | 5    | 1.0K  |            |        |  |

|                                                           | f = 4MHz,<br>$C_L$ = 20pF,<br>XOSC.GAIN = 1,<br>ESR = 100 $\Omega$   |                   |                      | -    | 6.3K              | 2    | 20.1K |            |        |  |

| Startup time                                              | f = 8 MHz,<br>$C_L$ = 20pF,<br>XOSC.GAIN = 2,<br>ESR = 35 $\Omega$   | t <sub>STAF</sub> | t <sub>STARTUP</sub> | -    | 6.2K              | 2    | 0.3K  | сус        | cycles |  |

|                                                           | f = 16 MHz,<br>$C_L = 20$ pF,<br>XOSC.GAIN = 3,<br>ESR = 25 $\Omega$ |                   |                      | -    | 7.7K              | 2    | 1.2K  |            |        |  |

|                                                           | f = 32MHz,<br>$C_L$ = 18pF,<br>XOSC.GAIN = 4,<br>ESR = 40 $\Omega$   |                   |                      | -    | 6.0K              | 1    | 4.2K  |            |        |  |

| Parameter Conditions                                      |                                                                      |                   | Sy                   | mbol | Min.              | Тур. | Ma    | <b>x</b> . | Unit   |  |

| $f = 2MHz,$ $C_{L} = 20pF,$ XOSC.GAIN AGC off $f = 2MHz,$ |                                                                      | = 0,              |                      |      | -                 | 89   | 19    |            | μΑ     |  |

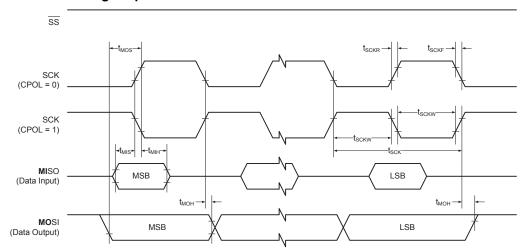

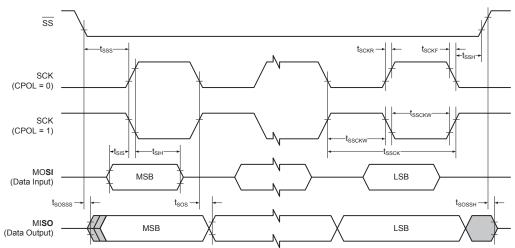

### 37.15.2 SERCOM in SPI Mode Timing

Figure 37-13. SPI Timing Requirements in Master Mode

| Table 37-51. | SPI Timing | <b>Characteristics and</b> | Requirements <sup>(1)</sup> |

|--------------|------------|----------------------------|-----------------------------|

|--------------|------------|----------------------------|-----------------------------|

| Symbol            | Parameter                    | Conditions | Min.                   | Тур.                    | Max. | Units |

|-------------------|------------------------------|------------|------------------------|-------------------------|------|-------|

| t <sub>SCK</sub>  | SCK period                   | Master     |                        | 84                      |      | ns    |

| t <sub>SCKW</sub> | SCK high/low width           | Master     | -                      | 0.5*t <sub>SCK</sub>    | -    |       |

| t <sub>SCKR</sub> | SCK rise time <sup>(2)</sup> | Master     | -                      | -                       | -    |       |

| t <sub>SCKF</sub> | SCK fall time <sup>(2)</sup> | Master     | -                      | -                       | -    |       |

| t <sub>MIS</sub>  | MISO setup to SCK            | Master     | -                      | 21                      | -    |       |

| t <sub>MIH</sub>  | MISO hold after SCK          | Master     | -                      | 13                      | -    |       |

| t <sub>MOS</sub>  | MOSI setup SCK               | Master     | -                      | t <sub>SCK</sub> /2 - 3 | -    |       |

| t <sub>MOH</sub>  | MOSI hold after SCK          | Master     | -                      | 3                       | -    |       |

| t <sub>SSCK</sub> | Slave SCK Period             | Slave      | 1*t <sub>CLK_APB</sub> | -                       | -    |       |