Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 48MHz                                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                               |

| Number of I/O              | 22                                                                                    |

| Program Memory Size        | 29.5KB (29.5k x 8)                                                                    |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 4K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 5.5V                                                                           |

| Data Converters            | A/D 8x12b                                                                             |

| Oscillator Type            | External                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                                       |

| Supplier Device Package    | 28-TSSOP                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/mini57ede |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Hardware fault brake and software brake protections

- Supports rising, falling, central, period, and fault break interrupts

- Supports duty/period trigger A/D conversion

- Timer comparing matching event trigger PWM to do phase change

- Supports comparator event trigger PWM to force PWM output low for current period

- Provides interrupt accumulation function

- USCI (Universal Serial Control Interface Controller)

- Two USCI devices

- Supports to be configured as UART, SPI or I<sup>2</sup>C individually

- Supports programmable baud-rate generator

- ADC (Analog-to-Digital Converter)

- 12-bit ADC with 700 kSPS

- Supports 2 sample/hold

- Up to 8-ch single-end input from I/O and one internal input from band-gap.

- Conversion started either by software trigger, PWM trigger, ACMP trigger or external pin trigger

- Supports temperature sensor for measurement chip temperature

- Supports Simultaneous and Sequential function to continuous conversion 4 channels maximum.

- Programmable Gain Amplifier (PGA)

- Supports 8 level gain selects from 1, 2, 3, 5, 7, 9, 11 and 13

- Unity gain frequency up to 8 MHz

- Analog Comparator

- Two analog comparators with programmable 16-level internal voltage reference

- Built-in CRV (comparator reference voltage)

- Supports Hysteresis function

- Interrupt when compared results changed

- Hardware Divider

- Signed (two's complement) integer calculation

- 32-bit dividend with 16-bit divisor calculation capacity

- 32-bit quotient and 32-bit remainder outputs (16-bit remainder with sign extends to 32-bit)

- Divided by zero warning flag

- 6 HCLK clocks taken for one cycle calculation

- Waiting for calculation ready automatically when reading quotient and remainder

- ISP (In-System Programming) and ICP (In-Circuit Programming)

- BOD (Brown-out Detector)

- 8 programmable threshold levels: 4.3V/4.0V/3.7V/3.0V/2.7V/2.4V/2.2V/2.0V

- Supports Brown-out interrupt and reset option

- 96-bit unique ID

- LVR (Low Voltage Reset)

- Operating Temperature: -40°C ~105°C

- Reliability: EFT > ± 4KV, ESD HBM pass 4KV

- Packages:

- Green package (RoHS)

- 20-pin TSSOP, 28-pin TSSOP, 33-pin QFN

# **3 ABBREVIATIONS**

| Acronym | Description                                      |

|---------|--------------------------------------------------|

| ACMP    | Analog Comparator Controller                     |

| ADC     | Analog-to-Digital Converter                      |

| АНВ     | Advanced High-Performance Bus                    |

| APB     | Advanced Peripheral Bus                          |

| BOD     | Brown-out Detection                              |

| BPWM    | Basic Pulse Width Modulation                     |

| DAP     | Debug Access Port                                |

| EPWM    | Enhanced Pulse Width Modulation                  |

| FIFO    | First In, First Out                              |

| FMC     | Flash Memory Controller                          |

| GPIO    | General-Purpose Input/Output                     |

| HCLK    | The Clock of Advanced High-Performance Bus       |

| HIRC    | 48 MHz Internal High Speed RC Oscillator         |

| НХТ     | 4~24 MHz External High Speed Crystal Oscillator  |

| ICP     | In Circuit Programming                           |

| ISP     | In System Programming                            |

| ISR     | Interrupt Service Routine                        |

| LDO     | Low Dropout Regulator                            |

| LIRC    | 10 kHz internal low speed RC oscillator (LIRC)   |

| LXT     | 32.768 kHz External Low Speed Crystal Oscillator |

| NVIC    | Nested Vectored Interrupt Controller             |

| PCLK    | The Clock of Advanced Peripheral Bus             |

| PWM     | Pulse Width Modulation                           |

| SPI     | Serial Peripheral Interface                      |

| SPS     | Samples per Second                               |

| TMR     | Timer Controller                                 |

| UART    | Universal Asynchronous Receiver/Transmitter      |

| UCID    | Unique Customer ID                               |

| WDT     | Watchdog Timer                                   |

Table 3-1 List of Abbreviations

| Pin No. | Pin Name  | Туре | MFP* | Description                                        |

|---------|-----------|------|------|----------------------------------------------------|

|         | BPWM_CH0  | I/O  | MFP3 | PWM channel0 output/capture input.                 |

|         | ACMP1_P0  | А    | MFP5 | Analog comparator1 positive input pin.             |

|         | I2C1_SCL  | I/O  | MFP8 | l²C1 clock pin.                                    |

|         | SPI0_SS   |      | MFP9 | SPI0 slave select pin.                             |

|         | SPI1_CLK  | I/O  | MFPA | SPI1 serial clock pin                              |

|         | UART1_TXD | 0    | MFPB | Data transmitter output pin for UART1.             |

| 16      | PD.4      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | BPWM_CH0  | I/O  | MFP3 | PWM channel0 output/capture input.                 |

|         | UART1_RXD | I    | MFPB | Data receiver input pin for UART1.                 |

| 17      | PD.1      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | ICE_CLK   | I    | MFP1 | Serial wired debugger clock pin                    |

|         | ACMP1_P2  | А    | MFP5 | Analog comparator1 positive input pin.             |

|         | I2C0_SCL  | I/O  | MFP8 | l <sup>2</sup> C0 clock pin.                       |

|         | SPI0_CLK  | I/O  | MFP9 | SPI0 serial clock pin.                             |

|         | SPI1_SS   | I/O  | MFPA | SPI1 slave select pin                              |

|         | UART0_TXD | 0    | MFPB | Data transmitter output pin for UART0.             |

| 18      | PC.3      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | ACMP1_O   | 0    | MFP5 | Analog comparator1 output.                         |

|         | PGA_O     | А    | MFP6 | PGA output pin                                     |

|         | SPI0_CLK  | I/O  | MFP9 | SPI0 serial clock pin.                             |

|         | SPI1_SS   | I/O  | MFPA | SPI1 slave select pin                              |

| 19      | PD.5      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | UART0_TXD | 0    | MFPB | Data transmitter output pin for UART0.             |

| 20      | PA.5      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | XT_OUT    | 0    | MFP1 | External 4~24 MHz (high speed) crystal output pin. |

|         | EPWM_CH5  | I/O  | MFP3 | PWM channel5 output/capture input.                 |

|         | ACMP0_O   | 0    | MFP4 | Analog comparator0 output.                         |

| 21      | PA.4      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | XT_IN     | I    | MFP1 | External 4~24 MHz (high speed) crystal input pin.  |

|         | EPWM_CH4  | I/O  | MFP3 | PWM channel4 output/capture input.                 |

| 22      | PA.3      | I/O  | MFP0 | General purpose digital I/O pin.                   |

|         | EPWM_CH3  | I/O  | MFP3 | PWM channel3 output/capture input.                 |

|         | h         | I/O  | MFP8 | l <sup>2</sup> C0 clock pin.                       |

| Pin No. | Pin Name  | Туре | MFP* | Description                               |

|---------|-----------|------|------|-------------------------------------------|

|         | ADC1_CH2  | А    | MFP2 | ADC1 channel2 analog input.               |

|         | BRAKE     | I    | MFP3 | Brake input pin of EPWM.                  |

|         | CCAP_P1   | I    | MFP7 | Timer Continuous Capture input pin        |

|         | I2C1_SDA  | I/O  | MFP8 | I <sup>2</sup> C1 data input/output pin.  |

|         | SPI0_MISO | I/O  | MFP9 | SPI0 1st MISO (Master In, Slave Out) pin. |

|         | SPI1_MOSI | I/O  | MFPA | SPI1 MOSI (Master Out, Slave In) pin.     |

|         | UART1_RXD | I    | MFPB | Data receiver input pin for UART1.        |

| 10      | PD.2      | I/O  | MFP0 | General purpose digital I/O pin.          |

|         | ICE_DAT   | I/O  | MFP1 | Serial wired debugger data pin            |

|         | ADC1_CH1  | А    | MFP2 | ADC1 channel1 analog input.               |

|         | CCAP_P0   | I    | MFP7 | Timer Continuous Capture input pin        |

|         | I2C0_SDA  | I/O  | MFP8 | I <sup>2</sup> C0 data input/output pin.  |

|         | SPI0_MOSI | I/O  | MFP9 | SPI0 1st MOSI (Master Out, Slave In) pin. |

|         | SPI1_MISO | I/O  | MFPA | SPI1 MISO (Master In, Slave Out) pin.     |

|         | UART0_RXD | I    | MFPB | Data receiver input pin for UART0.        |

| 11      | PC.0      | I/O  | MFP0 | General purpose digital I/O pin.          |

|         | ADC0_CH3  | А    | MFP2 | ADC0 channel3 analog input.               |

|         | BPWM_CH0  | I/O  | MFP3 | PWM channel0 output/capture input.        |

|         | ACMP1_P0  | А    | MFP5 | Analog comparator1 positive input pin.    |

|         | I2C1_SCL  | I/O  | MFP8 | I <sup>2</sup> C1 clock pin.              |

|         | SPI0_SS   | I/O  | MFP9 | SPI0 slave select pin.                    |

|         | SPI1_CLK  | I/O  | MFPA | SPI1 serial clock pin                     |

|         | UART1_TXD | 0    | MFPB | Data transmitter output pin for UART1.    |

| 12      | PD.1      | I/O  | MFP0 | General purpose digital I/O pin.          |

|         | ICE_CLK   | I    | MFP1 | Serial wired debugger clock pin           |

|         | ACMP1_P2  | А    | MFP5 | Analog comparator1 positive input pin.    |

|         | I2C0_SCL  | I/O  | MFP8 | I <sup>2</sup> C0 clock pin.              |

|         | SPI0_CLK  | I/O  | MFP9 | SPI0 serial clock pin.                    |

|         | SPI1_SS   | I/O  | MFPA | SPI1 slave select pin                     |

|         | UART0_TXD | 0    | MFPB | Data transmitter output pin for UART0.    |

| 13      | PC.3      | I/O  | MFP0 | General purpose digital I/O pin.          |

|         | ACMP1_O   | 0    | MFP5 | Analog comparator1 output.                |

|         | PGA_O     | А    | MFP6 | PGA output pin                            |

|    | PB.3      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

|----|-----------|---------|------|----------------------------------------------------|--|--|

|    | ACMP1_N   | A       | MFP5 | Analog comparator1 negative input pin.             |  |  |

| 11 | PGA I     | A       | MFP6 | PGA input pin                                      |  |  |

|    | т 07_1    | 1/0     | MFP7 | Timer0event counter input / toggle output          |  |  |

|    | PC.2      | 1/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

|    |           |         | MFP0 |                                                    |  |  |

|    | ADC1_CH2  | A       |      | ADC1 channel2 analog input.                        |  |  |

|    | BRAKE     | <br>  . | MFP3 | Brake input pin of EPWM.                           |  |  |

| 12 | CCAP_P1   |         | MFP7 | Timer Continuous Capture input pin                 |  |  |

|    | I2C1_SDA  | I/O     | MFP8 | I <sup>2</sup> C1 data input/output pin.           |  |  |

|    | SPI0_MISO | I/O     | MFP9 | SPI0 1st MISO (Master In, Slave Out) pin.          |  |  |

|    | SPI1_MOSI | I/O     | MFPA | SPI1 MOSI (Master Out, Slave In) pin.              |  |  |

|    | UART1_RXD | I       | MFPB | Data receiver input pin for UART1.                 |  |  |

|    | PD.2      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

|    | ICE_DAT   | I/O     | MFP1 | Serial wired debugger data pin                     |  |  |

|    | ADC1_CH1  | А       | MFP2 | ADC1 channel1 analog input.                        |  |  |

| 13 | CCAP_P0   | I       | MFP7 | Timer Continuous Capture input pin                 |  |  |

| 10 | I2C0_SDA  | I/O     | MFP8 | I <sup>2</sup> C0 data input/output pin.           |  |  |

|    | SPI0_MOSI | I/O     | MFP9 | SPI0 1st MOSI (Master Out, Slave In) pin.          |  |  |

|    | SPI1_MISO | I/O     | MFPA | SPI1 MISO (Master In, Slave Out) pin.              |  |  |

|    | UART0_RXD | I       | MFPB | Data receiver input pin for UART0.                 |  |  |

|    | PD.3      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

| 14 | BPWM_CH1  | I/O     | MFP3 | PWM channel1 output/capture input.                 |  |  |

|    | UART1_TXD | 0       | MFPB | Data transmitter output pin for UART1.             |  |  |

| 15 | NC        |         |      | No Connection                                      |  |  |

| 16 | NC        |         |      | No Connection                                      |  |  |

| 17 | NC        |         |      | No Connection                                      |  |  |

| 18 | NC        |         |      | No Connection                                      |  |  |

|    | PD.5      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

| 19 | UART0_TXD | 0       | MFPB | Data transmitter output pin for UART0.             |  |  |

|    | PA.5      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

|    | XT_OUT    | 0       | MFP1 | External 4~24 MHz (high speed) crystal output pin. |  |  |

| 20 | EPWM_CH5  | I/O     | MFP3 | PWM channel5 output/capture input.                 |  |  |

|    | ACMP0_O   | 0       | MFP4 | Analog comparator0 output.                         |  |  |

| 21 | PA.4      | I/O     | MFP0 | General purpose digital I/O pin.                   |  |  |

|    |           |         | -    |                                                    |  |  |

| Μ   | :  | :   |

|-----|----|-----|

| Ινι | IN | 137 |

|     |    |     |

|    | XT_IN        | I   | MFP1 | External 4~24 MHz (high speed) crystal input pin. |  |  |

|----|--------------|-----|------|---------------------------------------------------|--|--|

|    | <br>EPWM_CH4 | I/O | MFP3 | PWM channel4 output/capture input.                |  |  |

| 22 | NC           |     |      | No Connection                                     |  |  |

|    | PA.3         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

|    | EPWM_CH3     | I/O | MFP3 | PWM channel3 output/capture input.                |  |  |

|    | I2C0_SCL     | I/O | MFP8 | l <sup>2</sup> C0 clock pin.                      |  |  |

| 23 | SPI0_CLK     | I/O | MFP9 | SPI0 serial clock pin.                            |  |  |

|    | SPI1_SS      | I/O | MFPA | SPI1 slave select pin                             |  |  |

|    | UART0_TXD    | 0   | MFPB | Data transmitter output pin for UART0.            |  |  |

|    | PA.2         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

|    | EPWM_CH2     | I/O | MFP3 | PWM channel2 output/capture input.                |  |  |

|    | I2C0_SDA     | I/O | MFP8 | l²C0 data input/output pin.                       |  |  |

| 24 | SPI0_MOSI    | I/O | MFP9 | SPI0 1st MOSI (Master Out, Slave In) pin.         |  |  |

|    | SPI1_MISO    | I/O | MFPA | SPI1 MISO (Master In, Slave Out) pin.             |  |  |

|    | UART0_RXD    | I   | MFPB | Data receiver input pin for UART0.                |  |  |

|    | PA.1         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

|    | EPWM_CH1     | I/O | MFP3 | PWM channel1 output/capture input.                |  |  |

|    | I2C1_SDA     | I/O | MFP8 | l²C1 data input/output pin.                       |  |  |

| 25 | SPI0_MISO    | I/O | MFP9 | SPI0 1st MISO (Master In, Slave Out) pin.         |  |  |

|    | SPI1_MOSI    | I/O | MFPA | SPI1 MOSI (Master Out, Slave In) pin.             |  |  |

|    | UART1_RXD    | I   | MFPB | Data receiver input pin for UART1.                |  |  |

|    | PA.0         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

|    | CLKO         | 0   | MFP1 | Clock Out                                         |  |  |

|    | EPWM_CH0     | I/O | MFP3 | PWM channel0 output/capture input.                |  |  |

| 26 | I2C1_SCL     | I/O | MFP8 | l <sup>2</sup> C1 clock pin.                      |  |  |

|    | SPI0_SS      | I/O | MFP9 | SPI0 slave select pin.                            |  |  |

|    | SPI1_CLK     | I/O | MFPA | SPI1 serial clock pin                             |  |  |

|    | UART1_TXD    | 0   | MFPB | Data transmitter output pin for UART1.            |  |  |

| 27 | PC.4         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

| 21 | ECAP_P3      | I   | MFP7 | Enhanced Input Capture input pin                  |  |  |

|    | PC.0         | I/O | MFP0 | General purpose digital I/O pin.                  |  |  |

| 28 | ADC0_CH3     | А   | MFP2 | ADC0 channel3 analog input.                       |  |  |

| 28 | BPWM_CH0     | I/O | MFP3 | PWM channel0 output/capture input.                |  |  |

|    | ACMP1_P0     | А   | MFP5 | Analog comparator1 positive input pin.            |  |  |

|                  | DDAKE     |      | MEDO |     |                                         |  |

|------------------|-----------|------|------|-----|-----------------------------------------|--|

|                  | BRAKE     | PC.2 | MFP3 |     | EPWM brake pin.                         |  |

|                  | EPWM_CH5  | PA.5 | MFP3 | 0   | Enhanced PWM output pin.                |  |

|                  | EPWM_CH4  | PA.4 | MFP3 | 0   | Enhanced PWM output pin.                |  |

| EPWM             | EPWM_CH3  | PA.3 | MFP3 | 0   | Enhanced PWM output pin.                |  |

|                  | EPWM_CH2  | PA.2 | MFP3 | 0   | Enhanced PWM output pin.                |  |

|                  | EPWM_CH1  | PA.1 | MFP3 | 0   | Enhanced PWM output pin.                |  |

|                  | EPWM_CH0  | PA.0 | MFP3 | 0   | Enhanced PWM output pin.                |  |

|                  | I2C1_SDA  | PC.2 | MFP8 | I/O | l <sup>2</sup> C1 data pin.             |  |

|                  | I2C0_SDA  | PD.2 | MFP8 | I/O | l²C0 data pin.                          |  |

|                  | I2C0_SCL  | PD.1 | MFP8 | I/O | l <sup>2</sup> C0 clock pin.            |  |

| l <sup>2</sup> C | I2C1_SCL  | PC.0 | MFP8 | I/O | l²C1 clock pin.                         |  |

| i C              | I2C0_SCL  | PA.3 | MFP8 | I/O | l <sup>2</sup> C0 clock pin.            |  |

|                  | I2C0_SDA  | PA.2 | MFP8 | I/O | l²C0 data pin.                          |  |

|                  | I2C1_SDA  | PA.1 | MFP8 | I/O | l²C1 data pin.                          |  |

|                  | I2C1_SCL  | PA.0 | MFP8 | I/O | l²C1 clock pin.                         |  |

|                  | ICE_DAT   | PD.2 | MFP1 | I/O | Serial wired debugger data pin          |  |

| ICE              | ICE_CLK   | PD.1 | MFP1 | I   | Serial wired debugger clock pin         |  |

| nRESET           | nRESET    |      |      | I   | External reset pin, internal pull-high. |  |

| <b>DO</b> 4      | PGA_I     | PB.3 | MFP6 | А   | PGA analog input pin.                   |  |

| PGA              | PGA_O     | PC.3 | MFP6 | А   | PGA analog output pin.                  |  |

|                  | SPI0_MOSI | PC.1 | MFP9 | I/O | SPI0 MOSI (Master Out, Slave In) pin.   |  |

|                  | SPI0_MISO | PC.2 | MFP9 | I/O | SPI0 MISO (Master In, Slave Out) pin.   |  |

|                  | SPI0_MOSI | PD.2 | MFP9 | I/O | SPI0 MOSI (Master Out, Slave In) pin.   |  |

|                  | SPI0_CLK  | PC.3 | MFP9 | I/O | SPI0 clock pin.                         |  |

|                  | SPI0_CLK  | PD.1 | MFP9 | I/O | SPI0 clock pin.                         |  |

| SPI0             | SPI0_SS   | PC.0 | MFP9 | I   | SPI0 slave selection pin.               |  |

|                  | SPI0_CLK  | PA.3 | MFP9 | I/O | SPI0 clock pin.                         |  |

|                  | SPI0_MOSI | PA.2 | MFP9 | I/O | SPI0 MOSI (Master Out, Slave In) pin.   |  |

|                  | SPI0_MISO | PA.1 | MFP9 | I/O | SPI0 MISO (Master In, Slave Out) pin.   |  |

|                  | SPI0_SS   | PA.0 | MFP9 | I   | SPI0 slave selection pin.               |  |

|                  | SPI1_MISO | PC.1 | MFPA | I/O | SPI1 MISO (Master In, Slave Out) pin    |  |

|                  | SPI1_MOSI | PC.2 | MFPA | I/O | SPI1 MOSI (Master Out, Slave In) pin.   |  |

| SPI1             | SPI1_MISO | PD.2 | MFPA | I/O | SPI1 MISO (Master In, Slave Out) pin    |  |

|                  | SPI1_SS   | PC.3 | MFPA | I/O | SPI1 Slave Select                       |  |

|                  | _         |      |      |     |                                         |  |

## 6.2 System Manager

### 6.2.1 Overview

System management includes the following sections:

- System Reset

- System Power Architecture

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset, and multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

### 6.2.2 System Reset

The system reset can be issued by one of the events listed below. These reset event flags can be read from SYS\_RSTSTS register to determine the reset source. Hardware reset can reset chip through peripheral reset signals. Software reset can trigger reset through control registers.

- Hardware Reset Sources

- Power-on Reset (POR)

- Low level on the nRESET pin

- Watchdog Timer Time-out Reset (WDT)

- Low Voltage Reset (LVR)

- Brown-out Detector Reset (BOD Reset)

- Software Reset Sources

- CHIP Reset will reset whole chip by writing 1 to CHIPRST (SYS\_IPRST0[0])

- MCU Reset to reboot but keeping the booting setting from APROM or LDROM by writing 1 to SYSRESETREQ (SCS\_AIRCR[2])

- CPU Reset for Cortex<sup>®</sup>-M0 core Only by writing 1 to CPURST (SYS\_IPRST0[1])

### 6.2.8 System Timer (SysTick)

The Cortex<sup>®</sup>-M0 includes an integrated system timer, SysTick, which provides a simple, 24-bit cleared-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used in several different ways, for example:

An RTOS tick timer fires at a programmable rate (for example 100Hz) and invokes a SysTick routine.

A high-speed alarm timer uses Core clock.

A variable rate alarm or signal timer – the duration range is dependent on the reference clock used and the dynamic range of the counter.

A simple counter can be used by software to measure task completion time.

An internal Clock Source control based on missing/meeting durations. The COUNTFLAG bit-field in the control and status register can be used to determine if an action completed within a set duration, as part of a dynamic clock management control loop.

When enabled, the timer will count down from the value in the SysTick Current Value Register (SYST\_CVR) to 0, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) on the next clock edge, and then decrement on subsequent clocks. When the counter transitions to 0, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on read.

The SYST\_CVR value is UNKNOWN on reset. Software should write to the register to clear it to 0 before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is zero, the timer will be maintained with a current value of zero after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>®</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

| 34 | 18 | Reserved     | Reserved                                      |

|----|----|--------------|-----------------------------------------------|

| 35 | 19 | Reserved     | Reserved                                      |

| 36 | 20 | Reserved     | Reserved                                      |

| 37 | 21 | HIRCTRIM_INT | HIRC TRIM interrupt                           |

| 38 | 22 | TMR0_INT     | Timer 0 interrupt                             |

| 39 | 23 | TMR1_INT     | Timer 1 interrupt                             |

| 40 | 24 | Reserved     | Reserved                                      |

| 41 | 25 | Reserved     | Reserved                                      |

| 42 | 26 | ACMP_INT     | Analog Comparator 0 or Comparator 1 interrupt |

| 43 | 27 | Reserved     | Reserved                                      |

| 44 | 28 | PWRWU_INT    | Chip wake-up from Power-down state interrupt  |

| 45 | 29 | ADC0_INT     | ADC0 interrupt                                |

| 46 | 30 | ADC1_INT     | ADC1 interrupt                                |

| 47 | 31 | ADCWCMP_INT  | ADC Window Compare interrupt                  |

Table 6.2-9 System Interrupt Map Vector Table

### 6.2.9.4 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table based address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with the exception handler entry as illustrated in previous section.

| Vector Table Word Offset (Bytes) | Description                                         |

|----------------------------------|-----------------------------------------------------|

| 0x00                             | Initial Stack Pointer Value                         |

| Exception Number * 0x04          | Exception Entry Pointer using that Exception Number |

Table 6.2-10 Vector Table Format

### 6.2.9.5 Operation Description

The NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used

# IRQ0 ~ IRQ31 Set-pending Control Register (NVIC\_ISPR)

| Register  | Offset       | R/W | Description                               | Reset Value |

|-----------|--------------|-----|-------------------------------------------|-------------|

| NVIC_ISPR | SCS_BA+0x200 | R/W | IRQ0 ~ IRQ31 Set-Pending Control Register | 0x0000_0000 |

| 31 | 30      | 29 | 28   | 27   | 26 | 25 | 24 |  |  |  |

|----|---------|----|------|------|----|----|----|--|--|--|

|    | SETPEND |    |      |      |    |    |    |  |  |  |

| 23 | 22      | 21 | 20   | 19   | 18 | 17 | 16 |  |  |  |

|    | SETPEND |    |      |      |    |    |    |  |  |  |

| 15 | 14      | 13 | 12   | 11   | 10 | 9  | 8  |  |  |  |

|    |         |    | SETF | PEND |    |    |    |  |  |  |

| 7  | 6       | 5  | 4    | 3    | 2  | 1  | 0  |  |  |  |

|    |         |    | SETF | PEND |    |    |    |  |  |  |

| Bits   | Description | Description                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [31:0] | SETPEND     | Set Interrupt Pending Register         Write operation:         0 = No effect.         1 = Write 1 to set pending state. Each bit represents an interrupt number from IRQ0 ~         IRQ31 (Vector number from 16 ~ 47).         Read operation: |  |  |  |  |  |

|        |             | <ul> <li>0 = Associated interrupt in not in pending status.</li> <li>1 = Associated interrupt is in pending status.</li> <li>Note: Read value indicates the current pending status.</li> </ul>                                                   |  |  |  |  |  |

# IRQ0 ~ IRQ31 Clear-pending Control Register (NVIC\_ICPR)

| Register  | Offset       | R/W | Description                                 | Reset Value |

|-----------|--------------|-----|---------------------------------------------|-------------|

| NVIC_ICPR | SCS_BA+0x280 | R/W | IRQ0 ~ IRQ31 Clear-Pending Control Register | 0x0000_0000 |

| 31 | 30      | 29 | 28   | 27   | 26 | 25 | 24 |  |  |

|----|---------|----|------|------|----|----|----|--|--|

|    | CLRPEND |    |      |      |    |    |    |  |  |

| 23 | 22      | 21 | 20   | 19   | 18 | 17 | 16 |  |  |

|    | CLRPEND |    |      |      |    |    |    |  |  |

| 15 | 14      | 13 | 12   | 11   | 10 | 9  | 8  |  |  |

|    | CLRPEND |    |      |      |    |    |    |  |  |

| 7  | 6       | 5  | 4    | 3    | 2  | 1  | 0  |  |  |

|    |         |    | CLRF | PEND |    |    |    |  |  |

| Bits   | Description |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [31:0] | CLRPEND     | Clear Interrupt Pending Register         Write operation:         0 = No effect.         1 = Write 1 to clear pending state. Each bit represents an interrupt number from IRQ0 ~         IRQ31 (Vector number from 16 ~ 47).         Read operation:         0 = Associated interrupt in not in pending status.         1 = Associated interrupt is in pending status.         Note: Read value indicates the current pending status. |  |  |  |  |  |

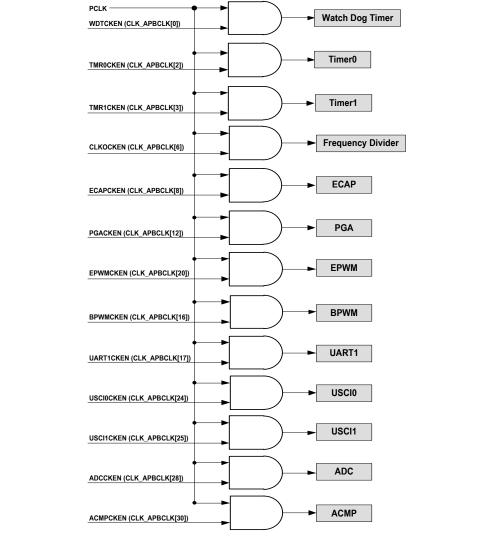

Figure 6.3-5 Peripherals Bus Clock Source Selection for PCLK

|        | Peripheral Clock Selectable | Ext. CLK<br>(HXT Or LXT) | HIRC | LIRC | HCLK |

|--------|-----------------------------|--------------------------|------|------|------|

| WDT    | Yes                         | Yes                      | No   | Yes  | Yes  |

| WWDT   | Yes                         | Yes                      | No   | Yes  | Yes  |

| Timer0 | Yes                         | Yes                      | Yes  | Yes  | Yes  |

| Timer1 | Yes                         | Yes                      | Yes  | Yes  | Yes  |

| USCI0  | Yes                         | Yes                      | Yes  | Yes  | Yes  |

| USCI1  | Yes                         | Yes                      | Yes  | Yes  | Yes  |

| ADC    | Yes                         | Yes                      | Yes  | No   | Yes  |

| ACMP   | No                          | No                       | No   | No   | Yes  |

| ECAP   | No                          | No                       | No   | No   | Yes  |

| EBWM   | No                          | No                       | No   | No   | Yes  |

| BPWM   | No                          | No                       | No   | No   | Yes  |

| HDIV   | No                          | No                       | No   | No   | Yes  |

Table 6.3-1 Peripheral Clock Source Selection Table

**Note:** For the peripherals those peripheral clock are not selectable, its clock source is fixed to PCLK.

### 6.3.5 Power-down Mode Clock

When entering Power-down mode, system clocks, some clock sources and some peripheral clocks are disabled. Some clock sources and peripherals clock are still active in Power-down mode.

The clocks still kept active are listed below:

- Clock Generator

- 10 kHz internal low speed oscillator (LIRC) clock

- 32.768 kHz external low speed crystal oscillator (LXT) clock (If PDLXT = 1 and XTLEN[1:0] = 10)

- Peripherals Clock (When 10 kHz low speed oscillator is adopted as clock source)

- Watchdog Clock

- Timer 0/1 Clock

### 6.3.6 Frequency Divider Output

This device is equipped with a power-of-2 frequency divider which is composed of 16 chained divide-by-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one

- Supports High Drive and High Sink I/O mode

- Supports software selectable slew rate control

- Configurable default I/O mode of all pins after reset by CIOINI (CONFIG0[10]) setting

- CIOIN = 0, all GPIO pins in Quasi-bidirectional mode after chip reset

- CIOIN = 1, all GPIO pins in input mode after chip reset

- GPIOA supports the pull-up and pull-low resistor enabled in four I/O modes

- GPIOB to GPIOD internal pull-up resistor enabled only in Quasi-bidirectional I/O mode

- Enabling the pin interrupt function will also enable the wake-up function

### 6.5.3 GPIO Interrupt and Wake-up Function

Each GPIO pin can be set as chip interrupt source by setting correlative RHIEN (Px\_INTEN[n+16])/FLIEN (Px\_INTEN[n]) bit and TYPE (Px\_INTTYPE[n]). There are five types of interrupt conditions to be selected: low level trigger, high level trigger, falling edge trigger, rising edge trigger and both rising and falling edge trigger. For edge trigger condition, user can enable input signal de-bounce function to prevent unexpected interrupt happened which caused by noise. The de-bounce clock source and sampling cycle period can be set through DBCLKSRC (GPIO\_DBCTL[4]) and DBCLKSEL (GPIO\_DBCTL[3:0]) register.

The GPIO can also be the chip wake-up source when chip enters Idle/Power-down mode. The setting of wake-up trigger condition is the same as GPIO interrupt trigger.

### 1. To ensure the I/O status before entering Idle/Power-down mode

When using toggle GPIO to wake-up system, user must make sure the I/O status before entering Idle/Power-down mode according to the relative wake-up settings.

For example, if configuring the wake-up event occurred by I/O rising edge/high level trigger, user must make sure the I/O status of specified pin is at low level before entering Idle/Power-down mode; and if configuring I/O falling edge/low level trigger to trigger a wake-up event, user must make sure the I/O status of specified pin is at high level before entering Power-down mode.

### 2. To disable the I/O de-bounce function before entering Idle/Power-down mode

If the specified wake-up I/O pin with enabling input signal de-bounce function, system will encounter two GPIO interrupt events while the system is woken up by this GPIO pin. One interrupt event is caused by wake-up function, the other is caused by I/O input de-bounce function. User should be disable the de-bounce function before entering Idle/Power-down mode to avoid the second interrupt event occurred after system woken up.

## 6.10 Watchdog Timer (WDT)

### 6.10.1 Overview

The Watchdog Timer is used to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, the Watchdog Timer supports the function to wake-up system from Idle/Power-down mode.

### 6.10.2 Features

- 18-bit free running up counter for Watchdog Timer time-out interval

- Selectable time-out interval (24 ~ 218) WDT\_CLK cycle and the time-out interval period is 104 ms ~ 26.3168 s if WDT\_CLK = 10 kHz

- System kept in reset state for a period of (1 / WDT\_CLK) \* 63

- Supports Watchdog Timer time-out wake-up function only if WDT clock source is selected as 10 kHz

## 6.13 USCI – SPI Mode

### 6.13.1 Overview

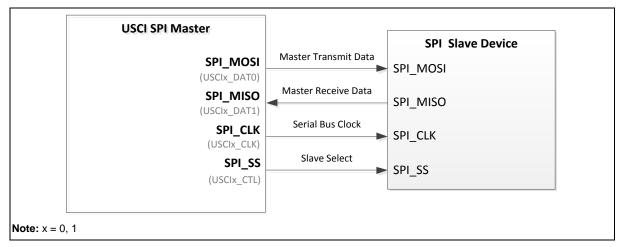

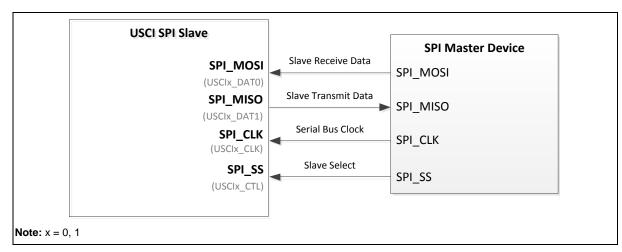

The SPI protocol of USCI controller applies to synchronous serial data communication and allows full duplex transfer. It supports both master and Slave operation mode with the 4-wire bi-direction interface. SPI mode of USCI controller performs a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. The SPI mode is selected by FUNMODE (USPI\_CTL[2:0]) = 0x1.

The SPI protocol can operate as master or Slave mode by setting the SLAVE (USPI\_PROTCTL[0]) to communicate with the off-chip SPI Slave or master device. The application block diagrams in master and Slave mode are shown as Figure 6.13-1 and Figure 6.13-2.

Figure 6.13-1 SPI Master Mode Application Block Diagram (x=0, 1)

Figure 6.13-2 SPI Slave Mode Application Block Diagram (x=0, 1)

## 6.13.2 Features

# 8.4 Analog Characteristics

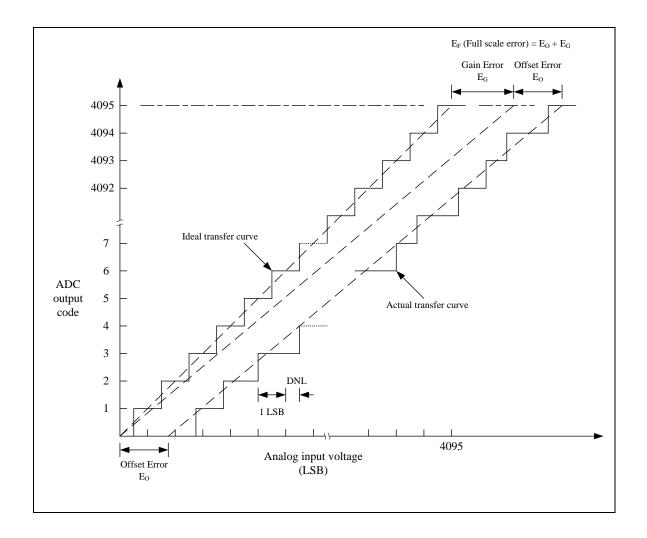

## 8.4.1 12-bit SAR ADC

| Symbol            | Parameter                                          | Min | Тур       | Max       | Unit               | Test Condition                                              |

|-------------------|----------------------------------------------------|-----|-----------|-----------|--------------------|-------------------------------------------------------------|

| -                 | Resolution                                         | -   | -         | 12        | Bit                | -                                                           |

| DNL               | Differential Nonlinearity Error                    | -   | 2         | -         | LSB                | V <sub>DD</sub> = 3.0~5.5 V                                 |

| INL               | Integral Nonlinearity Error                        | -   | ±2        | -         | LSB                | V <sub>DD</sub> = 3.0~5.5 V                                 |

| Eo                | Offset Error                                       | -   | ±1        | -         | LSB                | V <sub>DD</sub> = 3.0~5.5 V                                 |

| E <sub>G</sub>    | Gain Error (Transfer Gain)                         | -   | -1        | -         | LSB                | V <sub>DD</sub> = 3.0~5.5 V                                 |

| EA                | Absolute Error                                     | -   | ±3        | -         | LSB                | V <sub>DD</sub> = 3.0~5.5 V                                 |

| -                 | Monotonic                                          |     | Guarantee | b         | -                  | -                                                           |

| F <sub>ADC</sub>  | ADC Clock Frequency                                |     | 12        | 16        | MHz                | V <sub>DD</sub> = 3.0 ~5.5 V                                |

| Fs                | Sample Rate (F <sub>ADC</sub> /T <sub>CONV</sub> ) |     |           | 700       | kSPS               | V <sub>DD</sub> = 3.0~5.5 V                                 |

| T <sub>ACQ</sub>  | Acquisition Time (Sample Stage)                    | N+1 |           |           | 1/F <sub>ADC</sub> | $V_{DD}$ = 3.0 ~5.5 V<br>N is sampling counter,<br>N=1~1024 |

|                   |                                                    | 200 |           |           | ns                 | V <sub>DD</sub> = 3.0~5.5 V                                 |

| T <sub>CONV</sub> | Conversion Time                                    |     | 1000      | 1050      | ns                 | V <sub>DD</sub> = 3.0~5.5 V                                 |

| V <sub>DD</sub>   | Supply Voltage                                     | 3.0 | -         | 5.5       | V                  | -                                                           |

| I <sub>DDA</sub>  | Supply Current (Avg.)                              | -   | 1         | -         | mA                 | V <sub>DD</sub> = 5.5 V                                     |

| V <sub>IN</sub>   | Analog Input Voltage                               | 0   | -         | $AV_{DD}$ | V                  | -                                                           |

| C <sub>IN</sub>   | Input Capacitance                                  | -   | 1.6       | -         | pF                 | -                                                           |

| R <sub>IN</sub>   | Input Load                                         | -   | 2.5       | -         | kΩ                 | -                                                           |

Note: ADC voltage reference is same with  $V_{\text{DD}}$

## 8.4.2 LDO & Power Management

| Symbol           | Parameter       | Min | Тур | Мах | Unit | Test Condition |

|------------------|-----------------|-----|-----|-----|------|----------------|

| V <sub>DD</sub>  | DC Power Supply | 2.1 | -   | 5.5 | V    | -              |

| V <sub>LDO</sub> | Output Voltage  |     | 1.5 |     | V    | -              |

| ТА               | Temperature     | -40 | 25  | 105 | °C   |                |

Note: It is recommended a 0.1 $\mu$ F bypass capacitor is connected between V<sub>DD</sub> and the closest V<sub>SS</sub> pin of the device.

## 8.4.3 Low Voltage Reset

| Symbol           | Parameter      | Min | Тур | Max | Unit | Test Condition |

|------------------|----------------|-----|-----|-----|------|----------------|

| AV <sub>DD</sub> | Supply Voltage | 2.1 | -   | 5.5 | V    | -              |

| T <sub>A</sub>   | Temperature    | -40 | 25  | 105 | °C   | -              |