# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | SmartCard, UART/USART                                                     |

| Peripherals                | LED, POR, WDT                                                             |

| Number of I/O              | 14                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | Flash RAM                                                                 |

| EEPROM Size                | 16К х 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 5.4V                                                              |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 24-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5121-icsul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Figure 6. Push-pull Output Configuration

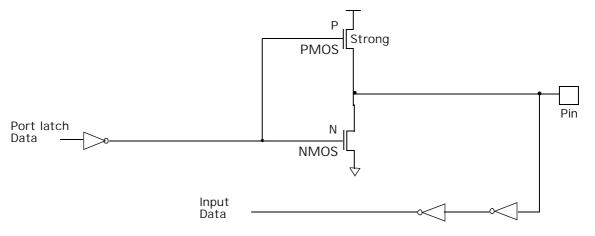

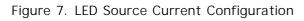

LED Output Configuration The input only configuration is shown in Figure 7.

Note: The port can be configured in quasi bi-directional mode and the level of current can be programmed by means of LEDC and LEDCON1 registers before switching the led on by writing a logical O in Port latch.

A/T8xC5121

Table 2. SFR Addresses and Reset Values

|     | 0/8               | 1/9                                     | 2/A                  | 3/B                                     |   | 4/C                  |   | 5/D                  |   | 6/E                  | 7/F                  |     |

|-----|-------------------|-----------------------------------------|----------------------|-----------------------------------------|---|----------------------|---|----------------------|---|----------------------|----------------------|-----|

| F8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | FFh |

| F0h | B<br>0000 0000    | LEDCON<br>XXXX 0000                     |                      |                                         |   |                      |   |                      |   |                      |                      | F7h |

| E8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | EFh |

| E0h | ACC<br>0000 0000  |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | E7h |

| D8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | DFh |

| D0h | PSW<br>0000 0000  | RCON<br>XXXX OXXX                       |                      |                                         |   |                      |   |                      |   |                      |                      | D7h |

| C8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | CFh |

| C0h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | C7h |

| B8h | IPL0<br>XXX0 0000 | SADEN<br>0000 0000                      | ISEL<br>0000 0100    |                                         |   |                      |   |                      |   |                      | DCCKPS<br>XXXX XX11  | BFh |

| B0h | P3<br>1111 1111   | IE1<br>XXXX 0XXX                        | IPL1<br>XXXX 0XXX    | IPH1<br>XXXX 0XXX                       | 0 | SCWT0 *<br>1000 0000 | 0 | SCWT1 *<br>0010 0101 | 0 | SCWT2 *<br>0000 0000 | IPH0<br>XXX0 0000    | B7h |

|     |                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1000000000           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1 | SCGT0 *<br>0000 1100 | 1 | SCGT1*<br>0000 0000  | 1 | SCICR *<br>0000 0000 |                      |     |

| A8h | IE0<br>0XX0 0000  | SADDR<br>0000 0000                      | SCTBUF*<br>0000 0000 | SCSR<br>XXX0 1000                       | 0 | SCCON *<br>0X000     | 0 | SCISR*<br>10X0 0000  | 0 | SCIIR*<br>0X00 0000  | CKCON1<br>XXXX 0XXX  | AFh |

|     |                   |                                         | SCRBUF<br>0000 000   |                                         | 1 | SCETU0<br>0111 0100  | 1 | SCETU1<br>0XXX       | 1 | SCIER *<br>0X00 0000 |                      |     |

| A0h | P2<br>1111 1111   |                                         | AUXR1<br>XXX XXX0    |                                         |   |                      |   |                      |   | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X0000 | A7h |

| 98h | SCON<br>XXX0 0000 | SBUF<br>XXXX XXXX                       | BRL<br>0000 0000     | BDRCON<br>XXX0 0000                     |   |                      |   |                      |   |                      |                      | 9Fh |

| 90h | P1<br>XX11 1111   | SIOCON<br>00XX 0000                     |                      |                                         |   |                      |   |                      |   |                      | CKRL<br>XXXX 111X    | 97h |

| 88h | TCON<br>0000 0000 | TMOD<br>0000 0000                       | TL0<br>0000 0000     | TL1<br>0000 0000                        |   | TH0<br>0000 0000     |   | TH1<br>0000 0000     |   | AUXR<br>00XX XX00    | CKCON0<br>X0X0 X000  | 8Fh |

| 80h | P0<br>1111 1111   | SP<br>0000 0111                         | DPL<br>0000 0000     | DPH<br>0000 0000                        |   | 20                   |   |                      |   |                      | PCON<br>00XX XX00    | 87h |

|     | 0/8               | 1/9                                     | 2/A                  | 3/B                                     |   | 4/C                  |   | 5/D                  |   | 6/E                  | 7/F                  |     |

Reserved

| SCRS Bit (SCSR.0) | (*)       |

|-------------------|-----------|

| 0                 | SFR value |

| 1                 | SFR value |

The ports status under Power-down is the status which was valid before entering mode.

The INT1 interrupt is a multiplexed input (see Interrupt paragraph) with CPRES (Cal detection) and Rxd (UART Rx). So these three inputs can be used to exit from Powe down mode. The configurations which must be set are detailed below:

Rxd input:

RXEN (ISEL.O) must be set

EX1 (IEO.2) must be set

A low level detected during more than 100 microseconds exit from Powerdown

CPRES input:

PRSEN (ISEL.1) must be set

EX1 (IEO.2) must be set

EA (IEO.7) must be set

In the INT1 interrupt vector, the CPLEV Bit (ISEL.7) must be inverted and PRESIT Bit (ISEL.5) must be reset.

Figure 10. Power-down Exit Waveform

| INTO —         |                                                                                                                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT1           |                                                                                                                                                                                                                   |

| XTAL1          |                                                                                                                                                                                                                   |

| _              | Active phase Power-down phase 🗶 Oscillator restart phaseActive phase                                                                                                                                              |

|                | Exiting from Power-down by reset redefines all the SFRs, exiting from Power-down external interrupt does no affect the SFRs.                                                                                      |

|                | Exiting from Power-down by either reset or external interrupt does not affect the in RAM content.                                                                                                                 |

|                | Note: If idle mode is activated with Power-down mode (IDL and PD bits set), the exit sequer<br>is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared an<br>idle mode is not entered. |

| SCI Control    | Prior to entering Power-down mode, a de-activation of the Smart Card system mus performed.                                                                                                                        |

| LED Control    | Prior to entering Power-down mode, if the LED mode output is used, the medium pull must be disconnected by setting the LEDPD bit in the PCON Register (PCON 3).                                                   |

| Low Power Mode | Only in Power-down mode, in order to reduce the power consumption, the user c choose to select this low-power mode.                                                                                               |

|                | The activation reference is the following.                                                                                                                                                                        |

|                | First select the Low-power mode by setting the LP bit in the AUXR Register (AUXI 6)                                                                                                                               |

|                | The activation of Power-down can then be done.                                                                                                                                                                    |

#### Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port O when used w external program or data memory. Nevertheless, during internal code execution, AL signal is still generated.

Only in case of PLCC52 version, in order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location O (See Table 4). As soon as AO set, ALE is no longer output but remains active during MOVX and MOVC instructio and external fetches. During ALE disabling, ALE pin is weakly pulled high.

Power Modes Control Registers Table 3. PCON Register

PCON (S:87h) Power Configuration Register

| 7             | 6               | 5                                                                    | 4                                                                                                                                                                                                                                                              | 3             | 2            | 1             | 0            |      |  |  |

|---------------|-----------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------|--------------|------|--|--|

| SMOD1         | SMODO           | -                                                                    | -                                                                                                                                                                                                                                                              | LEDPD         | GFO          | PD            | IDL          |      |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                          | scription                                                                                                                                                                                                                                                      |               |              |               |              |      |  |  |

| 7             | SMOD1           |                                                                      | ble Baud Rate bit<br>to double the Baud Rate when Timer 1 is used and mode 1, 2 or 3 is selec<br>N register.                                                                                                                                                   |               |              |               |              |      |  |  |

| 6             | SMODO           | accesses to S<br>When set, rea                                       | N Select bit<br>n cleared, read/write accesses to SCON.7 are to SMO bit and read/writ<br>sses to SCON.6 are to SM1 bit.<br>n set, read/write accesses to SCON.7 are to FE bit and read/write acce<br>N.6 are to OVR bit. SCON is Serial Port Control register. |               |              |               |              |      |  |  |

| 5             |                 | Reserved                                                             |                                                                                                                                                                                                                                                                |               |              |               |              | 1    |  |  |

| 4             |                 | Reserved                                                             |                                                                                                                                                                                                                                                                |               |              |               |              | 1    |  |  |

| 3             | LEDPD           | When cleaned                                                         | ED Control Power-Down Mode bits<br>/hen cleaned the I/O pull-up is the standard C51 pull-up control. When set<br>redium pull-up is disconnected.                                                                                                               |               |              |               |              |      |  |  |

| 2             | GFO             | General-purpo<br>One use is to<br>during Idle mo                     | indicate we                                                                                                                                                                                                                                                    | ther an inter | rupt occurre | ed during nor | mal operatio | n or |  |  |

| 1             | PD              | Cleared by har<br>Set to activat                                     | ower-down Mode bit<br>eared by hardware when an interrupt or reset occurs.<br>et to activate the Power-down mode.<br>IDL and PD are both set, PD takes precedence.                                                                                             |               |              |               |              |      |  |  |

| 0             | IDL             | Idle Mode bit<br>Cleared by har<br>Set to activat<br>If IDL and PD a | te the Idle m                                                                                                                                                                                                                                                  | node.         |              | ccurs.        |              |      |  |  |

Reset Value = XOXX XXOOb

Table 5. IEO Register

IEO

Interrupt Enable Register (A8h)

| 7             | 6               | 5                                     | 4                                                                                                                                                                                                       | 3                                            | 2             | 1             | 0        |  |  |

|---------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|---------------|----------|--|--|

| EA            | -               | -                                     | ES                                                                                                                                                                                                      | ET1                                          | EX1           | ETO           | EXO      |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                            | on                                                                                                                                                                                                      |                                              |               |               |          |  |  |

| 7             | EA              | Clear to o<br>Set to en<br>If EA = 1, | able All interrupt bit<br>ar to disable all interrupts.<br>• to enable all interrupts.<br>A = 1, each interrupt source is individually enabled or disabled by settin<br>aring its interrupt enable bit. |                                              |               |               |          |  |  |

| 6             | -               | Reserved<br>The value                 | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.                                                                                                                           |                                              |               |               |          |  |  |

| 5             | -               | Reserved<br>The value                 | read from t                                                                                                                                                                                             | his bit is ind                               | eterminate. I | Do not set tl | nis bit. |  |  |

| 4             | ES              | Clear to d                            | Serial port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                                                                                               |                                              |               |               |          |  |  |

| 3             | ET1             | Clear to d                            | Timer 1 overflow interrupt Enable bit<br>Clear to disable Timer 1 overflow interrupt.<br>Set to enable Timer 1 overflow interrupt.                                                                      |                                              |               |               |          |  |  |

| 2             | EX1             | Clear to d                            | External interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                        |                                              |               |               |          |  |  |

| 1             | ETO             | Clear to d                            | Timer O overflow interrupt Enable bit<br>Clear to disable Timer O overflow interrupt.<br>Set to enable Timer O overflow interrupt.                                                                      |                                              |               |               |          |  |  |

| 0             | EXO             | Clear to d                            |                                                                                                                                                                                                         | nable bit<br>nal interrupt<br>Il interrupt O |               |               |          |  |  |

Reset Value = OXXO 0000b

the different counters. One of the most important counters is the guard time counter gives time slots corresponding to the character frame.

It is enabled only in UART mode.

The transition from the receipt mode to the transmit mode is done automatically. Pri is given to the transmission.

ETU Counter The ETU (Elementary Timing Unit) counter controls the working frequency of the bar shifter, in fact, it generates the enable signal of the barrel shifter.

It is 11 bits wide and there is a special compensation mode activated with the most nificant bit that allows non integer ETU value with a working clock equal to the clock.

But the decimal value is limited to a half clock cycle. In fact the bit duration is not fix takes turns in n clock cycles and n-1 clock cycles. The character duration (10 bits also equal to  $10^{*}(n+1/2)$  clock cycles.

This allows to reach the required precision of the character duration specified by ISO7816 standard.

example: F = 372 D = 32 = > ETU = 11.625 clock cycles.

ETU = (ETU[10-0] -0.5 \* COMP)\*f with ETU[10-0] = 12, COMP = 1 (bit 7 of SCETU1)

To achieve this clock rate we activated the compensation mode and we programm the ETU duration to 12 clock cycles.

The result will be a full character duration (10 bits) equal to 11.5 clock cycles.

Guard Time Counter The minimum time between the leading edge of the start bit of a character and the ling edge of the start bit of the following character transmitted (Guard time) is control by one counter.

It is 9 bits wide and is incremented at the ETU rate.

Figure 15. Guard Time Counter

| ETU Counter | _ |  |  |

|-------------|---|--|--|

|             |   |  |  |

|             |   |  |  |

|             |   |  |  |

Waiting Time Counter (WT) The WT counter is a 24 bits down counter which can be loaded with the value conta in the SCWT2, SCWT1, SCWT0 registers. Its main purpose is time out signal genera tion. It is 24 bits wide and is decremented at the ETU rate. The ETU counter acts a prescaler (See Figure 16).

When the WT counter timeout, an interrupt is generated and the SCIB function locked: reception and emission are disabled. It can be enabled by resetting the macro reloading the counter.

Figure 16. Waiting Time Counter

The counter is loaded, if WTEN = 0, during the write of SCWT2 register.

This counter is available in both UART and manual modes. But the behaviour depends

A/T8xC5121

Table 16. SCCON Register

SCCON (S:ACh, SCRS = 0) Smart Card Contacts Register

| 7          | 6                   | 5                                 | 4                                                                                                                                                                                                                                                | 3                          | 2             | 1             | 1 0                                              |          |  |  |

|------------|---------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|---------------|--------------------------------------------------|----------|--|--|

| CLK        | -                   | CARDC8                            | CARDC4                                                                                                                                                                                                                                           | CARDIO                     | CARDCLK       | CARDRST       | CARDVCC                                          | ]        |  |  |

| Bit Number | Bit Mnemoni         | nic Descript                      | tion                                                                                                                                                                                                                                             |                            |               |               |                                                  | ]        |  |  |

| 7          | CLK                 | Clear th<br>Set this<br>Note: int | rd Clock Selection<br>ar this bit to use the CardClk bit (CARDCLK) to drive Card CLK pin.<br>t this bit to use XTAL signal to drive the Card CLK pin.<br>te: internal synchronization avoids any glitch on the CLK pin when<br>itching this bit. |                            |               |               |                                                  |          |  |  |

| 6          | -                   | Reserved<br>The valu              | -                                                                                                                                                                                                                                                | this bit is                | indetermina   | ate. Do not   | change this bit o                                | or write |  |  |

| 5          | CARDC8              |                                   | rd C8<br>ear this bit to drive a low level on the Card C8 pin.<br>t this bit to set a high level on the Card C8 pin.                                                                                                                             |                            |               |               |                                                  |          |  |  |

| 4          | CARDC4              |                                   |                                                                                                                                                                                                                                                  |                            |               |               |                                                  |          |  |  |

| 3          | CARDIO              | driven to<br>Then thi             |                                                                                                                                                                                                                                                  |                            |               |               |                                                  |          |  |  |

| 2          | CARDCLK             |                                   |                                                                                                                                                                                                                                                  |                            | SCCON Reg     | ister, the va | alue of this bit is                              | driven   |  |  |

| 1          | CARDRST             | Set this                          | T<br>his bit to driv<br>bit to set a<br>not allowed                                                                                                                                                                                              | a high level               | I on the Card |               | I.                                               |          |  |  |

| 0          | CARDV <sub>CC</sub> | Clear th<br>bits of S<br>Set this | SCC register                                                                                                                                                                                                                                     | r have no e<br>er-on the C | effect while  | this bit is c | et its power-off.<br>cleared.<br>vation sequence |          |  |  |

Reset Value = 0X00 0000b

A/T8xC5121

#### Table 24. SCETUO Register

SCETUO (S:ACh, SCRS = 1) Smart Card ETU Register O

| 7             | 6               | 5                         | 4            | 3                                              | 2            | 1           | 0    |       |

|---------------|-----------------|---------------------------|--------------|------------------------------------------------|--------------|-------------|------|-------|

| ETU7          | ETU6            | ETU5                      | ETU4         | ETU3                                           | ETU2         | ETU1        | ETUO |       |

| Bit<br>Number | Bit<br>Mnemonic | Description               |              |                                                |              |             |      |       |

| 7-0           | ETU[7:0]        | frequency.<br>According t | o ISO7816, E | it is (ETU[10<br>ETU[10:0] car<br>of ETU[10:0] | n be set bet | ween 11 and |      | d CLK |

Reset Value = 0111 0100b

Table 25. SCGT1 Register

SCGT1 (S:B5h, SCRS = 1) Smart Card Transmit Guard Time Register 1

| 7             | 6               | 5                        | 4                                                                                       | 3 | 2            | 1            | 0          |  |  |

|---------------|-----------------|--------------------------|-----------------------------------------------------------------------------------------|---|--------------|--------------|------------|--|--|

|               |                 |                          |                                                                                         |   |              |              | GT8        |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              |                                                                                         |   |              |              |            |  |  |

| 7-1           |                 | Reserved<br>The value re | Reserved<br>The value read from these bits is indeterminate. Do not change these bits . |   |              |              |            |  |  |

| 0             | GT8             |                          | ard Time MS<br>her with the                                                             |   | ard Time LSE | 3 (see SCGTO | Register). |  |  |

Reset Value = XXXX XXXOb

Table 26. SCGTO Register

SCGTO (S:B4h, SCRS = 1) Smart Card Transmit Guard Time Register 0

| 7             | 6               | 5                           | 4   | 3           | 2   | 1   | 0                            |  |

|---------------|-----------------|-----------------------------|-----|-------------|-----|-----|------------------------------|--|

| GT7           | GT6             | GT5                         | GT4 | GT3         | GT2 | GT1 | GTO                          |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                 |     |             |     |     |                              |  |

| 7-0           | GT[7:0]         | The minimul<br>GT[8:0] * ET | Ū.  | een two cor |     |     | ansmit mode<br>(11 to 254+1) |  |

Reset Value = 0000 1100b

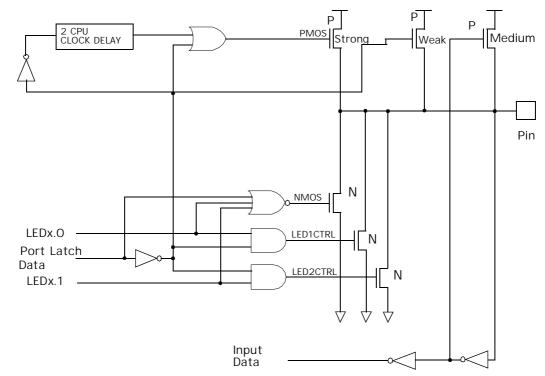

## Interrupt System

The T8xC5121 has a total of 6 interrupt vectors: four external interrup ItsT(IKOP, CPRES, RxD), two Timer 0 interrupts (Timer 0s 0 and 1), serial port interrupt and Sm Card Interface interrupt. These interrupts are shown in Figure 23.

Figure 23. Interrupt Control System

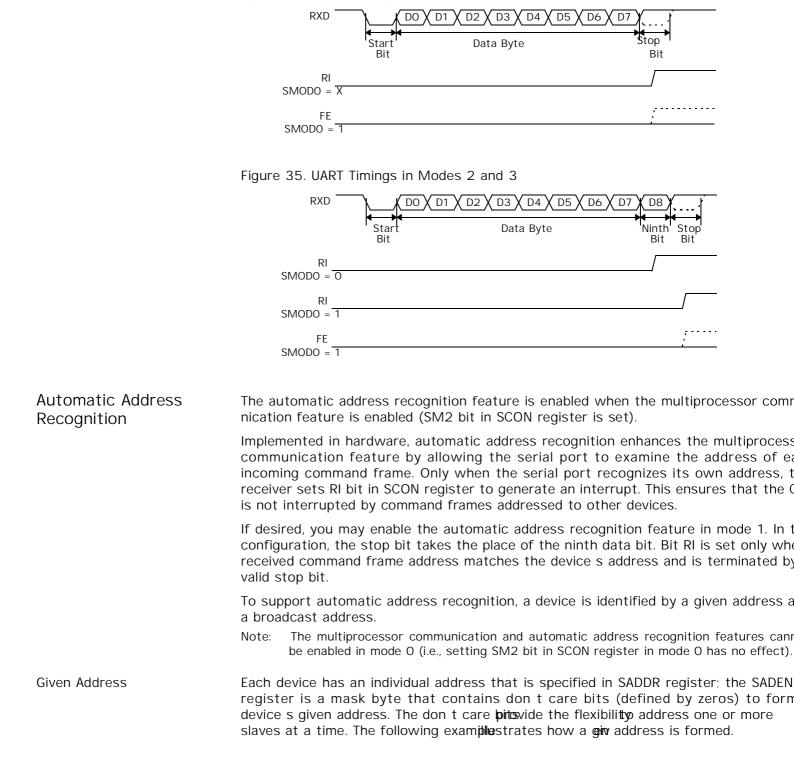

Each of the interrupt sources can be individually enabled or disabled by setting or cleing a bit in the Interrupt Enable register (see Figure 32). This register also contain global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one of four priority levels setting or clearing a bit in the Interrupt Priority register (see Figure 36) and in Interrupt Priority High register (see Figure 38). Table 30 shows the bit values and private levels associated with each combination.

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

## Table 33. IE1 Register

| 7             | 6               | 5                                                                               | 4                                                                                               | 3    | 2 | 1 | 0 |  |

|---------------|-----------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|---|---|---|--|

| -             | -               | -                                                                               | -                                                                                               | ESCI | - | - | - |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                                                                      | Description                                                                                     |      |   |   |   |  |

| 7             | -               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

| 6             | -               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

| 5             | -               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

| 4             | -               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

| 3             | ESCI            | Clear to d                                                                      | SCI Interrupt Enable<br>Clear to disable the SCI interrupt.<br>Set to enable the SCI interrupt. |      |   |   |   |  |

| 2             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                                                                                 |      |   |   |   |  |

| 1             | -               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

| 0             | _               | Reserved<br>The value                                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                 |      |   |   |   |  |

Reset Value = XXXX OXXXb

# **Electrical Characteristics**

## Absolute Maximum Ratings

| Ambiant Temperature Under Bias25C to 85C              |

|-------------------------------------------------------|

| Storage Temperature                                   |

| Voltage onV $_{\rm CC}$ to $V_{\rm S}$ 0.5V to + 6.0V |

| Voltage on Any Pin to_sy0.5V to $~v_{cc}$ + 0.5V      |

Note: Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

## DC Parameters

| Symbol                               | Parameter                                  | Min                                                                        | Тур   | Max                      | Unit                                                  | Test Conditions                      |

|--------------------------------------|--------------------------------------------|----------------------------------------------------------------------------|-------|--------------------------|-------------------------------------------------------|--------------------------------------|

| V <sub>IL</sub>                      | Input Low Voltage                          | -0.5                                                                       |       | 0.2 <sub>€C</sub> V- 0.1 | V                                                     |                                      |

| V <sub>IH</sub>                      | Input High Voltage<br>except XTAL1, RST    | .2 V <sub>CC</sub> + .9                                                    |       | V <sub>CC</sub> + 0.5    | V                                                     |                                      |

| V <sub>IH1</sub>                     | Input H <u>igh V</u> oltage,<br>XTAL1, RST | 0.7 V <sub>CC</sub>                                                        |       | V <sub>CC</sub> + 0.5    | V                                                     |                                      |

| V <sub>OL</sub>                      | Output Low Voltage<br>Port O and 2         |                                                                            |       | 0.45                     | V                                                     | δ <sub>L =</sub> 1.6 mA              |

| V <sub>OH</sub>                      | Output High Voltage<br>Port O and 2        | 0.9 x V <sub>C</sub>                                                       |       |                          | V                                                     | Ι <sub>OH</sub> = -40 μΑ             |

| DI <sub>CC</sub>                     | Digital Supply Outpu<br>Current            |                                                                            | 6     | 10                       | mA                                                    | G_ = 100 nF                          |

| DV <sub>CC</sub>                     | Digital Supply<br>Voltage                  | 2.5                                                                        | 2 .9  | 3.0                      | V                                                     | C <sub>L</sub> = 100 nF<br>DIcc=10mA |

| lcc                                  | Normal Power Down<br>mode                  |                                                                            | 80    | 100                      | μA                                                    | 25°C                                 |

| lcc                                  | Pulsed Power Down<br>mode                  |                                                                            | 20    | 30                       | μA                                                    | 50°C Vcc=3V                          |

| Іссор                                | Power Supply<br>current                    | $I_{ccop}$ = 0.25 Freq (MHz) +4 mA<br>$I_{ccIDLE}$ = 0.03 Freq (MHz) +5 mA |       |                          | V <sub>CC</sub> = 5.4V and<br>Bootloader<br>execution |                                      |

| V <sub>PFDP</sub>                    | Power-fail high leve<br>threshold          |                                                                            | 2 .55 |                          | V                                                     |                                      |

| V <sub>PFDM</sub>                    | Power-fail low level threshold             |                                                                            | 2 .45 |                          | V                                                     |                                      |

| t <sub>G</sub>                       | Power Fail glitch<br>time                  |                                                                            |       | 50                       | ns                                                    |                                      |

| t <sub>rise,</sub> t <sub>fall</sub> | $V_{\text{DD}}$ rise and fall time         | 1 µs                                                                       |       | 600                      | sec.                                                  |                                      |

Table 72. Core DC Parameters (XTAL, RST PO, P2, ALE, PSEN, EA)