# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | SmartCard, UART/USART                                                    |

| Peripherals                | LED, POR, WDT                                                            |

| Number of I/O              | 14                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | Flash RAM                                                                |

| EEPROM Size                | 16K x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 5.4V                                                             |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 24-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 24-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5121-ysul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Description

T8xC5121 is a high performance CMOS ROM/CRAM derivative of the 80C51 CMOS single chip 8-bit microcontrollers.

T8xC5121 retains the features of the Atmel 80C51 with extended ROM capacity (16 Kbytes), 512 bytes of internal RAM, a 4-level interrupt system, two 16-bit timer/counters (T0/T1), a full duplex enhanced UART (EUART) with baud rate generator (BRG) and an on-chip oscillator.

In addition, the T8xC5121 have, a Multi protocol Smart Card Interface, a dual data pointer, 2 programmable LED current sources (2-4-10 mA) and a hardware Watchdog.

T89C5121 Flash RAM version and T85C5121 Code RAM version can be loaded by In-System Programming (ISP) software residing in the on-chip ROM from a low-cost external serial EEPROM or from R232 interface.

T8xC5121 have 2 software-selectable modes of reduced activity for further reduction in power consumption.

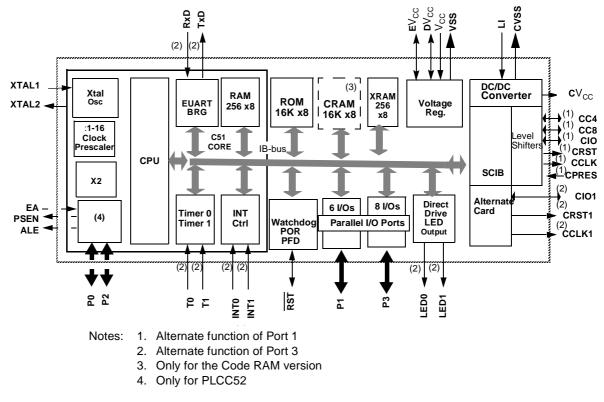

# **Block Diagram**

Figure 1. Block Diagram

2

#### Table 1. Ports Description (Continued)

|      | Signal | scription (Co | Internal<br>Power |     |      |                                                                                                                                                                                                                                                               |

|------|--------|---------------|-------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port | Name   | Alternate     | Supply            | ESD | Туре | Description                                                                                                                                                                                                                                                   |

| P3.0 | RxD    |               | EV <sub>CC</sub>  |     | I    | UART function<br>Receive data input                                                                                                                                                                                                                           |

|      |        |               |                   |     | I/O  | Input/Output function<br>P3.0 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |

|      |        |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |

| P3.1 | TxD    |               | EV <sub>CC</sub>  |     | 0    | UART function<br>Transmit data output<br>OE active at low or high level depending of PMSOEN bits in SIOCON Reg.                                                                                                                                               |

|      |        |               |                   |     | I/O  | Input/Output function<br>P3.1 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |

|      |        |               |                   |     | z    | Reset configuration<br>High impedance due to PMOS switched OFF                                                                                                                                                                                                |

| P3.2 | INT0   |               | DV <sub>CC</sub>  |     | I    | External interrupt 0<br>INTO input set IE0 in the TCON register. If bit IT0 in this register is set, bits IE0<br>are set by a falling edge on INT0. If bit IT0 is cleared, bits IE0 is set by a low<br>level on INT0.                                         |

|      |        |               |                   |     | I/O  | Input/Output function<br>P3.2 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |

|      |        |               |                   |     | I    | Timer 0: Gate input<br>INT0 serves as external run control for Timer 0 when<br>selected in TCON register.                                                                                                                                                     |

|      |        |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |

| P3.3 | INT1   | OE            | EV <sub>cc</sub>  |     | I    | External Interrupt 1<br>INT1 input set OEIT in ISEL Register, IE1 in the TCON register.<br>If bit IT1 in this register is set, bits OEIT and IE1 are set by a falling edge on<br>INT1. If bit IT1 is cleared, bits OEIT and IE1 is set by a low level on INT1 |

|      |        |               |                   |     | I    | <b>UART function</b><br>Output enable. A low or high level (depending OELEV bit in<br>ISEL Register) on this pin disables the PMOS transistors of TxD<br>(P3.1) and T0 (P3.4). This function can be disabled by software                                      |

|      |        |               |                   |     | I/O  | Input/Output function<br>P3.3 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |

|      |        |               |                   |     | I    | Timer 1 function: Gate input<br>INT1 serves as external run control for Timer 1 when<br>selected in TCON register.                                                                                                                                            |

|      |        |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |

| P3.4 |        | ТО            | EV <sub>CC</sub>  |     | 0    | UART function<br>OE active at low or high level depending of PMSOEN<br>bits in SIOCON Reg.                                                                                                                                                                    |

#### Table 1. Ports Description (Continued)

| Port | Signal<br>Name | Alternate | Internal<br>Power<br>Supply | ESD | Туре | Description                                                                                                                                                                                                                                    |

|------|----------------|-----------|-----------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.4 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                             |

|      |                |           |                             |     | I    | Timer 0 function: External clock input<br>When Timer 0 operates as a counter, a falling edge on the T0 pin<br>increments the count.                                                                                                            |

|      |                |           |                             |     | z    | Reset configuration<br>High impedance due to PMOS switched OFF                                                                                                                                                                                 |

| P3.5 | CIO1           |           | DV <sub>CC</sub>            |     | I/O  | Alternate card function<br>Card I/O                                                                                                                                                                                                            |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.5 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                             |

|      |                |           |                             |     | I    | Timer 1 function: External clock input<br>When Timer 1 operates as a counter, a falling edge on the T1 pin<br>increments the count.                                                                                                            |

|      |                |           |                             |     | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                                                                                                                              |

| P3.6 | CCLK1          | LED0      | DV <sub>CC</sub>            |     | 0    | Alternate card function<br>Card clock                                                                                                                                                                                                          |

|      |                |           |                             |     | 0    | LED function<br>These pins can be directly connected to the cathode of standard<br>LED without external current limiting resistors. The typical current<br>of each output can be programmed by software to 2, 4 or 10 mA<br>(LEDCON register). |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.6 is a LED port.                                                                                                                                                                                                   |

|      |                |           |                             |     | I    | Reset configuration<br>Input at high level                                                                                                                                                                                                     |

| P3.7 | CRST1          |           | DV <sub>CC</sub>            |     | ο    | Alternate card function<br>Card reset                                                                                                                                                                                                          |

| P3.7 | CRST1          | LED1      | DV <sub>CC</sub>            |     | 0    | LED function<br>These pins can be directly connected to the cathode of standard<br>LED without external current limiting resistors. The typical current<br>of each output can be programmed by software to 2, 4 or 10 mA<br>(LEDCON register). |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.7 is a a LED port.                                                                                                                                                                                                 |

|      |                |           |                             |     | I    | Reset configuration<br>Input at high level                                                                                                                                                                                                     |

## Table 17. SCISR Register

SCISR (S:ADh, SCRS = 0) Smart Card UART Interface Status Register

| 7             | 6               | 5                                                                 | 4                                                                                                                                                                                                             | 3                                     | 2              | 1              | 0             |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|----------------|---------------|--|--|--|

| SCTBE         | CARDIN          | ClccOVF                                                           | CICCOVF CVCCOK SCWTO SCTC SCRC SCPE                                                                                                                                                                           |                                       |                |                |               |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                       |                                                                                                                                                                                                               |                                       |                |                |               |  |  |  |

| 7             | SCTBE           | This bit is set register of the                                   | SCIB transmit buffer empty<br>This bit is set by hardware when the Transmit Buffer is copied to the transmit shift<br>register of the Smart Card UART.<br>t is cleared by hardware when SCTBUF is written to. |                                       |                |                |               |  |  |  |

| 6             | CARDIN          | This bit is set software).                                        | Card presence status<br>This bit is set when a card is detected (debouncing filter has to be done in<br>oftware).<br>t is cleared otherwise.                                                                  |                                       |                |                |               |  |  |  |

| 5             | ClccOVF         | This bit is set                                                   | ICC overflow on card<br>This bit is set when the current on card is above the limit<br>It shall be cleared by the hardware .                                                                                  |                                       |                |                |               |  |  |  |

| 4             | CVccOK          | Card voltage<br>This bit is set<br>CVcc field.<br>It is cleared o | t when the ou                                                                                                                                                                                                 | tput voltage is                       | within the vol | tage range sp  | ecified by    |  |  |  |

| 3             | SCWTO           | This bit is set                                                   |                                                                                                                                                                                                               | when the Sm<br>eload of the co        |                |                |               |  |  |  |

| 2             | SCTC            | This bit is set<br>character.                                     | Smart card transmitted character<br>This bit is set by hardware when the Smart Card UART has transmitted a<br>character.<br>It shall be cleared by software after this register has been read.                |                                       |                |                |               |  |  |  |

| 1             | SCRC            | This bit is set                                                   |                                                                                                                                                                                                               | racter<br>when the Sm<br>/hen SCBUF i |                | T has received | d a character |  |  |  |

| 0             | SCPE            | This bit is set                                                   | Smart card parity error<br>This bit is set at the same time as SCTI or SCRI if a parity error is detected.<br>It shall be cleared by software after this register has been read.                              |                                       |                |                |               |  |  |  |

Reset Value = 1000 0000b

## Table 18. SCIIR Register

SCIIR (S:AEh, SCRS = 0) Smart Card UART Interrupt Identification Register (read only)

| 7             | 6        | :    | 5                                                                                                                                                                                                  | 4                                                            | 3                 | 2             | 1              | 0                  |  |

|---------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------|---------------|----------------|--------------------|--|

| SCTBI         | -        | Clcc | ERR                                                                                                                                                                                                | CVccERR                                                      | SCWTI             | SCTI          | SCRI           | SCPI               |  |

| Bit<br>Number | Bit Mnem | onic | Descri                                                                                                                                                                                             | ption                                                        |                   |               |                |                    |  |

| 7             | SCTE     | 31   | SCIB transmit buffer interrupt<br>This bit is set by hardware when the Transmit Buffer is copie<br>shift register of the Smart Card UART.<br>It is cleared by hardware when this register is read. |                                                              |                   |               |                | ed to the transmit |  |

| 6             | -        |      | <b>Reserv</b><br>The va                                                                                                                                                                            | <b>/ed</b><br>lue read from th                               | is bit is indeter | minate. Do no | ot change this | bit or write 0.    |  |

| 5             | ClccEF   | R    | <b>Card current status</b><br>This bit is set when the output current goes out of the current range.<br>It is cleared by hardware when this register is read.                                      |                                                              |                   |               |                |                    |  |

| 4             | CVccE    | RR   | <b>Card voltage status</b><br>This bit is set when the output voltage goes out of the voltage range specified by CVcc field.<br>It is cleared by hardware when this register is read.              |                                                              |                   |               |                |                    |  |

| 3             | SCW      | ГІ   | This bi                                                                                                                                                                                            | <b>card wait Time</b><br>t is set by hardw<br>ared by hardwa | are when the      |               |                | out.               |  |

| 2             | SCT      | I    | Smart card transmit interrupt<br>This bit is set by hardware when the Smart Card UART completes a<br>character transmission.<br>It is cleared by hardware when this register is read.              |                                                              |                   |               |                |                    |  |

| 1             | SCR      | I    | Smart card receive interrupt<br>This bit is set by hardware when the Smart Card UART completes a<br>character reception.<br>It is cleared by hardware when this register is read.                  |                                                              |                   |               |                |                    |  |

| 0             | SCP      | I    | Smart card parity error interrupt<br>This bit is set at the same time as SCTI or SCRI if a parity error is detected.<br>It is cleared by hardware when this register is read.                      |                                                              |                   |               |                |                    |  |

Reset Value = 0X00 0000b

## Table 19. SCIER Register

SCIER (S:AEh, SCRS = 1) Smart Card UART Interrupt Enable Register

| 7          | 6               | 5                    | 4                                                                                                                                                                                                                       | 3                 | 2              | 1               | 0     |  |  |

|------------|-----------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-----------------|-------|--|--|

| ESCTBI     | -               | ClccER               | ECVccER                                                                                                                                                                                                                 | ESCWTI            | ESCTI          | ESCRI           | ESCPI |  |  |

| Bit Number | Bit<br>Mnemonic | Descript             | ion                                                                                                                                                                                                                     |                   |                |                 |       |  |  |

| 7          | ESCTBI          | Clear this           | Smart Card UART Transmit Buffer Empty Interrupt Enable<br>Clear this bit to disable the Smart Card UART Transmit Buffer Empty interrupt.<br>Set this bit to enable the Smart Card UART Transmit Buffer Empty interrupt. |                   |                |                 |       |  |  |

| 6          | -               | Reserve<br>The value | d<br>e read from this                                                                                                                                                                                                   | s bit is indeterr | minate. Do not | t change this t | pit . |  |  |

| 5          | ClccER          | Clear this           | Card Current Error Interrupt Enable<br>Clear this bit to disable the Card Current Error interrupt.<br>Set this bit to enable the Card Current Error interrupt.                                                          |                   |                |                 |       |  |  |

| 4          | ECVccER         | Clear this           | Card Voltage Error Interrupt Enable<br>Clear this bit to disable the Card Voltage Error interrupt.<br>Set this bit to enable the Card Voltage Error interrupt.                                                          |                   |                |                 |       |  |  |

| 3          | ESCWTI          | Clear this           | ard Wait Timed<br>bit to disable to<br>bit to enable the                                                                                                                                                                | the Smart Car     | d Wait timeou  |                 |       |  |  |

| 2          | ESCTI           | Clear this           | Smart Card Transmit Interrupt Enable<br>Clear this bit to disable the Smart Card UART Transmit interrupt.<br>Set this bit to enable the Smart Card UART Transmit interrupt.                                             |                   |                |                 |       |  |  |

| 1          | ESCRI           | Clear this           | Smart Card Receive Interrupt Enable<br>Clear this bit to disable the Smart Card UART Receive interrupt.<br>Set this bit to enable the Smart Card UART Receive interrupt.                                                |                   |                |                 |       |  |  |

| 0          | ESCPI           | Clear this           | Smart Card Parity Error Interrupt Enable<br>Clear this bit to disable the Smart Card UART Parity Error interrupt.<br>Set this bit to enable the Smart Card UART Parity Error interrupt.                                 |                   |                |                 |       |  |  |

Reset Value = 0X00 0000b

A/T8xC5121

## Table 20. SCSR Register

SCSR (S:ABh) Smart Card Selection Register

| 7             | 6                  | 5                                      | 4                                                                                                                                                                                                                                                                           | 3       | 2             | 1            | 0    |  |  |  |  |

|---------------|--------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------|------|--|--|--|--|

| -             | -                  | -                                      | CREPSEL                                                                                                                                                                                                                                                                     | ALTKPS1 | ALTKPS0       | SCCLK1       | SCRS |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic    | Description                            |                                                                                                                                                                                                                                                                             |         |               |              |      |  |  |  |  |

| 7             | -                  | Reserved                               |                                                                                                                                                                                                                                                                             |         |               |              |      |  |  |  |  |

| 6             | -                  | Reserved                               |                                                                                                                                                                                                                                                                             |         |               |              |      |  |  |  |  |

| 5             | -                  | Reserved                               |                                                                                                                                                                                                                                                                             |         |               |              |      |  |  |  |  |

| 4             | CREPSEL            | Clear this bit                         | Character repetition selection<br>Clear this bit to select 5 times repetition before parity error indication<br>Set this bit to select 4 times repetition before parity error indication                                                                                    |         |               |              |      |  |  |  |  |

| 3-2           | ALTKPS1<br>ALTKPS0 | 00ALTKPS =<br>01ALTKPS =<br>10ALTKPS = | Alternate Card Clock prescaler factor         00ALTKPS = 0:       prescaler factor equals 1         01ALTKPS = 1:       prescaler factor equals 2         10ALTKPS = 2:       prescaler factor equals 4 (reset value)         11ALTKPS = 3:       prescaler factor equals 8 |         |               |              |      |  |  |  |  |

| 1             | SCCLK1             | Set to select                          | Alternate card clock selection<br>Set to select the prescaled clock (CCLK1)<br>Clear to select the standard port configuration (P3.6)                                                                                                                                       |         |               |              |      |  |  |  |  |

| 0             | SCRS               |                                        | register selection it selects which                                                                                                                                                                                                                                         |         | CIB registers | is accessed. |      |  |  |  |  |

Reset Value = XXX0 1000b

#### Table 21. SCTBUF Register

SCTBUF (S:AA, write-only, SCRS = 0) Smart Card Transmit Buffer Register

| 7          | 6         |      | 5           | 4                                                                                                                                                          | 3 | 2 | 1 | 0 |  |  |

|------------|-----------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|--|

|            |           |      |             |                                                                                                                                                            |   |   |   |   |  |  |

| Bit Number | Bit Mnemo | onic | Description |                                                                                                                                                            |   |   |   |   |  |  |

| _          | _         |      | Bit orde    | Can store a new byte to be transmitted on the I/O pin when SCTBE is set.<br>Bit ordering on the I/O pin depends on the Convention (see SCICR<br>Register). |   |   |   |   |  |  |

Reset Value = 0000 0000b

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

| Table 31. | Interrupt | Vector A | Addresses |

|-----------|-----------|----------|-----------|

|-----------|-----------|----------|-----------|

| Interrupt Source  | Vector Address |

|-------------------|----------------|

| IEO               | 0003h          |

| TF0               | 000Bh          |

| IE1 & Rxlt & Prlt | 0013h          |

| TF1               | 001Bh          |

| RI & TI           | 0023h          |

| SCI               | 0053h          |

| INT1 Interrupt Vector | <ul> <li>The INT1 interrupt is multiplexed with the three following inputs:</li> <li>INT1/OE: Standard 8051 interrupt input</li> <li>Rxd: Received data on UART</li> <li>CPRES: Insertion or removall of the main card</li> <li>The setting configurations for each input is detailed below:</li> </ul>                                                                                                                                                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT1/OE Input         | <ul> <li>This interrupt input is active under the following conditions:</li> <li>It must be enabled thanks to OEEN Bit (ISEL Register)</li> <li>It can be active on a level or falling edge: thanks to IT1 Bit (TCON Register)</li> <li>If level triggering selection is set, the active level 0 or 1 can be selected with OELEV Bit (ISEL Register)</li> <li>The Bit IE1 (TCON Register) is set by hardware when external interrupt detected. It is cleared when interrupt is processed.</li> </ul> |

| Rxd Input             | A second vector interrupt input is the reception of a character. UART Rx input can generate an interrupt if enabled with Bit RXEN (ISEL.0). The global enable bits EX1 and EA must also be set.<br>Then, the Bit RXIT (ISEL Register) is set by hardware when a low level is detected on P3.0/RXD input.                                                                                                                                                                                             |

| CPRES Input           | The third input is the detection of a level change on CPRES input (P1.2). This input can generate an interrupt if enabled with PRESEN (ISEL.1), EX1 (IE0.2) and EA (IE0.7) Bits. This detection is done according to the level selected with Bit CPLEV (ISEL.7). Then the Bit PRESIT (ISEL.5) is set by hardware when the triggering conditions are met. This Bit must be cleared by software.                                                                                                       |

# **Dual Data Pointer**

T8xC5121 contains a Dual Data Pointer accelerating data memory block moves. The Standard 80C52 Data Pointer is a 16-bit value that is used to address off-chip data RAM or peripherals. In T8xC5121, the standard 16-bit data pointer is called DPTR and located at SFR location 82H and 83H. The second Data Pointer named DPTR1 is located at the same address than the previous one. The DPTR select bit (DPS / bit0) chooses the active pointer and it is located into the AUXR1 register. It should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

The user switches between data pointers by toggling the LSB of the AUXR1. The increment (INC) is a solution for this. All DPTR-related instructions use the currently selected DPTR for any activity. Therefore only one instruction is required to switch from a source to a destination address. Using the Dual Data Pointer saves code and resources when moves of blocks need to be accomplished.

The second Data Pointer can be used to address the on-chip XRAM.

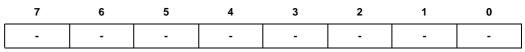

#### Table 41. DPL Register

DPL - Low Byte of DPTR1 (82h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset value = 0000 0000b

Table 42. DPH Register

DPH - High Byte of DPTR1 (83h)

Reset value =  $0000\ 0000b$

A/T8xC5121

## Table 43. AUXR1 Register

AUXR1 - Dual Pointer Selection Register (A2h)

| 7             | 6              | 5         | 4                                                                               | 3                                | 2 | 1 | 0   |  |  |  |  |

|---------------|----------------|-----------|---------------------------------------------------------------------------------|----------------------------------|---|---|-----|--|--|--|--|

| -             | -              | -         | -                                                                               | -                                | - | - | DPS |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemoni | c Descrip | Description                                                                     |                                  |   |   |     |  |  |  |  |

| 7             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 6             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 5             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 4             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 3             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 2             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 1             | -              |           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                  |   |   |     |  |  |  |  |

| 0             | DPS            |           | select DPTR                                                                     | ) as Data Poin<br>Is Data Pointe |   |   |     |  |  |  |  |

Reset value = XXXX XXX0b

# UART Timings

The following description will be included in L version:

Mode SelectionSM0 and SM1 bits in SCON register (see Table 67) are used to select a mode among<br/>the single synchronous and the three asynchronous modes according to Table 64.

| Table 64. | Serial I/O Port Mode Selection |

|-----------|--------------------------------|

|-----------|--------------------------------|

| SM0 | SM1 | Mode | Description                | Baud Rate        |

|-----|-----|------|----------------------------|------------------|

| 0   | 0   | 0    | Synchronous Shift Register | Fixed / Variable |

| 0   | 1   | 1    | 8-bit UART                 | Variable         |

| 1   | 0   | 2    | 9-bit UART                 | Fixed            |

| 1   | 1   | 3    | 9-bit UART                 | Variable         |

**Baud Rate Generator** Depending on the mode and the source selection, the baud rate can be generated from either the Timer 1 or the Internal Baud Rate Generator. The Timer 1 can be used in Modes 1 and 3 while the Internal Baud Rate Generator can be used in Modes 0, 1 and 3.

The addition of the Internal Baud Rate Generator allows freeing of the Timer 1 for other purposes in the application. It is highly recommended to use the Internal Baud Rate Generator as it allows higher and more accurate baud rates than with Timer 1.

Baud rate formulas depend on the modes selected and are given in the following mode sections.

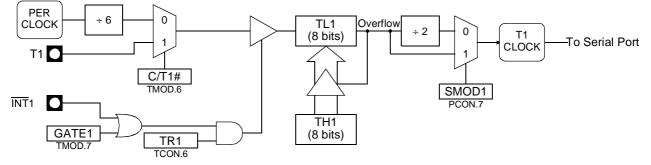

Timer 1

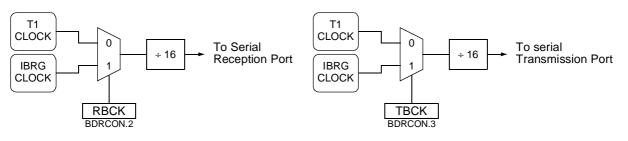

When using the Timer 1, the Baud Rate is derived from the overflow of the timer. As shown in Figure 36 the Timer 1 is used in its 8-bit auto-reload mode (detailed in Section "Timer 0/Counter Operations", page 73). SMOD1 bit in PCON register allows doubling of the generated baud rate.

Figure 36. Timer 1 Baud Rate Generator Block Diagram

Internal Baud Rate Generator When using the Internal Baud Rate Generator, the Baud Rate is derived from the overflow of the timer. As shown in Figure 37, the Internal Baud Rate Generator is an 8-bit auto-reload timer feed by the peripheral clock or by the peripheral clock divided by 6 depending on the SPD bit in BDRCON register (see Table 68). The Internal Baud Rate Generator is enabled by setting BBR bit in BDRCON register. SMOD1 bit in PCON register allows doubling of the generated baud rate.

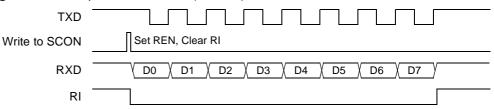

**Reception (Mode 0)** To start a reception in mode 0, write to SCON register clearing SM0, SM1 and RI bits and setting the REN bit.

As shown in Figure 40, Clock is pulsed and the LSB (D0) is sampled on the RXD pin. The D0 bit is then shifted into the shift register. After eight sampling, the MSB (D7) is shifted into the shift register, and hardware asserts RI bit to indicate a completed reception. Software can then read the received byte from SBUF register.

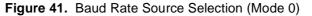

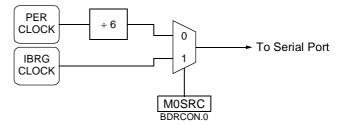

Baud Rate Selection (Mode 0) In mode 0, baud rate can be either fixed or variable.

As shown in Figure 41, the selection is done using M0SRC bit in BDRCON register. Figure 42 gives the baud rate calculation formulas for each baud rate source.

a. Fixed Formula

$Baud\_Rate = \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot (256 \text{ -BRL})}$  $BRL = 256 \frac{2^{SMOD1} \cdot F_{PER}}{6^{(1-SPD)} \cdot 32 \cdot Baud_Rate}$

b. Variable Formula

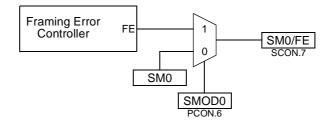

Framing Error Detection (Modes 1, 2 and 3) Framing error detection is provided for the three asynchronous modes. To enable the framing bit error detection feature, set SMOD0 bit in PCON register as shown in Figure 46.

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two devices. If a valid stop bit is not found, the software sets FE bit in SCON register.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a chip reset clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When the framing error detection feature is enabled, RI rises on stop bit instead of the last data bit as detailed in Figure 36.

Figure 46. Framing Error Block Diagram

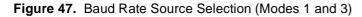

Baud Rate Selection (Modes 1<br/>and 3)In modes 1 and 3, the Baud Rate is derived either from the Timer 1 or the Internal Baud<br/>Rate Generator and allows different baud rate in reception and transmission.

As shown in Figure 47 the selection is done using RBCK and TBCK bits in BDRCON register.

Figure 48 gives the baud rate calculation formulas for each baud rate source while Table 65 details Internal Baud Rate Generator configuration for different peripheral clock frequencies and giving baud rates closer to the standard baud rates.

Figure 48. Baud Rate Formulas (Modes 1 and 3)

Baud\_Rate =  $\frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6^{(1-\text{SPD})} \cdot 32 \cdot (256 - \text{BRL})}$ Baud\_Rate =  $\frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6 \cdot 32 \cdot (256 - \text{TH1})}$ BRL =  $256 \frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6^{(1-\text{SPD})} \cdot 32 \cdot \text{Baud}_{\text{Rate}}}$ TH1 =  $256 \frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{192 \cdot \text{Baud}_{\text{Rate}}}$ a. BRG Formulab. T1 Formula

90 A/T8xC5121

|                          |                                        | F <sub>PER</sub> = 6 MHz <sup>1</sup> |                        |                                        |             | F <sub>PER</sub> = 8 MHz <sup>1</sup> |                          |                      |  |  |

|--------------------------|----------------------------------------|---------------------------------------|------------------------|----------------------------------------|-------------|---------------------------------------|--------------------------|----------------------|--|--|

| Baud Rate                | SPD                                    | SMOD1                                 | BRL                    | Error %                                | SPD         | SMOD1                                 | BRL                      | Error %              |  |  |

| 115200                   | -                                      | -                                     | -                      | -                                      | -           | -                                     | -                        | -                    |  |  |

| 57600                    | -                                      | -                                     | -                      | -                                      | 1           | 1                                     | 247                      | 3.55                 |  |  |

| 38400                    | 1                                      | 1                                     | 246                    | 2.34                                   | 1           | 1                                     | 243                      | 0.16                 |  |  |

| 19200                    | 1                                      | 1                                     | 236                    | 2.34                                   | 1           | 1                                     | 230                      | 0.16                 |  |  |

| 9600                     | 1                                      | 1                                     | 217                    | 0.16                                   | 1           | 1                                     | 204                      | 0.16                 |  |  |

| 4800                     | 1                                      | 1                                     | 178                    | 0.16                                   | 1           | 1                                     | 152                      | 0.16                 |  |  |

|                          | F <sub>PER</sub> = 12 MHz <sup>2</sup> |                                       |                        | F <sub>PER</sub> = 16 MHz <sup>2</sup> |             |                                       |                          |                      |  |  |

|                          |                                        | $\mathbf{F}_{\text{PER}} = 1$         | 12 MHZ <sup>-</sup>    |                                        |             | $F_{PER} = 1$                         | 16 MHz <sup>2</sup>      |                      |  |  |

| Baud Rate                | SPD                                    | F <sub>PER</sub> = 1<br>SMOD1         | BRL                    | Error %                                | SPD         | F <sub>PER</sub> = 1<br>SMOD1         | BRL                      | Error %              |  |  |

| Baud Rate 115200         | SPD<br>-                               |                                       |                        | Error %                                | SPD<br>1    | T                                     |                          | Error %<br>3.55      |  |  |

|                          | -                                      | SMOD1                                 | BRL                    |                                        | -           | SMOD1                                 | BRL                      |                      |  |  |

| 115200                   | -                                      | SMOD1                                 | BRL<br>-               | -                                      | 1           | SMOD1                                 | <b>BRL</b> 247           | 3.55                 |  |  |

| 115200<br>57600          | - 1                                    | <b>SMOD1</b><br>-<br>1                | BRL<br>-<br>243        | - 0.16                                 | 1           | <b>SMOD1</b> 1 1                      | BRL<br>247<br>239        | 3.55<br>2.12         |  |  |

| 115200<br>57600<br>38400 | -<br>1<br>1                            | <b>SMOD1</b><br>-<br>1<br>1           | BRL<br>-<br>243<br>236 | -<br>0.16<br>2.34                      | 1<br>1<br>1 | <b>SMOD1</b> 1 1 1 1                  | BRL<br>247<br>239<br>230 | 3.55<br>2.12<br>0.16 |  |  |

Table 65. Internal Baud Rate Generator Value

Notes: 1. These frequencies are achieved in X1 mode,  $F_{PER} = F_{OSC} \div 2$ .

2. These frequencies are achieved in X2 mode,  $F_{PER} = F_{OSC}$ .

**Baud Rate Selection (Mode 2)** In mode 2, the baud rate can only be programmed to two fixed values: 1/16 or 1/32 of the peripheral clock frequency.

As shown in Figure 49, the selection is done using SMOD1 bit in PCON register.

Figure 50 gives the baud rate calculation formula depending on the selection.

Baud\_Rate =  $\frac{2 \text{SMOD1} \text{ FPER}}{32}$

**Table 69.** SIOCON RegisterSerial Input Output Configuration RegisterRegister (91h)

| 7             | 6                  | 5                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                                                                                              | 3              | 2               | 1         | 0     |  |  |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------|-------|--|--|--|--|

| PMSOEN1       | PMSOEN             |                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                              | CPRES<br>RES   | EVAUTO          | VEXT0     | VEXT1 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                    |                |                 |           |       |  |  |  |  |

| 7 - 6         | PMOSEN1<br>PMOSEN0 | Output Enable function on Txd/P3.1 and T0/P3.4:         PMSOEN1       PMSOEN0         0       0       PMOS is always off (reset value)         0       1       PMOS is always driven according to P3.1 or P3.4 value         1       0       PMOS is driven only when OE is high         1       1       PMOS is driven only when OE is low |                                                                                                                                                                                                                                                                |                |                 |           |       |  |  |  |  |

| 5 - 4         | -                  | Reserved<br>The value read                                                                                                                                                                                                                                                                                                                  | from this bit                                                                                                                                                                                                                                                  | is indetermina | ite. Do not set | this bit. |       |  |  |  |  |

| 3             | CPRES<br>RES       | Card Presenc<br>0 Internal pull-<br>1 Internal pull-                                                                                                                                                                                                                                                                                        | up is connect                                                                                                                                                                                                                                                  | ed             |                 |           |       |  |  |  |  |

| 2             | EVAUTO             | Set to enable t                                                                                                                                                                                                                                                                                                                             | EVCC Auto setup<br>Set to enable the Automatic mode of EV <sub>CC</sub> regulator<br>Clear to disable the Automatic mode of EV <sub>CC</sub> regulator                                                                                                         |                |                 |           |       |  |  |  |  |

| 1 - 0         | VEXT0<br>VEXT1     | •                                                                                                                                                                                                                                                                                                                                           | Clear to disable the Automatic mode of $EV_{CC}$ regulator         EVCC voltage configuration:         VEXT0       VEXT1         0       0       Power-down, $EV_{CC}$ is external (reset value)         0       1 $EV_{CC} = 1.8V$ 1       0 $EV_{CC} = 2.3V$ |                |                 |           |       |  |  |  |  |

Reset Value = 00XX 0000b

# **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Ambiant Temperature Under Bias25°C to 85°C      |

|-------------------------------------------------|

| Storage Temperature65°C to + 150°C              |

| Voltage on $V_{CC}$ to $V_{SS}$ -0.5V to + 6.0V |

| Voltage on Any Pin to $V_{\text{SS}}$           |

Note: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

## **DC Parameters**

$T_{A}$  = -40°C to +85°C;  $V_{SS}$  = 0 V;  $v_{cc}$  = 2.85V to 5.4V; F = 7.36 to 16 MHz

| Symbol                               | Parameter                               | Min                                     | Тур   | Max                       | Unit | Test Conditions                                |

|--------------------------------------|-----------------------------------------|-----------------------------------------|-------|---------------------------|------|------------------------------------------------|

| V <sub>IL</sub>                      | Input Low Voltage                       | -0.5                                    |       | 0.2 V <sub>CC</sub> - 0.1 | V    |                                                |

| V <sub>IH</sub>                      | Input High Voltage<br>except XTAL1, RST | .2 V <sub>CC</sub> + .9                 |       | V <sub>CC</sub> + 0.5     | V    |                                                |

| V <sub>IH1</sub>                     | Input High Voltage,<br>XTAL1, RST       | $0.7 V_{CC}$                            |       | V <sub>CC</sub> + 0.5     | V    |                                                |

| V <sub>OL</sub>                      | Output Low Voltage,<br>Port 0 and 2     |                                         |       | 0.45                      | V    | I <sub>OL =</sub> 1.6 mA                       |

| V <sub>OH</sub>                      | Output High Voltage,<br>Port 0 and 2    | 0.9 x V <sub>CC</sub>                   |       |                           | V    | I <sub>OH</sub> = -40 μA                       |

| DI <sub>CC</sub>                     | Digital Supply Output<br>Current        |                                         | 6     | 10                        | mA   | C <sub>L</sub> = 100 nF                        |

| DV <sub>CC</sub>                     | Digital Supply<br>Voltage               | 2.5                                     | 2 .9  | 3.0                       | V    | C <sub>L</sub> = 100 nF<br>DIcc=10mA           |

| lcc                                  | Normal Power Down<br>mode               |                                         | 80    | 100                       | μA   | 25°C                                           |

| lcc                                  | Pulsed Power Down mode                  |                                         | 20    | 30                        | μA   | 50°C Vcc=3V                                    |

| Іссор                                | Power Supply current                    | $I_{ccop} = 0.25$<br>$I_{ccIDLE} = 0.0$ |       |                           |      | $V_{CC} = 5.4V$ and<br>Bootloader<br>execution |

| V <sub>PFDP</sub>                    | Power-fail high level threshold         |                                         | 2 .55 |                           | V    |                                                |

| V <sub>PFDM</sub>                    | Power-fail low level threshold          |                                         | 2 .45 |                           | V    |                                                |

| t <sub>G</sub>                       | Power Fail glitch time                  |                                         |       | 50                        | ns   |                                                |

| t <sub>rise,</sub> t <sub>fall</sub> | V <sub>DD</sub> rise and fall time      | 1 µs                                    |       | 600                       | sec. |                                                |

### Table 72. Core DC Parameters (XTAL, RST, P0, P2, ALE, PSEN, EA)

98 A/T8xC5121

| Symbol            | Parameter          | Min                    | Тур              | Max             | Unit  | Test Conditions                     |

|-------------------|--------------------|------------------------|------------------|-----------------|-------|-------------------------------------|

|                   |                    | -0.5                   |                  | 0.4             | V     | $EV_{CC} = 1.8V$                    |

|                   |                    | -0.5                   |                  | 0.5             | V     | $EV_{CC} = 2.3V$                    |

| VIL               | Input Low Voltage  | -0.5                   |                  | 0.5             | V     | $EV_{CC} = 2.8V$                    |

|                   |                    |                        |                  |                 |       | External EVcc                       |

|                   |                    |                        |                  |                 |       | Automatic EVcc                      |

|                   |                    | 1.4                    |                  | 2.3             | V     | EV <sub>CC</sub> = 1.8V             |

|                   |                    | 1.4                    |                  | 2.8             | v     | $EV_{CC} = 2.3V$                    |

| V <sub>IH</sub>   | Input High Voltage | 2.0                    |                  | 3.3             | v     | $EV_{CC} = 2.8V$                    |

| ЧН                | input ngri voltage | 0.7 x EV <sub>CC</sub> | EV <sub>CC</sub> | $EV_{CC}$ +     | v     | External EV <sub>CC</sub>           |

|                   |                    |                        | -•00             | 0.5             | •     | Automatic EVcc                      |

|                   |                    |                        |                  |                 |       |                                     |

| V <sub>OL</sub>   | Output Low         |                        |                  | 0.4             | V     | I <sub>OL</sub> = 1.2 mA            |

| - OL              | Voltage            |                        |                  |                 | -     | ·0L ···=····                        |

|                   |                    | 1.6                    |                  | 1.8             | V     | $EV_{CC} = 1.8V I_{OH} = 1 \ \mu A$ |

| V <sub>OH</sub>   | Output High        | 1.8                    |                  | 2.3             | V     | $EV_{CC} = 2.3V$                    |

| V OH              | Voltage            | 2.2                    |                  | 2.7             | V     | $EV_{CC} = 2.8V I_{OH} = 10\mu A$   |

|                   |                    | $0.8 \times EV_{CC}$   |                  | $EV_{CC}$       | V     | External EV <sub>CC</sub>           |

| Elcc              | Extra Supply       |                        |                  | +3              | mA    | C <sub>L</sub> = 100 nF             |

| LICC              | Current            |                        |                  | 10              | 110.4 |                                     |

|                   |                    | 1.6                    | 1.7              | 1.8             | V     | C <sub>L</sub> = 100 nF, 1.8V       |

|                   | Extra Supply       | 2.1                    | 2.2              | 2.3             | V     | C <sub>L</sub> = 100 nF, 2.3V       |

| $\rm EV_{\rm CC}$ | Voltage            | 2.6                    | 2.7              | 2.8             | V     | C <sub>L</sub> = 100 nF, 2.8V       |

|                   |                    | 1.6                    |                  | V <sub>CC</sub> | V     | External EV <sub>CC</sub>           |

|                   |                    |                        |                  |                 |       | Automatic EVcc                      |

| Ts                | Sampling time      |                        |                  |                 |       | Automatic EVcc                      |

| Table 73. Serial Interface DC parameter | rs (P3.0, P3.1, P3.3 and P3.4) |

|-----------------------------------------|--------------------------------|

|-----------------------------------------|--------------------------------|

Table 74. LED outputs DC Parameters (P3.6 and P3.7)

| Symbol          | Parameter                                         | Min         | Тур          | Мах          | Unit           | Test Conditions                                                                                                                                   |

|-----------------|---------------------------------------------------|-------------|--------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>OL</sub> | Output Low<br>Current, P3.6 and<br>P3.7 LED modes | 1<br>2<br>5 | 2<br>4<br>10 | 4<br>8<br>20 | mA<br>mA<br>mA | 2 mA configuration<br>4 mA configuration<br>10 mA configuration<br>$(T_A = -20^{\circ}C \text{ to } +50^{\circ}C, V_{CC} - V_{OL} = 2V \pm 20\%)$ |

| Symbol                        | Parameter            | Min                                              | Тур | Мах                                                  | Unit | Test Conditions                                    |

|-------------------------------|----------------------|--------------------------------------------------|-----|------------------------------------------------------|------|----------------------------------------------------|

| V <sub>OL</sub>               | Output Low Voltage   | 0(1)<br>0(1)                                     |     | 0.12 x<br>CV <sub>CC</sub><br>0.4                    | V    | I <sub>OL</sub> = 20 μA<br>I <sub>OL</sub> = 50 μA |

| I <sub>OL</sub>               | Output Low Current   |                                                  |     | 15                                                   | mA   |                                                    |

| V <sub>OH</sub>               | Output High Voltage  | CV <sub>CC</sub> - 0.5<br>0.8 x CV <sub>CC</sub> |     | CV <sub>CC</sub><br>CV <sub>CC</sub> (1)             | V    | I <sub>OH</sub> = 50 μA<br>I <sub>OH</sub> = 20 μA |

| I <sub>OH</sub>               | Output High Current  |                                                  |     | 15                                                   | mA   |                                                    |

| t <sub>R</sub> t <sub>F</sub> | Rise and Fall delays |                                                  |     | 0.8                                                  | μs   | C <sub>IN</sub> = 30 pF                            |

|                               | Voltage stability    | -0.25<br>CV <sub>CC</sub> -0.5                   |     | 0.4 x CV <sub>CC</sub><br>CV <sub>CC</sub> +<br>0.25 |      | Low level<br>High level                            |

Table 82. Smart Card RST, CC4, CC8, DC Parameters (Port P1.5, P1.3, P1.1)

Note: 1. The voltage on RST should remain between -0.3V and  $CV_{cc}$  + 0.3V during dynamic operation.

Table 83. Alternate Card RST DC Parameters (Port P3.7) : 5V tolerant

| Symbol                        | Parameter            | Min                                              | Тур | Max                                      | Unit | Test Conditions                                                 |

|-------------------------------|----------------------|--------------------------------------------------|-----|------------------------------------------|------|-----------------------------------------------------------------|

| V <sub>OL</sub>               | Output Low Voltage   | 0 (1)                                            |     | $0.2 \text{ x DV}_{CC}$                  | V    | I <sub>OL</sub> = 200 μA                                        |

| V <sub>OH</sub>               | Output High Voltage  | 0.8 x DV <sub>CC</sub><br>0.8 x DV <sub>CC</sub> |     | DV <sub>CC</sub> (1)<br>DV <sub>CC</sub> | V    | I <sub>OH</sub> = 20 μA (1.8V)<br>I <sub>OH</sub> = 200 μA (3V) |

| t <sub>R</sub> t <sub>F</sub> | Rise and Fall delays |                                                  |     | 400                                      | μs   | C <sub>IN</sub> = 30 pF                                         |

Note: 1. The voltage on RST should remain between -0.3V and  $DV_{cc}$  + 0.3V during dynamic operation.

Table 84. Card Presence DC Parameters (P1.2)

|   | Symbol           | Parameter                             | Min | Тур | Max | Unit | Test Conditions                                                  |

|---|------------------|---------------------------------------|-----|-----|-----|------|------------------------------------------------------------------|

| I | I <sub>OL1</sub> | CPRES weak pull-<br>up output current | 3   | 10  | 25  | μA   | P1.2 = 1, short to V <sub>SS</sub><br>(internal pull-up enabled) |

- 6. Distance between Device pads and Smart Card connector must be less than 4 centimeters.

- 7. C6,C7 should be as close as possible to the Smart Card connector to reduce noise and interferences.

# A/T8xC5121

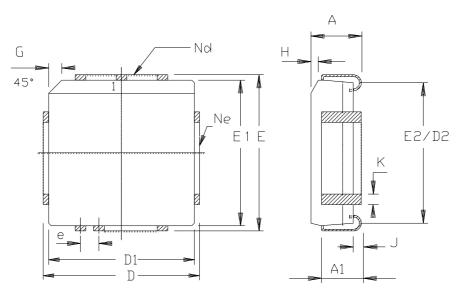

# PLCC52

|    | М      | M     | INCH  |       |  |

|----|--------|-------|-------|-------|--|

| A  | 4.20   | 4.57  | .165  | . 180 |  |

| A1 | 2, 29  | 3.30  | . 090 | . 130 |  |

| D  | 19.94  | 20.19 | . 785 | . 795 |  |

| D1 | 19.05  | 19.25 | . 750 | . 758 |  |

| D2 | 17.53  | 18.54 | . 690 | . 730 |  |

| E  | 19.94  | 20.19 | . 785 | . 795 |  |

| E1 | 19.05  | 19.25 | . 750 | . 758 |  |

| E5 | 17.53  | 18.54 | . 690 | . 730 |  |

| e  | 1.27   | BSC   | . 050 | BSC   |  |

| G  | 1.07   | 1.22  | .042  | . 048 |  |

| н  | 1.07   | 1.42  | . 042 | . 056 |  |

| J  | 0.51   | -     | . 020 | -     |  |

| К  | 0.33   | 0.53  | . 013 | . 021 |  |

| Nd | 1      | 3     | 13    |       |  |

| Ne | 1      | 3     | 13    |       |  |

| Р  | KG STD | 00    |       |       |  |