#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                    |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | SmartCard, UART/USART                                                    |

| Peripherals                | LED, POR, WDT                                                            |

| Number of I/O              | 14                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | Code RAM                                                                 |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 5.4V                                                             |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 52-LCC (J-Lead)                                                          |

| Supplier Device Package    | 52-PLCC (19.15x19.15)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t85c5121-s3sil |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## A/T8xC5121

## Signals

All the T8xC5121 signals are detailed in Table 1.

The port structure is described in Section "Port Structure Description".

#### Table 1. Ports Description

|      | Ports Des      | •         | Internal<br>Power |      |      |                                                                                                                                         |

|------|----------------|-----------|-------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Port | Signal<br>Name | Alternate | Supply            | ESD  | Туре | Description                                                                                                                             |

| P1.0 | CIO            |           | cv <sub>cc</sub>  | 4 kV | I/O  | Smart card interface function<br>Card I/O.                                                                                              |

|      |                |           |                   |      | I/O  | Input/Output function<br>P1.0 is a bi-directional I/O port .                                                                            |

|      |                |           |                   |      | I    | Reset configuration<br>Input .                                                                                                          |

| P1.1 | CC8            |           | CV <sub>CC</sub>  | 4 kV | 0    | Smart card interface function<br>Card contact 8                                                                                         |

|      |                |           |                   |      | 0    | Output function<br>P1.1 is a Push-pull port.                                                                                            |

|      |                |           |                   |      | I    | Reset configuration<br>Input                                                                                                            |

| P1.2 | CPRES          |           | V <sub>cc</sub>   | 4 kV | I    | Smart card interface function<br>Card presence                                                                                          |

|      |                |           |                   |      | I/O  | Input/Output function<br>P1.2 is a bi-directional I/O port with internal pull-ups- (External Pull-up<br>configuration can be selected). |

|      |                |           |                   |      | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                       |

| P1.3 | CC4            |           | cv <sub>cc</sub>  | 4 kV | 0    | Smart card interface function<br>Card contact 4                                                                                         |

|      |                |           |                   |      | Ο    | Output function<br>P1.3 is a Push-pull port.                                                                                            |

|      |                |           |                   |      | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                       |

| P1.4 | CCLK           |           | cv <sub>cc</sub>  | 4 kV | 0    | Smart card interface function<br>Card clock                                                                                             |

|      |                |           |                   |      | I/O  | Input/Output function<br>P1.4 is a a Push-pull port.                                                                                    |

|      |                |           |                   |      | ο    | Reset configuration<br>Output at low level                                                                                              |

| P1.5 | CRST           |           | CV <sub>CC</sub>  | 4 kV | 0    | Smart card interface function<br>Card reset                                                                                             |

|      |                |           |                   |      | I/O  | Input/Output function<br>P1.5 is a a Push-pull port.                                                                                    |

|      |                |           |                   |      | 0    | Reset configuration<br>Output at low level                                                                                              |

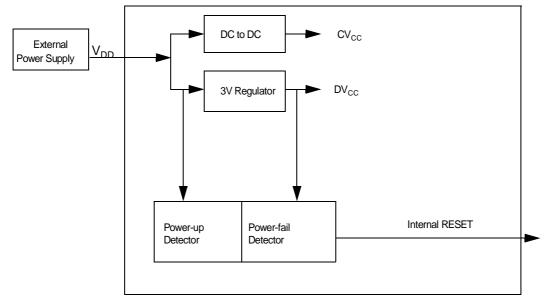

## PowerMonitor

The PowerMonitor function supervises the evolution of the voltages feeding the microcontroller, and if needed, suspends its activity when the detected value is out of specification.

It is guaranteed to start up properly when T8xC5121 is powered up and prevents code execution errors when the power supply becomes lower than the functional threshold.

This section describes the functions of the PowerMonitor.

**Description** In order to start up and to properly maintain the microcontroller operation, V<sub>DD</sub> has to be stabilized in the V<sub>DD</sub> operating range and the oscillator has to be stabilised with a nominal amplitude compatible with logic threshold.

This control is carried out during three phases which are the power-up, normal operation and stop. It complies with the following requirements:

- It guarantees an operational Reset when the microcontroller is powered

- and a protection if the power supply goes out from the functional range of the microcontroller.

Figure 8. PowerMonitor Block Diagram

### **PowerMonitor Diagram**

The target of the PowerMonitor is to survey the power supply in order to detect any voltage drops which are not in the target specification. This PowerMonitor block checks two kind of situations that occur:

- During the power-up condition, when V<sub>DD</sub> is reaching the product specification

- During a steady-state condition, when V<sub>DD</sub> is stable but disturbed by any undesirable voltage drops.

Figure 9 shows some configurations that can be met by the PowerMonitor.

## Table 5. IE0 Register

IE0

Interrupt Enable Register (A8h)

| 7             | 6               | 5                                         | 4                                                                                                                                                                                                                         | 3                                                   | 2             | 1               | 0   |

|---------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------|-----------------|-----|

| EA            | -               | -                                         | ES                                                                                                                                                                                                                        | ET1                                                 | EX1           | ET0             | EX0 |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                                | on                                                                                                                                                                                                                        |                                                     |               |                 |     |

| 7             | EA              | Clear to di<br>Set to ena<br>If EA = 1, e | Enable All interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA = 1, each interrupt source is individually enabled or disabled by setting or<br>clearing its interrupt enable bit. |                                                     |               |                 |     |

| 6             | -               | Reserved<br>The value                     |                                                                                                                                                                                                                           | s bit is indeter                                    | minate. Do no | t set this bit. |     |

| 5             | -               |                                           | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                    |                                                     |               |                 |     |

| 4             | ES              | Clear to di                               | <b>t Enable bit</b><br>sable serial p<br>ble serial por                                                                                                                                                                   | •                                                   |               |                 |     |

| 3             | ET1             | Clear to di                               | sable Timer 1                                                                                                                                                                                                             | rupt Enable to<br>overflow interru                  | rrupt.        |                 |     |

| 2             | EX1             | Clear to di                               | External interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                          |                                                     |               |                 |     |

| 1             | ET0             | Clear to di                               | sable Timer (                                                                                                                                                                                                             | rupt Enable b<br>) overflow inte<br>verflow interru | rrupt.        |                 |     |

| 0             | EX0             | Clear to di                               | nterrupt 0 Er<br>sable externa<br>ble external i                                                                                                                                                                          | al interrupt 0.                                     |               |                 |     |

Reset Value = 0XX0 0000b

## Smart Card Interface Block (SCIB)

Introduction The SCIB provides all signals to directly interface a smart card. Compliance with the ISO7816, EMV'2000, GSM and WHQL standards has been certified. Both synchronous (e.g. memory card) and asynchronous smart cards (e.g. microprocessor card) are supported. The component supplies the different voltages requested by the smart card. The power-off sequence is directly managed by the SCIB. The card presence switch of the smart card connector is used to detect card insertion or card removal. In case of card removal, the SCIB de-activates the smart card using the de-activation sequence. An interrupt can be generated when a card is inserted or removed. Any malfunction is reported to the microcontroller (interrupt + control register). The different operating modes are configured by internal registers. Main Features Support of ISO/IEC7816 Character mode 1 transmit buffer + 1 receive buffer 11 bits ETU counter . 9 bits guard time counter

- 24 bits waiting time counter

- Auto-character repetition on error signal detection in transmit mode

- Auto-error signal generation on parity error detection in receive mode

- Power-on and power-off sequence generation

- Manual mode to directly drive the card I/O

## Table 16. SCCON Register

SCCON (S:ACh, SCRS = 0) Smart Card Contacts Register

| 7          | 6                   | 5                                      | 4                                                                                                                                                                                                                                                                    | 3                | 2               | 1                | 0               |

|------------|---------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|-----------------|

| CLK        | -                   | CARDC8                                 | CARDC4                                                                                                                                                                                                                                                               | CARDIO           | CARDCLK         | CARDRST          | CARDVCC         |

| Bit Number | Bit Mnemon          | ic Descript                            | ion                                                                                                                                                                                                                                                                  |                  |                 |                  |                 |

| 7          | CLK                 | Clear this<br>Set this b<br>Note: inte | Card Clock Selection<br>Clear this bit to use the CardClk bit (CARDCLK) to drive Card CLK<br>Set this bit to use XTAL signal to drive the Card CLK pin.<br>Note: internal synchronization avoids any glitch on the CLK pin w<br>switching this bit.                  |                  |                 |                  |                 |

| 6          | -                   | <b>Reserve</b><br>The value            |                                                                                                                                                                                                                                                                      | is bit is indete | rminate. Do no  | ot change this   | bit or write 0. |

| 5          | CARDC8              |                                        | <b>Card C8</b><br>Clear this bit to drive a low level on the Card C8 pin.<br>Set this bit to set a high level on the Card C8 pin.                                                                                                                                    |                  |                 |                  |                 |

| 4          | CARDC4              |                                        | <b>Card C4</b><br>Clear this bit to drive a low level on the Card C4 pin.<br>Set this bit to set a high level on the Card C4 pin.                                                                                                                                    |                  |                 |                  |                 |

| 3          | CARDIO              | driven to<br>Then this                 | <b>Card I/O</b><br>When the UART bit is cleared in SCICR Register, the value of this bit is driven to the Card I/O pin.<br>Then this pin can be used as a pseudo bi-directional I/O when this bit is set To be used as an input, this bit must contain a 1.          |                  |                 |                  |                 |

| 2          | CARDCLK             |                                        |                                                                                                                                                                                                                                                                      | eared in SCCC    | DN Register, th | ne value of this | s bit is driven |

| 1          | CARDRST             | Clear this<br>Set this b               | <b>Card RST</b><br>Clear this bit to drive a low level on the Card RST pin.<br>Set this bit to set a high level on the Card RST pin.<br>Read is not allowed if VCARDOK=0                                                                                             |                  |                 |                  |                 |

| 0          | CARDV <sub>CC</sub> | Clear this<br>bits of SC<br>Set this b | Card VCC Control<br>Clear this bit to desactivate the Card interface and set its power-off. The<br>bits of SCC register have no effect while this bit is cleared.<br>Set this bit to power-on the Card interface. The activation sequence sh<br>handled by software. |                  |                 |                  |                 |

Reset Value = 0X00 0000b

## Table 19. SCIER Register

SCIER (S:AEh, SCRS = 1) Smart Card UART Interrupt Enable Register

| 7          | 6               | 5                    | 4                                                                                                                                                                                                               | 3                 | 2              | 1               | 0     |

|------------|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-----------------|-------|

| ESCTBI     | -               | ClccER               | ECVccER                                                                                                                                                                                                         | ESCWTI            | ESCTI          | ESCRI           | ESCPI |

| Bit Number | Bit<br>Mnemonic | Descript             | ion                                                                                                                                                                                                             |                   |                |                 |       |

| 7          | ESCTBI          | Clear this           | Smart Card UART Transmit Buffer Empty Interrupt Enable<br>Clear this bit to disable the Smart Card UART Transmit Buffer Empty inter<br>Set this bit to enable the Smart Card UART Transmit Buffer Empty interru |                   |                |                 |       |

| 6          | -               | Reserve<br>The value | d<br>e read from this                                                                                                                                                                                           | s bit is indeterr | minate. Do not | t change this t | pit . |

| 5          | ClccER          | Clear this           | <b>Card Current Error Interrupt Enable</b><br>Clear this bit to disable the Card Current Error interrupt.<br>Set this bit to enable the Card Current Error interrupt.                                           |                   |                |                 |       |

| 4          | ECVccER         | Clear this           | <b>Card Voltage Error Interrupt Enable</b><br>Clear this bit to disable the Card Voltage Error interrupt.<br>Set this bit to enable the Card Voltage Error interrupt.                                           |                   |                |                 |       |

| 3          | ESCWTI          | Clear this           | ard Wait Timed<br>bit to disable to<br>bit to enable the                                                                                                                                                        | the Smart Car     | d Wait timeou  |                 |       |

| 2          | ESCTI           | Clear this           | Smart Card Transmit Interrupt Enable<br>Clear this bit to disable the Smart Card UART Transmit interrupt.<br>Set this bit to enable the Smart Card UART Transmit interrupt.                                     |                   |                |                 |       |

| 1          | ESCRI           | Clear this           | Smart Card Receive Interrupt Enable<br>Clear this bit to disable the Smart Card UART Receive interrupt.<br>Set this bit to enable the Smart Card UART Receive interrupt.                                        |                   |                |                 |       |

| 0          | ESCPI           | Clear this           | Smart Card Parity Error Interrupt Enable<br>Clear this bit to disable the Smart Card UART Parity Error interrupt.<br>Set this bit to enable the Smart Card UART Parity Error interrupt.                         |                   |                |                 |       |

Reset Value = 0X00 0000b

#### Table 22. SCRBUF Register

SCRBUF (S:AA read-only, SCRS = 1) Smart Card Receive Buffer Register

| 7             | 6               | 5           | 4 | 3                               | 2 | 1 | 0          |

|---------------|-----------------|-------------|---|---------------------------------|---|---|------------|

| _             | -               | -           | - | -                               | - | - | _          |

| Bit<br>Number | Bit<br>Mnemonic | Description |   |                                 |   |   |            |

| -             | _               |             | • | ed from the l/<br>depends on th | • |   | Register). |

Reset Value = 0000 0000b

#### Table 23. SCETU1 Register

SCETU1 (S:ADh, SCRS = 1) Smart Card ETU Register 1

| 7             | 6               | 5                         | 4                                | 3                                                | 2                | 1              | 0         |

|---------------|-----------------|---------------------------|----------------------------------|--------------------------------------------------|------------------|----------------|-----------|

| COMP          | -               | -                         | -                                | -                                                | ETU10            | ETU9           | ETU8      |

| Bit<br>Number | Bit<br>Mnemonic | Description               |                                  |                                                  |                  |                |           |

| 7             | COMP            | CLK period ra<br>period). | when no time<br>atio is close to | e compensatio<br>o an integer w<br>reduce the ET | ith an error les | ss than 1/4 of | Card CLK  |

| 6-3           | -               | Reserved<br>The value rea | ad from these                    | bits is indeter                                  | minate. Do no    | ot change thes | se bits . |

| 2-0           | ETU[10:8]       | ETU MSB<br>Used togethe   | er with the ET                   | U LSB (see S                                     | CETU0 Regis      | ter).          |           |

Reset Value = 0XXX X001b

## **Dual Data Pointer**

T8xC5121 contains a Dual Data Pointer accelerating data memory block moves. The Standard 80C52 Data Pointer is a 16-bit value that is used to address off-chip data RAM or peripherals. In T8xC5121, the standard 16-bit data pointer is called DPTR and located at SFR location 82H and 83H. The second Data Pointer named DPTR1 is located at the same address than the previous one. The DPTR select bit (DPS / bit0) chooses the active pointer and it is located into the AUXR1 register. It should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

The user switches between data pointers by toggling the LSB of the AUXR1. The increment (INC) is a solution for this. All DPTR-related instructions use the currently selected DPTR for any activity. Therefore only one instruction is required to switch from a source to a destination address. Using the Dual Data Pointer saves code and resources when moves of blocks need to be accomplished.

The second Data Pointer can be used to address the on-chip XRAM.

#### Table 41. DPL Register

DPL - Low Byte of DPTR1 (82h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset value = 0000 0000b

Table 42. DPH Register

DPH - High Byte of DPTR1 (83h)

Reset value =  $0000\ 0000b$

A/T8xC5121

## Table 43. AUXR1 Register

AUXR1 - Dual Pointer Selection Register (A2h)

| 7             | 6              | 5                          | 4           | 3                                | 2              | 1                 | 0   |

|---------------|----------------|----------------------------|-------------|----------------------------------|----------------|-------------------|-----|

| -             | -              | -                          | -           | -                                | -              | -                 | DPS |

| Bit<br>Number | Bit<br>Mnemoni | c Descrip                  | tion        |                                  |                |                   |     |

| 7             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 6             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 5             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 4             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 3             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 2             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 1             | -              | <b>Reserve</b><br>The valu |             | nis bit is indete                | erminate. Do r | not set this bit. |     |

| 0             | DPS            |                            | select DPTR | ) as Data Poin<br>Is Data Pointe |                |                   |     |

Reset value = XXXX XXX0b

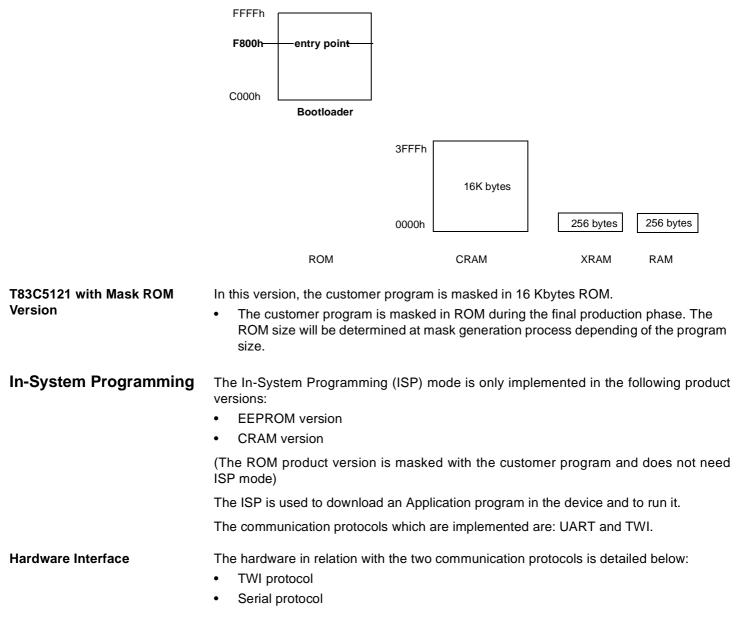

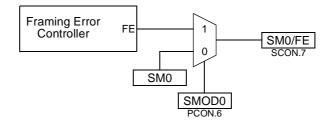

## **Memory Management**

Program Memory All the T8xC5121 versions implement 16 Kbytes of ROM memory, 256 Bytes RAM and 256 Bytes XRAM.

The hardware configuration byte and the split of internal memory spaces depends on the product and is detailed below.

**ROM Configuration Byte**

**Table 44.** ROM Configuration Byte Hardware Register

| 7             | 6               | 5           | 4                                                                                                   | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|-----------------------------------------------------------------------------------------------------|---|---|---|---|

| -             | BLJRB           | -           | -                                                                                                   | - | - | - |   |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio  | 'n                                                                                                  |   |   |   |   |

| 7             |                 | Reserved    |                                                                                                     |   |   |   |   |

| 6             | BLJRB           | Set to conf | Bootloader Jump RAM Bit<br>Set to configure User Code in ROM<br>Clear to configure Bootlader in ROM |   |   |   |   |

| 5-0           |                 | Reserved    |                                                                                                     |   |   |   |   |

The BLJRB depends of the product version:

- 1: ROM mask version

- 0: EEPROM/CRAM versions

This bit defines if, after reset, either the Customer ROM program or the Bootloader program is executed (for In System programming).

**Program ROM Lock Bits** The program Lock system protects the on-chip program against software piracy.

The T8xC5121 products are delivered with the highest protection level.

Table 45.

T8xC5121 Products Protection Level

| Pro               | Program Lock Bits |     | Protection Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>Level | LB1               | LB2 |                                                                                                                                                                                                                                                                                                                                                                                       |

| 3                 | Ρ                 | Ρ   | SSOP24 version:         Read function is disabled.But checksum control is still enabled         PLCC52 version:         MOVC instruction executed from external program memory are disabled         from fetching code bytes from internal memory,         EA is sampled and latched on reset.         But checksum control is still enabled.         External execution is possible. |

P = Programmed

| Timer 1                                    | Timer 1 is identical to Timer 0 except for Mode 3 which is a hold-count mode. The fol-<br>lowing comments help to understand the differences:                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | • Timer 1 functions as either a Timer 0 or an event Counter in the three operating modes. Figure 28 through Figure 30 show the logical configuration for modes 0, 1, and 2. Mode 3 of Timer 1 is a hold-count mode.                                                                                                                                                                                                                                                                 |

|                                            | <ul> <li>Timer 1 is controlled by the four high-order bits of the TMOD register (see Figure 56) and bits 2, 3, 6 and 7 of the TCON register (see Figure 55). The TMOD register selects the method of Timer 0 gating (GATE1), Timer 0 or Counter operation (C/T1#) and the operating mode (M11 and M01). The TCON register provides Timer 1 control functions: overflow flag (TF1), run control bit (TR1), interrupt flag (IE1) and the interrupt type control bit (IT1).</li> </ul> |

|                                            | • Timer 1 can serve as the Baud Rate Generator for the Serial Port. Mode 2 is best suited for this purpose.                                                                                                                                                                                                                                                                                                                                                                         |

|                                            | <ul> <li>For normal Timer 0 operation (GATE1 = 0), setting TR1 allows TL1 to be<br/>incremented by the selected input. Setting GATE1 and TR1 allows external pin INT1<br/>to control Timer 0 operation.</li> </ul>                                                                                                                                                                                                                                                                  |

|                                            | • Timer 1 overflow (count rolls over from all 1s to all 0s) sets the TF1 flag and generates an interrupt request.                                                                                                                                                                                                                                                                                                                                                                   |

|                                            | • When Timer 0 is in mode 3, it uses Timer 1's overflow flag (TF1) and run control bit (TR1). For this situation, use Timer 1 only for applications that do not require an interrupt (such as a Baud Rate Generator for the Serial Port) and switch Timer 1 in and out of mode 3 to turn it off and on.                                                                                                                                                                             |

|                                            | <ul> <li>It is important to stop the Timer 0/Counter before changing modes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              |

| Mode 0 (13-bit Timer 0)                    | Mode 0 configures Timer 1 as a 13-bit Timer 0, which is set up as an 8-bit Timer 0 (TH1 register) with a modulo-32 prescaler implemented with the lower 5 bits of the TL1 register (see Figure 28). The upper 3 bits of TL1 register are ignored. Prescaler overflow increments the TH1 register.                                                                                                                                                                                   |

| Mode 1 (16-bit Timer 0)                    | Mode 1 configures Timer 1 as a 16-bit Timer 0 with TH1 and TL1 registers connected in cascade (see Figure 29). The selected input increments the TL1 register.                                                                                                                                                                                                                                                                                                                      |

| Mode 2 (8-bit Timer 0 with<br>Auto-Reload) | Mode 2 configures Timer 1 as an 8-bit Timer 0 (TL1 register) with automatic reload from the TH1 register on overflow (see Figure 30). TL1 overflow sets the TF1 flag in the TCON register and reloads TL1 with the contents of TH1, which is preset by the software. The reload leaves TH1 unchanged.                                                                                                                                                                               |

| Mode 3 (Halt)                              | Placing Timer 1 in mode 3 causes it to halt and hold its count. This can be used to halt Timer 1 when the TR1 run control bit is not available i.e., when Timer 0 is in mode 3.                                                                                                                                                                                                                                                                                                     |

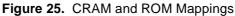

## Serial I/O Port

The serial I/O port is entirely compatible with the serial I/O port in the 80C52.

It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates.

Serial I/O port includes the following enhancements:

- Framing error detection and Automatic Address Recognition

- Internal Baud Rate Generator

#### Figure 32. Serial I/O UART Port Block Diagram

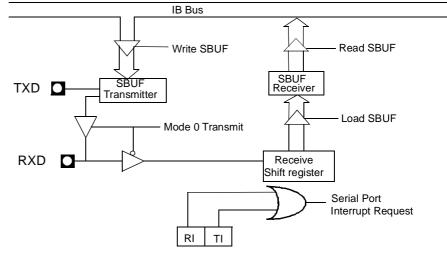

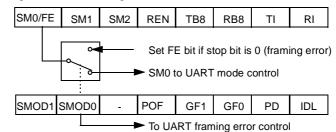

## **Framing Error Detection**

Framing bit error detection is provided for the three asynchronous modes. To enable the framing bit error detection feature, set SMOD0 bit in PCON register.

#### Figure 33. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 34 and Figure 35).

|                   | To address a device by its individual address, the SADEN mask byte must be 1111<br>1111b.<br>For example:<br>SADDR0101 0110b<br>SADEN1111 1100b<br>Given0101 01XXb                                                                                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | The following is an example of how to use given addresses to address different slaves:<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                                                                                                                         |

|                   | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                                                                                                                                                                                   |

|                   | Slave C:SADDR1111 0011b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                                                                                                                                                                                   |

|                   | The SADEN byte is selected so that each slave may be addressed separately.<br>For slave A, bit 0 (the LSB) is a don't care bit; for slaves B and C, bit 0 is a 1. To commu-<br>nicate with slave A only, the master must send an address where bit 0 is clear (e.g.<br>1111 0000b).                    |

|                   | For slave A, bit 1 is a 0; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves A and B, but not slave C, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).<br>To communicate with slaves A, B and C, the master must send an address with bit 0 set, |

|                   | bit 1 clear, and bit 2 clear (e.g. 1111 0001b).                                                                                                                                                                                                                                                        |

| Broadcast Address | A broadcast address is formed from the logical OR of the SADDR and SADEN registers<br>with zeros defined as don't care bits, e.g.:<br>SADDR0101 0110b<br>SADEN1111 1100b                                                                                                                               |

|                   | SADDR OR SADEN1111 111Xb                                                                                                                                                                                                                                                                               |

|                   | The use of don't care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:<br>Slave A:SADDR1111 0001b<br>SADEN1111 1010b                                                   |

|                   | Given1111 1X11b,                                                                                                                                                                                                                                                                                       |

|                   | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 1X11B,                                                                                                                                                                                                                                  |

|                   | Slave C:SADDR = 1111 0010b<br><u>SADEN1111 1101b</u><br>Given1111 1111b                                                                                                                                                                                                                                |

|                   | For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.                                                        |

Framing Error Detection (Modes 1, 2 and 3) Framing error detection is provided for the three asynchronous modes. To enable the framing bit error detection feature, set SMOD0 bit in PCON register as shown in Figure 46.

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two devices. If a valid stop bit is not found, the software sets FE bit in SCON register.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a chip reset clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When the framing error detection feature is enabled, RI rises on stop bit instead of the last data bit as detailed in Figure 36.

Figure 46. Framing Error Block Diagram

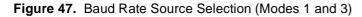

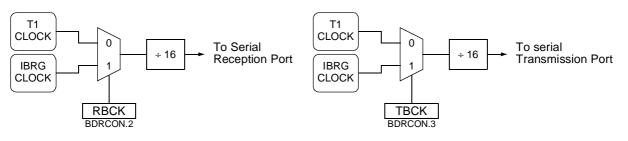

Baud Rate Selection (Modes 1<br/>and 3)In modes 1 and 3, the Baud Rate is derived either from the Timer 1 or the Internal Baud<br/>Rate Generator and allows different baud rate in reception and transmission.

As shown in Figure 47 the selection is done using RBCK and TBCK bits in BDRCON register.

Figure 48 gives the baud rate calculation formulas for each baud rate source while Table 65 details Internal Baud Rate Generator configuration for different peripheral clock frequencies and giving baud rates closer to the standard baud rates.

Figure 48. Baud Rate Formulas (Modes 1 and 3)

Baud\_Rate =  $\frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6^{(1-\text{SPD})} \cdot 32 \cdot (256 - \text{BRL})}$ Baud\_Rate =  $\frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6 \cdot 32 \cdot (256 - \text{TH1})}$ BRL =  $256 \frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{6^{(1-\text{SPD})} \cdot 32 \cdot \text{Baud}_{\text{Rate}}}$ TH1 =  $256 \frac{2^{\text{SMOD1}} \cdot \text{F}_{\text{PER}}}{192 \cdot \text{Baud}_{\text{Rate}}}$ a. BRG Formulab. T1 Formula

90 A/T8xC5121

# Table 67.SCON RegisterSCON (S:98h)Serial Control Registe

| 7             | 6               | 5                                                                                                                                                                                                                                                                                             | 4                                                                                                                                                                                                                                                         | 3                     | 2                   | 1  | 0  |  |  |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|----|----|--|--|--|--|

| FE/SM0        | SM1             | SM2                                                                                                                                                                                                                                                                                           | REN                                                                                                                                                                                                                                                       | TB8                   | RB8                 | ТІ | RI |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                           |                       |                     |    |    |  |  |  |  |

| 7             | FE              | Set by hardware to i                                                                                                                                                                                                                                                                          | aming Error bit<br>select this function, set SMOD0 bit in PCON register.<br>et by hardware to indicate an invalid stop bit.<br>ust be cleared by software.                                                                                                |                       |                     |    |    |  |  |  |  |

| 7             | SM0             | Serial Port Mode bi<br>To select this function<br>Software writes to bi<br>Refer to SM1 bit for                                                                                                                                                                                               | on, clear SMOD0 bi<br>its SM0 and SM1 to                                                                                                                                                                                                                  | o select the Serial P | ort operating mode. |    |    |  |  |  |  |

| 6             | SM1             | To select this function Software writes to be                                                                                                                                                                                                                                                 | 0       0       Shift Register       F <sub>OSC</sub> /12 or variable if SRC bit in BDRCON is set         0       1       1       8-bit UART       Variable         1       0       2       9-bit UART       F <sub>OSC</sub> /32 or F <sub>OSC</sub> /64 |                       |                     |    |    |  |  |  |  |

| 5             | SM2             | Serial Port Mode bit 2<br>Software writes to bit SM2 to enable and disable the multiprocessor communication and automatic address<br>recognition features.<br>This allows the Serial Port to differentiate between data and command frames and to recognize slave and broadcast<br>addresses. |                                                                                                                                                                                                                                                           |                       |                     |    |    |  |  |  |  |

| 4             | REN             | Clear to disable rece                                                                                                                                                                                                                                                                         | Receiver Enable bit<br>Clear to disable reception in mode 1, 2 and 3, and to enable transmission in mode 0.<br>Set to enable reception in all modes.                                                                                                      |                       |                     |    |    |  |  |  |  |

| 3             | TB8             |                                                                                                                                                                                                                                                                                               | Transmit bit 8<br>Modes 0 and 1: Not used.<br>Modes 2 and 3: Software writes the ninth data bit to be transmitted to TB8.                                                                                                                                 |                       |                     |    |    |  |  |  |  |

| 2             | RB8             | Receiver bit 8<br>Mode 0: Not used.<br>Mode 1 (SM2 cleared): Set or cleared by hardware to reflect the stop bit received.<br>Modes 2 and 3 (SM2 set): Set or cleared by hardware to reflect the ninth bit received.                                                                           |                                                                                                                                                                                                                                                           |                       |                     |    |    |  |  |  |  |

| 1             | TI              | Set by the transmitte                                                                                                                                                                                                                                                                         | Transmit Interrupt flag<br>Set by the transmitter after the last data bit is transmitted.<br>Must be cleared by software.                                                                                                                                 |                       |                     |    |    |  |  |  |  |

| 0             | RI              | Receive Interrupt f<br>Set by the receiver a<br>Must be cleared by s                                                                                                                                                                                                                          | after the stop bit of                                                                                                                                                                                                                                     | a frame has been re   | ceived.             |    |    |  |  |  |  |

| Pocot Value - | = XXX0 0000b    |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                           |                       |                     |    |    |  |  |  |  |

Reset Value = XXX0 0000b

**Table 69.** SIOCON RegisterSerial Input Output Configuration RegisterRegister (91h)

| 7             | 6                  | 5                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                             | 3     | 2 | 1 | 0 |  |  |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|---|---|---|--|--|--|--|

| PMSOEN1       | PMSOEN             |                                                                                                                                                                                                                                                                                                                                                                                 | VEXT0                                                                                                                         | VEXT1 |   |   |   |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                   |       |   |   |   |  |  |  |  |

| 7 - 6         | PMOSEN1<br>PMOSEN0 | Output Enable function on Txd/P3.1 and T0/P3.4:         PMSOEN1       PMSOEN0         0       0       PMOS is always off (reset value)         0       1       PMOS is always off verset value)         1       0       PMOS is always off verset value)         1       0       PMOS is driven only when OE is high         1       1       PMOS is driven only when OE is low |                                                                                                                               |       |   |   |   |  |  |  |  |

| 5 - 4         | -                  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                                                                                                                 |                                                                                                                               |       |   |   |   |  |  |  |  |

| 3             | CPRES<br>RES       | 0 Internal pull-                                                                                                                                                                                                                                                                                                                                                                | Card Presence pull-up resistor<br>0 Internal pull-up is connected<br>1 Internal pull-up is disconnected                       |       |   |   |   |  |  |  |  |

| 2             | EVAUTO             | EVCC Auto setup<br>Set to enable the Automatic mode of EV <sub>CC</sub> regulator<br>Clear to disable the Automatic mode of EV <sub>CC</sub> regulator                                                                                                                                                                                                                          |                                                                                                                               |       |   |   |   |  |  |  |  |

| 1 - 0         | VEXT0<br>VEXT1     | •                                                                                                                                                                                                                                                                                                                                                                               | EVCC voltage configuration:VEXT0VEXT100Power-down, $EV_{CC}$ is external (reset value)01 $EV_{CC} = 1.8V$ 10 $EV_{CC} = 2.3V$ |       |   |   |   |  |  |  |  |

Reset Value = 00XX 0000b

## Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the Watchdog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

Using the WDT

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x T<sub>CLK PERIPH</sub>, where T<sub>CLK PERIPH</sub>= 1/F<sub>CLK PERIPH</sub>. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16 ms to 2s @  $F_{OSCA}$  = 12 MHz. To manage this feature, refer to WDTPRG register description, Table 70. The WDTPRG register should be configured before the WDT activation sequence, and can not be modified until next reset.

Table 70.

WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

A/T8xC5121

#### Table 71. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7                                                      | 6               | 5                       | 4                                                                                     | 3 | 2  | 1  | 0  |  |  |  |  |

|--------------------------------------------------------|-----------------|-------------------------|---------------------------------------------------------------------------------------|---|----|----|----|--|--|--|--|

| -                                                      | -               | -                       | -                                                                                     | - | S2 | S1 | S0 |  |  |  |  |

| Bit<br>Number                                          | Bit<br>Mnemonic | Descriptio              | n                                                                                     |   |    |    |    |  |  |  |  |

| 7                                                      | -               |                         |                                                                                       |   |    |    |    |  |  |  |  |

| 6                                                      | -               |                         |                                                                                       |   |    |    |    |  |  |  |  |

| 5                                                      | -               | Reserved<br>The value r | Reserved<br>The value read from this bit is undetermined. Do not try to set this bit. |   |    |    |    |  |  |  |  |

| 4                                                      | -               |                         |                                                                                       |   |    |    |    |  |  |  |  |

| 3                                                      | -               |                         |                                                                                       |   |    |    |    |  |  |  |  |

| 2                                                      | S2              | WDT Time                | WDT Time-out select bit 2                                                             |   |    |    |    |  |  |  |  |

| 1                                                      | S1              | WDT Time                | WDT Time-out select bit 1                                                             |   |    |    |    |  |  |  |  |

| 0                                                      | S0              | WDT Time                | -out select bit                                                                       | 0 |    |    |    |  |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                 |                         |                                                                                       |   |    |    |    |  |  |  |  |

Reset Value = XXXX X000

# WDT during Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode the user does not need to service the WDT. There are 2 methods of exiting Power-down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the T8xC5121 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is better to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the T8xC5121 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

| Symbol            | Parameter          | Min                    | Тур              | Мах             | Unit  | Test Conditions                              |  |

|-------------------|--------------------|------------------------|------------------|-----------------|-------|----------------------------------------------|--|

|                   |                    | -0.5                   |                  | 0.4             | V     | EV <sub>CC</sub> = 1.8V                      |  |

|                   |                    | -0.5                   |                  | 0.5             | V     | $EV_{CC} = 2.3V$                             |  |

| VIL               | Input Low Voltage  | -0.5                   |                  | 0.5             | V     | $EV_{CC} = 2.8V$                             |  |

|                   |                    |                        |                  |                 |       | External EVcc                                |  |

|                   |                    |                        |                  |                 |       | Automatic EVcc                               |  |

|                   |                    | 1.4                    |                  | 2.3             | V     | EV <sub>CC</sub> = 1.8V                      |  |

|                   |                    | 1.4                    |                  | 2.8             | v     | $EV_{CC} = 2.3V$                             |  |

| V <sub>IH</sub>   | Input High Voltage | 2.0                    |                  | 3.3             | v     | $EV_{CC} = 2.8V$                             |  |

| ЧН                | input ngri voltage | 0.7 x EV <sub>CC</sub> | EV <sub>CC</sub> | $EV_{CC}$ +     | v     | External EV <sub>CC</sub>                    |  |

|                   |                    |                        | -•00             | 0.5             | •     | Automatic EVcc                               |  |

|                   |                    |                        |                  |                 |       |                                              |  |

| V <sub>OL</sub>   | Output Low         |                        |                  | 0.4             | v     | I <sub>OL</sub> = 1.2 mA                     |  |

| - OL              | Voltage            |                        |                  |                 | -     |                                              |  |

|                   |                    | 1.6                    |                  | 1.8             | V     | $EV_{CC}$ = 1.8V I <sub>OH</sub> = 1 $\mu$ A |  |

| V <sub>OH</sub>   | Output High        | 1.8                    |                  | 2.3             | V     | $EV_{CC} = 2.3V$                             |  |

| V OH              | Voltage            | 2.2                    |                  | 2.7             | V     | $EV_{CC} = 2.8V I_{OH} = 10\mu A$            |  |

|                   |                    | $0.8 \times EV_{CC}$   |                  | $EV_{CC}$       | V     | External EV <sub>CC</sub>                    |  |

| Elcc              | Extra Supply       |                        |                  | +3              | mA    | C <sub>L</sub> = 100 nF                      |  |

| LICC              | Current            |                        |                  | 10              | 110.4 |                                              |  |

|                   |                    | 1.6                    | 1.7              | 1.8             | V     | C <sub>L</sub> = 100 nF, 1.8V                |  |

|                   | Extra Supply       | 2.1                    | 2.2              | 2.3             | V     | C <sub>L</sub> = 100 nF, 2.3V                |  |

| $\rm EV_{\rm CC}$ | Voltage            | 2.6                    | 2.7              | 2.8             | V     | C <sub>L</sub> = 100 nF, 2.8V                |  |

|                   |                    | 1.6                    |                  | V <sub>CC</sub> | V     | External EV <sub>CC</sub>                    |  |

|                   |                    |                        |                  |                 |       | Automatic EVcc                               |  |

| Ts                | Sampling time      |                        |                  |                 |       | Automatic EVcc                               |  |

| Table 73.         Serial Interface DC parameter | rs (P3.0, P3.1, P3.3 and P3.4) |

|-------------------------------------------------|--------------------------------|

|-------------------------------------------------|--------------------------------|

Table 74. LED outputs DC Parameters (P3.6 and P3.7)

| Symbol          | Parameter                                         | Min         | Тур          | Мах          | Unit           | Test Conditions                                                                                                                                   |

|-----------------|---------------------------------------------------|-------------|--------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>OL</sub> | Output Low<br>Current, P3.6 and<br>P3.7 LED modes | 1<br>2<br>5 | 2<br>4<br>10 | 4<br>8<br>20 | mA<br>mA<br>mA | 2 mA configuration<br>4 mA configuration<br>10 mA configuration<br>$(T_A = -20^{\circ}C \text{ to } +50^{\circ}C, V_{CC} - V_{OL} = 2V \pm 20\%)$ |