Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 400MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 256kB                                                                                     |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf703wcbcz411                       |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### SECURITY FEATURES DISCLAIMER

To our knowledge, the Security Features, when used in accordance with the data sheet and hardware reference manual specifications, provide a secure method of implementing code and data safeguards. However, Analog Devices does not guarantee that this technology provides absolute security. ACCORDINGLY, ANALOG DEVICES HEREBY DISCLAIMS ANY AND ALL EXPRESS AND IMPLIED WARRANTIES THAT THE SECURITY FEATURES CANNOT BE BREACHED, COMPROMISED, OR OTHERWISE CIRCUM-VENTED AND IN NO EVENT SHALL ANALOG DEVICES BE LIABLE FOR ANY LOSS, DAMAGE, DESTRUCTION, OR RELEASE OF DATA, INFORMATION, PHYSICAL PROP-ERTY, OR INTELLECTUAL PROPERTY.

### **ADSP-BF70x DETAILED SIGNAL DESCRIPTIONS**

Table 6 provides a detailed description of each pin.

#### Table 6. ADSP-BF70x Detailed Signal Descriptions

| Port Name | Direction | Description                                                                                                                                                                                                                                                              |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN_RX    | Input     | Receive. Typically an external CAN transceiver's RX output.                                                                                                                                                                                                              |

| CAN_TX    | Output    | Transmit. Typically an external CAN transceiver's TX input.                                                                                                                                                                                                              |

| CNT_DG    | Input     | <b>Count Down and Gate.</b> Depending on the mode of operation this input acts either as a count down signal or a gate signal Count Down - This input causes the GP counter to decrement Gate - Stops the GP counter from incrementing or decrementing.                  |

| CNT_UD    | Input     | <b>Count Up and Direction.</b> Depending on the mode of operation this input acts either as a count up signal or a direction signal Count Up - This input causes the GP counter to increment Direction - Selects whether the GP counter is incrementing or decrementing. |

| CNT_ZM    | Input     | <b>Count Zero Marker.</b> Input that connects to the zero marker output of a rotary device or detects the pressing of a pushbutton.                                                                                                                                      |

| DMC_Ann   | Output    | Address n. Address bus.                                                                                                                                                                                                                                                  |

| DMC_BAn   | Output    | Bank Address Input n. Defines which internal bank an ACTIVATE, READ, WRITE, or PRECHARGE                                                                                                                                                                                 |

| Dime_DAin | output    | command is being applied to on the dynamic memory. Also defines which mode registers (MR, EMR, EMR2, and/or EMR3) are loaded during the LOAD MODE REGISTER command.                                                                                                      |

| DMC_CAS   | Output    | <b>Column Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the CAS input of dynamic memory.                                                                                    |

| DMC_CK    | Output    | Clock. Outputs DCLK to external dynamic memory.                                                                                                                                                                                                                          |

| DMC_CK    | Output    | Clock (Complement). Complement of DMC_CK.                                                                                                                                                                                                                                |

| DMC_CKE   | Output    | Clock enable. Active high clock enables. Connects to the dynamic memory's CKE input.                                                                                                                                                                                     |

| DMC_CSn   | Output    | Chip Select n. Commands are recognized by the memory only when this signal is asserted.                                                                                                                                                                                  |

| DMC_DQnn  | I/O       | Data n. Bidirectional Data bus.                                                                                                                                                                                                                                          |

| DMC_LDM   | Output    | <b>Data Mask for Lower Byte.</b> Mask for DMC_DQ07:DMC_DQ00 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_LDQS  | I/O       | <b>Data Strobe for Lower Byte.</b> DMC_DQ07:DMC_DQ00 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_LDQS  | I/O       | Data Strobe for Lower Byte (complement). Complement of LDQS. Not used in single-ended mode.                                                                                                                                                                              |

| DMC_ODT   | Output    | <b>On-die termination.</b> Enables dynamic memory termination resistances when driven high (assuming the memory is properly configured). ODT is enabled/disabled regardless of read or write commands.                                                                   |

| DMC_RAS   | Output    | <b>Row Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the RAS input of dynamic memory.                                                                                       |

| DMC_UDM   | Output    | <b>Data Mask for Upper Byte.</b> Mask for DMC_DQ15:DMC_DQ08 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_UDQS  | I/O       | <b>Data Strobe for Upper Byte.</b> DMC_DQ15:DMC_DQ08 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_UDQS  | I/O       | Data Strobe for Upper Byte (complement). Complement of UDQSb. Not used in single-ended mode.                                                                                                                                                                             |

| DMC_VREF  | Input     | Voltage Reference. Connect to half of the VDD_DMC voltage.                                                                                                                                                                                                               |

| DMC_WE    | Output    | Write Enable. Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the WE input of dynamic memory.                                                                                                     |

| PPI_CLK   | I/O       | <b>Clock.</b> Input in external clock mode, output in internal clock mode.                                                                                                                                                                                               |

| PPI_Dnn   | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                          |

| PPI_FS1   | I/O       | Frame Sync 1 (HSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS2   | I/O       | Frame Sync 2 (VSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS3   | I/O       | Frame Sync 3 (FIELD). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| HADC_VINn | Input     | <b>Analog Input at channel n.</b> Analog voltage inputs for digital conversion.                                                                                                                                                                                          |

### 12 mm × 12 mm 88-LEAD LFCSP (QFN) SIGNAL DESCRIPTIONS

The processor's pin definitions are shown in Table 11. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

#### Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions

| Signal Name | Description                     | Port      | Pin Name      |

|-------------|---------------------------------|-----------|---------------|

| CAN0_RX     | CAN0 Receive                    | С         | PC_02         |

| CAN0_TX     | CAN0 Transmit                   | С         | PC_03         |

| CAN1_RX     | CAN1 Receive                    | A         | PA_12         |

| CAN1_TX     | CAN1 Transmit                   | A         | PA_13         |

| CNT0_DG     | CNT0 Count Down and Gate        | A         | PA_07         |

| CNT0_UD     | CNT0 Count Up and Direction     | A         | PA_15         |

| CNT0_ZM     | CNT0 Count Zero Marker          | A         | PA_13         |

| GND         | Ground                          | Not Muxed | GND           |

| JTG_SWCLK   | TAPC0 Serial Wire Clock         | Not Muxed | JTG_TCK_SWCLK |

| JTG_SWDIO   | TAPC0 Serial Wire DIO           | Not Muxed | JTG_TMS_SWDIO |

| JTG_SWO     | TAPC0 Serial Wire Out           | Not Muxed | JTG_TDO_SWO   |

| JTG_TCK     | TAPC0 JTAG Clock                | Not Muxed | JTG_TCK_SWCLK |

| JTG_TDI     | TAPC0 JTAG Serial Data In       | Not Muxed | JTG_TDI       |

| JTG_TDO     | TAPC0 JTAG Serial Data Out      | Not Muxed | JTG_TDO_SWO   |

| JTG_TMS     | TAPC0 JTAG Mode Select          | Not Muxed | JTG_TMS_SWDIO |

| JTG_TRST    | TAPC0 JTAG Reset                | Not Muxed | JTG_TRST      |

| MSI0_CD     | MSI0 Card Detect                | A         | PA_08         |

| MSI0_CLK    | MSI0 Clock                      | С         | PC_09         |

| MSI0_CMD    | MSI0 Command                    | С         | PC_05         |

| MSI0_D0     | MSI0 Data 0                     | С         | PC_08         |

| MSI0_D1     | MSI0 Data 1                     | С         | PC_04         |

| MSI0_D2     | MSI0 Data 2                     | С         | PC_07         |

| MSI0_D3     | MSI0 Data 3                     | С         | PC_06         |

| MSI0_D4     | MSI0 Data 4                     | С         | PC_10         |

| PA_00-PA_15 | Position 00 through Position 15 | A         | PA_00-PA_15   |

| PB_00-PB_15 | Position 00 through Position 15 | В         | PB_00-PB_15   |

| PC_00-PC_10 | Position 00 through Position 10 | С         | PC_00-PC_10   |

| PPI0_CLK    | EPPI0 Clock                     | А         | PA_14         |

| PPI0_D00    | EPPI0 Data 0                    | В         | PB_07         |

| PPI0_D01    | EPPI0 Data 1                    | В         | PB_06         |

| PPI0_D02    | EPPI0 Data 2                    | В         | PB_05         |

| PPI0_D03    | EPPI0 Data 3                    | В         | PB_04         |

| PPI0_D04    | EPPI0 Data 4                    | В         | PB_03         |

| PPI0_D05    | EPPI0 Data 5                    | В         | PB_02         |

| PPI0_D06    | EPPI0 Data 6                    | В         | PB_01         |

| PPI0_D07    | EPPIO Data 7                    | В         | PB_00         |

### Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

| Signal Name          | Description                                      | Port      | Pin Name       |

|----------------------|--------------------------------------------------|-----------|----------------|

| SPT0_AFS             | SPORT0 Channel A Frame Sync                      | Α         | PA_12          |

| SPT0_AFS             | SPORT0 Channel A Frame Sync                      | С         | PC_05          |

| SPT0_ATDV            | SPORT0 Channel A Transmit Data Valid             | А         | PA_15          |

| SPT0_BCLK            | SPORT0 Channel B Clock                           | В         | PB_04          |

| SPT0_BCLK            | SPORT0 Channel B Clock                           | С         | PC_04          |

| SPT0_BD0             | SPORT0 Channel B Data 0                          | В         | PB_05          |

| SPT0_BD0             | SPORT0 Channel B Data 0                          | С         | PC_06          |

| SPT0_BD1             | SPORT0 Channel B Data 1                          | В         | <br>PB_07      |

| SPT0_BD1             | SPORTO Channel B Data 1                          | С         | PC_01          |

| SPT0_BFS             | SPORTO Channel B Frame Sync                      | В         | PB_06          |

| SPTO_BFS             | SPORTO Channel B Frame Sync                      | C         | PC_07          |

| SPT0_BTDV            | SPORTO Channel B Transmit Data Valid             | A         | PA_15          |

| SPT1_ACLK            | SPORT1 Channel A Clock                           | A         | PA_08          |

| SPT1_AD0             | SPORT1 Channel A Data 0                          | A         | PA_10          |

| SPT1_AD1             | SPORT1 Channel A Data 0                          | A         | PA_11          |

| SPT1_AD1<br>SPT1_AFS | SPORT1 Channel A Frame Sync                      | A         | PA_11<br>PA_09 |

|                      | SPORT1 Channel A Transmit Data Valid             | A         |                |

| SPT1_ATDV            |                                                  |           | PA_07          |

| SPT1_BCLK            | SPORT1 Channel B Clock<br>SPORT1 Channel B Clock | B         | PB_00          |

| SPT1_BCLK            |                                                  | C         | PC_10          |

| SPT1_BD0             | SPORT1 Channel B Data 0                          | В         | PB_02          |

| SPT1_BD1             | SPORT1 Channel B Data 1                          | В         | PB_03          |

| SPT1_BFS             | SPORT1 Channel B Frame Sync                      | В         | PB_01          |

| SPT1_BTDV            | SPORT1 Channel B Transmit Data Valid             | Α         | PA_07          |

| SYS_BMODE0           | Boot Mode Control 0                              | Not Muxed | SYS_BMODE0     |

| SYS_BMODE1           | Boot Mode Control 1                              | Not Muxed | SYS_BMODE1     |

| SYS_CLKIN            | Clock/Crystal Input                              | Not Muxed | SYS_CLKIN      |

| SYS_CLKOUT           | Processor Clock Output                           | Not Muxed | SYS_CLKOUT     |

| SYS_EXTWAKE          | External Wake Control                            | Not Muxed | SYS_EXTWAKE    |

| SYS_FAULT            | Active-Low Fault Output                          | Not Muxed | SYS_FAULT      |

| SYS_HWRST            | Processor Hardware Reset Control                 | Not Muxed | SYS_HWRST      |

| SYS_NMI              | Non-maskable Interrupt                           | Not Muxed | SYS_NMI        |

| SYS_RESOUT           | Reset Output                                     | Not Muxed | SYS_RESOUT     |

| SYS_WAKE0            | Power Saving Mode Wake-up 0                      | В         | PB_07          |

| SYS_WAKE1            | Power Saving Mode Wake-up 1                      | В         | PB_08          |

| SYS_WAKE2            | Power Saving Mode Wake-up 2                      | В         | PB_12          |

| SYS_WAKE3            | Power Saving Mode Wake-up 3                      | С         | PC_02          |

| SYS_WAKE4            | Power Saving Mode Wake-up 4                      | A         | PA_12          |

| SYS_XTAL             | Crystal Output                                   | Not Muxed | SYS_XTAL       |

| FM0_ACI0             | TIMER0 Alternate Capture Input 0                 | С         | PC_03          |

| TM0_ACI1             | TIMER0 Alternate Capture Input 1                 | В         | PB_01          |

| TM0_ACI2             | TIMER0 Alternate Capture Input 2                 | с         | PC_07          |

| TM0_ACI3             | TIMER0 Alternate Capture Input 3                 | В         | PB_09          |

| <br>TM0_ACI4         | TIMER0 Alternate Capture Input 4                 | С         | PC_01          |

| TM0_ACI5             | TIMER0 Alternate Capture Input 5                 | C         | PC_02          |

| TM0_ACI6             | TIMER0 Alternate Capture Input 6                 | A         | PA_12          |

| TM0_ACLK0            | TIMERO Alternate Clock 0                         | C         | PC_04          |

| Signal Name | Multiplexed<br>Function 0 | Multiplexed<br>Function 1 | Multiplexed<br>Function 2 | Multiplexed<br>Function 3 | Multiplexed<br>Function Input Tap |

|-------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------|

| PC_00       | UART1_TX                  | SPT0_AD1                  | PPI0_D15                  |                           |                                   |

| PC_01       | UART1_RX                  | SPT0_BD1                  | PPI0_D14                  | SMC0_A09                  | TM0_ACI4                          |

| PC_02       | UARTO_RTS                 | CAN0_RX                   | PPI0_D13                  | SMC0_A10                  | TM0_ACI5/SYS_<br>WAKE3            |

| PC_03       | UARTO_CTS                 | CAN0_TX                   | PPI0_D12                  | SMC0_A11                  | TM0_ACI0                          |

| PC_04       | SPT0_BCLK                 | SPI0_CLK                  | MSI0_D1                   | SMC0_A12                  | TM0_ACLK0                         |

| PC_05       | SPT0_AFS                  | TM0_TMR3                  | MSI0_CMD                  |                           |                                   |

| PC_06       | SPT0_BD0                  | SPI0_MISO                 | MSI0_D3                   |                           |                                   |

| PC_07       | SPT0_BFS                  | SPI0_MOSI                 | MSI0_D2                   |                           | TM0_ACI2                          |

| PC_08       | SPT0_AD0                  | SPI0_D2                   | MSI0_D0                   |                           |                                   |

| PC_09       | SPT0_ACLK                 | SPI0_D3                   | MSI0_CLK                  |                           | TM0_ACLK2                         |

| PC_10       | SPT1_BCLK                 | MSI0_D4                   | SPI1_SEL3                 |                           | TM0_ACLK1                         |

### Table 14. Signal Multiplexing for Port C

### ADSP-BF70x DESIGNER QUICK REFERENCE

Table 15 provides a quick reference summary of pin related information for circuit board design. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Pin Type: The Type column in the table identifies the I/O type or supply type of the pin. The abbreviations used in this column are na (none), I/O (input/output), a (analog), s (supply), and g (ground).

- Driver Type: The Driver Type column in the table identifies the driver type used by the pin. The driver types are defined in the output drive currents section of this data sheet.

- Internal Termination: The Int Term column in the table specifies the termination present when the processor is not in the reset or hibernate state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Reset Termination: The Reset Term column in the table specifies the termination present when the processor is in the reset state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Reset Drive: The Reset Drive column in the table specifies the active drive on the signal when the processor is in the reset state.

- Hibernate Termination: The Hiber Term column in the table specifies the termination present when the processor is in the hibernate state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Hibernate Drive: The Hiber Drive column in the table specifies the active drive on the signal when the processor is in the hibernate state.

- Power Domain: The Power Domain column in the table specifies the power supply domain in which the signal resides.

- Description and Notes: The Description and Notes column in the table identifies any special requirements or characteristics for the signal. If no special requirements are listed the signal may be left unconnected if it is not used. Also, for multiplexed general-purpose I/O pins, this column identifies the functions available on the pin.

If an external pull-up or pull-down resistor is required for any signal, 100  $k\Omega$  is the maximum value that can be used unless otherwise noted.

Note that for Port A, Port B, and Port C (PA\_00 to PC\_14), when <u>SYS\_HWRST</u> is low, these pads are three-state. After <u>SYS\_HWRST</u> is released, but before code execution begins, these pins are internally pulled up. Subsequently, the state depends on the input enable and output enable which are controlled by software.

Software control of internal pull-ups works according to the following settings in the PADS\_PCFG0 register. When PADS\_PCFG0 = 0: For PA\_15:PA\_00, PB\_15:PB\_00, and PC\_14:PC\_00, the internal pull-up is enabled when both the input enable and output enable of a particular pin are deasserted. When PADS\_PCFG0 = 1: For PA\_15:PA\_00, PB\_15:PB\_00, and PC\_14:PC\_00, the internal pull-up is enabled as long as the output enable of a particular pin is deasserted.

There are some exceptions to this scheme:

- Internal pull-ups are always disabled if MSI mode is selected for that signal.

- The following signals enabled the internal pull-down when the output enable is de-asserted: <u>SMC0\_AMS[1:0]</u>, <u>SMC0\_ARE</u>, <u>SMC0\_AWE</u>, <u>SMC0\_AOE</u>, <u>SMC0\_ARDY</u>, <u>SPI0\_SEL[6:1]</u>, <u>SPI1\_SEL[4:1]</u>, and <u>SPI2\_SEL[3:1]</u>.

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                 |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|------------------------------------------|

| DMC0_A00    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 0<br>Notes: No notes. |

| DMC0_A01    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 1<br>Notes: No notes. |

| DMC0_A02    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 2<br>Notes: No notes. |

| DMC0_A03    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 3<br>Notes: No notes. |

| DMC0_A04    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 4<br>Notes: No notes. |

| DMC0_A05    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 5<br>Notes: No notes. |

#### Table 15. ADSP-BF70x Designer Quick Reference

|                   | _    | Driver | Int<br>T | Reset | Reset | Hiber<br>- | Hiber | Power    | Description                                                                                                                                                  |

|-------------------|------|--------|----------|-------|-------|------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name       | Туре | Туре   | Term     | Term  | Drive | Term       | Drive | Domain   | and Notes                                                                                                                                                    |

| GND_HADC          | g    | na     | none     | none  | none  | none       | none  | na       | Desc: Ground HADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                                       |

| HADC0_VIN0        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel (<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VIN1        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel <sup>2</sup><br>Notes: If HADC is not used, connect to<br>ground.                                                        |

| HADC0_VIN2        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 2<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VIN3        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 3<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VREFN       | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Ground Reference for<br>ADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                 |

| HADC0_VREFP       | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 External Reference for<br>ADC<br>Notes: If HADC is not used, connect to<br>ground.                                                               |

| JTG_TCK_<br>SWCLK | I/O  | na     | pd       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Clock   Serial Wire Clock<br>Notes: Functional during reset.                                                                                      |

| JTG_TDI           | I/O  | na     | pu       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Serial Data In<br>Notes: Functional during reset.                                                                                                 |

| JTG_TDO_SWO       | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Serial Data Out   Serial Wire<br>Out<br>Notes: Functional during reset, three-<br>state when JTG_TRST is asserted.                                |

| JTG_TMS_<br>SWDIO | I/O  | А      | pu       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Mode Select   Serial Wire DIC<br>Notes: Functional during reset.                                                                                  |

| JTG_TRST          | I/O  | na     | pd       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Reset<br>Notes: Functional during reset, a 10k<br>external pull-down may be used to<br>shorten the t <sub>VDDEXT_RST</sub> timing<br>requirement. |

| PA_00             | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: SPI1 Clock   TRACE0 Trace Data 7<br>SMC0 Byte Enable 0<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.         |

| PA_01             | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: SPI1 Master In, Slave Out   TRACEC<br>Trace Data 6   SMC0 Byte Enable 1<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.         |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

#### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                      |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_05       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Frame Sync   TM0<br>Timer 3   MSI0 Command<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                              |

| PC_06       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Data 0   SPl0<br>Master In, Slave Out   MSI0 Data 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                     |

| PC_07       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Frame Sync   SPI0<br>Master Out, Slave In   MSI0 Data 2   TM0<br>Alternate Capture Input 2<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                              |

| PC_08       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Data 0   SPI0 Data<br>2   MSI0 Data 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                   |

| PC_09       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Clock   SPI0 Data<br>3   MSI0 Clock   TM0 Alternate Clock 2<br>Notes: No notes.                                                                                                                                                                                          |

| PC_10       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Clock   MSI0 Data<br>4   SPI1 Slave Select Output 3   TM0<br>Alternate Clock 1<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used. |

| PC_11       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Frame Sync   MSI0<br>Data 5   SPI0 Slave Select Output 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used.                       |

| PC_12       | Ι/Ο  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 0   MSI0 Data<br>6<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                 |

### **SPECIFICATIONS**

For information about product specifications, contact your Analog Devices, Inc. representative.

### **OPERATING CONDITIONS**

| Parameter                          |                                    | Test Conditions/Comments                               | Min                      | Nominal                  | Max                                    | Unit |

|------------------------------------|------------------------------------|--------------------------------------------------------|--------------------------|--------------------------|----------------------------------------|------|

| V <sub>DD_INT</sub>                | Internal Supply Voltage            | CCLK ≤ 400 MHz                                         | 1.045                    | 1.100                    | 1.155                                  | V    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 1.7                      | 1.8                      | 1.9                                    | v    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| V <sub>DD_DMC</sub>                | DDR2/LPDDR Supply Voltage          |                                                        | 1.7                      | 1.8                      | 1.9                                    | v    |

| $V_{DD_USB}^{2}$                   | USB Supply Voltage                 |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_{RTC}}$                     | Real-Time Clock Supply Voltage     |                                                        | 2.00                     | 3.30                     | 3.47                                   | v    |

| $V_{DD\_HADC}$                     | Housekeeping ADC Supply<br>Voltage |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_OTP}^{1}$                   | OTP Supply Voltage                 |                                                        |                          |                          |                                        |      |

|                                    | For Reads                          |                                                        | 2.25                     | 3.30                     | 3.47                                   | V    |

|                                    | For Writes                         |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| V <sub>DDR_VREF</sub>              | DDR2 Reference Voltage             |                                                        | $0.49 \times V_{DD_DMC}$ | $0.50 \times V_{DD_DMC}$ | $0.51 \times V_{DD_DMC}$               | v    |

| $V_{HADC_{REF}}^{3}$               | HADC Reference Voltage             |                                                        | 2.5                      | 3.30                     | V <sub>DD_HADC</sub>                   | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD_{EXT}} = 3.47 V$                                | 2.0                      |                          |                                        | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD\_EXT} = 1.9 V$                                  | $0.7 \times V_{DD\_EXT}$ |                          |                                        | V    |

| V <sub>IHTWI</sub> <sup>5, 6</sup> | High Level Input Voltage           | $V_{DD\_EXT} = maximum$                                | $0.7 \times V_{VBUSTWI}$ |                          | V <sub>VBUSTWI</sub>                   | V    |

| $V_{\text{IH}_{DDR2}}^{7}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $V_{DDR\_REF} + 0.25$    |                          |                                        | v    |

| $V_{\text{IH\_LPDDR}}^{8}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $0.8 \times V_{DD_DMC}$  |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 1.075 V$                                     | 0.50                     |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 0.725 V$                                     | 0.55                     |                          |                                        | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD_{EXT}} = 3.13 V$                                |                          |                          | 0.8                                    | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD\_EXT} = 1.7 V$                                  |                          |                          | $0.3 \times V_{\text{DD}\_\text{EXT}}$ | V    |

| V <sub>ILTWI</sub> 5, 6            | Low Level Input Voltage            | $V_{DD\_EXT} = minimum$                                |                          |                          | $0.3 	imes V_{VBUSTWI}$                | V    |

| $V_{IL_DDR2}^{7}$                  |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $V_{DDR_{REF}} - 0.25$                 | V    |

| $V_{IL\_LPDDR}^{8}$                |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $0.2 \times V_{DD_DMC}$                | V    |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = 0^{\circ}C \text{ to } +70^{\circ}C$    | 0                        |                          | 105                                    | °C   |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +85^{\circ}C$  | -40                      |                          | +105                                   | °C   |

| T                                  | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +105^{\circ}C$ | -40                      |                          | +125                                   | °C   |

<sup>1</sup>Must remain powered (even if the associated function is not used).

<sup>2</sup> If not used, connect to 1.8 V or 3.3 V.

$^{3}\mathrm{V}_{\mathrm{HADC\_VREF}}$  should always be less than  $\mathrm{V}_{\mathrm{DD\_HADC}}.$

<sup>4</sup> Parameter value applies to all input and bidirectional signals except RTC signals, TWI signals, DMC0 signals, and USB0 signals.

<sup>5</sup> Parameter applies to TWI signals.

$^{6}$  TWI signals are pulled up to  $V_{BUSTWI}$ . See Table 16.

<sup>7</sup> Parameter applies to DMC0 signals in DDR2 mode.

<sup>8</sup> Parameter applies to DMC0 signals in LPDDR mode.

<sup>9</sup> Parameter applies to signals DMC0\_LDQS, <u>DMC0\_LDQS</u>, DMC0\_UDQS, <u>DMC0\_UDQS</u> when used in DDR2 differential input mode.

#### Table 18. Peripheral Clock Operating Conditions

| Parameter                      |                                                                       | Restriction                                  | Min | Тур | Мах | Unit |

|--------------------------------|-----------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>OCLK</sub>              | Output Clock Frequency                                                |                                              |     |     | 50  | MHz  |

| f <sub>sys_clkoutj</sub>       | SYS_CLKOUT Period Jitter <sup>1, 2</sup>                              |                                              |     | ±2  |     | %    |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Transmitting Data                           |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Receiving Data                              |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKEXT</sub>  | External SPI Clock When Receiving Data <sup>3, 4</sup>                | $f_{SPICLKEXT} \leq f_{SCLK0}$               |     |     | 50  | MHz  |

| <b>f</b> <sub>spiclkext</sub>  | External SPI Clock When Transmitting Data <sup>3, 4</sup>             | $f_{\text{SPICLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| f <sub>MSICLKPROG</sub>        | Programmed MSI Clock                                                  |                                              |     |     | 50  | MHz  |

<sup>1</sup>SYS\_CLKOUT jitter is dependent on the application system design including pin switching activity, board layout, and the jitter characteristics of the SYS\_CLKIN source. Due to the dependency on these factors the measured jitter may be higher or lower than this typical specification for each end application.

<sup>2</sup> The value in the Typ field is the percentage of the SYS\_CLKOUT period.

<sup>3</sup> The maximum achievable frequency for any peripheral in external clock mode is dependent on being able to meet the setup and hold times in the ac timing specifications section for that peripheral. Pay particular attention to setup and hold times for VDD\_EXT = 1.8 V which may preclude the maximum frequency listed here.

$^4$  The peripheral external clock frequency must also be less than or equal to the  $f_{SCLK}$  that clocks the peripheral.

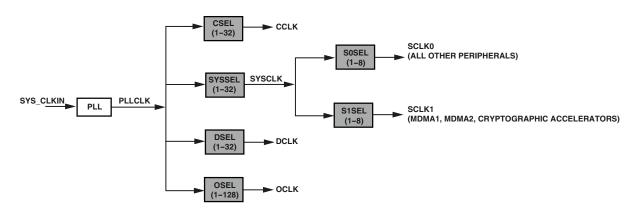

Figure 6. Clock Relationships and Divider Values

#### Table 19. Phase-Locked Loop Operating Conditions

| Parameter                  |                     | Min   | Max | Unit |

|----------------------------|---------------------|-------|-----|------|

| <b>f</b> <sub>PLLCLK</sub> | PLL Clock Frequency | 230.2 | 800 | MHz  |

| CGU_CTL.MSEL <sup>1</sup>  | PLL Multiplier      | 8     | 41  |      |

<sup>1</sup>The CGU\_CTL.MSEL setting must also be chosen to ensure that the f<sub>PLLCLK</sub> specification is not violated.

### PACKAGE INFORMATION

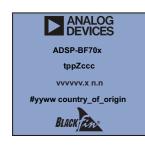

The information presented in Figure 7 and Table 27 provides details about package branding. For a complete listing of product availability, see the Ordering Guide.

Figure 7. Product Information on Package<sup>1</sup>

<sup>1</sup> Exact brand may differ, depending on package type.

#### Table 27. Package Brand Information

| Brand Key  | Field Description          |

|------------|----------------------------|

| ADSP-BF70x | Product model              |

| t          | Temperature range          |

| рр         | Package type               |

| Z          | RoHS compliant designation |

| ссс        | See Ordering Guide         |

| ννννν.χ    | Assembly lot code          |

| n.n        | Silicon revision           |

| yyww       | Date code                  |

### **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 28 may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### Table 28. Absolute Maximum Ratings

| Parameter                                            | Rating             |

|------------------------------------------------------|--------------------|

| Internal Supply Voltage (V <sub>DD_INT</sub> )       | –0.33 V to +1.20 V |

| External (I/O) Supply Voltage (V <sub>DD_EXT</sub> ) | –0.33 V to +3.60 V |

| DDR2 Controller Supply Voltage                       | –0.33 V to +1.90 V |

| (V <sub>DD_DMC</sub> )                               |                    |

| USB PHY Supply Voltage (V <sub>DD_USB</sub> )        | –0.33 V to +3.60 V |

| Real-Time Clock Supply Voltage                       | –0.33 V to +3.60 V |

| (V <sub>DD_RTC</sub> )                               |                    |

| Housekeeping ADC Supply Voltage                      | –0.33 V to +3.60 V |

| (V <sub>DD_HADC</sub> )                              |                    |

| One-Time Programmable Memory                         | –0.33 V to +3.60 V |

| Supply Voltage (V <sub>DD_OTP</sub> )                |                    |

| HADC Reference Voltage (V <sub>HADC_REF</sub> )      | –0.33 V to +3.60 V |

#### Table 28. Absolute Maximum Ratings (Continued)

| Parameter                                                        | Rating                                   |

|------------------------------------------------------------------|------------------------------------------|

| DDR2 Reference Voltage (V <sub>DDR_REF</sub> )                   | –0.33 V to +1.90 V                       |

| Input Voltage <sup>1, 2</sup>                                    | –0.33 V to +3.60 V                       |

| TWI Input Voltage <sup>2, 3</sup>                                | –0.33 V to +5.50 V                       |

| USB0_Dx Input Voltage <sup>4</sup>                               | –0.33 V to +5.25 V                       |

| USB0_VBUS Input Voltage <sup>5</sup>                             | –0.33 V to +6 V                          |

| DDR2 Input Voltage⁵                                              | –0.33 V to +1.90 V                       |

| Output Voltage Swing                                             | $-0.33$ V to V <sub>DD_EXT</sub> + 0.5 V |

| I <sub>OH</sub> /I <sub>OL</sub> Current per Signal <sup>1</sup> | 4 mA (max)                               |

| Storage Temperature Range                                        | –65°C to +150°C                          |

| Junction Temperature While Biased                                | +125°C                                   |

<sup>1</sup> Applies to 100% transient duty cycle.

$^2$  Applies only when  $V_{\rm DD\_EXT}$  is within specifications. When  $V_{\rm DD\_EXT}$  is outside specifications, the range is  $V_{\rm DD\_EXT}\pm0.2$  V.

<sup>3</sup> Applies to balls TWI\_SCL and TWI\_SDA.

<sup>4</sup> If the USB is not used, connect USB0\_Dx and USB0\_VBUS according to Table 15 on Page 38.

$^5$  Applies only when  $V_{DD\_DMC}$  is within specifications. When  $V_{DD\_DMC}$  is outside specifications, the range is  $V_{DD\_DMC}\pm 0.2$  V.

### **ESD SENSITIVITY**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

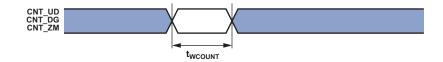

#### Up/Down Counter/Rotary Encoder Timing

Table 47 and Figure 25 describe timing, related to the general-purpose counter (CNT).

#### Table 47. Up/Down Counter/Rotary Encoder Timing

|                     |                                                  |                      | D_EXT<br>Nominal |                      | V <sub>DD_EXT</sub><br>V Nominal |      |

|---------------------|--------------------------------------------------|----------------------|------------------|----------------------|----------------------------------|------|

| Parameter           |                                                  | Min                  | Max              | Min                  | Max                              | Unit |

| Timing Requirement  | nt                                               |                      |                  |                      |                                  |      |

| t <sub>wcount</sub> | Up/Down Counter/Rotary Encoder Input Pulse Width | $2 \times t_{SCLK0}$ |                  | $2 \times t_{SCLK0}$ |                                  | ns   |

Figure 25. Up/Down Counter/Rotary Encoder Timing

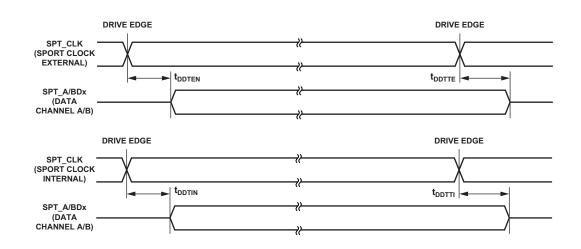

#### Table 51. Serial Ports—Enable and Three-State

|                    |                                                          | 1.8   | V <sub>DD_EXT</sub><br>SV Nominal | 3.3 | V <sub>DD_EXT</sub><br>3.3 V Nominal |      |

|--------------------|----------------------------------------------------------|-------|-----------------------------------|-----|--------------------------------------|------|

| Paramete           | er                                                       | Min   | Max                               | Min | Max                                  | Unit |

| Switching          | Characteristics                                          |       |                                   |     |                                      |      |

| t <sub>DDTEN</sub> | Data Enable from External Transmit SPT_CLK <sup>1</sup>  | 1     |                                   | 1   |                                      | ns   |

| t <sub>DDTTE</sub> | Data Disable from External Transmit SPT_CLK <sup>1</sup> |       | 14                                |     | 14                                   | ns   |

| t <sub>DDTIN</sub> | Data Enable from Internal Transmit SPT_CLK <sup>1</sup>  | -1.12 |                                   | -1  |                                      | ns   |

| t <sub>DDTTI</sub> | Data Disable from Internal Transmit SPT_CLK <sup>1</sup> |       | 2.8                               |     | 2.8                                  | ns   |

<sup>1</sup>Referenced to drive edge.

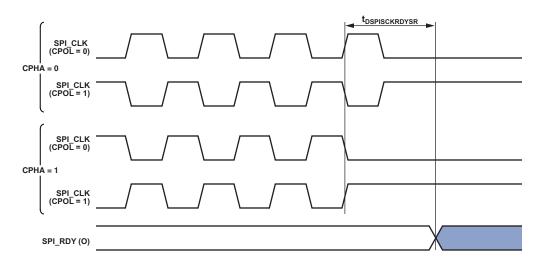

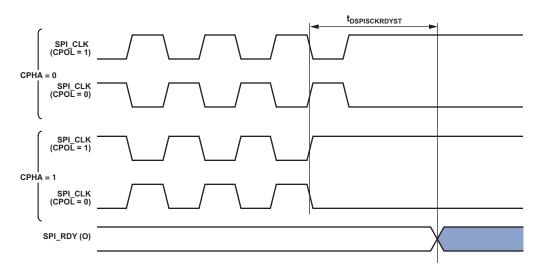

#### Serial Peripheral Interface (SPI) Port—SPI\_RDY Slave Timing

Table 56. SPI Port—SPI\_RDY Slave Timing

|                           |                                                                           | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal       |                                     |      |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|------|

| Parameter                 |                                                                           | Min                                              | Max                                 | Unit |

| Switching C               | haracteristics                                                            |                                                  |                                     |      |

| t <sub>dspisckrdysr</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Receive  | $2.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $3.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

| t <sub>dspisckrdyst</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Transmit | $3.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $4.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

Figure 33. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Receive (FCCH = 0)

Figure 34. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Transmit (FCCH = 1)

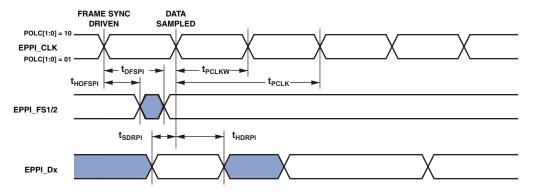

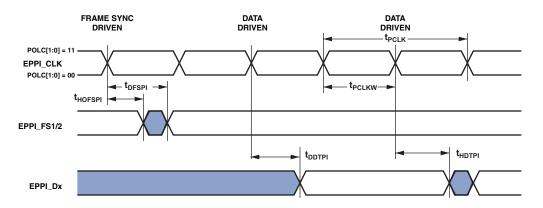

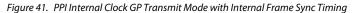

#### Enhanced Parallel Peripheral Interface Timing

The following tables and figures describe enhanced parallel peripheral interface timing operations. The POLC bits in the EPPI\_CTL register may be used to set the sampling/driving edges of the EPPI clock.

When internally generated, the programmed PPI clock ( $f_{PCLKPROG}$ ) frequency in MHz is set by the following equation where VALUE is a field in the EPPI\_CLKDIV register that can be set from 0 to 65,535:

$$f_{PCLKPROG} = \frac{f_{SCLK0}}{(VALUE+1)}$$

$t_{PCLKPROG} = \frac{1}{f_{PCLKPROG}}$

When externally generated the EPPI\_CLK is called  $f_{\mbox{\scriptsize PCLKEXT}}$  :

$$t_{PCLKEXT} = \frac{1}{f_{PCLKEXT}}$$

#### Table 60. Enhanced Parallel Peripheral Interface—Internal Clock

|                     |                                                                            | V <sub>DD_EXT</sub><br>1.8V Nomi |     | V <sub>DD_EXT</sub><br>3.3 V Nom |     |      |

|---------------------|----------------------------------------------------------------------------|----------------------------------|-----|----------------------------------|-----|------|

| Parameter           |                                                                            | Min                              | Max | Min                              | Max | Unit |

| Timing Requ         | irements                                                                   |                                  |     |                                  |     |      |

| t <sub>SFSPI</sub>  | External FS Setup Before EPPI_CLK                                          | 6.5                              |     | 5                                |     | ns   |

| t <sub>HFSPI</sub>  | External FS Hold After EPPI_CLK                                            | 1.5                              |     | 1                                |     | ns   |

| t <sub>SDRPI</sub>  | Receive Data Setup Before EPPI_CLK                                         | 6.4                              |     | 5                                |     | ns   |

| t <sub>HDRPI</sub>  | Receive Data Hold After EPPI_CLK                                           | 1                                |     | 1                                |     | ns   |

| t <sub>SFS3GI</sub> | External FS3 Input Setup Before EPPI_CLK<br>Fall Edge in Clock Gating Mode | 16.5                             |     | 14                               |     | ns   |

| t <sub>HFS3GI</sub> | External FS3 Input Hold Before EPPI_CLK<br>Fall Edge in Clock Gating Mode  | 1.5                              |     | 0                                |     | ns   |

| Switching Ch        | naracteristics                                                             |                                  |     |                                  |     |      |

| t <sub>PCLKW</sub>  | EPPI_CLK Width <sup>1</sup>                                                | $0.5 \times t_{PCLKPROG} - 2$    |     | $0.5 \times t_{PCLKPROG} - 2$    |     | ns   |

| t <sub>PCLK</sub>   | EPPI_CLK Period <sup>1</sup>                                               | t <sub>PCLKPROG</sub> – 2        |     | t <sub>PCLKPROG</sub> – 2        |     | ns   |

| t <sub>DFSPI</sub>  | Internal FS Delay After EPPI_CLK                                           |                                  | 2   |                                  | 2   | ns   |

| t <sub>HOFSPI</sub> | Internal FS Hold After EPPI_CLK                                            | -4                               |     | -3                               |     | ns   |

| t <sub>DDTPI</sub>  | Transmit Data Delay After EPPI_CLK                                         |                                  | 2   |                                  | 2   | ns   |

| t <sub>HDTPI</sub>  | Transmit Data Hold After EPPI_CLK                                          | -4                               |     | -3                               |     | ns   |

<sup>1</sup>See Table 18 on Page 52 in Clock Related Operating Conditions for details on the minimum period that may be programmed for t<sub>PCLKPROG</sub>.

Figure 40. PPI Internal Clock GP Receive Mode with Internal Frame Sync Timing

Figure 42. PPI Internal Clock GP Receive Mode with External Frame Sync Timing

#### Universal Asynchronous Receiver-Transmitter (UART) Ports—Receive and Transmit Timing

The universal asynchronous receiver-transmitter (UART) ports receive and transmit operations are described in the *ADSP-BF70x Blackfin+ Processor Hardware Reference*.

#### Controller Area Network (CAN) Interface

The controller area network (CAN) interface timing is described in the ADSP-BF70x Blackfin+ Processor Hardware Reference.

#### Universal Serial Bus (USB) On-The-Go—Receive and Transmit Timing

Table 62 describes the universal serial bus (USB) on-the-go receive and transmit operations.

#### Table 62. USB On-The-Go—Receive and Transmit Timing

|                   |                                  |     | V <sub>DD_USB</sub><br>3.3 V Nominal |      |

|-------------------|----------------------------------|-----|--------------------------------------|------|

| Parameter         |                                  | Min | Max                                  | Unit |

| Timing Requirem   | ents                             |     |                                      |      |

| f <sub>USBS</sub> | USB_XI Frequency                 | 24  | 24                                   | MHz  |

| fs <sub>USB</sub> | USB_XI Clock Frequency Stability | -50 | +50                                  | ppm  |

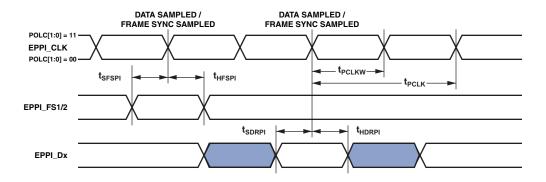

Figure 49. MSI Controller Timing

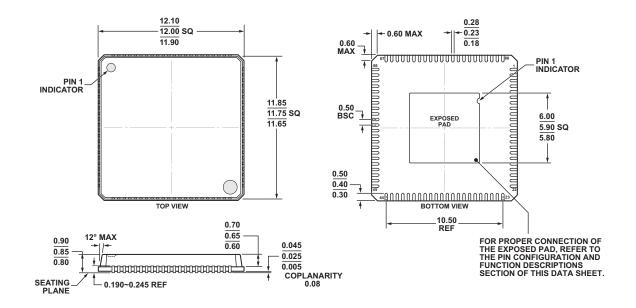

Dimensions for the 12 mm  $\times$  12 mm LFCSP\_VQ package in Figure 72 are shown in millimeters.

COMPLIANT TO JEDEC STANDARDS MO-220

Figure 72. 88-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] (CP-88-8) Dimensions shown in millimeters

### SURFACE-MOUNT DESIGN

Table 71 is provided as an aid to PCB design. For industry-<br/>standard design recommendations, refer to IPC-7351, Generic<br/>Requirements for Surface-Mount Design and Land Pattern<br/>Standard.

#### Table 71. CSP\_BGA Data for Use with Surface-Mount Design

| Package  | Package             | Package             | Package         |

|----------|---------------------|---------------------|-----------------|

|          | Ball Attach Type    | Solder Mask Opening | Ball Pad Size   |

| BC-184-1 | Solder Mask Defined | 0.4 mm Diameter     | 0.5 mm Diameter |

### PLANNED AUTOMOTIVE PRODUCTION PRODUCTS

|                          |                 |             | Temperature        |                     | Package  |

|--------------------------|-----------------|-------------|--------------------|---------------------|----------|

| Model <sup>1, 2, 3</sup> | Max. Core Clock | L2 SRAM     | Grade <sup>4</sup> | Package Description | Option   |

| ADBF702WCCPZ3xx          | 300 MHz         | 256K bytes  | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF702WCCPZ4xx          | 400 MHz         | 256K bytes  | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF703WCBCZ3xx          | 300 MHz         | 256K bytes  | –40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF703WCBCZ4xx          | 400 MHz         | 256K bytes  | –40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF704WCCPZ3xx          | 300 MHz         | 512K bytes  | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF704WCCPZ4xx          | 400 MHz         | 512K bytes  | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF705WCBCZ3xx          | 300 MHz         | 512K bytes  | –40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF705WCBCZ4xx          | 400 MHz         | 512K bytes  | –40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF706WCCPZ3xx          | 300 MHz         | 1024K bytes | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF706WCCPZ4xx          | 400 MHz         | 1024K bytes | –40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF707WCBCZ3xx          | 300 MHz         | 1024K bytes | –40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF707WCBCZ4xx          | 400 MHz         | 1024K bytes | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

<sup>1</sup> Select Automotive grade products, supporting  $-40^{\circ}$ C to  $+105^{\circ}$ C T<sub>AMBIENT</sub> condition, will be available when they appear in the Automotive Products table. <sup>2</sup> Z = RoHS Compliant Part.

$^3\,\rm xx$  denotes the current die revision.

<sup>4</sup> Referenced temperature is ambient temperature. The ambient temperature is not a specification. See Operating Conditions on Page 50 for the junction temperature (T<sub>j</sub>) specification which is the only temperature specification.