Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 512kB                                                                                     |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf705wcbcz311                       |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

output enable and the input enable of a GPIO pin are both active, the data signal before the pad driver is looped back to the receive path for the same GPIO pin.

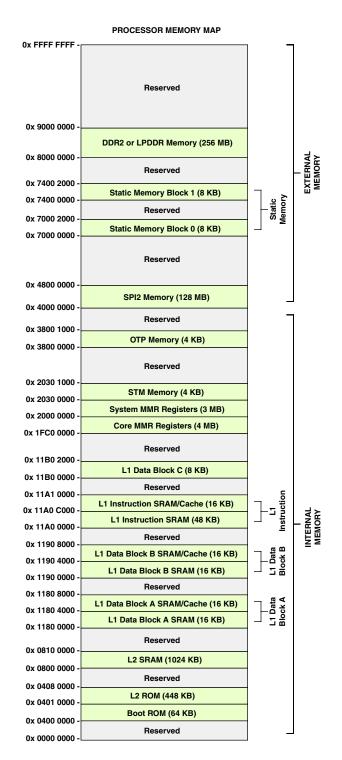

### MEMORY ARCHITECTURE

The processor views memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low-latency core-accessible memory as cache or SRAM, and larger, lower-cost and performance interface-accessible memory systems. See Figure 3.

#### Internal (Core-Accessible) Memory

The L1 memory system is the highest-performance memory available to the Blackfin+ processor core.

The core has its own private L1 memory. The modified Harvard architecture supports two concurrent 32-bit data accesses along with an instruction fetch at full processor speed which provides high-bandwidth processor performance. In the core, a 64K byte block of data memory partners with an 64K byte memory block for instruction storage. Each data block is multibanked for efficient data exchange through DMA and can be configured as SRAM. Alternatively, 16K bytes of each block can be configured in L1 cache mode. The four-way set-associative instruction cache and the 2 two-way set-associative data caches greatly accelerate memory access performance, especially when accessing external memories.

The L1 memory domain also features a 8K byte data SRAM block which is ideal for storing local variables and the software stack. All L1 memory is protected by a multi-parity-bit concept, regardless of whether the memory is operating in SRAM or cache mode.

Outside of the L1 domain, L2 and L3 memories are arranged using a Von Neumann topology. The L2 memory domain is a unified instruction and data memory and can hold any mixture of code and data required by the system design. The L2 memory domain is accessible by the Blackfin+ core through a dedicated 64-bit interface. It operates at SYSCLK frequency.

The processor features up to 1M byte of L2 SRAM, which is ECC-protected and organized in eight banks. Individual banks can be made private to any system master. There is also a 512K byte single-bank ROM in the L2 domain. It contains boot code, security code, and general-purpose ROM space.

#### **OTP Memory**

The processor features 4 kB of one-time-programmable (OTP) memory which is memory-map accessible. This memory stores a unique chip identification and is used to support secure-boot and secure operation.

Figure 3. ADSP-BF706/ADSP-BF707 Internal/External Memory Map

### Static Memory Controller (SMC)

The SMC can be programmed to control up to two blocks of external memories or memory-mapped devices, with very flexible timing parameters. Each block occupies a 8K byte segment regardless of the size of the device used.

### Dynamic Memory Controller (DMC)

The DMC includes a controller that supports JESD79-2E compatible double-data-rate (DDR2) SDRAM and JESD209A lowpower DDR (LPDDR) SDRAM devices. The DMC PHY features on-die termination on all data and data strobe pins that can be used during reads.

### I/O Memory Space

The processor does not define a separate I/O space. All resources are mapped through the flat 32-bit address space. Onchip I/O devices have their control registers mapped into memory-mapped registers (MMRs) at addresses in a region of the 4G byte address space. These are separated into two smaller blocks, one which contains the control MMRs for all core functions, and the other which contains the registers needed for setup and control of the on-chip peripherals outside of the core. The MMRs are accessible only in supervisor mode and appear as reserved space to on-chip peripherals.

### Booting

The processor has several mechanisms for automatically loading internal and external memory after a reset. The boot mode is defined by the SYS\_BMODE input pins dedicated for this purpose. There are two categories of boot modes. In master boot mode, the processor actively loads data from serial memories. In slave boot modes, the processor receives data from external host devices.

The boot modes are shown in Table 2. These modes are implemented by the SYS\_BMODE bits of the reset configuration register and are sampled during power-on resets and softwareinitiated resets.

#### Table 2. Boot Modes

| SYS_BMODE Setting | Boot Mode    |

|-------------------|--------------|

| 00                | No Boot/Idle |

| 01                | SPI2 Master  |

| 10                | SPI2 Slave   |

| 11                | UART0 Slave  |

### **SECURITY FEATURES**

The ADSP-BF70x processor supports standards-based hardware-accelerated encryption, decryption, authentication, and true random number generation. The following hardware-accelerated cryptographic ciphers are supported:

- AES in ECB, CBC, ICM, and CTR modes with 128-, 192-, and 256-bit keys

- DES in ECB and CBC mode with 56-bit key

- 3DES in ECB and CBC mode with 3x 56-bit key

The following hardware-accelerated hash functions are supported:

- SHA-1

- SHA-2 with 224-bit and 256-bit digest

- HMAC transforms for SHA-1 and SHA-2

Public key accelerator is available to offload computation-intensive public key cryptography operations.

Both a hardware-based nondeterministic random number generator and pseudo-random number generator are available. The TRNG also provides HW post-processing to meet NIST requirements of FIPS 140-2, while the PRNG is ANSI X9.31 compliant.

Secure boot is also available with 224-bit elliptic curve digital signatures ensuring integrity and authenticity of the boot stream. Optionally, confidentiality is also ensured through AES-128 encryption.

#### CAUTION

This product includes security features that can be used to protect embedded nonvolatile memory contents and prevent execution of unauthorized code. When security is enabled on this device (either by the ordering party or the subsequent receiving parties), the ability of Analog Devices to conduct failure analysis on returned devices is limited. Contact Analog Devices for details on the failure analysis limitations for this device.

Secure debug is also employed to allow only trusted users to access the system with debug tools.

### **PROCESSOR SAFETY FEATURES**

The ADSP-BF70x processor has been designed for functional safety applications. While the level of safety is mainly dominated by the system concept, the following primitives are provided by the devices to build a robust safety concept.

#### Multi-Parity-Bit-Protected L1 Memories

In the processor's L1 memory space, whether SRAM or cache, each word is protected by multiple parity bits to detect the single event upsets that occur in all RAMs. This applies both to L1 instruction and data memory spaces.

#### **ECC-Protected L2 Memories**

Error correcting codes (ECC) are used to correct single event upsets. The L2 memory is protected with a single error correctdouble error detect (SEC-DED) code. By default ECC is enabled, but it can be disabled on a per-bank basis. Single-bit errors are transparently corrected. Dual-bit errors can issue a

### Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

| Port Name   | Direction | Description                                                                                                                                                                          |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPT_BCLK    | I/O       | <b>Channel B Clock.</b> Data and Frame Sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                             |

| SPT_BD0     | I/O       | <b>Channel B Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                  |

| SPT_BD1     | I/O       | <b>Channel B Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                |

| SPT_BFS     | I/O       | <b>Channel B Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                       |

| SPT_BTDV    | Output    | <b>Channel B Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots.          |

| SYS_BMODEn  | Input     | Boot Mode Control n. Selects the boot mode of the processor.                                                                                                                         |

| SYS_CLKIN   | Input     | Clock/Crystal Input. Connect to an external clock source or crystal.                                                                                                                 |

| SYS_CLKOUT  | Output    | <b>Processor Clock Output.</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter of the HRM for more details.                                                 |

| SYS_EXTWAKE | Output    | <b>External Wake Control.</b> Drives low during hibernate and high all other times. Typically connected to the enable input of the voltage regulator controlling the VDD_INT supply. |

| SYS_FAULT   | I/O       | Active-Low Fault Output. Indicates internal faults or senses external faults depending on the operating mode.                                                                        |

| SYS_HWRST   | Input     | Processor Hardware Reset Control. Resets the device when asserted.                                                                                                                   |

| SYS_NMI     | Input     | Non-maskable Interrupt. See the processor hardware and programming references for more details.                                                                                      |

| SYS_RESOUT  | Output    | Reset Output. Indicates that the device is in the reset or hibernate state.                                                                                                          |

| SYS_WAKEn   | Input     | Power Saving Mode Wakeup n. Wake-up source input for deep sleep and/or hibernate mode.                                                                                               |

| SYS_XTAL    | Output    | <b>Crystal Output.</b> Drives an external crystal. Must be left unconnected if an external clock is driving CLKIN.                                                                   |

| JTG_SWCLK   | I/O       | Serial Wire Clock. Clocks data into and out of the target during debug.                                                                                                              |

| JTG_SWDIO   | I/O       | Serial Wire DIO. Sends and receives serial data to and from the target during debug.                                                                                                 |

| JTG_SWO     | Output    | Serial Wire Out. Provides trace data to the emulator.                                                                                                                                |

| JTG_TCK     | Input     | JTAG Clock. JTAG test access port clock.                                                                                                                                             |

| JTG_TDI     | Input     | JTAG Serial Data In. JTAG test access port data input.                                                                                                                               |

| JTG_TDO     | Output    | JTAG Serial Data Out. JTAG test access port data output.                                                                                                                             |

| JTG_TMS     | Input     | JTAG Mode Select. JTAG test access port mode select.                                                                                                                                 |

| JTG_TRST    | Input     | JTAG Reset. JTAG test access port reset.                                                                                                                                             |

| TM_ACIn     | Input     | Alternate Capture Input n. Provides an additional input for WIDCAP, WATCHDOG, and PININT modes.                                                                                      |

| TM_ACLKn    | Input     | Alternate Clock n. Provides an additional time base for use by an individual timer.                                                                                                  |

| TM_CLK      | Input     | <b>Clock.</b> Provides an additional global time base for use by all the GP timers.                                                                                                  |

| TM_TMRn     | I/O       | Timer n. The main input/output signal for each timer.                                                                                                                                |

| TRACE_CLK   | Output    | Trace Clock. Clock output.                                                                                                                                                           |

| TRACE_Dnn   | Output    | Trace Data n. Unidirectional data bus.                                                                                                                                               |

| TWI_SCL     | I/O       | Serial Clock. Clock output when master, clock input when slave.                                                                                                                      |

| TWI_SDA     | I/O       | Serial Data. Receives or transmits data.                                                                                                                                             |

| UART_CTS    | Input     | Clear to Send. Flow control signal.                                                                                                                                                  |

| UART_RTS    | Output    | Request to Send. Flow control signal.                                                                                                                                                |

| UART_RX     | Input     | <b>Receive.</b> Receive input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                     |

| UART_TX     | Output    | <b>Transmit.</b> Transmit output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                  |

| USB_CLKIN   | Input     | <b>Clock/Crystal Input.</b> This clock input is multiplied by a PLL to form the USB clock. See data sheet specifications for frequency/tolerance information.                        |

| Port Name | Direction | Description                                                                                                                                                                                                                                                                              |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_DM    | I/O       | Data –. Bidirectional differential data line.                                                                                                                                                                                                                                            |

| USB_DP    | I/O       | Data +. Bidirectional differential data line.                                                                                                                                                                                                                                            |

| USB_ID    | Input     | <b>OTG ID.</b> Senses whether the controller is a host or device. This signal is pulled low when an A-type plug is sensed (signifying that the USB controller is the A device), but the input is high when a B-type plug is sensed (signifying that the USB controller is the B device). |

| USB_VBC   | Output    | <b>VBUS Control.</b> Controls an external voltage source to supply VBUS when in host mode. May be configured as open-drain. Polarity is configurable as well.                                                                                                                            |

| USB_VBUS  | I/O       | Bus Voltage. Connects to bus voltage in host and device modes.                                                                                                                                                                                                                           |

| USB_XTAL  | Output    | <b>Crystal.</b> Drives an external crystal. Must be left unconnected if an external clock is driving USB_CLKIN.                                                                                                                                                                          |

### Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

#### Multiplexed Multiplexed Multiplexed Multiplexed Multiplexed Signal Name **Function 0 Function 1 Function 2** Function 3 Function Input Tap PC\_00 UART1\_TX SPT0\_AD1 PPI0\_D15 PC\_01 UART1\_RX SPT0\_BD1 PPI0\_D14 SMC0\_A09 TM0\_ACI4 PC\_02 UARTO\_RTS CAN0\_RX PPI0\_D13 SMC0\_A10 TM0\_ACI5/SYS\_ WAKE3 UARTO\_CTS PC\_03 CAN0\_TX PPI0\_D12 SMC0\_A11 TM0\_ACI0 PC\_04 SPT0\_BCLK SPI0\_CLK MSI0\_D1 SMC0\_A12 TM0\_ACLK0 SPT0\_AFS TM0\_TMR3 MSI0\_CMD PC\_05 PC\_06 SPT0\_BD0 SPI0\_MISO MSI0\_D3 SPI0\_MOSI MSI0\_D2 PC\_07 SPT0\_BFS TM0\_ACI2 MSI0\_D0 PC\_08 SPT0\_AD0 SPI0\_D2 SPI0\_D3 MSI0\_CLK PC\_09 SPT0\_ACLK TM0\_ACLK2 SPI1\_SEL3 PC\_10 SPT1\_BCLK MSI0\_D4 TM0\_ACLK1 SPI0\_SEL3 PC\_11 SPT1\_BFS MSI0\_D5 PC\_12 SPT1\_BD0 MSI0\_D6 PC\_13 SPT1\_BD1 MSI0\_D7 MSI0\_INT PC\_14 SPT1\_BTDV

#### Table 10. Signal Multiplexing for Port C

| Signal Name                      | Description                                                                   | Port   | Pin Name       |

|----------------------------------|-------------------------------------------------------------------------------|--------|----------------|

| SMC0_D11                         | SMC0 Data 11                                                                  | В      | PB_11          |

| SMC0_D12                         | SMC0 Data 12                                                                  | В      | PB_12          |

| SMC0_D13                         | SMC0 Data 13                                                                  | В      | PB_13          |

| SMC0_D14                         | SMC0 Data 14                                                                  | В      | PB_14          |

| SMC0_D15                         | SMC0 Data 15                                                                  | В      | PB_15          |

| SPI0_CLK                         | SPI0 Clock                                                                    | В      | PB_00          |

| SPI0_CLK                         | SPI0 Clock                                                                    | С      | PC_04          |

| SPI0_D2                          | SPI0 Data 2                                                                   | В      | PB_03          |

| SPI0_D2                          | SPI0 Data 2                                                                   | С      | PC_08          |

| SPI0_D3                          | SPI0 Data 3                                                                   | В      | PB_07          |

| SPI0_D3                          | SPI0 Data 3                                                                   | С      | PC_09          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                                     | В      | PB_01          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                                     | С      | PC_06          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                                     | В      | PB_02          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                                     | С      | PC_07          |

| SPI0_RDY                         | SPI0 Ready                                                                    | А      | PA_06          |

| SPI0_SEL1                        | SPI0 Slave Select Output 1                                                    | А      | PA_05          |

| SPI0_SEL2                        | SPI0 Slave Select Output 2                                                    | А      | PA_06          |

| SPI0_SEL4                        | SPI0 Slave Select Output 4                                                    | В      | PB_04          |

| SPI0_SEL5                        | SPI0 Slave Select Output 5                                                    | В      | PB_05          |

| SPI0_SEL6                        | SPI0 Slave Select Output 6                                                    | В      | PB_06          |

| SPI0_SS                          | SPI0 Slave Select Input                                                       | А      | PA_05          |

| SPI1_CLK                         | SPI1 Clock                                                                    | А      | PA_00          |

| SPI1_MISO                        | SPI1 Master In, Slave Out                                                     | А      | PA_01          |

| SPI1_MOSI                        | SPI1 Master Out, Slave In                                                     | А      | PA_02          |

|                                  | SPI1 Ready                                                                    | А      | <br>PA_03      |

| SPI1_SEL1                        | SPI1 Slave Select Output 1                                                    | А      | <br>PA_04      |

|                                  | SPI1 Slave Select Output 2                                                    | А      | <br>PA_03      |

|                                  | SPI1 Slave Select Output 3                                                    | с      | <br>PC_10      |

| SPI1_SEL4                        | SPI1 Slave Select Output 4                                                    | A      | PA_14          |

| SPI1_SS                          | SPI1 Slave Select Input                                                       | A      | PA_04          |

| SPI2_CLK                         | SPI2 Clock                                                                    | В      | PB_10          |

| SPI2_D2                          | SPI2 Data 2                                                                   | В      | PB_13          |

| SPI2_D3                          | SPI2 Data 3                                                                   | В      | PB_14          |

| SPI2_MISO                        | SPI2 Master In, Slave Out                                                     | В      | PB_11          |

| SPI2_MOSI                        | SPI2 Master Out, Slave In                                                     | В      | PB_12          |

| SPI2_RDY                         | SPI2 Ready                                                                    | A      | PA_04          |

| SPI2_SEL1                        | SPI2 Slave Select Output 1                                                    | В      | PB_15          |

| SPI2_SEL2                        | SPI2 Slave Select Output 1                                                    | В      | PB_08          |

| SPI2_SEL3                        | SPI2 Slave Select Output 2<br>SPI2 Slave Select Output 3                      | B      | PB_09          |

| SPI2_SELS                        | SPI2 Slave Select Output                                                      | B      | PB_15          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                                        | A      | PA_13          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                                        | C      | PC_09          |

| SPT0_ACLK<br>SPT0_AD0            | SPORTO Channel A Data 0                                                       |        | PC_09<br>PA_14 |

|                                  |                                                                               | A      |                |

|                                  |                                                                               |        |                |

| SPT0_AD0<br>SPT0_AD0<br>SPT0_AD1 | SPORTO Channel A Data 0<br>SPORTO Channel A Data 0<br>SPORTO Channel A Data 1 | C<br>C | PC_08<br>PC_00 |

Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                      |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_05       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Frame Sync   TM0<br>Timer 3   MSI0 Command<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                              |

| PC_06       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Data 0   SPl0<br>Master In, Slave Out   MSI0 Data 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                     |

| PC_07       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Frame Sync   SPI0<br>Master Out, Slave In   MSI0 Data 2   TM0<br>Alternate Capture Input 2<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                              |

| PC_08       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Data 0   SPI0 Data<br>2   MSI0 Data 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                   |

| PC_09       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Clock   SPI0 Data<br>3   MSI0 Clock   TM0 Alternate Clock 2<br>Notes: No notes.                                                                                                                                                                                          |

| PC_10       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Clock   MSI0 Data<br>4   SPI1 Slave Select Output 3   TM0<br>Alternate Clock 1<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used. |

| PC_11       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Frame Sync   MSI0<br>Data 5   SPI0 Slave Select Output 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used.                       |

| PC_12       | Ι/Ο  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 0   MSI0 Data<br>6<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                 |

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                      |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|-----------------------------------------------|

| VDD_OTP     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for OTP                             |

|             |      |                |             |               |                |               |                |                 | Notes: Must be powered.                       |

| VDD_RTC     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for RTC                             |

|             |      |                |             |               |                |               |                |                 | Notes: If RTC is not used, connect to ground. |

| VDD_USB     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for USB                             |

|             |      |                |             |               |                |               |                |                 | Notes: If USB is not used, connect to         |

|             |      |                |             |               |                |               |                |                 | VDD_EXT.                                      |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Parameter                                  |                                                             | <b>Test Conditions/Comments</b>                                                                                                                                                                                                                              | Min | Тур | Мах | Uni |

|--------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| I <sub>OZH_TWI</sub> <sup>14</sup>         | Three-State Leakage Current                                 | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V}, V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 5.5 \text{ V}$                                                                                                                                            |     |     | 10  | μΑ  |

| ADSP-BF701/                                | 703/705/707 Input Capacitance                               |                                                                                                                                                                                                                                                              |     |     |     |     |

| C <sub>IN</sub> (GPIO) <sup>15</sup>       | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 5.2 | 6.0 | pF  |

| C <sub>IN_TWI</sub> <sup>14</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.9 | 7.4 | pF  |

| C <sub>IN_DDR</sub> <sup>16</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.1 | 6.9 | pF  |

| ADSP-BF700/                                | 702/704/706 Input Capacitance                               | 1                                                                                                                                                                                                                                                            |     |     |     |     |

| C <sub>IN</sub> (GPIO) <sup>15</sup>       | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 5.0 | 5.3 | pF  |

| C <sub>IN_TWI</sub> <sup>14</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.8 | 7.4 | pF  |

| I <sub>DD_DEEPSLEEP</sub> <sup>17, 1</sup> | <sup>8</sup> V <sub>DD_INT</sub> Current in Deep Sleep Mode | Clocks disabled<br>T <sub>1</sub> = 25°C                                                                                                                                                                                                                     |     | 1.4 |     | mA  |

| I <sub>DD_IDLE</sub> <sup>18</sup>         | V <sub>DD_INT</sub> Current in Idle                         | $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 100 \text{ MHz}$ $ASF = 0.05 \text{ (idle)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_1 = 25^{\circ}C$                                   |     | 13  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 800 \text{ MHz}$ $f_{CCLK} = 400 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$                                             |     | 90  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $T_{J} = 25^{\circ}C$ $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 300 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_{J} = 25^{\circ}C$ |     | 66  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 400 \text{ MHz}$ $f_{CCLK} = 200 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_J = 25^{\circ}C$                         |     | 49  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 100 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_J = 25^{\circ}C$                         |     | 30  |     | mA  |

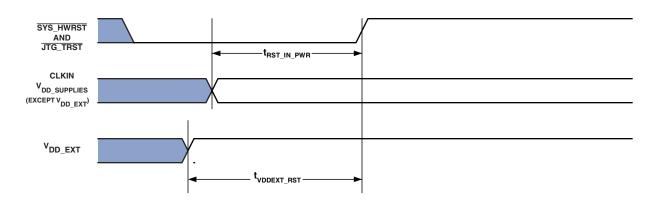

#### Power-Up Reset Timing

A power-up reset is required to place the processor in a known state after power-up. A power-up reset is initiated by asserting SYS\_HWRST and JTG\_TRST. During power-up reset, all pins are high impedance except for those noted in the ADSP-BF70x Designer Quick Reference on Page 38.

Both JTG\_TRST and SYS\_HWRST need to be asserted upon power-up, but only SYS\_HWRST needs to be released for the device to boot properly. JTG\_TRST may be asserted indefinitely for normal operation. JTG\_TRST only needs to be released when using an emulator to connect to the DAP for debug or boundary scan. There is an internal pull-down on JTG\_TRST to ensure internal emulation logic will always be properly initialized during power-up reset.

Table 30 and Figure 9 show the relationship between power supply startup and processor reset timing, related to the clock generation unit (CGU) and reset control unit (RCU). In Figure 9,  $V_{DD_{\_SUPPLIES}}$  are  $V_{DD_{\_INT}}$ ,  $V_{DD_{\_EXT}}$ ,  $V_{DD_{\_DMC}}$ ,  $V_{DD_{\_USB}}$ ,  $V_{DD_{\_CTC}}$ ,  $V_{DD_{\_OTP}}$ , and  $V_{DD_{\_HADC}}$ .

There is no power supply sequencing requirement for the ADSP-BF70x processor. However, if saving power during power-on is important, bringing up  $V_{DD_{INT}}$  last is recommended. This avoids a small current drain in the  $V_{DD_{INT}}$  domain during the transition period of I/O voltages from 0 V to within the voltage specification.

#### Table 30. Power-Up Reset Timing

| Paramete                | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Min                  | Max | Unit |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|

| Timing Red              | quirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |     |      |

| t <sub>rst_in_pwr</sub> | $\label{eq:starsest} \overrightarrow{SYS\_HWRST} and \end{system} \overrightarrow{JTG\_TRST} Deasserted \ After \ V_{DD\_INT}, \ V_{DD\_DMC}, \ V_{DD\_USB}, \\ V_{DD\_RTC}, \ V_{DD\_OTP}, \ V_{DD\_HADC}, \ and \ SYS\_CLKIN \ are \ Stable \ and \ Within \ Specification \ Note: \ System \ Syst$ | $11 \times t_{CKIN}$ |     | ns   |

| t <sub>VDDEXT_RST</sub> | SYS_HWRST Deasserted After V <sub>DD_EXT</sub> is Stable and Within Specifications (No External Pull-Down on JTG_TRST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                   |     | μs   |

| t <sub>vddext_rst</sub> | $\overline{SYS}_{HWRST}$ Deasserted After $V_{DD\_EXT}$ is Stable and Within Specifications (10k External Pull-Down on $\overline{JTG}_{TRST}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                    |     | μs   |

Figure 9. Power-Up Reset Timing

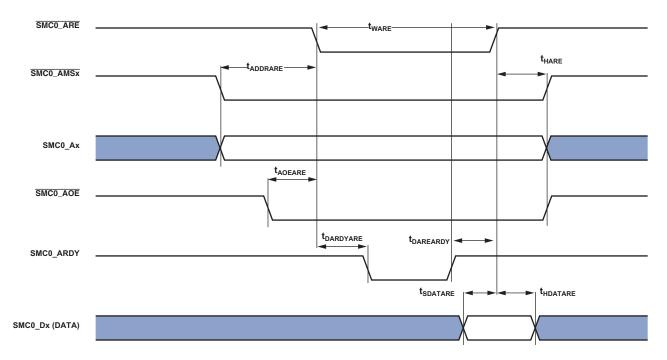

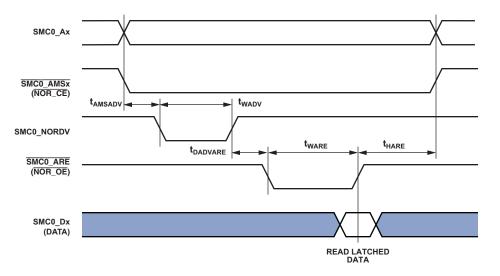

Figure 10. Asynchronous Read

#### Asynchronous Flash Read

Table 33 and Figure 12 show asynchronous flash memory read timing, related to the static memory controller (SMC).

#### Table 33. Asynchronous Flash Read

|                     |                                                                             | V <sub>DD_E</sub> )<br>1.8 V/3.3 V M |     |      |

|---------------------|-----------------------------------------------------------------------------|--------------------------------------|-----|------|

| Parameter           |                                                                             | Min                                  | Max | Unit |

| Switching C         | haracteristics                                                              |                                      |     |      |

| t <sub>amsadv</sub> | SMC0_Ax (Address)/SMC0_AMSx Assertion Before SMC0_NORDV<br>Low <sup>1</sup> | PREST × t <sub>SCLK0</sub> – 2       |     | ns   |

| t <sub>wadv</sub>   | SMC0_NORDV Active Low Width <sup>2</sup>                                    | $RST \times t_{SCLK0} - 2$           |     | ns   |

| DADVARE             | SMC0_ARE Low Delay From SMC0_NORDV High <sup>3</sup>                        | $PREAT \times t_{SCLK0} - 2$         |     | ns   |

| t <sub>HARE</sub>   | Output <sup>4</sup> Hold After SMC0_ARE High <sup>5</sup>                   | $RHT \times t_{SCLK0} - 2$           |     | ns   |

| t <sub>ware</sub> 6 | SMC0_ARE Active Low Width <sup>7</sup>                                      | $RAT \times t_{SCLK0} - 2$           |     | ns   |

<sup>1</sup> PREST value set using the SMC\_BxETIM.PREST bits.

<sup>2</sup> RST value set using the SMC\_BxTIM.RST bits.

<sup>3</sup> PREAT value set using the SMC\_BxETIM.PREAT bits.

<sup>4</sup>Output signals are SMC0\_Ax, <u>SMC0\_AMS</u>, <u>SMC0\_AOE</u>.

<sup>5</sup> RHT value set using the SMC\_BxTIM.RHT bits.

<sup>6</sup>SMC0\_BxCTL.ARDYEN bit = 0.

$^7\,\rm RAT$  value set using the SMC\_BxTIM.RAT bits.

Figure 12. Asynchronous Flash Read

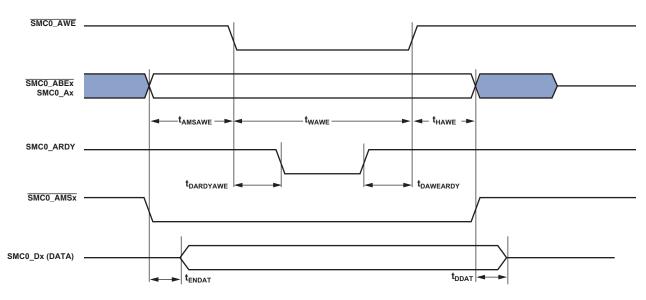

#### Asynchronous Write

Table 35 and Figure 14 show asynchronous memory write timing, related to the static memory controller (SMC).

#### Table 35. Asynchronous Memory Write (BxMODE = b#00)

|                                |                                                                 | V <sub>DD</sub><br>1.8V N                    | _ <sub>EXT</sub><br>ominal                 | V <sub>DD</sub><br>3.3 V No                  |                                            |      |

|--------------------------------|-----------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------|--------------------------------------------|------|

| Parameter                      | r                                                               | Min                                          | Max                                        | Min                                          | Max                                        | Unit |

| Timing Req                     | uirement                                                        |                                              |                                            |                                              |                                            |      |

| t <sub>DARDYAWE</sub> 1        | SMC0_ARDY Valid After<br>SMC0_AWE Low <sup>2</sup>              |                                              | (WAT – 2.5) ×<br>t <sub>SCLK0</sub> – 17.5 |                                              | (WAT – 2.5) ×<br>t <sub>SCLK0</sub> – 17.5 | ns   |

| Switching (                    | Characteristics                                                 |                                              |                                            |                                              |                                            |      |

| t <sub>endat</sub>             | DATA Enable After SMC0_AMSx<br>Assertion                        | -3                                           |                                            | -2                                           |                                            | ns   |

| t <sub>DDAT</sub>              | DATA Disable After <u>SMC0_AMSx</u><br>Deassertion              |                                              | 4.5                                        |                                              | 4                                          | ns   |

| t <sub>AMSAWE</sub>            | SMC0_Ax/SMC0_AMSx Assertion<br>Before SMC0_AWE Low <sup>3</sup> | $(PREST + WST + PREAT) \times t_{SCLK0} - 2$ |                                            | $(PREST + WST + PREAT) \times t_{SCLK0} - 4$ |                                            | ns   |

| t <sub>HAWE</sub>              | Output <sup>4</sup> Hold After <mark>SMC0_AWE</mark> High⁵      | $WHT \times t_{SCLK0}$                       |                                            | $WHT \times t_{SCLK0}$                       |                                            | ns   |

| t <sub>WAWE</sub> <sup>6</sup> | SMC0_AWE Active Low Width <sup>6</sup>                          | WAT $\times$ t <sub>SCLK0</sub> – 2          |                                            | WAT $\times$ t <sub>SCLK0</sub> – 2          |                                            | ns   |

| t <sub>DAWEARDY</sub> 1        | SMC0_AWE High Delay After<br>SMC0_ARDY Assertion                |                                              | $3.5 \times t_{SCLK0} + 17.5$              |                                              | $3.5 \times t_{SCLK0} + 17.5$              | ns   |

<sup>1</sup>SMC\_BxCTL.ARDYEN bit = 1.

$^2\,\rm WAT$  value set using the SMC\_BxTIM.WAT bits.

<sup>3</sup> PREST, WST, PREAT values set using the SMC\_BxETIM.PREST bits, SMC\_BxTIM.WST bits, SMC\_BxETIM.PREAT bits, and the SMC\_BxTIM.RAT bits.

<sup>4</sup> Output signals are DATA, SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_ABEx</u>.

<sup>5</sup> WHT value set using the SMC\_BxTIM.WHT bits.

<sup>6</sup>SMC\_BxCTL.ARDYEN bit = 0.

Figure 14. Asynchronous Write

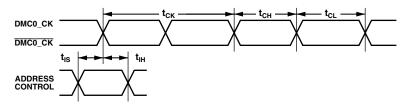

### DDR2 SDRAM Clock and Control Cycle Timing

Table 39 and Figure 17 show DDR2 SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

### Table 39. DDR2 SDRAM Read Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                 |                                                |      | 200 MHz |                 |

|-----------------|------------------------------------------------|------|---------|-----------------|

| Parameter       |                                                | Min  | Мах     | Unit            |

| Switching       | Characteristics                                |      |         |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |         | ns              |

| t <sub>CH</sub> | High Clock Pulse Width                         | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>CL</sub> | Low Clock Pulse Width                          | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 350  |         | ps              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMC0_CK Rise  | 475  |         | ps              |

NOTE: CONTROL = DMC0\_CS0, DMC0\_CKE, DMC0\_RAS, DMC0\_CAS, AND DMC0\_WE. ADDRESS = DMC0\_A00-13, AND DMC0\_BA0-2.

Figure 17. DDR2 SDRAM Clock and Control Cycle Timing

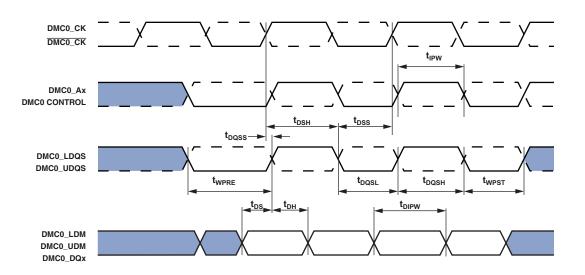

### DDR2 SDRAM Write Cycle Timing

Table 41 and Figure 19 show DDR2 SDRAM write cycle timing, related to the dynamic memory controller (DMC).

### Table 41. DDR2 SDRAM Write Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                                |                                                                | 200 MHz <sup>1</sup> |       |                 |

|--------------------------------|----------------------------------------------------------------|----------------------|-------|-----------------|

| Parameter                      |                                                                | Min                  | Max   | Unit            |

| Switching Chara                | cteristics                                                     |                      |       |                 |

| t <sub>DQSS</sub> <sup>2</sup> | DMC0_DQS Latching Rising Transitions to Associated Clock Edges | -0.25                | +0.25 | t <sub>CK</sub> |

| t <sub>DS</sub>                | Last Data Valid to DMC0_DQS Delay                              | 0.15                 |       | ns              |

| t <sub>DH</sub>                | DMC0_DQS to First Data Invalid Delay                           | 0.275                |       | ns              |

| t <sub>DSS</sub>               | DMC0_DQS Falling Edge to Clock Setup Time                      | 0.2                  |       | t <sub>CK</sub> |

| t <sub>DSH</sub>               | DMC0_DQS Falling Edge Hold Time From DMC0_CK                   | 0.2                  |       | t <sub>CK</sub> |

| t <sub>DQSH</sub>              | DMC0_DQS Output High Pulse Width                               | 0.35                 |       | t <sub>CK</sub> |

| t <sub>DQSL</sub>              | DMC0_DQS Output Low Pulse Width                                | 0.35                 |       | t <sub>CK</sub> |

| t <sub>WPRE</sub>              | Write Preamble                                                 | 0.35                 |       | t <sub>CK</sub> |

| t <sub>WPST</sub>              | Write Postamble                                                | 0.4                  |       | t <sub>CK</sub> |

| t <sub>IPW</sub>               | Address and Control Output Pulse Width                         | 0.6                  |       | t <sub>CK</sub> |

| t <sub>DIPW</sub>              | DMC0_DQ and DMC0_DM Output Pulse Width                         | 0.35                 |       | t <sub>CK</sub> |

<sup>1</sup>To ensure proper operation of the DDR2, all the DDR2 guidelines have to be strictly followed.

<sup>2</sup> Write command to first DMC0\_DQS delay = WL  $\times$  t<sub>CK</sub> + t<sub>DQSS</sub>.

Figure 19. DDR2 SDRAM Controller Output AC Timing

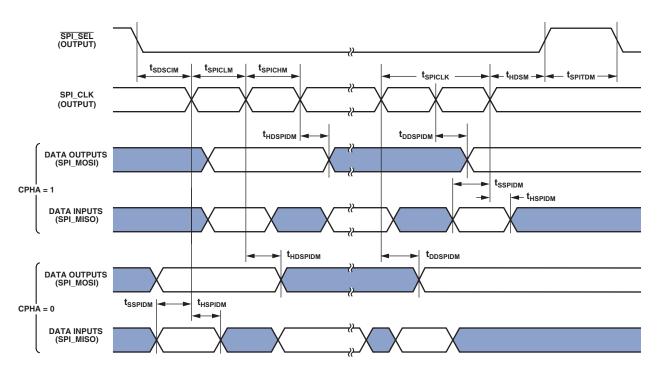

Figure 31. Serial Peripheral Interface (SPI) Port—Master Timing

Figure 32. Serial Peripheral Interface (SPI) Port—Slave Timing

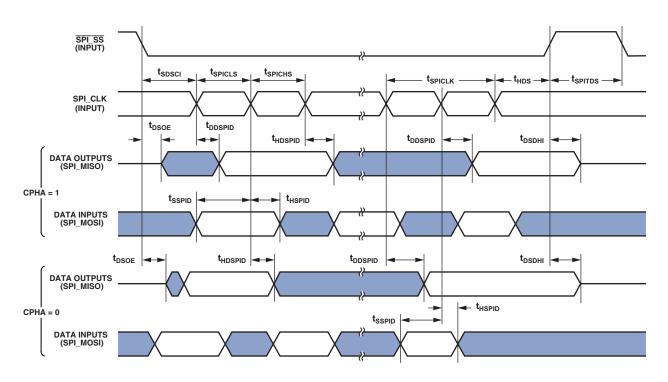

Figure 39. SPI\_CLK Switching Diagram after SPI\_RDY Assertion, CPHA = x

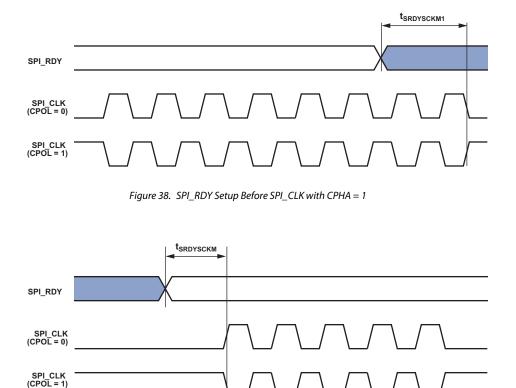

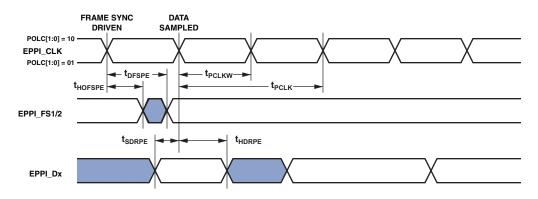

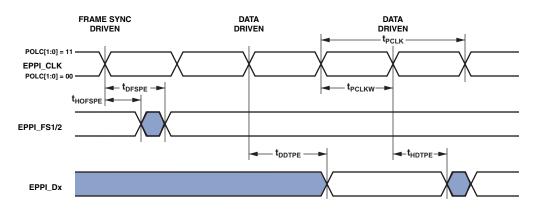

Figure 43. PPI Internal Clock GP Transmit Mode with External Frame Sync Timing

Figure 44. Clock Gating Mode with Internal Clock and External Frame Sync Timing

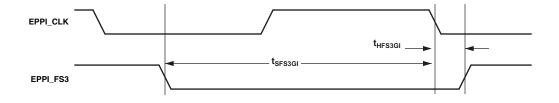

Table 61. Enhanced Parallel Peripheral Interface—External Clock

|                     |                                    | V <sub>DD_EXT</sub><br>1.8V Nominal |      | V <sub>DD_EXT</sub><br>3.3 V Nominal |      |      |

|---------------------|------------------------------------|-------------------------------------|------|--------------------------------------|------|------|

| Parameter           |                                    | Min                                 | Max  | Min                                  | Max  | Unit |

| Timing              | Requirements                       |                                     |      |                                      |      |      |

| t <sub>PCLKW</sub>  | EPPI_CLK Width <sup>1</sup>        | $(0.5 \times t_{PCLKEXT}) - 1$      |      | $(0.5 \times t_{PCLKEXT}) - 1$       |      | ns   |

| t <sub>PCLK</sub>   | EPPI_CLK Period <sup>1</sup>       | t <sub>PCLKEXT</sub> – 1            |      | t <sub>PCLKEXT</sub> – 1             |      | ns   |

| t <sub>SFSPE</sub>  | External FS Setup Before EPPI_CLK  | 1.5                                 |      | 1                                    |      | ns   |

| t <sub>HFSPE</sub>  | External FS Hold After EPPI_CLK    | 3.3                                 |      | 3                                    |      | ns   |

| t <sub>sdrpe</sub>  | Receive Data Setup Before EPPI_CLK | 1                                   |      | 1                                    |      | ns   |

| t <sub>HDRPE</sub>  | Receive Data Hold After EPPI_CLK   | 3                                   |      | 3                                    |      | ns   |

| Switchi             | ng Characteristics                 |                                     |      |                                      |      |      |

| t <sub>DFSPE</sub>  | Internal FS Delay After EPPI_CLK   |                                     | 17.5 |                                      | 14.5 | ns   |

| t <sub>HOFSPE</sub> | Internal FS Hold After EPPI_CLK    | 2.5                                 |      | 2.5                                  |      | ns   |

| t <sub>DDTPE</sub>  | Transmit Data Delay After EPPI_CLK |                                     | 17.5 |                                      | 14.5 | ns   |

| t <sub>HDTPE</sub>  | Transmit Data Hold After EPPI_CLK  | 2.5                                 |      | 2.5                                  |      | ns   |

<sup>1</sup>This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external EPPI\_CLK. For the external EPPI\_CLK ideal maximum frequency, see the f<sub>PCLKEXT</sub> specification in Table 18 on Page 52 in Clock Related Operating Conditions.

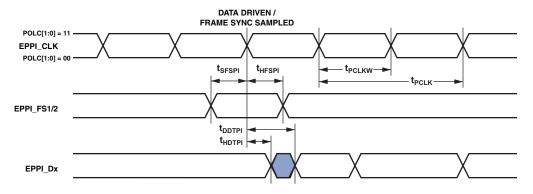

Figure 45. PPI External Clock GP Receive Mode with Internal Frame Sync Timing

Figure 46. PPI External Clock GP Transmit Mode with Internal Frame Sync Timing