# E·XFL

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

| Product Status          | Active                                                                                                 |

|-------------------------|--------------------------------------------------------------------------------------------------------|

| Туре                    | <sup>2</sup> lackfinC                                                                                  |

| Interface               | RAO, DSPI, E <sup>2</sup> I/E3 I, ICR, PPI, MSPI, SD/SDIN, SPI, SPNVT, UAVT/USAVT, US <sup>2</sup> NTG |

| Rlock Vate              | 1663 Hz                                                                                                |

| Oon-Bolatile 3 emory    | VN3 (825k <sup>2</sup> )                                                                               |

| Nn-Rhip VA3             | 23 <sup>2</sup>                                                                                        |

| Boltage - I/N           | 2.4B, °.°B                                                                                             |

| Boltage - Rore          | 2.26B                                                                                                  |

| Nperating Temperature   | -16-R: 268-R (TA)                                                                                      |

| 3 ounting Type          | Surface 3 ount                                                                                         |

| Package / Rase          | 44-BFMFO Exposed Pad, RSP                                                                              |

| Supplier Device Package | 44-LFRSP-BM (25x25)                                                                                    |

| Purchase UVL            | https@/www.e-xfl.com/product-detail/analog-devices/adbfX6Wwccpz122                                     |

|                         |                                                                                                        |

Email@info7 E-KFL.RN3

Address@Voom A, 2WF, Full V in Rommercial Rentre, 8X° Oathan Voad, 3 ongkok, Hong Wong

### TABLE OF CONTENTS

| General Description 3                                      |

|------------------------------------------------------------|

| Blackfin+ Processor Core 4                                 |

| Instruction Set Description 5                              |

| Processor Infrastructure 5                                 |

| Memory Architecture 7                                      |

| Security Features                                          |

| Processor Safety Features 8                                |

| Additional Processor Peripherals                           |

| Power and Clock Management 12                              |

| System Debug 15                                            |

| Development Tools 15                                       |

| Additional Information 16                                  |

| Related Signal Chains 16                                   |

| Security Features Disclaimer 17                            |

| ADSP-BF70x Detailed Signal Descriptions 18                 |

| 184-Ball CSP_BGA Signal Descriptions 22                    |

| GPIO Multiplexing for 184-Ball CSP_BGA 29                  |

| 12 mm × 12 mm 88-Lead LFCSP (QFN)<br>Signal Descriptions   |

| GPIO Multiplexing for 12 mm × 12 mm 88-Lead<br>LFCSP (QFN) |

### **REVISION HISTORY**

### 9/15—Rev. 0 to Rev. A

| Updated Processor Comparison           | 3   |

|----------------------------------------|-----|

| Updated Serial Ports (SPORTs)          | 10  |

| Updated Mobile Storage Interface (MSI) | 11  |

| Updated External Components for RTC    | 13  |

| Updated Development Tools              | 15  |

| Updated SPI Port—SPI_RDY Timing        | 92  |

| Added Models to Ordering Guide         | 116 |

| ADSP-BF70x Designer Quick Reference                                                             |

|-------------------------------------------------------------------------------------------------|

| Specifications 50                                                                               |

| Operating Conditions 50                                                                         |

| Electrical Characteristics 53                                                                   |

| HADC 58                                                                                         |

| Package Information 59                                                                          |

| Absolute Maximum Ratings 59                                                                     |

| ESD Sensitivity 59                                                                              |

| Timing Specifications                                                                           |

| Output Drive Currents 102                                                                       |

| Test Conditions 104                                                                             |

| Environmental Conditions 106                                                                    |

| ADSP-BF70x 184-Ball CSP_BGA Ball Assignments<br>(Numerical by Ball Number) 107                  |

| ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN)<br>Lead Assignments (Numerical by Lead Number) 110 |

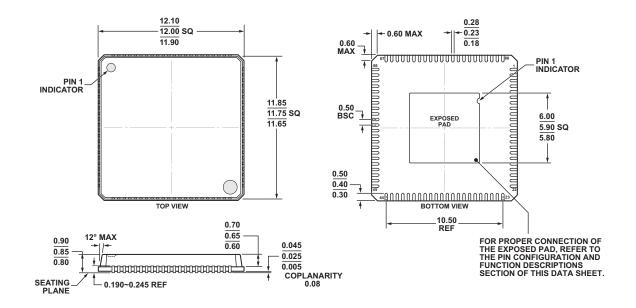

| Outline Dimensions 113                                                                          |

| Surface-Mount Design 114                                                                        |

| Planned Automotive Production Products 115                                                      |

| Ordering Guide 116                                                                              |

### **GENERAL DESCRIPTION**

The ADSP-BF70x processor is a member of the Blackfin<sup>®</sup> family of products. The Blackfin processor combines a dual-MAC 16-bit state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture. New enhancements to the Blackfin+ core add 32-bit MAC and 16-bit complex MAC support, cache enhancements, branch prediction and other instruction set improvements—all while maintaining instruction set compatibility to previous Blackfin products. The processor offers performance up to 400 MHz, as well as low static power consumption. Produced with a low-power and low-voltage design methodology, they provide world-class power management and performance.

By integrating a rich set of industry-leading system peripherals and memory (shown in Table 1), the Blackfin processor is the platform of choice for next-generation applications that require RISC-like programmability, multimedia support, and leadingedge signal processing in one integrated package. These applications span a wide array of markets, from automotive systems to embedded industrial, instrumentation, video/image analysis, biometric and power/motor control applications.

#### Table 1. Processor Comparison

| D                | ocessor Feature                                            | ADSP-   | ADSP-        | ADSP-   | ADSP-    | ADSP-<br>BF704 | ADSP-        | ADSP-   | ADSP-    |  |

|------------------|------------------------------------------------------------|---------|--------------|---------|----------|----------------|--------------|---------|----------|--|

|                  |                                                            | BF700   | <b>BF701</b> | BF702   | BF703    |                | <b>BF705</b> | BF706   | BF707    |  |

|                  | ximum Speed Grade (MHz) <sup>1</sup><br>ximum SYSCLK (MHz) |         | 00           |         |          | 00             |              |         |          |  |

|                  |                                                            | 88-Lead | 184-Ball     | 88-Lead | 184-Ball | 2<br>88-Lead   | 184-Ball     | 88-Lead | 184-Ball |  |

| Pd               | ckage Options                                              | LFCSP   | CSP_BGA      | LFCSP   | CSP_BGA  | LFCSP          | CSP_BGA      | LFCSP   | CSP_BGA  |  |

| GP               | IOs                                                        | 43      | 47           | 43      | 47       | 43             | 47           | 43      | 47       |  |

|                  | L1 Instruction SRAM                                        |         | •            |         | 48       | 3K             | •            |         | •        |  |

| _                | L1 Instruction SRAM/Cache                                  |         |              |         | 16       | 5K             |              |         |          |  |

| Memory (bytes)   | L1 Data SRAM                                               |         |              |         | 32       | 2K             |              |         |          |  |

| (d)              | L1 Data SRAM/Cache                                         |         |              |         | 32       | 2K             |              |         |          |  |

| (Jor             | L1 Scratchpad (L1 Data C)                                  |         |              |         | 8        | К              |              |         |          |  |

| Aem              | L2 SRAM                                                    | 12      | 28K          | 25      | 6K       | 51             | 2K           | 10      | 24K      |  |

| 2                | L2 ROM                                                     |         |              |         | 51       | 2K             |              |         |          |  |

|                  | DDR2/LPDDR (16-bit)                                        | No      | Yes          | No      | Yes      | No             | Yes          | No      | Yes      |  |

| I <sup>2</sup> C |                                                            |         |              |         |          | 1              |              |         |          |  |

| Up               | /Down/Rotary Counter                                       | 1       |              |         |          |                |              |         |          |  |

| GP               | Timer                                                      | 8       |              |         |          |                |              |         |          |  |

| Wa               | itchdog Timer                                              | 1       |              |         |          |                |              |         |          |  |

| GP               | Counter                                                    | 1       |              |         |          |                |              |         |          |  |

| SP               | ORTs                                                       | 2       |              |         |          |                |              |         |          |  |

| Qı               | ad SPI                                                     |         |              |         |          | 2              |              |         |          |  |

| Du               | al SPI                                                     |         |              |         |          | 1              |              |         |          |  |

| SP               | Host Port                                                  |         |              |         |          | 1              |              |         |          |  |

| US               | B 2.0 HS OTG                                               | 1       |              |         |          |                |              |         |          |  |

| Pa               | rallel Peripheral Interface                                | 1       |              |         |          |                |              |         |          |  |

| CA               | Ν                                                          | 2       |              |         |          |                |              |         |          |  |

| UA               | RT                                                         | 2       |              |         |          |                |              |         |          |  |

| Real-Time Clock  |                                                            | 1       |              |         |          |                |              |         |          |  |

|                  | tic Memory Controller (SMC)                                | Yes     |              |         |          |                |              |         |          |  |

| Se               | curity Crypto Engine                                       | Yes     |              |         |          |                |              |         |          |  |

| SD               | /SDIO (MSI)                                                | 4-bit   | 8-bit        | 4-bit   | 8-bit    | 4-bit          | 8-bit        | 4-bit   | 8-bit    |  |

| 4-(              | Channel 12-Bit ADC                                         | No      | Yes          | No      | Yes      | No             | Yes          | No      | Yes      |  |

<sup>1</sup>Other speed grades available.

The program sequencer controls the flow of instruction execution, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with dynamic branch prediction), and subroutine calls. Hardware supports zero-overhead looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.

The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering), and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).

The Blackfin processor supports a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories are those that typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The data memory holds data, and a dedicated scratchpad data memory stores stack and local variable information.

In addition, multiple L1 memory blocks are provided, offering a configurable mix of SRAM and cache. The memory management unit (MMU) provides memory protection for individual tasks that may be operating on the core and can protect system registers from unintended access.

The architecture provides three modes of operation: user mode, supervisor mode, and emulation mode. User mode has restricted access to certain system resources, thus providing a protected software environment, while supervisor mode has unrestricted access to the system and core resources.

### INSTRUCTION SET DESCRIPTION

The Blackfin processor instruction set has been optimized so that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. The Blackfin processor supports a limited multi-issue capability, where a 32-bit instruction can be issued in parallel with two 16-bit instructions, allowing the programmer to use many of the core resources in a single instruction cycle.

The Blackfin processor family assembly language instruction set employs an algebraic syntax designed for ease of coding and readability. The instructions have been specifically tuned to provide a flexible, densely encoded instruction set that compiles to a very small final memory size. The instruction set also provides fully featured multifunction instructions that allow the programmer to use many of the processor core resources in a single instruction. Coupled with many features more often seen on microcontrollers, this instruction set is very efficient when compiling C and C++ source code. In addition, the architecture supports both user (algorithm/application code) and supervisor (O/S kernel, device drivers, debuggers, ISRs) modes of operation, allowing multiple levels of access to core processor resources. The assembly language, which takes advantage of the processor's unique architecture, offers the following advantages:

- Seamlessly integrated DSP/MCU features are optimized for both 8-bit and 16-bit operations.

- A multi-issue load/store modified-Harvard architecture, which supports two 16-bit MAC or four 8-bit ALU + two load/store + two pointer updates per cycle.

- All registers, I/O, and memory are mapped into a unified 4G byte memory space, providing a simplified programming model.

- Control of all asynchronous and synchronous events to the processor is handled by two subsystems: the core event controller (CEC) and the system event controller (SEC).

- Microcontroller features, such as arbitrary bit and bit-field manipulation, insertion, and extraction; integer operations on 8-, 16-, and 32-bit data-types; and separate user and supervisor stack pointers.

- Code density enhancements, which include intermixing of 16-bit and 32-bit instructions (no mode switching, no code segregation). Frequently used instructions are encoded in 16 bits.

### PROCESSOR INFRASTRUCTURE

The following sections provide information on the primary infrastructure components of the ADSP-BF70x processor.

### **DMA Controllers**

The processor uses direct memory access (DMA) to transfer data within memory spaces or between a memory space and a peripheral. The processor can specify data transfer operations and return to normal processing while the fully integrated DMA controller carries out the data transfers independent of processor activity.

DMA transfers can occur between memory and a peripheral or between one memory and another memory. Each memory-tomemory DMA stream uses two channels, where one channel is the source channel, and the second is the destination channel.

All DMAs can transport data to and from all on-chip and offchip memories. Programs can use two types of DMA transfers, descriptor-based or register-based. Register-based DMA allows the processor to directly program DMA control registers to initiate a DMA transfer. On completion, the control registers may be automatically updated with their original setup values for continuous transfer. Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. Descriptor-based DMA transfers allow multiple DMA sequences to be chained together and a DMA channel can be programmed to automatically set up and start another DMA transfer after the current sequence completes.

The DMA controller supports the following DMA operations.

- A single linear buffer that stops on completion.

- A linear buffer with negative, positive, or zero stride length.

- A circular, auto-refreshing buffer that interrupts when each buffer becomes full.

#### **General-Purpose Timers**

There is one GP timer unit, and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TIMER\_TMRx pins, an external TIMER\_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The GP timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals through the TRU (for instance, to signal a fault). Each timer may also be started and/or stopped by any TRU master without core intervention.

#### **Core Timer**

The processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### Watchdog Timer

The core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, through generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts down to zero from the programmed value. This protects the system from remaining in an unknown state where software that would normally reset the timer has stopped running due to an external noise condition or software error.

After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in its timer control register that is set only upon a watchdog-generated reset.

### Serial Ports (SPORTs)

Two synchronous serial ports (comprised of four half-SPORTs) provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices' audio codecs, ADCs, and DACs. Each half-SPORT is made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial port data can be automatically transferred to and from on-chip memory/external memory through dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. In this configuration, one SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in six modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- Left-justified mode

- Right-justified mode

#### **General-Purpose Counters**

A 32-bit counter is provided that can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is either controlled by a levelsensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumbwheel devices. All three pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable this timer to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmed count values are exceeded.

#### Parallel Peripheral Interface (PPI)

The processor provides a parallel peripheral interface (PPI) that supports data widths up to 18 bits. The PPI supports direct connection to TFT LCD panels, parallel analog-to-digital and digital-to-analog converters, video encoders and decoders, image sensor modules, and other general-purpose peripherals.

The following features are supported in the PPI module:

- Programmable data length: 8 bits, 10 bits, 12 bits, 14 bits, 16 bits, and 18 bits per clock.

- Various framed, non-framed, and general-purpose operating modes. Frame syncs can be generated internally or can be supplied by an external device.

- ITU-656 status word error detection and correction for ITU-656 receive modes and ITU-656 preamble and status word decode.

- Optional packing and unpacking of data to/from 32 bits from/to 8 bits, 16 bits and 24 bits. If packing/unpacking is enabled, endianness can be configured to change the order of packing/unpacking of bytes/words.

- RGB888 can be converted to RGB666 or RGB565 for transmit modes.

- Various de-interleaving/interleaving modes for receiving/transmitting 4:2:2 YCrCb data.

- Configurable LCD data enable (DEN) output available on Frame Sync 3.

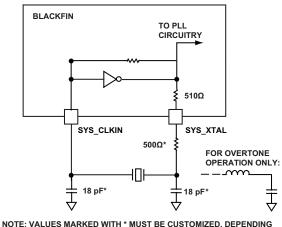

level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations on multiple devices over the required temperature range.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18pF SHOULD BE TREATED AS A MAXIMUM.

Figure 4. External Crystal Connection

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone by adding a tuned inductor circuit as shown in Figure 4. A design procedure for third-overtone operation is discussed in detail in application note (EE-168) *Using Third Overtone Crystals with the ADSP-218x DSP* (www.analog.com/ee-168).

The same recommendations may be used for the USB crystal oscillator.

#### **Real-Time Clock**

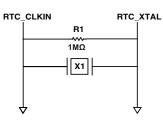

The real-time clock (RTC) provides a robust set of digital watch features, including current time, stopwatch, and alarm. The RTC is clocked by a 32.768 kHz crystal external to the processor. Connect RTC pins RTC\_CLKIN and RTC\_XTAL with external components as shown in Figure 5.

The RTC peripheral has dedicated power supply pins so that it can remain powered up and clocked even when the rest of the processor is in a low power state. The RTC provides several programmable interrupt options, including interrupt per second, minute, hour, or day clock ticks, interrupt on programmable stopwatch countdown, or interrupt at a programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60-second counter, a 60-minute counter, a 24-hour counter, and a 32,768-day counter. When the alarm interrupt is enabled, the alarm function generates an interrupt when the output of the timer matches the programmed value in the alarm control register. There are two alarms. The first alarm is for a time of day. The second alarm is for a specific day and time of that day.

NOTE: CRYSTAL LOAD CAPACITORS ARE NOT NECESSARY IN MOST CASES.

Figure 5. External Components for RTC

The stopwatch function counts down from a programmed value, with one-second resolution. When the stopwatch interrupt is enabled and the counter underflows, an interrupt is generated.

#### **Clock Generation**

The clock generation unit (CGU) generates all on-chip clocks and synchronization signals. Multiplication factors are programmed to define the PLLCLK frequency. Programmable values divide the PLLCLK frequency to generate the core clock (CCLK), the system clocks (SYSCLK, SCLK0, and SCLK1), the LPDDR or DDR2 clock (DCLK), and the output clock (OCLK).

Writing to the CGU control registers does not affect the behavior of the PLL immediately. Registers are first programmed with a new value, and the PLL logic executes the changes so that it transitions smoothly from the current conditions to the new ones.

SYS\_CLKIN oscillations start when power is applied to the VDD\_EXT pins. The rising edge of SYS\_HWRST can be applied after all voltage supplies are within specifications, and SYS\_CLKIN oscillations are stable.

### Clock Out/External Clock

The SYS\_CLKOUT output pin has programmable options to output divided-down versions of the on-chip clocks. By default, the SYS\_CLKOUT pin drives a buffered version of the SYS\_ CLKIN input. Clock generation faults (for example, PLL unlock) may trigger a reset by hardware. The clocks shown in Table 3 can be output on the SYS\_CLKOUT pin.

### **ADSP-BF70x DETAILED SIGNAL DESCRIPTIONS**

Table 6 provides a detailed description of each pin.

#### Table 6. ADSP-BF70x Detailed Signal Descriptions

| Port Name | Direction | Description                                                                                                                                                                                                                                                              |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN_RX    | Input     | Receive. Typically an external CAN transceiver's RX output.                                                                                                                                                                                                              |

| CAN_TX    | Output    | Transmit. Typically an external CAN transceiver's TX input.                                                                                                                                                                                                              |

| CNT_DG    | Input     | <b>Count Down and Gate.</b> Depending on the mode of operation this input acts either as a count down signal or a gate signal Count Down - This input causes the GP counter to decrement Gate - Stops the GP counter from incrementing or decrementing.                  |

| CNT_UD    | Input     | <b>Count Up and Direction.</b> Depending on the mode of operation this input acts either as a count up signal or a direction signal Count Up - This input causes the GP counter to increment Direction - Selects whether the GP counter is incrementing or decrementing. |

| CNT_ZM    | Input     | <b>Count Zero Marker.</b> Input that connects to the zero marker output of a rotary device or detects the pressing of a pushbutton.                                                                                                                                      |

| DMC_Ann   | Output    | Address n. Address bus.                                                                                                                                                                                                                                                  |

| DMC_BAn   | Output    | Bank Address Input n. Defines which internal bank an ACTIVATE, READ, WRITE, or PRECHARGE                                                                                                                                                                                 |

| Dime_DAin | output    | command is being applied to on the dynamic memory. Also defines which mode registers (MR, EMR, EMR2, and/or EMR3) are loaded during the LOAD MODE REGISTER command.                                                                                                      |

| DMC_CAS   | Output    | <b>Column Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the CAS input of dynamic memory.                                                                                    |

| DMC_CK    | Output    | Clock. Outputs DCLK to external dynamic memory.                                                                                                                                                                                                                          |

| DMC_CK    | Output    | Clock (Complement). Complement of DMC_CK.                                                                                                                                                                                                                                |

| DMC_CKE   | Output    | Clock enable. Active high clock enables. Connects to the dynamic memory's CKE input.                                                                                                                                                                                     |

| DMC_CSn   | Output    | Chip Select n. Commands are recognized by the memory only when this signal is asserted.                                                                                                                                                                                  |

| DMC_DQnn  | I/O       | Data n. Bidirectional Data bus.                                                                                                                                                                                                                                          |

| DMC_LDM   | Output    | <b>Data Mask for Lower Byte.</b> Mask for DMC_DQ07:DMC_DQ00 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_LDQS  | I/O       | <b>Data Strobe for Lower Byte.</b> DMC_DQ07:DMC_DQ00 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_LDQS  | I/O       | Data Strobe for Lower Byte (complement). Complement of LDQS. Not used in single-ended mode.                                                                                                                                                                              |

| DMC_ODT   | Output    | <b>On-die termination.</b> Enables dynamic memory termination resistances when driven high (assuming the memory is properly configured). ODT is enabled/disabled regardless of read or write commands.                                                                   |

| DMC_RAS   | Output    | <b>Row Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the RAS input of dynamic memory.                                                                                       |

| DMC_UDM   | Output    | <b>Data Mask for Upper Byte.</b> Mask for DMC_DQ15:DMC_DQ08 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_UDQS  | I/O       | <b>Data Strobe for Upper Byte.</b> DMC_DQ15:DMC_DQ08 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_UDQS  | I/O       | Data Strobe for Upper Byte (complement). Complement of UDQSb. Not used in single-ended mode.                                                                                                                                                                             |

| DMC_VREF  | Input     | Voltage Reference. Connect to half of the VDD_DMC voltage.                                                                                                                                                                                                               |

| DMC_WE    | Output    | Write Enable. Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the WE input of dynamic memory.                                                                                                     |

| PPI_CLK   | I/O       | <b>Clock.</b> Input in external clock mode, output in internal clock mode.                                                                                                                                                                                               |

| PPI_Dnn   | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                          |

| PPI_FS1   | I/O       | Frame Sync 1 (HSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS2   | I/O       | Frame Sync 2 (VSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS3   | I/O       | Frame Sync 3 (FIELD). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| HADC_VINn | Input     | <b>Analog Input at channel n.</b> Analog voltage inputs for digital conversion.                                                                                                                                                                                          |

| Signal Name | Description                | Port | Pin Name |

|-------------|----------------------------|------|----------|

| SMC0_ARE    | SMC0 Read Enable           | A    | PA_13    |

| SMC0_AWE    | SMC0 Write Enable          | A    | PA_14    |

| SMC0_D00    | SMC0 Data 0                | В    | PB_07    |

| SMC0_D01    | SMC0 Data 1                | В    | PB_06    |

| SMC0_D02    | SMC0 Data 2                | В    | PB_05    |

| SMC0_D03    | SMC0 Data 3                | В    | PB_04    |

| SMC0_D04    | SMC0 Data 4                | В    | PB_03    |

| SMC0_D05    | SMC0 Data 5                | В    | PB_02    |

| SMC0_D06    | SMC0 Data 6                | В    | PB_01    |

| SMC0_D07    | SMC0 Data 7                | В    | PB_00    |

| SMC0_D08    | SMC0 Data 8                | В    | PB_08    |

| SMC0_D09    | SMC0 Data 9                | В    | PB_09    |

| SMC0_D10    | SMC0 Data 10               | В    | PB_10    |

| SMC0_D11    | SMC0 Data 11               | В    | PB_11    |

| SMC0_D12    | SMC0 Data 12               | В    | PB_12    |

| SMC0_D13    | SMC0 Data 13               | В    | PB_13    |

| SMC0_D14    | SMC0 Data 14               | В    | PB_14    |

| SMC0_D15    | SMC0 Data 15               | В    | PB_15    |

| SPI0_CLK    | SPI0 Clock                 | В    | PB_00    |

| SPI0_CLK    | SPI0 Clock                 | С    | PC_04    |

| SPI0_D2     | SPI0 Data 2                | В    | PB_03    |

| SPI0_D2     | SPI0 Data 2                | С    | PC_08    |

| SPI0_D3     | SPI0 Data 3                | В    | PB_07    |

| SPI0_D3     | SPI0 Data 3                | С    | PC_09    |

| SPI0_MISO   | SPI0 Master In, Slave Out  | В    | PB_01    |

| SPI0_MISO   | SPI0 Master In, Slave Out  | С    | PC_06    |

| SPI0_MOSI   | SPI0 Master Out, Slave In  | В    | PB_02    |

| SPI0_MOSI   | SPI0 Master Out, Slave In  | С    | PC_07    |

| SPI0_RDY    | SPI0 Ready                 | A    | PA_06    |

| SPI0_SEL1   | SPI0 Slave Select Output 1 | A    | PA_05    |

| SPI0_SEL2   | SPI0 Slave Select Output 2 | A    | PA_06    |

| SPI0_SEL3   | SPI0 Slave Select Output 3 | С    | PC_11    |

| SPI0_SEL4   | SPI0 Slave Select Output 4 | В    | PB_04    |

| SPI0_SEL5   | SPI0 Slave Select Output 5 | В    | PB_05    |

| SPI0_SEL6   | SPI0 Slave Select Output 6 | В    | PB_06    |

| SPI0_SS     | SPI0 Slave Select Input    | А    | PA_05    |

| SPI1_CLK    | SPI1 Clock                 | А    | PA_00    |

| SPI1_MISO   | SPI1 Master In, Slave Out  | А    | PA_01    |

| SPI1_MOSI   | SPI1 Master Out, Slave In  | А    | PA_02    |

| SPI1_RDY    | SPI1 Ready                 | А    | PA_03    |

| SPI1_SEL1   | SPI1 Slave Select Output 1 | А    | PA_04    |

| SPI1_SEL2   | SPI1 Slave Select Output 2 | А    | PA_03    |

| SPI1_SEL3   | SPI1 Slave Select Output 3 | С    | PC_10    |

| SPI1_SEL4   | SPI1 Slave Select Output 4 | А    | PA_14    |

| SPI1_SS     | SPI1 Slave Select Input    | А    | PA_04    |

| SPI2_CLK    | SPI2 Clock                 | В    | PB_10    |

### Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

### 12 mm × 12 mm 88-LEAD LFCSP (QFN) SIGNAL DESCRIPTIONS

The processor's pin definitions are shown in Table 11. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

#### Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions

| Signal Name | Description                     | Port      | Pin Name      |

|-------------|---------------------------------|-----------|---------------|

| CAN0_RX     | CAN0 Receive                    | С         | PC_02         |

| CAN0_TX     | CAN0 Transmit                   | С         | PC_03         |

| CAN1_RX     | CAN1 Receive                    | A         | PA_12         |

| CAN1_TX     | CAN1 Transmit                   | A         | PA_13         |

| CNT0_DG     | CNT0 Count Down and Gate        | A         | PA_07         |

| CNT0_UD     | CNT0 Count Up and Direction     | A         | PA_15         |

| CNT0_ZM     | CNT0 Count Zero Marker          | A         | PA_13         |

| GND         | Ground                          | Not Muxed | GND           |

| JTG_SWCLK   | TAPC0 Serial Wire Clock         | Not Muxed | JTG_TCK_SWCLK |

| JTG_SWDIO   | TAPC0 Serial Wire DIO           | Not Muxed | JTG_TMS_SWDIO |

| JTG_SWO     | TAPC0 Serial Wire Out           | Not Muxed | JTG_TDO_SWO   |

| JTG_TCK     | TAPC0 JTAG Clock                | Not Muxed | JTG_TCK_SWCLK |

| JTG_TDI     | TAPC0 JTAG Serial Data In       | Not Muxed | JTG_TDI       |

| JTG_TDO     | TAPC0 JTAG Serial Data Out      | Not Muxed | JTG_TDO_SWO   |

| JTG_TMS     | TAPC0 JTAG Mode Select          | Not Muxed | JTG_TMS_SWDIO |

| JTG_TRST    | TAPC0 JTAG Reset                | Not Muxed | JTG_TRST      |

| MSI0_CD     | MSI0 Card Detect                | A         | PA_08         |

| MSI0_CLK    | MSI0 Clock                      | С         | PC_09         |

| MSI0_CMD    | MSI0 Command                    | С         | PC_05         |

| MSI0_D0     | MSI0 Data 0                     | С         | PC_08         |

| MSI0_D1     | MSI0 Data 1                     | С         | PC_04         |

| MSI0_D2     | MSI0 Data 2                     | С         | PC_07         |

| MSI0_D3     | MSI0 Data 3                     | С         | PC_06         |

| MSI0_D4     | MSI0 Data 4                     | С         | PC_10         |

| PA_00-PA_15 | Position 00 through Position 15 | A         | PA_00-PA_15   |

| PB_00-PB_15 | Position 00 through Position 15 | В         | PB_00-PB_15   |

| PC_00-PC_10 | Position 00 through Position 10 | С         | PC_00-PC_10   |

| PPI0_CLK    | EPPI0 Clock                     | A         | PA_14         |

| PPI0_D00    | EPPI0 Data 0                    | В         | PB_07         |

| PPI0_D01    | EPPI0 Data 1                    | В         | PB_06         |

| PPI0_D02    | EPPI0 Data 2                    | В         | PB_05         |

| PPI0_D03    | EPPI0 Data 3                    | В         | PB_04         |

| PPI0_D04    | EPPI0 Data 4                    | В         | PB_03         |

| PPI0_D05    | EPPI0 Data 5                    | В         | PB_02         |

| PPI0_D06    | EPPI0 Data 6                    | В         | PB_01         |

| PPI0_D07    | EPPIO Data 7                    | В         | PB_00         |

|             |      | Driver   | Int   | Reset | Reset | Hiber | Hiber | Power     | Description                                         |

|-------------|------|----------|-------|-------|-------|-------|-------|-----------|-----------------------------------------------------|

| Signal Name | Туре | Туре     | Term  | Term  | Drive | Term  | Drive | Domain    | and Notes                                           |

| DMC0_A06    | 1/0  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 6                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A07    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 7                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A08    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 8                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A09    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 9                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A10    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 10                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A11    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 11                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A12    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 12                               |

| DMC0 442    | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A13    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 13                               |

|             | 1/0  | <b>D</b> |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_BA0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 0<br>Notes: No notes. |

| DMC0_BA1    | I/O  | В        | nono  | nono  | nono  | nono  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 1                     |

| DIVICO_BAT  | 1/0  | D        | none  | none  | none  | none  | none  | VDD_DIVIC | Notes: No notes.                                    |

| DMC0_BA2    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 2                     |

| DIVICO_DIV2 | 1/0  |          | none  | none  | none  | none  | none  | VDD_DIMC  | Notes: For LPDDR, leave unconnected.                |

| DMC0_CAS    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Column Address Strobe                    |

| bineo_erio  | ., 0 |          | lione | none  | none  | none  | none  |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | с        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock                                    |

|             |      | -        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | С        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock (complement)                       |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CKE    | I/O  | В        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock enable                             |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CS0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Chip Select 0                            |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ00   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 0                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ01   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 1                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ02   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 2                                   |

|             | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ03   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 3                                   |

|             | 1/0  | D        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ04   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 4<br>Notes: No notes.               |

| DMC0_DQ05   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 5                                   |

|             | "0   |          | none  | none  | none  | none  | lione |           | Notes: No notes.                                    |

| DMC0_DQ06   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 6                                   |

| 2           |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ07   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 7                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

|                   | _    | Driver | Int<br>T | Reset | Reset | Hiber<br>- | Hiber | Power    | Description                                                                                                                                                  |

|-------------------|------|--------|----------|-------|-------|------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name       | Туре | Туре   | Term     | Term  | Drive | Term       | Drive | Domain   | and Notes                                                                                                                                                    |

| GND_HADC          | g    | na     | none     | none  | none  | none       | none  | na       | Desc: Ground HADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                                       |

| HADC0_VIN0        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel (<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VIN1        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel <sup>2</sup><br>Notes: If HADC is not used, connect to<br>ground.                                                        |

| HADC0_VIN2        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 2<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VIN3        | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 3<br>Notes: If HADC is not used, connect to<br>ground.                                                                   |

| HADC0_VREFN       | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 Ground Reference for<br>ADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                 |

| HADC0_VREFP       | a    | na     | none     | none  | none  | none       | none  | VDD_HADC | Desc: HADC0 External Reference for<br>ADC<br>Notes: If HADC is not used, connect to<br>ground.                                                               |

| JTG_TCK_<br>SWCLK | I/O  | na     | pd       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Clock   Serial Wire Clock<br>Notes: Functional during reset.                                                                                      |

| JTG_TDI           | I/O  | na     | pu       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Serial Data In<br>Notes: Functional during reset.                                                                                                 |

| JTG_TDO_SWO       | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Serial Data Out   Serial Wire<br>Out<br>Notes: Functional during reset, three-<br>state when JTG_TRST is asserted.                                |

| JTG_TMS_<br>SWDIO | I/O  | А      | pu       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Mode Select   Serial Wire DIC<br>Notes: Functional during reset.                                                                                  |

| JTG_TRST          | I/O  | na     | pd       | none  | none  | none       | none  | VDD_EXT  | Desc: JTAG Reset<br>Notes: Functional during reset, a 10k<br>external pull-down may be used to<br>shorten the t <sub>VDDEXT_RST</sub> timing<br>requirement. |

| PA_00             | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: SPI1 Clock   TRACE0 Trace Data 7<br>SMC0 Byte Enable 0<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.         |

| PA_01             | I/O  | A      | none     | none  | none  | none       | none  | VDD_EXT  | Desc: SPI1 Master In, Slave Out   TRACEC<br>Trace Data 6   SMC0 Byte Enable 1<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.         |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                      |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|-----------------------------------------------|

| VDD_OTP     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for OTP                             |

|             |      |                |             |               |                |               |                |                 | Notes: Must be powered.                       |

| VDD_RTC     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for RTC                             |

|             |      |                |             |               |                |               |                |                 | Notes: If RTC is not used, connect to ground. |

| VDD_USB     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for USB                             |

|             |      |                |             |               |                |               |                |                 | Notes: If USB is not used, connect to         |

|             |      |                |             |               |                |               |                |                 | VDD_EXT.                                      |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Parameter                                   |                                                     | Test Conditions/Comments                                                                                                                                                                                                          | Min | Тур | Max                                                     | Unit |

|---------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------|------|

| I <sub>DD_HIBERNATE</sub> <sup>17, 15</sup> | <sup>9</sup> Hibernate State Current                |                                                                                                                                                                                                                                   |     | 33  |                                                         | μΑ   |

| I <sub>DD_HIBERNATE</sub> <sup>17, 15</sup> | <sup>9</sup> Hibernate State Current<br>Without USB | $V_{DD_{INT}} = 0 V,$ $V_{DD_{DMC}} = 1.8 V,$ $V_{DD_{EXT}} = V_{DD_{HADC}} = V_{DD_{OTP}} =$ $V_{DD_{RTC}} = V_{DD_{USB}} = 3.3 V,$ $T_{J} = 25^{\circ}C,$ $f_{CLKIN} = 0,$ $USB protection disabled$ $(USB_{PHY_{CTLDIS}} = 1)$ |     | 15  |                                                         | μΑ   |

| I <sub>DD_INT</sub> <sup>18</sup>           | V <sub>DD_INT</sub> Current                         | V <sub>DD_INT</sub> within operating conditions table specifications                                                                                                                                                              |     |     | See I <sub>DDINT_TOT</sub><br>equation on<br>on Page 56 |      |

| I <sub>DD_RTC</sub>                         | I <sub>DD_RTC</sub> Current                         | $V_{DD_{RTC}} = 3.3 \text{ V}, \text{ T}_{J} = 125^{\circ}\text{C}$                                                                                                                                                               |     |     | 10                                                      | μA   |

<sup>1</sup> Applies to all output and bidirectional signals except DMC0 signals, TWI signals, and USB0 signals.

<sup>2</sup> Applies to DMC0\_Axx, DMC0\_CAS, DMC0\_CKE, DMC0\_CK, DMC0\_CK, DMC0\_CS, DMC0\_DQxx, DMC0\_LDM, DMC0\_LDQS, DMC0\_LDQS,

DMC0\_ODT, DMC0\_RAS, DMC0\_UDM, DMC0\_UDQS, DMC0\_UDQS, and DMC0\_WE signals.

<sup>3</sup> Applies to all output and bidirectional signals except DMC0 signals and USB0 signals.

<sup>4</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TDI, and JTG\_TMS\_SWDIO signals.

<sup>5</sup> Applies to DMC0\_VREF signal.

<sup>6</sup> Applies to JTG\_TCK\_SWCLK and JTG\_TRST signals.

<sup>7</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TCK, and <u>JTG\_TRST</u> signals.

<sup>8</sup> Applies to JTG\_TDI, JTG\_TMS\_SWDIO, PA\_xx, PB\_xx, and PC\_xx signals when internal GPIO pull-ups are enabled. For information on when internal pull-ups are enabled for GPIOs. See ADSP-BF70x Designer Quick Reference on Page 38.

<sup>9</sup> Applies to USB0\_CLKIN signal.

<sup>10</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_AMS0</u>, <u>SMC0\_ARE</u>, <u>SMC0\_AWE</u>, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, JTG\_TDO\_SWO, USB0\_DM, USB0\_DP, USB0\_ID, and USB0\_VBC signals.

<sup>11</sup> Applies to DMC0\_Axx, DMC0\_BAxx, DMC0\_CAS, DMC0\_CS0, DMC0\_DQxx, DMC0\_LDQS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_UDQS, DMC0\_LDM, DMC0\_UDM, DMC0\_ODT, DMC0\_RAS, and DMC0\_WE signals.

<sup>12</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, <u>JTG\_TDO\_SWO</u>, <u>USB0\_DP</u>, <u>USB0\_ID</u>, <u>USB0\_ID</u>, <u>USB0\_VBC</u>, <u>U</u>

<sup>13</sup>Applies to USB0\_VBUS signals.

<sup>14</sup>Applies to all TWI signals.

<sup>15</sup>Applies to all signals, except DMC0 and TWI signals.

<sup>16</sup>Applies to all DMC0 signals.

<sup>17</sup>See the ADSP-BF70x Blackfin+ Processor Hardware Reference for definition of deep sleep and hibernate operating modes.

<sup>18</sup>Additional information can be found at Total Internal Power Dissipation.

<sup>19</sup>Applies to VDD\_EXT, VDD\_DMC, and VDD\_USB supply signals only. Clock inputs are tied high or low.

### **Total Internal Power Dissipation**

Total power dissipation has two components:

- 1. Static, including leakage current (deep sleep)

- 2. Dynamic, due to transistor switching characteristics for each clock domain

Many operating conditions can also affect power dissipation, including temperature, voltage, operating frequency, and processor activity. The following equation describes the internal current consumption.

$$\begin{split} I_{DDINT\_TOT} &= I_{DDINT\_DEEPSLEEP} + I_{DDINT\_CCLK\_DYN} + \\ I_{DDINT\_PLLCLK\_DYN} + I_{DDINT\_SYSCLK\_DYN} + \\ I_{DDINT\_SCLK0\_DYN} + I_{DDINT\_SCLK1\_DYN} + \\ I_{DDINT\_DCLK\_DYN} + I_{DDINT\_DMA\_DR\_DYN} + \\ I_{DDINT\_USBCLK\_DYN} \end{split}$$

$I_{DDINT\_DEEPSLEEP}$  is the only item present that is part of the static power dissipation component.  $I_{DDINT\_DEEPSLEEP}$  is specified as a function of voltage ( $V_{DD\_INT}$ ) and temperature (see Table 21).

There are eight different items that contribute to the dynamic power dissipation. These components fall into three broad categories: application-dependent currents, clock currents, and data transmission currents.

### **Application-Dependent Current**

The application-dependent currents include the dynamic current in the core clock domain.

Core clock (CCLK) use is subject to an activity scaling factor (ASF) that represents application code running on the processor cores and L1/L2 memories (Table 22). The ASF is combined with the CCLK frequency and  $V_{DD_{_{}INT}}$  dependent data in Table 23 to calculate this portion.

$I_{DDINT\_CCLK\_DYN}$  (mA) = Table 23 × ASF

### **Clock Current**

The dynamic clock currents provide the total power dissipated by all transistors switching in the clock paths. The power dissipated by each clock domain is dependent on voltage ( $V_{DD_{\_INT}}$ ), operating frequency and a unique scaling factor.

$I_{DDINT\_PLLCLK\_DYN} (mA) = 0.012 \times f_{PLLCLK} (MHz) \times V_{DD\_INT} (V)$   $I_{DDINT\_SYSCLK\_DYN} (mA) = 0.120 \times f_{SYSCLK} (MHz) \times V_{DD\_INT} (V)$   $I_{DDINT\_SCLK0\_DYN} (mA) = 0.110 \times f_{SCLK0} (MHz) \times V_{DD\_INT} (V)$   $I_{DDINT\_SCLK1\_DYN} (mA) = 0.068 \times f_{SCLK1} (MHz) \times V_{DD\_INT} (V)$   $I_{DDINT\_SCLK\_DYN} (mA) = 0.055 \times f_{DCLK} (MHz) \times V_{DD\_INT} (V)$ The dynamic component of the LISB clock is a unique case. T

The dynamic component of the USB clock is a unique case. The USB clock contributes a near constant current value when used.

Table 20. IDDINT\_USBCLK\_DYN Current

| Is USB Enabled?       | I <sub>DDINT_USBCLK_DYN</sub> (mA) |

|-----------------------|------------------------------------|

| Yes – High-Speed Mode | 13.94                              |

| Yes – Full-Speed Mode | 10.83                              |

| Yes – Suspend Mode    | 5.2                                |

| No                    | 0.34                               |

#### Data Transmission Current

The data transmission current represents the power dissipated when transmitting data. This current is expressed in terms of data rate. The calculation is performed by adding the data rate (MB/s) of each DMA-driven access to peripherals, L1, L2, and external memory. This number is then multiplied by a weighted data-rate coefficient and  $V_{DD_LINT}$ :

### $I_{DDINT\_DMADR\_DYN}$ (mA) = Weighted DRC × Total Data Rate (MB/s) × $V_{DD\_INT}$ (V)

A weighted data-rate coefficient is used because different coefficients exist depending on the source and destination of the transfer. For details on using this equation and calculating the weighted DRC, see the related Engineer Zone material. For a quick maximum calculation, the weighted DRC can be assumed to be 0.0497, which is the coefficient for L1 to L1 transfers.

|         | Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |       |

|---------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| (°C) رT | 1.045                          | 1.050 | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| -40     | 0.6                            | 0.6   | 0.7   | 0.7   | 0.7   | 0.8   | 0.8   | 0.8   | 0.9   | 0.9   | 0.9   | 1.0   | 1.0   |

| -20     | 1.1                            | 1.1   | 1.2   | 1.2   | 1.2   | 1.3   | 1.4   | 1.4   | 1.5   | 1.5   | 1.6   | 1.7   | 1.7   |

| 0       | 2.0                            | 2.0   | 2.1   | 2.2   | 2.3   | 2.4   | 2.5   | 2.5   | 2.6   | 2.7   | 2.8   | 3.0   | 3.0   |

| 25      | 4.3                            | 4.3   | 4.5   | 4.7   | 4.8   | 5.0   | 5.2   | 5.3   | 5.5   | 5.7   | 5.9   | 6.1   | 6.2   |

| 40      | 6.7                            | 6.8   | 7.0   | 7.3   | 7.5   | 7.8   | 8.0   | 8.3   | 8.6   | 8.8   | 9.1   | 9.4   | 9.6   |

| 55      | 10.3                           | 10.5  | 10.8  | 11.2  | 11.5  | 11.9  | 12.3  | 12.6  | 13.0  | 13.4  | 13.9  | 14.3  | 14.5  |

| 70      | 15.7                           | 15.9  | 16.4  | 16.8  | 17.4  | 17.9  | 18.4  | 18.9  | 19.5  | 20.1  | 20.7  | 21.3  | 21.6  |

| 85      | 23.3                           | 23.6  | 24.3  | 25.0  | 25.7  | 26.4  | 27.2  | 27.9  | 28.7  | 29.5  | 30.4  | 31.2  | 31.7  |

| 100     | 34.2                           | 34.6  | 35.5  | 36.5  | 37.5  | 38.5  | 39.5  | 40.6  | 41.7  | 42.8  | 43.9  | 45.1  | 45.7  |

| 105     | 38.7                           | 39.2  | 40.2  | 41.3  | 42.4  | 43.5  | 44.6  | 45.8  | 47.0  | 48.2  | 49.5  | 50.8  | 51.5  |

| 115     | 48.9                           | 49.5  | 50.7  | 52.0  | 53.4  | 54.7  | 56.0  | 57.5  | 59.0  | 60.5  | 62.0  | 63.6  | 64.4  |

| 125     | 61.5                           | 62.1  | 63.6  | 65.1  | 66.7  | 68.3  | 69.9  | 71.7  | 73.4  | 75.2  | 77.0  | 79.0  | 79.9  |

### Table 21. Static Current—IDD\_DEEPSLEEP (mA)

### Table 22. Activity Scaling Factors (ASF)

| I <sub>DDINT</sub> Power Vector | ASF  |

|---------------------------------|------|

| I <sub>DD-IDLE1</sub>           | 0.05 |

| I <sub>DD-IDLE2</sub>           | 0.05 |

| I <sub>DD-NOP1</sub>            | 0.56 |

| I <sub>DD-NOP2</sub>            | 0.59 |

| I <sub>DD-APP3</sub>            | 0.78 |

| I <sub>DD-APP1</sub>            | 0.79 |

| I <sub>DD-APP2</sub>            | 0.83 |

| I <sub>DD-TYP1</sub>            | 1.00 |

| I <sub>DD-TYP3</sub>            | 1.01 |

| I <sub>DD-TYP2</sub>            | 1.03 |

| I <sub>DD-HIGH1</sub>           | 1.39 |

| I <sub>DD-HIGH3</sub>           | 1.39 |

| I <sub>DD-HIGH2</sub>           | 1.54 |

| Table 23. | <b>CCLK Dynamic</b> | Current per core | (mA, with ASF = 1) |

|-----------|---------------------|------------------|--------------------|

|-----------|---------------------|------------------|--------------------|

|                         |       | Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |

|-------------------------|-------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| f <sub>CCLK</sub> (MHz) | 1.045 | 1.050                          | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| 400                     | 66.7  | 67.2                           | 67.9  | 68.7  | 69.4  | 70.2  | 71.1  | 71.8  | 72.6  | 73.4  | 74.2  | 74.9  | 75.4  |

| 350                     | 58.6  | 59.0                           | 59.6  | 60.3  | 61.0  | 61.7  | 62.4  | 63.0  | 63.7  | 64.4  | 65.1  | 65.8  | 66.1  |

| 300                     | 50.2  | 50.5                           | 51.1  | 51.7  | 52.3  | 52.9  | 53.5  | 54.1  | 54.7  | 55.3  | 55.9  | 56.4  | 56.8  |

| 250                     | 42.1  | 42.3                           | 42.8  | 43.3  | 43.8  | 44.3  | 44.7  | 45.3  | 45.8  | 46.3  | 46.8  | 47.4  | 47.6  |

| 200                     | 33.7  | 33.9                           | 34.3  | 34.7  | 35.1  | 35.5  | 35.9  | 36.3  | 36.7  | 37.1  | 37.5  | 37.9  | 38.0  |

| 150                     | 25.4  | 25.5                           | 25.8  | 26.1  | 26.4  | 26.7  | 27.0  | 27.3  | 27.6  | 27.9  | 28.2  | 28.5  | 28.8  |

| 100                     | 17.0  | 17.1                           | 17.3  | 17.5  | 17.7  | 17.9  | 18.1  | 18.3  | 18.5  | 18.6  | 18.8  | 19.0  | 19.1  |

### HADC

### HADC Electrical Characteristics

### Table 24. HADC Electrical Characteristics

| Parameter                          | Test Conditions                                                                                  | Тур | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|

| I <sub>DD_HADC_IDLE</sub>          | Current Consumption on V <sub>DD_HADC</sub> .<br>HADC is powered on, but not<br>converting.      | 2.0 | mA   |

| I <sub>DD_HADC_ACTIVE</sub>        | Current Consumption on $V_{DD_{HADC}}$ during a conversion.                                      | 2.5 | mA   |

| I <sub>DD_HADC_</sub><br>POWERDOWN | Current Consumption on V <sub>DD_HADC</sub> .<br>Analog circuitry of the HADC is<br>powered down | 10  | μΑ   |

### HADC DC Accuracy

#### Table 25. HADC DC Accuracy

| Parameter                       | Тур | Unit             |

|---------------------------------|-----|------------------|

| Resolution                      | 12  | Bits             |

| No Missing Codes (NMC)          | 10  | Bits             |

| Integral Nonlinearity (INL)     | ±2  | LSB <sup>1</sup> |

| Differential Nonlinearity (DNL) | ±2  | LSB <sup>1</sup> |

| Offset Error                    | ±8  | LSB <sup>1</sup> |

| Offset Error Matching           | ±10 | LSB <sup>1</sup> |

| Gain Error                      | ±4  | LSB <sup>1</sup> |

| Gain Error Matching             | ±4  | LSB <sup>1</sup> |

$^{1}$ LSB = HADC0\_VREFP ÷ 4096

### HADC Timing Specifications

### Table 26. HADC Timing Specifications

| Parameter              | Тур                   | Мах | Unit |

|------------------------|-----------------------|-----|------|

| <b>Conversion Time</b> | $20 	imes T_{SAMPLE}$ |     | μs   |

| Throughput Range       |                       | 1   | MSPS |

| TWAKEUP                |                       | 100 | μs   |

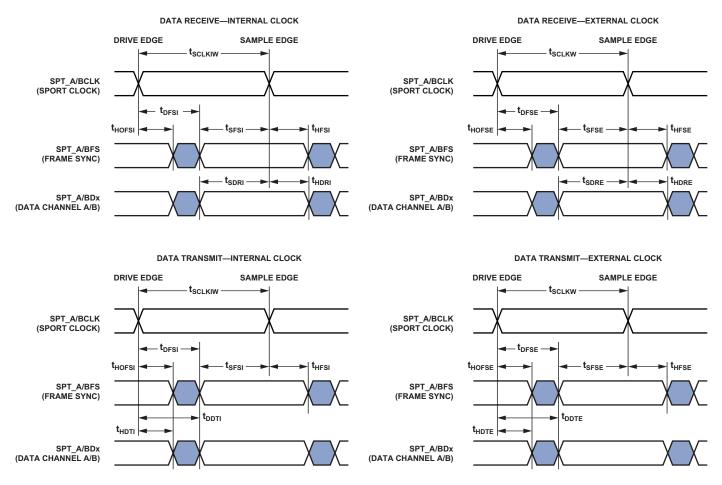

Figure 27. Serial Ports

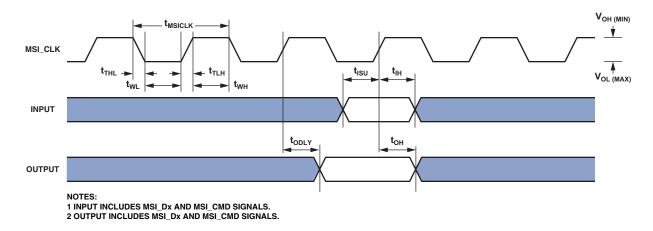

#### Mobile Storage Interface (MSI) Controller Timing

Table 64 and Figure 49 show I/O timing, related to the mobile storage interface (MSI).

The MSI timing depends on the period of the input clock that has been routed to the MSI peripheral ( $t_{MSICLKIN}$ ) by setting the MSI0\_UHS\_EXT register. See Table 63 for this information.

#### Table 63. t<sub>MSICLKIN</sub> Settings

| EXT_CLK_MUX_CTRL[31:30] | t <sub>MSICLKIN</sub>  |

|-------------------------|------------------------|

| 00                      | $t_{SCLK0} \times 2$   |

| 01                      | t <sub>SCLK0</sub>     |

| 10                      | t <sub>SCLK1</sub> × 3 |

$$t_{MSICLKIN} = \frac{1}{f_{MSICLKIN}}$$

$(f_{MSICLKPROG})$  frequency in MHz is set by the following equation where DIV0 is a field in the MSI\_CLKDIV register that can be set from 0 to 255. When DIV0 is set between 1 and 255, the following equation is used to determine  $f_{MSICLKPROG}$ :

$$f_{MSICLKPROG} = \frac{f_{MSICLKIN}}{DIV0 \times 2}$$

When DIV0 = 0,

$$f_{MSICLKPROG} = f_{MSICLKIN}$$

Also note the following:

$$t_{MSICLKPROG} = \frac{1}{f_{MSICLKPROG}}$$

#### Table 64. MSI Controller Timing

|                     |                                              |                                | dd_ext<br>Nominal                 | V <sub>0</sub><br>3.3V I       |                                 |      |

|---------------------|----------------------------------------------|--------------------------------|-----------------------------------|--------------------------------|---------------------------------|------|

| Param               | eter                                         | Min                            | Max                               | Min                            | Max                             | Unit |

| Timing              | Requirements                                 |                                |                                   |                                |                                 |      |

| t <sub>ISU</sub>    | Input Setup Time                             | 5.5                            |                                   | 4.7                            |                                 | ns   |

| t <sub>IH</sub>     | Input Hold Time                              | 2                              |                                   | 0.5                            |                                 | ns   |

| Switch              | ing Characteristics                          |                                |                                   |                                |                                 |      |

| t <sub>MSICLK</sub> | Clock Period Data Transfer Mode <sup>1</sup> | t <sub>MSICLKPROG</sub> – 1.5  |                                   | t <sub>MSICLKPROG</sub> – 1.5  |                                 | ns   |

| t <sub>WL</sub>     | Clock Low Time                               | 7                              |                                   | 7                              |                                 | ns   |

| $\mathbf{t}_{WH}$   | Clock High Time                              | 7                              |                                   | 7                              |                                 | ns   |

| t <sub>TLH</sub>    | Clock Rise Time                              |                                | 3                                 |                                | 3                               | ns   |

| $\mathbf{t}_{THL}$  | Clock Fall Time                              |                                | 3                                 |                                | 3                               | ns   |