Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                                           |

|-------------------------|-------------------------------------------------------------------------------------------|

| Product Status          | Active                                                                                    |

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 100MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 128kB                                                                                     |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                             |

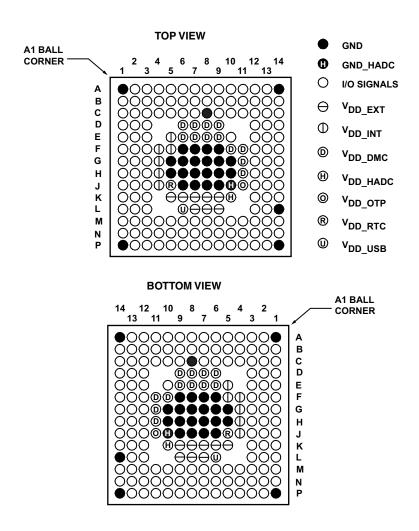

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf701kbcz-1                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The program sequencer controls the flow of instruction execution, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with dynamic branch prediction), and subroutine calls. Hardware supports zero-overhead looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.

The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering), and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).

The Blackfin processor supports a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories are those that typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The data memory holds data, and a dedicated scratchpad data memory stores stack and local variable information.

In addition, multiple L1 memory blocks are provided, offering a configurable mix of SRAM and cache. The memory management unit (MMU) provides memory protection for individual tasks that may be operating on the core and can protect system registers from unintended access.

The architecture provides three modes of operation: user mode, supervisor mode, and emulation mode. User mode has restricted access to certain system resources, thus providing a protected software environment, while supervisor mode has unrestricted access to the system and core resources.

#### INSTRUCTION SET DESCRIPTION

The Blackfin processor instruction set has been optimized so that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. The Blackfin processor supports a limited multi-issue capability, where a 32-bit instruction can be issued in parallel with two 16-bit instructions, allowing the programmer to use many of the core resources in a single instruction cycle.

The Blackfin processor family assembly language instruction set employs an algebraic syntax designed for ease of coding and readability. The instructions have been specifically tuned to provide a flexible, densely encoded instruction set that compiles to a very small final memory size. The instruction set also provides fully featured multifunction instructions that allow the programmer to use many of the processor core resources in a single instruction. Coupled with many features more often seen on microcontrollers, this instruction set is very efficient when compiling C and C++ source code. In addition, the architecture supports both user (algorithm/application code) and supervisor (O/S kernel, device drivers, debuggers, ISRs) modes of operation, allowing multiple levels of access to core processor resources.

The assembly language, which takes advantage of the processor's unique architecture, offers the following advantages:

- Seamlessly integrated DSP/MCU features are optimized for both 8-bit and 16-bit operations.

- A multi-issue load/store modified-Harvard architecture, which supports two 16-bit MAC or four 8-bit ALU + two load/store + two pointer updates per cycle.

- All registers, I/O, and memory are mapped into a unified 4G byte memory space, providing a simplified programming model.

- Control of all asynchronous and synchronous events to the processor is handled by two subsystems: the core event controller (CEC) and the system event controller (SEC).

- Microcontroller features, such as arbitrary bit and bit-field manipulation, insertion, and extraction; integer operations on 8-, 16-, and 32-bit data-types; and separate user and supervisor stack pointers.

- Code density enhancements, which include intermixing of 16-bit and 32-bit instructions (no mode switching, no code segregation). Frequently used instructions are encoded in 16 bits.

#### **PROCESSOR INFRASTRUCTURE**

The following sections provide information on the primary infrastructure components of the ADSP-BF70x processor.

#### **DMA Controllers**

The processor uses direct memory access (DMA) to transfer data within memory spaces or between a memory space and a peripheral. The processor can specify data transfer operations and return to normal processing while the fully integrated DMA controller carries out the data transfers independent of processor activity.

DMA transfers can occur between memory and a peripheral or between one memory and another memory. Each memory-tomemory DMA stream uses two channels, where one channel is the source channel, and the second is the destination channel.

All DMAs can transport data to and from all on-chip and off-chip memories. Programs can use two types of DMA transfers, descriptor-based or register-based. Register-based DMA allows the processor to directly program DMA control registers to initiate a DMA transfer. On completion, the control registers may be automatically updated with their original setup values for continuous transfer. Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. Descriptor-based DMA transfers allow multiple DMA sequences to be chained together and a DMA channel can be programmed to automatically set up and start another DMA transfer after the current sequence completes.

The DMA controller supports the following DMA operations.

- · A single linear buffer that stops on completion.

- A linear buffer with negative, positive, or zero stride length.

- A circular, auto-refreshing buffer that interrupts when each buffer becomes full.

output enable and the input enable of a GPIO pin are both active, the data signal before the pad driver is looped back to the receive path for the same GPIO pin.

#### **MEMORY ARCHITECTURE**

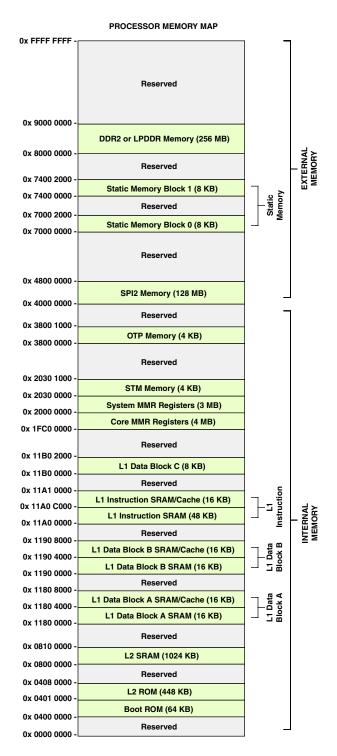

The processor views memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low-latency core-accessible memory as cache or SRAM, and larger, lower-cost and performance interface-accessible memory systems. See Figure 3.

#### Internal (Core-Accessible) Memory

The L1 memory system is the highest-performance memory available to the Blackfin+ processor core.

The core has its own private L1 memory. The modified Harvard architecture supports two concurrent 32-bit data accesses along with an instruction fetch at full processor speed which provides high-bandwidth processor performance. In the core, a 64K byte block of data memory partners with an 64K byte memory block for instruction storage. Each data block is multibanked for efficient data exchange through DMA and can be configured as SRAM. Alternatively, 16K bytes of each block can be configured in L1 cache mode. The four-way set-associative instruction cache and the 2 two-way set-associative data caches greatly accelerate memory access performance, especially when accessing external memories.

The L1 memory domain also features a 8K byte data SRAM block which is ideal for storing local variables and the software stack. All L1 memory is protected by a multi-parity-bit concept, regardless of whether the memory is operating in SRAM or cache mode.

Outside of the L1 domain, L2 and L3 memories are arranged using a Von Neumann topology. The L2 memory domain is a unified instruction and data memory and can hold any mixture of code and data required by the system design. The L2 memory domain is accessible by the Blackfin+ core through a dedicated 64-bit interface. It operates at SYSCLK frequency.

The processor features up to 1M byte of L2 SRAM, which is ECC-protected and organized in eight banks. Individual banks can be made private to any system master. There is also a 512K byte single-bank ROM in the L2 domain. It contains boot code, security code, and general-purpose ROM space.

#### **OTP Memory**

The processor features 4 kB of one-time-programmable (OTP) memory which is memory-map accessible. This memory stores a unique chip identification and is used to support secure-boot and secure operation.

Figure 3. ADSP-BF706/ADSP-BF707 Internal/External Memory Map

The CAN controller offers the following features:

- 32 mailboxes (8 receive only, 8 transmit only, 16 configurable for receive or transmit)

- · Dedicated acceptance masks for each mailbox

- · Additional data filtering on first two bytes

- Support for both the standard (11-bit) and extended (29-bit) identifier (ID) message formats

- Support for remote frames

- Active or passive network support

- CAN wake-up from hibernation mode (lowest static power consumption mode)

- Interrupts, including: TX complete, RX complete, error and global

An additional crystal is not required to supply the CAN clock, as the CAN clock is derived from a system clock through a programmable divider.

#### USB 2.0 On-the-Go Dual-Role Device Controller

The USB 2.0 on-the-go (OTG) dual-role device controller provides a low-cost connectivity solution for the growing adoption of this bus standard in industrial applications, as well as consumer mobile devices such as cell phones, digital still cameras, and MP3 players. The USB 2.0 controller allows these devices to transfer data using a point-to-point USB connection without the need for a PC host. The module can operate in a traditional USB peripheral-only mode as well as the host mode presented in the OTG supplement to the USB 2.0 specification.

The USB clock is provided through a dedicated external crystal or crystal oscillator.

The USB OTG dual-role device controller includes a phase locked loop with programmable multipliers to generate the necessary internal clocking frequency for USB.

#### Housekeeping ADC (HADC)

The HADC provides a general-purpose, multichannel successive approximation analog-to-digital converter. It supports the following features:

- 12-bit ADC core (10-bit accuracy) with built-in sample and hold

- · 4 single-ended input channels

- Throughput rates up to 1 MSPS

- Single external reference with analog inputs between 0 V and 3.3 V

- Selectable ADC clock frequency including the ability to program a prescaler

- Adaptable conversion type: allows single or continuous conversion with option of autoscan

- Auto sequencing capability with up to 4 autoconversions in a single session. Each conversion can be programmed to select any input channel.

- Four data registers (individually addressable) to store conversion values

### System Crossbars (SCB)

The system crossbars (SCB) are the fundamental building blocks of a switch-fabric style for (on-chip) system bus interconnection. The SCBs connect system bus masters to system bus slaves, providing concurrent data transfer between multiple bus masters and multiple bus slaves. A hierarchical model—built from multiple SCBs—provides a power and area efficient system interconnect, which satisfies the performance and flexibility requirements of a specific system.

The SCBs provide the following features:

- Highly efficient, pipelined bus transfer protocol for sustained throughput

- Full-duplex bus operation for flexibility and reduced latency

- Concurrent bus transfer support to allow multiple bus masters to access bus slaves simultaneously

- Protection model (privileged/secure) support for selective bus interconnect protection

#### **POWER AND CLOCK MANAGEMENT**

The processor provides three operating modes, each with a different performance/power profile. Control of clocking to each of the processor peripherals also reduces power consumption. See Table 5 for a summary of the power settings for each mode.

#### System Crystal Oscillator and USB Crystal Oscillator

The processor can be clocked by an external crystal (see Figure 4), a sine wave input, or a buffered, shaped clock derived from an external clock oscillator. If an external clock is used, it should be a TTL compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the SYS\_CLKIN pin of the processor. When an external clock is used, the SYS\_XTAL pin must be left unconnected. Alternatively, because the processor includes an on-chip oscillator circuit, an external crystal may be used.

For fundamental frequency operation, use the circuit shown in Figure 4. A parallel-resonant, fundamental frequency, microprocessor grade crystal is connected across the SYS\_CLKIN and SYS\_XTAL pins. The on-chip resistance between SYS\_CLKIN and the SYS\_XTAL pin is in the 500 k $\Omega$  range. Further parallel resistors are typically not recommended.

The two capacitors and the series resistor shown in Figure 4 fine-tune phase and amplitude of the sine frequency. The capacitor and resistor values shown in Figure 4 are typical values only. The capacitor values are dependent upon the load capacitance recommendations of the crystal manufacturer and the PCB physical layout. The resistor value depends on the drive

Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

| Port Name   | Direction | Description                                                                                                                                                                          |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPT_BCLK    | I/O       | <b>Channel B Clock.</b> Data and Frame Sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                             |

| SPT_BD0     | I/O       | <b>Channel B Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                  |

| SPT_BD1     | I/O       | <b>Channel B Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                |

| SPT_BFS     | I/O       | <b>Channel B Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                       |

| SPT_BTDV    | Output    | <b>Channel B Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots.          |

| SYS_BMODEn  | Input     | <b>Boot Mode Control n.</b> Selects the boot mode of the processor.                                                                                                                  |

| SYS_CLKIN   | Input     | Clock/Crystal Input. Connect to an external clock source or crystal.                                                                                                                 |

| SYS_CLKOUT  | Output    | <b>Processor Clock Output.</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter of the HRM for more details.                                                 |

| SYS_EXTWAKE | Output    | <b>External Wake Control.</b> Drives low during hibernate and high all other times. Typically connected to the enable input of the voltage regulator controlling the VDD_INT supply. |

| SYS_FAULT   | I/O       | <b>Active-Low Fault Output.</b> Indicates internal faults or senses external faults depending on the operating mode.                                                                 |

| SYS_HWRST   | Input     | Processor Hardware Reset Control. Resets the device when asserted.                                                                                                                   |

| SYS_NMI     | Input     | Non-maskable Interrupt. See the processor hardware and programming references for more details.                                                                                      |

| SYS_RESOUT  | Output    | Reset Output. Indicates that the device is in the reset or hibernate state.                                                                                                          |

| SYS_WAKEn   | Input     | <b>Power Saving Mode Wakeup n.</b> Wake-up source input for deep sleep and/or hibernate mode.                                                                                        |

| SYS_XTAL    | Output    | <b>Crystal Output.</b> Drives an external crystal. Must be left unconnected if an external clock is driving CLKIN.                                                                   |

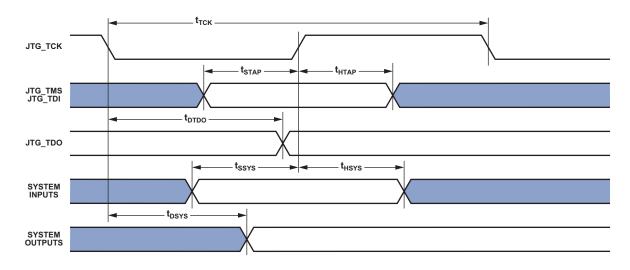

| JTG_SWCLK   | I/O       | Serial Wire Clock. Clocks data into and out of the target during debug.                                                                                                              |

| JTG_SWDIO   | I/O       | Serial Wire DIO. Sends and receives serial data to and from the target during debug.                                                                                                 |

| JTG_SWO     | Output    | Serial Wire Out. Provides trace data to the emulator.                                                                                                                                |

| JTG_TCK     | Input     | JTAG Clock. JTAG test access port clock.                                                                                                                                             |

| JTG_TDI     | Input     | JTAG Serial Data In. JTAG test access port data input.                                                                                                                               |

| JTG_TDO     | Output    | JTAG Serial Data Out. JTAG test access port data output.                                                                                                                             |

| JTG_TMS     | Input     | JTAG Mode Select. JTAG test access port mode select.                                                                                                                                 |

| JTG_TRST    | Input     | JTAG Reset. JTAG test access port reset.                                                                                                                                             |

| TM_ACIn     | Input     | <b>Alternate Capture Input n.</b> Provides an additional input for WIDCAP, WATCHDOG, and PININT modes.                                                                               |

| TM_ACLKn    | Input     | Alternate Clock n. Provides an additional time base for use by an individual timer.                                                                                                  |

| TM_CLK      | Input     | Clock. Provides an additional global time base for use by all the GP timers.                                                                                                         |

| TM_TMRn     | I/O       | Timer n. The main input/output signal for each timer.                                                                                                                                |

| TRACE_CLK   | Output    | Trace Clock. Clock output.                                                                                                                                                           |

| TRACE_Dnn   | Output    | Trace Data n. Unidirectional data bus.                                                                                                                                               |

| TWI_SCL     | I/O       | Serial Clock. Clock output when master, clock input when slave.                                                                                                                      |

| TWI_SDA     | I/O       | Serial Data. Receives or transmits data.                                                                                                                                             |

| UART_CTS    | Input     | Clear to Send. Flow control signal.                                                                                                                                                  |

| UART_RTS    | Output    | Request to Send. Flow control signal.                                                                                                                                                |

| UART_RX     | Input     | <b>Receive.</b> Receive input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                     |

| UART_TX     | Output    | <b>Transmit.</b> Transmit output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                  |

| USB_CLKIN   | Input     | <b>Clock/Crystal Input.</b> This clock input is multiplied by a PLL to form the USB clock. See data sheet specifications for frequency/tolerance information.                        |

Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

| Port Name | Direction | Description                                                                                                                                                                                                                                                                              |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_DM    | I/O       | Data –. Bidirectional differential data line.                                                                                                                                                                                                                                            |

| USB_DP    | I/O       | Data +. Bidirectional differential data line.                                                                                                                                                                                                                                            |

| USB_ID    | Input     | <b>OTG ID.</b> Senses whether the controller is a host or device. This signal is pulled low when an A-type plug is sensed (signifying that the USB controller is the A device), but the input is high when a B-type plug is sensed (signifying that the USB controller is the B device). |

| USB_VBC   | Output    | <b>VBUS Control.</b> Controls an external voltage source to supply VBUS when in host mode. May be configured as open-drain. Polarity is configurable as well.                                                                                                                            |

| USB_VBUS  | I/O       | Bus Voltage. Connects to bus voltage in host and device modes.                                                                                                                                                                                                                           |

| USB_XTAL  | Output    | <b>Crystal.</b> Drives an external crystal. Must be left unconnected if an external clock is driving USB_CLKIN.                                                                                                                                                                          |

Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name                           | Description                                                                  | Port                             | Pin Name                      |

|---------------------------------------|------------------------------------------------------------------------------|----------------------------------|-------------------------------|

| SYS_FAULT                             | Active-Low Fault Output                                                      | Not Muxed                        | SYS_FAULT                     |

| SYS_HWRST                             | Processor Hardware Reset Control                                             | Not Muxed                        | SYS_HWRST                     |

| SYS_NMI                               | Nonmaskable Interrupt                                                        | Not Muxed                        | SYS_NMI                       |

| SYS_RESOUT                            | Reset Output                                                                 | Not Muxed                        | SYS_RESOUT                    |

| SYS_WAKE0                             | Power Saving Mode Wake-up 0                                                  | В                                | PB_07                         |

| SYS_WAKE1                             | Power Saving Mode Wake-up 1                                                  | В                                | PB_08                         |

| SYS_WAKE2                             | Power Saving Mode Wake-up 2                                                  | В                                | PB_12                         |

| SYS_WAKE3                             | Power Saving Mode Wake-up 3                                                  | c                                | PC_02                         |

| SYS_WAKE4                             | Power Saving Mode Wake-up 4                                                  | Α                                | PA_12                         |

| SYS_XTAL                              | Crystal Output                                                               | Not Muxed                        | SYS_XTAL                      |

| TM0_ACI0                              | TIMERO Alternate Capture Input 0                                             | c                                | PC_03                         |

| TM0_ACI1                              | TIMERO Alternate Capture Input 1                                             | В                                | PB_01                         |

| TM0_ACI2                              | TIMERO Alternate Capture Input 2                                             | c                                | PC_07                         |

| TM0_ACI3                              | TIMERO Alternate Capture Input 3                                             | В                                | PB_09                         |

| TM0_ACI4                              | TIMERO Alternate Capture Input 4                                             | С                                | PC_01                         |

| TM0_ACI5                              | TIMERO Alternate Capture Input 5                                             | C                                | PC_02                         |

| TM0_ACI6                              | TIMERO Alternate Capture Input 6                                             | A                                | PA_12                         |

| TM0_ACLK0                             | TIMERO Alternate Clock 0                                                     | С                                | PC_04                         |

| TM0_ACLK1                             | TIMERO Alternate Clock 1                                                     | C                                | PC_10                         |

| TM0_ACLK2                             | TIMERO Alternate Clock 2                                                     | C                                | PC_09                         |

| TM0_ACLK3                             | TIMERO Alternate Clock 3                                                     | В                                | PB_00                         |

| TM0_ACLK4                             | TIMERO Alternate Clock 4                                                     | В                                | PB_10                         |

| TM0_ACLK5                             | TIMERO Alternate Clock 5                                                     | A                                | PA_14                         |

| TM0_ACLK6                             | TIMERO Alternate Clock 6                                                     | В                                | PB_04                         |

| TM0_CLK                               | TIMERO Clock                                                                 | В                                | PB_06                         |

| TM0_TMR0                              | TIMER0 Timer 0                                                               | A                                | PA_05                         |

| TM0_TMR1                              | TIMER0 Timer 1                                                               | A                                | PA_06                         |

| TM0_TMR2                              | TIMER0 Timer 2                                                               | A                                | PA_07                         |

| TM0_TMR3                              | TIMER0 Timer 3                                                               | C                                | PC_05                         |

| TM0_TMR4                              | TIMER0 Timer 4                                                               | A                                | PA_09                         |

| TM0_TMR5                              | TIMER0 Timer 5                                                               | A                                | PA_10                         |

| TM0_TMR6                              | TIMER0 Timer 6                                                               | A                                | PA_11                         |

| TM0_TMR7                              | TIMER0 Timer 7                                                               | A                                | PA_04                         |

| TRACEO_CLK                            | TPIU0 Trace Clock                                                            | В                                | PB_10                         |

| TRACEO_D00                            | TPIU0 Trace Data 0                                                           | В                                | PB_15                         |

| TRACE0_D01                            | TPIU0 Trace Data 1                                                           | В                                | PB_14                         |

| TRACE0_D02                            | TPIU0 Trace Data 2                                                           | В                                | PB_13                         |

| TRACEO_D03                            | TPIU0 Trace Data 3                                                           | В                                | PB_12                         |

| TRACE0_D04                            | TPIU0 Trace Data 4                                                           | В                                | PB_11                         |

| TRACEO_D05                            | TPIU0 Trace Data 5                                                           | A                                | PA_02                         |

| TRACEO_D06                            | TPIU0 Trace Data 6                                                           | A                                | PA_01                         |

| TRACEO_D07                            | TPIU0 Trace Data 7                                                           | A                                | PA_00                         |

|                                       |                                                                              |                                  |                               |

|                                       |                                                                              |                                  |                               |

|                                       |                                                                              |                                  |                               |

|                                       |                                                                              |                                  |                               |

| TWIO_SCL TWIO_SDA UARTO_CTS UARTO_RTS | TWIO Serial Clock TWIO Serial Data UARTO Clear to Send UARTO Request to Send | Not Muxed<br>Not Muxed<br>C<br>C | TWI0_SCL TWI0_SDA PC_03 PC_02 |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                                                                                                                                                                                                                                    |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_05       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Frame Sync   TM0 Timer 3   MSI0 Command Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                        |

| PC_06       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Data 0   SPI0 Master In, Slave Out   MSI0 Data 3 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                               |

| PC_07       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Frame Sync   SPI0 Master Out, Slave In   MSI0 Data 2   TM0 Alternate Capture Input 2 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                           |

| PC_08       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Data 0   SPI0 Data 2   MSI0 Data 0 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                             |

| PC_09       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Clock   SPI0 Data 3   MSI0 Clock   TM0 Alternate Clock 2 Notes: No notes.                                                                                                                                                                           |

| PC_10       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Clock   MSI0 Data 4   SPI1 Slave Select Output 3   TM0 Alternate Clock 1 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details. SPI slave select outputs require a pull-up when used. |

| PC_11       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Frame Sync   MSI0 Data 5   SPI0 Slave Select Output 3 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details. SPI slave select outputs require a pull-up when used.                    |

| PC_12       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 0   MSI0 Data 6  Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                                          |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                          |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|------------------------------------------------|

| VDD_OTP     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for OTP                              |

|             |      |                |             |               |                |               |                |                 | Notes: Must be powered.                        |

| VDD_RTC     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for RTC                              |

|             |      |                |             |               |                |               |                |                 | Notes: If RTC is not used, connect to ground.  |

| VDD_USB     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for USB                              |

|             |      |                |             |               |                |               |                |                 | Notes: If USB is not used, connect to VDD_EXT. |

### **ELECTRICAL CHARACTERISTICS**

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.400<br>0.400<br>0.320 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| V <sub>OH_DDR2</sub> <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -7.1 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OH_DDR2</sub> <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 40 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -5.8 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OH_DDR2</sub> <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -4.1 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OH_DDR2</sub> <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -3.4 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OH_DDR2</sub> <sup>2</sup> High Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -2.0 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OL_DDR2</sub> <sup>2</sup> High Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -2.0 mA         V <sub>DD_DMC</sub> - 0.320           V <sub>OL_DDR2</sub> <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 1.0 mA         I <sub>DD_DMC</sub> = 0.320           V <sub>OL_DDR2</sub> <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 5.8 mA         I <sub>DD_DMC</sub> = 0.20 mA           V <sub>OL_DDR2</sub> <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA         I <sub>DD_DMC</sub> = 0.20 mA           V <sub>OL_LPDDR2</sub> <sup>2</sup> Low Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA         I <sub></sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.400<br>0.400          |

| Programmed Impedance = 34 Ω   Vol. Dok.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.400                   |

| VOH_DDR2 <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 40 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -5.8 mA         V <sub>DD_DMC</sub> - 0.320           VOH_DDR2 <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -4.1 mA         V <sub>DD_DMC</sub> - 0.320           VOH_DDR2 <sup>2</sup> High Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -3.4 mA         V <sub>DD_DMC</sub> - 0.320           VOL_EDR02 <sup>2</sup> High Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -2.0 mA         V <sub>DD_DMC</sub> - 0.320           VOL_3         Low Level Output Voltage         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -2.0 mA         V <sub>DD_DMC</sub> - 0.320           VOL_DDR2 <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 7.1 mA           VOL_DDR2 <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 40 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 5.8 mA           VOL_DDR2 <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA           VOL_DDR2 <sup>2</sup> Low Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 2.0 mA           V <sub>IL_PDDR2</sub> Low Level Output Voltage, DDR2, Programmed Impedance = 3.0 N, I <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 2.0 mA         I <sub>DD_DMC</sub> = 1.70 V, I <sub>DD_DMC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.400<br>0.400          |

| Programmed Impedance = 40 Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.400<br>0.400          |

| VOH_DDRA2         High Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         VDD_DMC = 1.70 V, IQH = -4.1 mA         VDD_DMC = 0.320           VOH_DDRA2         High Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         VDD_DMC = 1.70 V, IQH = -3.4 mA         VDD_DMC = 0.320           VOH_DDRA2         High Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         VDD_DMC = 1.70 V, IQH = -2.0 mA         VDD_DMC = 0.320           VOL_3         Low Level Output Voltage         VDD_DMC = 1.70 V, IQH = 1.0 mA         VDD_DMC = 0.320           VOL_DDR22         Low Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         VDD_DMC = 1.70 V, IQH = 2.0 mA         VDD_DMC = 1.70 V, IQH = 7.1 mA           VOL_DDR22         Low Level Output Voltage, DDR2, Programmed Impedance = 40 Ω         VDD_DMC = 1.70 V, IQH = 4.1 mA         VDD_DMC = 1.70 V, IQH = 4.1 mA           VOL_DDR22         Low Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         VDD_DMC = 1.70 V, IQH = 4.1 mA         VDD_DMC = 1.70 V, IQH = 4.1 mA           VOL_DDR22         Low Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         VDD_DMC = 1.70 V, IQH = 3.4 mA         VDD_DMC = 1.70 V, IQH = 3.4 mA           VOL_DDR22         Low Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         VDD_DMC = 1.70 V, IQH = 3.4 mA         VDD_DMC = 1.90 V, IQH = 3.4 mA           IH_4         High Level Input Current         VDD_DMC = 1.70 V, IQH = 3.4 mA         VDD_DMC = 1.90 V, IQH = 3.4 mA </td <td>0.400</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.400                   |

| Programmed Impedance = 50 Ω   VoH_DDR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.400                   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.400<br>0.400          |

| Programmed Impedance = 60 Ω   Vol. Lipbor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.400<br>0.400          |

| VolLPDDR <sup>2</sup> High Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OH</sub> = -2.0 mA         V <sub>DD_DMC</sub> - 0.320           Vol. <sup>3</sup> Low Level Output Voltage         V <sub>DD_EXT</sub> = 1.7 V, I <sub>OL</sub> = 1.0 mA         I           Vol. <sup>3</sup> Low Level Output Voltage         V <sub>DD_EXT</sub> = 3.13 V, I <sub>OL</sub> = 2.0 mA         I           Vol. <sup>DDR2<sup>2</sup></sup> Low Level Output Voltage, DDR2, Programmed Impedance = 34 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 5.8 mA         I           Vol. <sup>DDR2<sup>2</sup></sup> Low Level Output Voltage, DDR2, Programmed Impedance = 40 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 5.8 mA         I           Vol. <sup>DDR2<sup>2</sup></sup> Low Level Output Voltage, DDR2, Programmed Impedance = 50 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 4.1 mA         I           Vol. <sup>DDR2<sup>2</sup></sup> Low Level Output Voltage, DDR2, Programmed Impedance = 60 Ω         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA         I           Vol. <sup>DDR2<sup>2</sup></sup> Low Level Output Voltage, LPDDR         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 2.0 mA         I           Vol. <sup>DDR2</sup> Low Level Input Current         V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 2.0 mA         I           Vol. <sup>DDR2</sup> V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA         I           V <sub>DD_DMC</sub> = 1.70 V, I <sub>OL</sub> = 3.4 mA         I         I           V <sub>DD_DMC</sub> = 1.70 V, I <sub>DD_DMC</sub> = 1.9 V, I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.400<br>0.400          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.400<br>0.400          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.400                   |