Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

|                         |                                                                              |

| Product Status          | Active                                                                       |

| Туре                    | Blackfin+                                                                    |

| nterface                | CAN, DSPI, EBI/EMI, I²C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 400MHz                                                                       |

| Non-Volatile Memory     | ROM (512kB)                                                                  |

| On-Chip RAM             | 512kB                                                                        |

| /oltage - I/O           | 1.8V, 3.3V                                                                   |

| /oltage - Core          | 1.10V                                                                        |

| perating Temperature    | -40°C ~ 85°C (TA)                                                            |

| lounting Type           | Surface Mount                                                                |

| Package / Case          | 88-VFQFN Exposed Pad, CSP                                                    |

| Supplier Device Package | 88-LFCSP-VQ (12x12)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf704bcpz-4         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **TABLE OF CONTENTS**

| General Description                                            |

|----------------------------------------------------------------|

| Blackfin+ Processor Core                                       |

| Instruction Set Description                                    |

| Processor Infrastructure                                       |

| Memory Architecture                                            |

| Security Features                                              |

| Processor Safety Features                                      |

| Additional Processor Peripherals                               |

| Power and Clock Management                                     |

| System Debug                                                   |

| Development Tools                                              |

| Additional Information                                         |

| Related Signal Chains                                          |

| Security Features Disclaimer                                   |

| ADSP-BF70x Detailed Signal Descriptions                        |

| 184-Ball CSP_BGA Signal Descriptions                           |

| GPIO Multiplexing for 184-Ball CSP_BGA                         |

| 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions          |

| GPIO Multiplexing for 12 mm $\times$ 12 mm 88-Lead LFCSP (QFN) |

|                                                                |

| REVISION HISTORY                                               |

| 9/15—Rev. 0 to Rev. A                                          |

| Updated Processor Comparison                                   |

| Updated Serial Ports (SPORTs)                                  |

| Updated Mobile Storage Interface (MSI)                         |

| Updated External Components for RTC                            |

| Updated Development Tools                                      |

| Updated SPI Port—SPI_RDY Timing 92                             |

| Added Models to Ordering Guide                                 |

| ADSP-BF70x Designer Quick Reference                                                             |

|-------------------------------------------------------------------------------------------------|

| Specifications                                                                                  |

| Operating Conditions                                                                            |

| Electrical Characteristics                                                                      |

| HADC 58                                                                                         |

| Package Information                                                                             |

| Absolute Maximum Ratings 59                                                                     |

| ESD Sensitivity                                                                                 |

| Timing Specifications                                                                           |

| Output Drive Currents                                                                           |

| Test Conditions                                                                                 |

| Environmental Conditions                                                                        |

| ADSP-BF70x 184-Ball CSP_BGA Ball Assignments (Numerical by Ball Number)                         |

| ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN)<br>Lead Assignments (Numerical by Lead Number) 110 |

| Outline Dimensions                                                                              |

| Surface-Mount Design                                                                            |

| Planned Automotive Production Products 115                                                      |

| Ordering Guide116                                                                               |

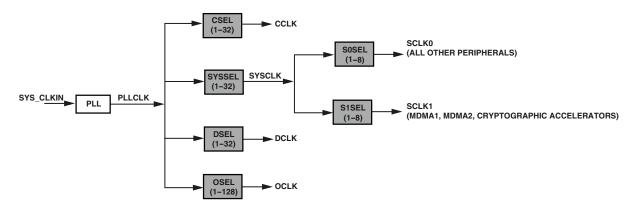

Table 3. Clock Dividers

|                                                            | Divider (if Available on    |

|------------------------------------------------------------|-----------------------------|

| Clock Source                                               | SYS_CLKOUT)                 |

| CCLK (Core Clock)                                          | By 16                       |

| SYSCLK (System Clock)                                      | By 8                        |

| SCLK0 (System Clock, All Peripherals not Covered by SCLK1) | Not available on SYS_CLKOUT |

| SCLK1 (System Clock for Crypto Engines and MDMA)           | By 8                        |

| DCLK (LPDDR/DDR2 Clock)                                    | By 8                        |

| OCLK (Output Clock)                                        | Programmable                |

| CLKBUF                                                     | None, direct from SYS_CLKIN |

## **Power Management**

As shown in Table 4, the processor supports multiple power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate Specifications table for processor operating conditions; even if the feature/peripheral is not used.

**Table 4. Power Domains**

| Power Domain                                       | <b>V</b> <sub>DD</sub> Range |

|----------------------------------------------------|------------------------------|

| All Internal Logic                                 | $V_{DD\_INT}$                |

| DDR2/LPDDR                                         | $V_{DD\_DMC}$                |

| USB                                                | $V_{DD\_USB}$                |

| OTP Memory                                         | $V_{DD\_OTP}$                |

| HADC                                               | $V_{DD\_HADC}$               |

| RTC                                                | $V_{DD\_RTC}$                |

| All Other I/O (Includes SYS, JTAG, and Ports Pins) | $V_{DD\_EXT}$                |

The dynamic power management feature of the processor allows the processor's core clock frequency ( $f_{CCLK}$ ) to be dynamically controlled.

The power dissipated by a processor is largely a function of its clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

See Table 5 for a summary of the power settings for each mode.

## Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed, providing capability for maximum operational frequency. This is the power-up default execution state in which maximum performance can be achieved. The processor core and all enabled peripherals run at full speed.

# Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core and to all synchronous peripherals. Asynchronous peripherals may still be running but cannot access internal resources or external memory.

**Table 5. Power Settings**

| Mode/State | PII      | PLL<br>Bypassed |          | f <sub>SYSCLK</sub> ,<br>f <sub>DCLK</sub> ,<br>f <sub>SCLK0</sub> ,<br>f <sub>SCLK1</sub> | Core<br>Power |

|------------|----------|-----------------|----------|--------------------------------------------------------------------------------------------|---------------|

| Full On    | Enabled  | No              | Enabled  |                                                                                            | On            |

| Deep Sleep | Disabled | _               | Disabled | Disabled                                                                                   | On            |

| Hibernate  | Disabled | _               | Disabled | Disabled                                                                                   | Off           |

## Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling the voltage and clocks to the processor core and to all of the peripherals. This setting signals the external voltage regulator supplying the VDD\_INT pins to shut off using the SYS\_EXTWAKE signal, which provides the lowest static power dissipation.

Any critical information stored internally (for example, memory contents, register contents, and other information) must be written to a nonvolatile storage device (or self-refreshed DRAM) prior to removing power if the processor state is to be preserved.

Because the  $V_{DD\_EXT}$  pins can still be supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to still have power applied without drawing unwanted current.

### **Reset Control Unit**

Reset is the initial state of the whole processor or the core and is the result of a hardware- or software-triggered event. In this state, all control registers are set to their default values and functional units are idle. Exiting a full system reset starts with the core being ready to boot.

The reset control unit (RCU) controls how all the functional units enter and exit reset. Differences in functional requirements and clocking constraints define how reset signals are generated. Programs must guarantee that none of the reset functions puts the system into an undefined state or causes resources to stall. This is particularly important when the core is reset (programs must ensure that there is no pending system activity involving the core when it is being reset).

From a system perspective, reset is defined by both the reset target and the reset source described as follows in the following list.

### Target defined:

- Hardware Reset—All functional units are set to their default states without exception. History is lost.

- System Reset—All functional units except the RCU are set to their default states.

- Core-only Reset—Affects the core only. The system software should guarantee that the core, while in reset state, is not accessed by any bus master.

#### Source defined:

- Hardware Reset—The SYS\_HWRST input signal is asserted active (pulled down).

- System Reset—May be triggered by software (writing to the RCU\_CTL register) or by another functional unit such as the dynamic power management (DPM) unit (hibernate) or any of the system event controller (SEC), trigger routing unit (TRU), or emulator inputs.

- Core-only Reset—Triggered by software.

- Trigger request (peripheral).

### **Voltage Regulation**

The processor requires an external voltage regulator to power the VDD\_INT pins. To reduce standby power consumption, the external voltage regulator can be signaled through SYS\_EXTWAKE to remove power from the processor core. This signal is high-true for power-up and may be connected directly to the low-true shut-down input of many common regulators.

While in the hibernate state, all external supply pins (VDD\_EXT, VDD\_USB, and VDD\_DMC) can still be powered, eliminating the need for external buffers. The external voltage regulator can be activated from this power down state by asserting the \$\overline{SYS}\_HWRST\$ pin, which then initiates a boot sequence. \$\overline{SYS}\_EXTWAKE\$ indicates a wake-up to the external voltage regulator.

#### SYSTEM DEBUG

The processor includes various features that allow for easy system debug. These are described in the following sections.

### System Watchpoint Unit

The system watchpoint unit (SWU) is a single module which connects to a single system bus and provides for transaction monitoring. One SWU is attached to the bus going to each system slave. The SWU provides ports for all system bus address channel signals. Each SWU contains four match groups of registers with associated hardware. These four SWU match groups operate independently, but share common event (interrupt, trigger, and others) outputs.

### **Debug Access Port**

The debug access port (DAP) provides IEEE-1149.1 JTAG interface support through its JTAG debug and serial wire debug port (SWJ-DP). SWJ-DP is a combined JTAG-DP and SW-DP that enables either serial wire debug (SWD) or a JTAG emulator to be connected to a target. SWD signals share the same pins as

JTAG. The DAP provides an optional instrumentation trace for both the core and system. It provides a trace stream that conforms to MIPI System Trace Protocol version 2 (STPv2).

#### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (CrossCore® Embedded Studio), evaluation products, emulators, and a wide variety of software add-ins

### **Integrated Development Environments (IDEs)**

CrossCore Embedded Studio is based on the Eclipse™ framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information, visit www.analog.com/cces.

### **EZ-KIT Lite Evaluation Board**

For processor evaluation, Analog Devices provides a wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information, visit www.analog.com and search on "ezkit" or "ezextender".

#### **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE, a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

#### ADSP-BF706 EZ-KIT Mini

The ADSP-BF706 EZ-KIT Mini™ product (ADZS-BF706-EZMini) contains the ADSP-BF706 processor and is shipped with all of the necessary hardware. Users can start their evaluation immediately. The EZ-KIT Mini product includes the standalone evaluation board and USB cable. The EZ-KIT Mini ships with an on-board debug agent.

The evaluation board is designed to be used in conjunction with the CrossCore Embedded Studio (CCES) development tools to test capabilities of the ADSP-BF706 Blackfin processor.

## Blackfin Low Power Imaging Platform (BLIP)

The Blackfin low power imaging platform (BLIP) integrates the ADSP-BF707 Blackfin processor and Analog Devices software code libraries. The code libraries are optimized to detect the presence and behavior of humans or vehicles in indoor and outdoor environments. The BLIP hardware platform is delivered preloaded with the occupancy software module.

#### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called board support packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

## **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information, see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with CrossCore Embedded Studio. For more information, visit <a href="https://www.analog.com">www.analog.com</a> and search on "Blackfin software modules" or "SHARC software modules".

## Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each DAP-enabled processor, Analog Devices supplies an IEEE 1149.1 JTAG test access port (TAP), serial wire debug port (SWJ-DP), and trace capabilities. In-circuit emulation is facilitated by use of the JTAG or SWD interface. The emulator accesses the processor's internal features through the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and

registers. The emulators require the target board to include a header(s) that supports connection of the processor's DAP to the emulator for trace and debug.

Analog Devices emulators actively drive JTG\_TRST high. Third-party emulators may expect a pull-up on JTG\_TRST and therefore will not drive JTG\_TRST high. When using this type of third-party emulator JTG\_TRST must still be driven low during power-up reset, but should subsequently be driven high externally before any emulation or boundary-scan operations. See Power-Up Reset Timing on Page 61 for more information on POR specifications.

For more details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, contact the factory for more information.

## **ADDITIONAL INFORMATION**

The following publications that describe the ADSP-BF70x processors can be accessed electronically on our website:

- ADSP-BF70x Blackfin+ Processor Hardware Reference

- ADSP-BF70x Blackfin+ Processor Programming Reference

- ADSP-BF70x Blackfin+ Processor Anomaly List

### **RELATED SIGNAL CHAINS**

A signal chain is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The application signal chains page in the Circuits from the Lab<sup>®</sup> site (http:\\www.analog.com\circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name          | Description                             | Port | Pin Name |

|----------------------|-----------------------------------------|------|----------|

| SMC0_ARE             | SMC0 Read Enable                        | A    | PA_13    |

| SMC0_AWE             | SMC0 Write Enable                       | Α    | PA_14    |

| SMC0_D00             | SMC0 Data 0                             | В    | PB_07    |

| SMC0_D01             | SMC0 Data 1                             | В    | PB_06    |

| SMC0_D02             | SMC0 Data 2                             | В    | PB_05    |

| SMC0_D03             | SMC0 Data 3                             | В    | PB_04    |

| SMC0_D04             | SMC0 Data 4                             | В    | PB_03    |

| SMC0_D05             | SMC0 Data 5                             | В    | PB_02    |

| SMC0_D06             | SMC0 Data 6                             | В    | PB_01    |

| SMC0_D07             | SMC0 Data 7                             | В    | PB_00    |

| SMC0_D08             | SMC0 Data 8                             | В    | PB_08    |

| SMC0_D09             | SMC0 Data 9                             | В    | PB_09    |

| SMC0_D10             | SMC0 Data 10                            | В    | PB_10    |

| SMC0_D11             | SMC0 Data 11                            | В    | PB_11    |

| SMC0_D12             | SMC0 Data 12                            | В    | PB_12    |

| SMC0_D13             | SMC0 Data 13                            | В    | PB_13    |

| SMC0_D14             | SMC0 Data 14                            | В    | PB_14    |

| SMC0_D15             | SMC0 Data 15                            | В    | PB_15    |

| SPIO_CLK             | SPI0 Clock                              | В    | PB_00    |

| SPIO_CLK             | SPI0 Clock                              | C    | PC_04    |

| SPIO_D2              | SPI0 Data 2                             | В    | PB_03    |

| SPIO_D2              | SPI0 Data 2                             | C    | PC_08    |

| SPIO_D2              | SPI0 Data 3                             | В    | PB_07    |

|                      | SPI0 Data 3                             | C    | PC_09    |

| SPI0_D3<br>SPI0_MISO | SPIO Master In, Slave Out               | В    | PB_01    |

|                      | SPI0 Master In, Slave Out               | C    | PC_06    |

| SPIO_MISO            | SPIO Master Out, Slave In               |      |          |

| SPIO_MOSI            |                                         | В    | PB_02    |

| SPIO_MOSI            | SPIO Master Out, Slave In<br>SPIO Ready | C    | PC_07    |

| SPIO_RDY             |                                         | A    | PA_06    |

| SPIO_SEL1            | SPI0 Slave Select Output 1              | A    | PA_05    |

| SPIO_SEL2            | SPI0 Slave Select Output 2              | A    | PA_06    |

| SPIO_SEL3            | SPI0 Slave Select Output 3              | C    | PC_11    |

| SPIO_SEL4            | SPI0 Slave Select Output 4              | В    | PB_04    |

| SPIO_SEL5            | SPI0 Slave Select Output 5              | В    | PB_05    |

| SPIO_SEL6            | SPI0 Slave Select Output 6              | В    | PB_06    |

| SPIO_SS              | SPIO Slave Select Input                 | A    | PA_05    |

| SPI1_CLK             | SPI1 Clock                              | A    | PA_00    |

| SPI1_MISO            | SPI1 Master In, Slave Out               | A    | PA_01    |

| SPI1_MOSI            | SPI1 Master Out, Slave In               | A    | PA_02    |

| SPI1_RDY             | SPI1 Ready                              | A    | PA_03    |

| SPI1_SEL1            | SPI1 Slave Select Output 1              | A    | PA_04    |

| SPI1_SEL2            | SPI1 Slave Select Output 2              | A    | PA_03    |

| SPI1_SEL3            | SPI1 Slave Select Output 3              | C    | PC_10    |

| SPI1_SEL4            | SPI1 Slave Select Output 4              | Α    | PA_14    |

| SPI1_SS              | SPI1 Slave Select Input                 | Α    | PA_04    |

| SPI2_CLK             | SPI2 Clock                              | В    | PB_10    |

## 12 mm × 12 mm 88-LEAD LFCSP (QFN) SIGNAL DESCRIPTIONS

The processor's pin definitions are shown in Table 11. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions

| Signal Name | Description                     | Port      | Pin Name      |

|-------------|---------------------------------|-----------|---------------|

| CAN0_RX     | CAN0 Receive                    | С         | PC_02         |

| CAN0_TX     | CAN0 Transmit                   | C         | PC_03         |

| CAN1_RX     | CAN1 Receive                    | A         | PA_12         |

| CAN1_TX     | CAN1 Transmit                   | A         | PA_13         |

| CNT0_DG     | CNT0 Count Down and Gate        | A         | PA_07         |

| CNT0_UD     | CNT0 Count Up and Direction     | A         | PA_15         |

| CNT0_ZM     | CNT0 Count Zero Marker          | A         | PA_13         |

| GND         | Ground                          | Not Muxed | GND           |

| JTG_SWCLK   | TAPC0 Serial Wire Clock         | Not Muxed | JTG_TCK_SWCLK |

| JTG_SWDIO   | TAPC0 Serial Wire DIO           | Not Muxed | JTG_TMS_SWDIO |

| JTG_SWO     | TAPC0 Serial Wire Out           | Not Muxed | JTG_TDO_SWO   |

| JTG_TCK     | TAPC0 JTAG Clock                | Not Muxed | JTG_TCK_SWCLK |

| JTG_TDI     | TAPC0 JTAG Serial Data In       | Not Muxed | JTG_TDI       |

| JTG_TDO     | TAPC0 JTAG Serial Data Out      | Not Muxed | JTG_TDO_SWO   |

| JTG_TMS     | TAPC0 JTAG Mode Select          | Not Muxed | JTG_TMS_SWDIO |

| JTG_TRST    | TAPC0 JTAG Reset                | Not Muxed | JTG_TRST      |

| MSI0_CD     | MSI0 Card Detect                | A         | PA_08         |

| MSI0_CLK    | MSI0 Clock                      | C         | PC_09         |

| MSI0_CMD    | MSI0 Command                    | C         | PC_05         |

| MSI0_D0     | MSI0 Data 0                     | C         | PC_08         |

| MSI0_D1     | MSI0 Data 1                     | C         | PC_04         |

| MSI0_D2     | MSI0 Data 2                     | С         | PC_07         |

| MSI0_D3     | MSI0 Data 3                     | c         | PC_06         |

| MSI0_D4     | MSI0 Data 4                     | C         | PC_10         |

| PA_00-PA_15 | Position 00 through Position 15 | A         | PA_00-PA_15   |

| PB_00-PB_15 | Position 00 through Position 15 | В         | PB_00-PB_15   |

| PC_00-PC_10 | Position 00 through Position 10 | c         | PC_00-PC_10   |

| PPI0_CLK    | EPPI0 Clock                     | A         | PA_14         |

| PPI0_D00    | EPPI0 Data 0                    | В         | PB_07         |

| PPI0_D01    | EPPI0 Data 1                    | В         | PB_06         |

| PPI0_D02    | EPPI0 Data 2                    | В         | PB_05         |

| PPI0_D03    | EPPI0 Data 3                    | В         | PB_04         |

| PPI0_D04    | EPPI0 Data 4                    | В         | PB_03         |

| PPI0_D05    | EPPI0 Data 5                    | В         | PB_02         |

| PPI0_D06    | EPPI0 Data 6                    | В         | PB_01         |

| PPI0_D07    | EPPI0 Data 7                    | В         | PB_00         |

Table 11. ADSP-BF70x 12 mm  $\times$  12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

| Signal Name | Description                          | Port      | Pin Name    |

|-------------|--------------------------------------|-----------|-------------|

| SPTO_AFS    | SPORTO Channel A Frame Sync          | A         | PA_12       |

| SPTO_AFS    | SPORTO Channel A Frame Sync          | С         | PC_05       |

| SPT0_ATDV   | SPORTO Channel A Transmit Data Valid | Α         | PA_15       |

| SPT0_BCLK   | SPORTO Channel B Clock               | В         | PB_04       |

| SPT0_BCLK   | SPORTO Channel B Clock               | С         | PC_04       |

| SPT0_BD0    | SPORTO Channel B Data 0              | В         | PB_05       |

| SPT0_BD0    | SPORT0 Channel B Data 0              | С         | PC_06       |

| SPT0_BD1    | SPORT0 Channel B Data 1              | В         | PB_07       |

| SPT0_BD1    | SPORT0 Channel B Data 1              | С         | PC_01       |

| SPTO_BFS    | SPORTO Channel B Frame Sync          | В         | PB_06       |

| SPTO_BFS    | SPORTO Channel B Frame Sync          | C         | PC_07       |

| SPT0_BTDV   | SPORTO Channel B Transmit Data Valid | A         | PA_15       |

| SPT1_ACLK   | SPORT1 Channel A Clock               | A         | PA_08       |

| SPT1_AD0    | SPORT1 Channel A Data 0              | Α         | PA_10       |

| SPT1_AD1    | SPORT1 Channel A Data 1              | Α         | PA_11       |

| SPT1_AFS    | SPORT1 Channel A Frame Sync          | Α         | PA_09       |

| SPT1_ATDV   | SPORT1 Channel A Transmit Data Valid | Α         | PA_07       |

| SPT1_BCLK   | SPORT1 Channel B Clock               | В         | PB_00       |

| SPT1_BCLK   | SPORT1 Channel B Clock               | C         | PC_10       |

| SPT1_BD0    | SPORT1 Channel B Data 0              | В         | PB_02       |

| SPT1_BD1    | SPORT1 Channel B Data 1              | В         | PB_03       |

| SPT1_BFS    | SPORT1 Channel B Frame Sync          | В         | PB_01       |

| SPT1_BTDV   | SPORT1 Channel B Transmit Data Valid | Α         | PA_07       |

| SYS_BMODE0  | Boot Mode Control 0                  | Not Muxed | SYS_BMODE0  |

| SYS_BMODE1  | Boot Mode Control 1                  | Not Muxed | SYS_BMODE1  |

| SYS_CLKIN   | Clock/Crystal Input                  | Not Muxed | SYS_CLKIN   |

| SYS_CLKOUT  | Processor Clock Output               | Not Muxed | SYS_CLKOUT  |

| SYS_EXTWAKE | External Wake Control                | Not Muxed | SYS_EXTWAKE |

| SYS_FAULT   | Active-Low Fault Output              | Not Muxed | SYS_FAULT   |

| SYS_HWRST   | Processor Hardware Reset Control     | Not Muxed | SYS_HWRST   |

| SYS_NMI     | Non-maskable Interrupt               | Not Muxed | SYS_NMI     |

| SYS_RESOUT  | Reset Output                         | Not Muxed | SYS_RESOUT  |

| SYS_WAKE0   | Power Saving Mode Wake-up 0          | В         | PB_07       |

| SYS_WAKE1   | Power Saving Mode Wake-up 1          | В         | PB_08       |

| SYS_WAKE2   | Power Saving Mode Wake-up 2          | В         | PB_12       |

| SYS_WAKE3   | Power Saving Mode Wake-up 3          | С         | PC_02       |

| SYS_WAKE4   | Power Saving Mode Wake-up 4          | Α         | PA_12       |

| SYS_XTAL    | Crystal Output                       | Not Muxed | SYS_XTAL    |

| TM0_ACI0    | TIMER0 Alternate Capture Input 0     | С         | PC_03       |

| TM0_ACI1    | TIMERO Alternate Capture Input 1     | В         | PB_01       |

| TM0_ACI2    | TIMERO Alternate Capture Input 2     | С         | PC_07       |

| TM0_ACI3    | TIMERO Alternate Capture Input 3     | В         | PB_09       |

| TM0_ACI4    | TIMERO Alternate Capture Input 4     | С         | PC_01       |

| TM0_ACI5    | TIMERO Alternate Capture Input 5     | С         | PC_02       |

| TM0_ACI6    | TIMERO Alternate Capture Input 6     | A         | PA_12       |

| TM0_ACLK0   | TIMERO Alternate Clock 0             | C         | PC_04       |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

|                   |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power    | Description                                                                                                                                          |

|-------------------|------|--------|------|-------|-------|-------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name       | Туре | Туре   | Term | Term  | Drive | Term  | Drive | Domain   | and Notes                                                                                                                                            |

| GND_HADC          | g    | na     | none | none  | none  | none  | none  | na       | Desc: Ground HADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                               |

| HADC0_VIN0        | a    | na     | none | none  | none  | none  | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 0<br>Notes: If HADC is not used, connect to<br>ground.                                                           |

| HADC0_VIN1        | a    | na     | none | none  | none  | none  | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 1<br>Notes: If HADC is not used, connect to<br>ground.                                                           |

| HADC0_VIN2        | a    | na     | none | none  | none  | none  | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 2<br>Notes: If HADC is not used, connect to<br>ground.                                                           |

| HADC0_VIN3        | a    | na     | none | none  | none  | none  | none  | VDD_HADC | Desc: HADC0 Analog Input at channel 3<br>Notes: If HADC is not used, connect to<br>ground.                                                           |

| HADC0_VREFN       | a    | na     | none | none  | none  | none  | none  | VDD_HADC | Desc: HADC0 Ground Reference for<br>ADC<br>Notes: If HADC is not used, connect to                                                                    |

| HADC0_VREFP       | a    | na     | none | none  | none  | none  | none  | VDD_HADC | ground.  Desc: HADC0 External Reference for ADC  Notes: If HADC is not used, connect to ground.                                                      |

| JTG_TCK_<br>SWCLK | I/O  | na     | pd   | none  | none  | none  | none  | VDD_EXT  | Desc: JTAG Clock   Serial Wire Clock<br>Notes: Functional during reset.                                                                              |

| JTG_TDI           | I/O  | na     | pu   | none  | none  | none  | none  | VDD_EXT  | Desc: JTAG Serial Data In Notes: Functional during reset.                                                                                            |

| JTG_TDO_SWO       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT  | Desc: JTAG Serial Data Out   Serial Wire<br>Out<br>Notes: Functional during reset, three-                                                            |

| JTG_TMS_<br>SWDIO | I/O  | A      | pu   | none  | none  | none  | none  | VDD_EXT  | state when JTG_TRST is asserted.  Desc: JTAG Mode Select   Serial Wire DIO  Notes: Functional during reset.                                          |

| JTG_TRST          | I/O  | na     | pd   | none  | none  | none  | none  | VDD_EXT  | Desc: JTAG Reset Notes: Functional during reset, a 10k external pull-down may be used to shorten the t <sub>VDDEXT_RST</sub> timing requirement.     |

| PA_00             | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT  | Desc: SPI1 Clock   TRACE0 Trace Data 7   SMC0 Byte Enable 0 Notes: SPI clock requires a pull-down when controlling most SPI flash devices.           |

| PA_01             | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT  | Desc: SPI1 Master In, Slave Out   TRACE0<br>Trace Data 6   SMC0 Byte Enable 1<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used. |

Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                                                                                                                                                                                                                                    |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_05       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Frame Sync   TM0 Timer 3   MSI0 Command Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                        |

| PC_06       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Data 0   SPI0 Master In, Slave Out   MSI0 Data 3 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                               |

| PC_07       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Frame Sync   SPI0 Master Out, Slave In   MSI0 Data 2   TM0 Alternate Capture Input 2 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                           |

| PC_08       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Data 0   SPI0 Data 2   MSI0 Data 0 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                             |

| PC_09       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Clock   SPI0 Data 3   MSI0 Clock   TM0 Alternate Clock 2 Notes: No notes.                                                                                                                                                                           |

| PC_10       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Clock   MSI0 Data 4   SPI1 Slave Select Output 3   TM0 Alternate Clock 1 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details. SPI slave select outputs require a pull-up when used. |

| PC_11       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Frame Sync   MSI0 Data 5   SPI0 Slave Select Output 3 Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details. SPI slave select outputs require a pull-up when used.                    |

| PC_12       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 0   MSI0 Data 6  Notes: An external pull-up may be required for MSI modes, see the MSI chapter in the hardware reference for details.                                                                                                          |

**Table 18. Peripheral Clock Operating Conditions**

| Parameter                 |                                                                       | Restriction                    | Min | Тур | Max | Unit |

|---------------------------|-----------------------------------------------------------------------|--------------------------------|-----|-----|-----|------|

| f <sub>OCLK</sub>         | Output Clock Frequency                                                |                                |     |     | 50  | MHz  |

| $f_{\text{SYS\_CLKOUTJ}}$ | SYS_CLKOUT Period Jitter <sup>1, 2</sup>                              |                                |     | ±2  |     | %    |

| $f_{\text{PCLKPROG}}$     | Programmed PPI Clock When Transmitting Data and Frame Sync            |                                |     |     | 50  | MHz  |

| $f_{PCLKPROG}$            | Programmed PPI Clock When Receiving Data or Frame Sync                |                                |     |     | 50  | MHz  |

| $f_{\text{PCLKEXT}}$      | External PPI Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{PCLKEXT} \le f_{SCLK0}$    |     |     | 50  | MHz  |

| $f_{\text{PCLKEXT}}$      | External PPI Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{PCLKEXT} \le f_{SCLK0}$    |     |     | 50  | MHz  |

| $f_{\text{SPTCLKPROG}}$   | Programmed SPT Clock When Transmitting Data and Frame Sync            |                                |     |     | 50  | MHz  |

| $f_{\text{SPTCLKPROG}}$   | Programmed SPT Clock When Receiving Data or Frame Sync                |                                |     |     | 50  | MHz  |

| $f_{\text{SPTCLKEXT}}$    | External SPT Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{SPTCLKEXT} \leq f_{SCLK0}$ |     |     | 50  | MHz  |

| $f_{\text{SPTCLKEXT}}$    | External SPT Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{SPTCLKEXT} \le f_{SCLK0}$  |     |     | 50  | MHz  |

| $f_{\text{SPICLKPROG}}$   | Programmed SPI Clock When Transmitting Data                           |                                |     |     | 50  | MHz  |

| $f_{SPICLKPROG}$          | Programmed SPI Clock When Receiving Data                              |                                |     |     | 50  | MHz  |

| $f_{SPICLKEXT}$           | External SPI Clock When Receiving Data <sup>3, 4</sup>                | $f_{SPICLKEXT} \leq f_{SCLK0}$ |     |     | 50  | MHz  |

| $f_{\text{SPICLKEXT}}$    | External SPI Clock When Transmitting Data <sup>3, 4</sup>             | $f_{SPICLKEXT} \leq f_{SCLK0}$ |     |     | 50  | MHz  |

| $f_{MSICLKPROG}$          | Programmed MSI Clock                                                  |                                |     |     | 50  | MHz  |

<sup>&</sup>lt;sup>1</sup> SYS\_CLKOUT jitter is dependent on the application system design including pin switching activity, board layout, and the jitter characteristics of the SYS\_CLKIN source. Due to the dependency on these factors the measured jitter may be higher or lower than this typical specification for each end application.

<sup>&</sup>lt;sup>4</sup>The peripheral external clock frequency must also be less than or equal to the f<sub>SCLK</sub> that clocks the peripheral.

Figure 6. Clock Relationships and Divider Values

Table 19. Phase-Locked Loop Operating Conditions

| Parameter                 |                     | Min   | Max | Unit |

|---------------------------|---------------------|-------|-----|------|

| f <sub>PLLCLK</sub>       | PLL Clock Frequency | 230.2 | 800 | MHz  |

| CGU_CTL.MSEL <sup>1</sup> | PLL Multiplier      | 8     | 41  |      |

$<sup>^1</sup>$ The CGU\_CTL.MSEL setting must also be chosen to ensure that the  $f_{PLLCLK}$  specification is not violated.

<sup>&</sup>lt;sup>2</sup> The value in the Typ field is the percentage of the SYS\_CLKOUT period.

<sup>&</sup>lt;sup>3</sup> The maximum achievable frequency for any peripheral in external clock mode is dependent on being able to meet the setup and hold times in the ac timing specifications section for that peripheral. Pay particular attention to setup and hold times for VDD\_EXT = 1.8 V which may preclude the maximum frequency listed here.

#### PACKAGE INFORMATION

The information presented in Figure 7 and Table 27 provides details about package branding. For a complete listing of product availability, see the Ordering Guide.

Figure 7. Product Information on Package<sup>1</sup>

Table 27. Package Brand Information

| Brand Key  | Field Description          |

|------------|----------------------------|

| ADSP-BF70x | Product model              |

| t          | Temperature range          |

| рр         | Package type               |

| Z          | RoHS compliant designation |

| ccc        | See Ordering Guide         |

| vvvvv.x    | Assembly lot code          |

| n.n        | Silicon revision           |

| yyww       | Date code                  |

## **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 28 may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Table 28. Absolute Maximum Ratings

| Parameter                                            | Rating             |

|------------------------------------------------------|--------------------|

| Internal Supply Voltage (V <sub>DD_INT</sub> )       | -0.33 V to +1.20 V |

| External (I/O) Supply Voltage (V <sub>DD_EXT</sub> ) | -0.33 V to +3.60 V |

| DDR2 Controller Supply Voltage                       | -0.33 V to +1.90 V |

| $(V_{DD\_DMC})$                                      |                    |

| USB PHY Supply Voltage ( $V_{DD\_USB}$ )             | -0.33 V to +3.60 V |

| Real-Time Clock Supply Voltage                       | -0.33 V to +3.60 V |

| $(V_{DD\_RTC})$                                      |                    |

| Housekeeping ADC Supply Voltage                      | -0.33 V to +3.60 V |

| $(V_{DD\_HADC})$                                     |                    |

| One-Time Programmable Memory                         | -0.33 V to +3.60 V |

| Supply Voltage (V <sub>DD_OTP</sub> )                |                    |

| HADC Reference Voltage (V <sub>HADC_REF</sub> )      | -0.33 V to +3.60 V |

Table 28. Absolute Maximum Ratings (Continued)

| Parameter                                                        | Rating                                           |

|------------------------------------------------------------------|--------------------------------------------------|

| DDR2 Reference Voltage (V <sub>DDR_REF</sub> )                   | -0.33 V to +1.90 V                               |

| Input Voltage <sup>1, 2</sup>                                    | -0.33 V to +3.60 V                               |

| TWI Input Voltage <sup>2, 3</sup>                                | -0.33 V to +5.50 V                               |

| USB0_Dx Input Voltage <sup>4</sup>                               | -0.33 V to +5.25 V                               |

| USB0_VBUS Input Voltage⁵                                         | -0.33 V to +6 V                                  |

| DDR2 Input Voltage⁵                                              | -0.33 V to +1.90 V                               |

| Output Voltage Swing                                             | $-0.33 \text{ V to V}_{DD\_EXT} + 0.5 \text{ V}$ |

| I <sub>OH</sub> /I <sub>OL</sub> Current per Signal <sup>1</sup> | 4 mA (max)                                       |

| Storage Temperature Range                                        | -65°C to +150°C                                  |

| Junction Temperature While Biased                                | +125°C                                           |

<sup>&</sup>lt;sup>1</sup> Applies to 100% transient duty cycle.

### **ESD SENSITIVITY**

### ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup> Exact brand may differ, depending on package type.

$<sup>^2</sup>$  Applies only when  $V_{DD\_EXT}$  is within specifications. When  $V_{DD\_EXT}$  is outside specifications, the range is  $V_{DD\_EXT}\pm0.2~V.$

<sup>&</sup>lt;sup>3</sup> Applies to balls TWI\_SCL and TWI\_SDA.

<sup>&</sup>lt;sup>4</sup> If the USB is not used, connect USB0\_Dx and USB0\_VBUS according to Table 15 on Page 38.

$<sup>^5</sup>$  Applies only when  $V_{DD\_DMC}$  is within specifications. When  $V_{DD\_DMC}$  is outside specifications, the range is  $V_{DD\_DMC}\pm0.2~V.$

### TIMING SPECIFICATIONS

Specifications are subject to change without notice.

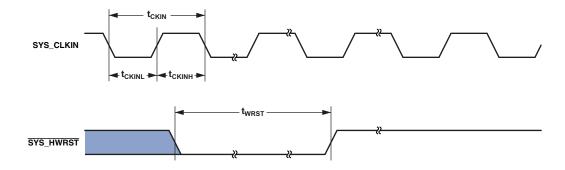

### **Clock and Reset Timing**

Table 29 and Figure 8 describe clock and reset operations related to the clock generation unit (CGU). Per the CCLK, SYSCLK, SCLK0, SCLK1, DCLK, and OCLK timing specifications in Table 17 on Page 51 and Table 18 on Page 52, combinations of SYS\_CLKIN and clock multipliers must not select clock rates in excess of the processor's maximum instruction rate.

Table 29. Clock and Reset Timing

|                    |                                                                            | 1.                     | V <sub>DD_EXT</sub><br>8 V Nominal | 3.3                  | V <sub>DD_EXT</sub><br>3 V Nominal |      |

|--------------------|----------------------------------------------------------------------------|------------------------|------------------------------------|----------------------|------------------------------------|------|

| Paramete           | r                                                                          | Min                    | Max                                | Min                  | Max                                | Unit |

| Timing Red         | quirement                                                                  |                        |                                    |                      |                                    |      |

| $f_{\text{CKIN}}$  | SYS_CLKIN Crystal Frequency (CGU_CTL.DF = 0) <sup>1, 2, 3</sup>            | 19.2                   | 35                                 | 19.2                 | 50                                 | MHz  |

| $f_{\text{CKIN}}$  | SYS_CLKIN Crystal Frequency (CGU_CTL.DF = 1) <sup>1, 2, 3</sup>            | N/A                    | N/A                                | 38.4                 | 50                                 | MHz  |

| $f_{\text{CKIN}}$  | SYS_CLKIN External Source Frequency (CGU_CTL.DF = $0$ ) <sup>1, 2, 3</sup> | 19.2                   | 60                                 | 19.2                 | 60                                 | MHz  |

| $f_{\text{CKIN}}$  | SYS_CLKIN External Source Frequency (CGU_CTL.DF = 1) <sup>1, 2, 3</sup>    | 38.4                   | 60                                 | 38.4                 | 60                                 | MHz  |

| $t_{CKINL}$        | SYS_CLKIN Low Pulse <sup>1</sup>                                           | 8.33                   |                                    | 8.33                 |                                    | ns   |

| t <sub>CKINH</sub> | SYS_CLKIN High Pulse <sup>1</sup>                                          | 8.33                   |                                    | 8.33                 |                                    | ns   |

| $t_{WRST}$         | SYS_HWRST Asserted Pulse Width Low <sup>4</sup>                            | 11 × t <sub>CKII</sub> | N                                  | $11 \times t_{CKIN}$ | 1                                  | ns   |

<sup>&</sup>lt;sup>1</sup> Applies to PLL bypass mode and PLL nonbypass mode.

<sup>&</sup>lt;sup>4</sup> Applies after power-up sequence is complete. See Table 30 and Figure 9 for power-up reset timing.

Figure 8. Clock and Reset Timing

$<sup>^2</sup>$  The  $t_{CKIN}$  period (see Figure 8) equals  $1/f_{CKIN}$ .

$<sup>^3</sup>$  Combinations of the CLKIN frequency and the PLL clock multiplier must not exceed the allowed  $f_{PLLCLK}$  setting discussed in Table 19.

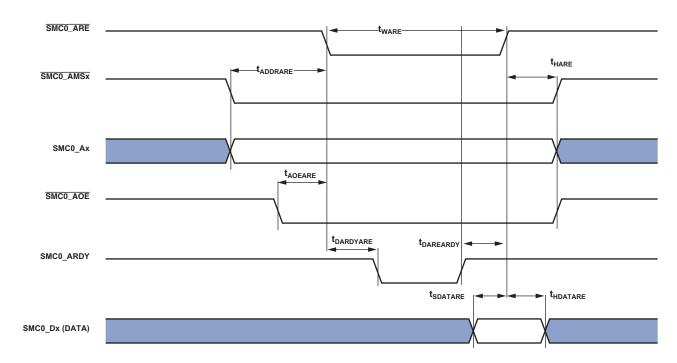

Figure 10. Asynchronous Read

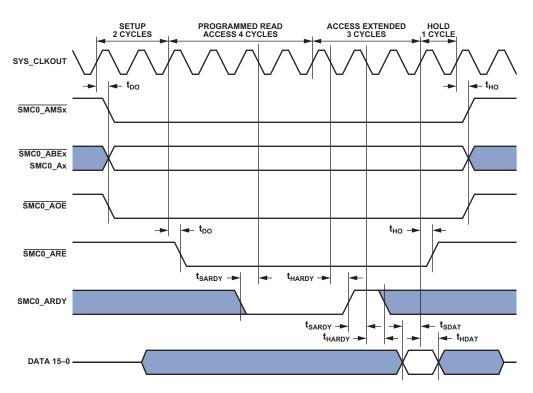

## SMC Read Cycle Timing With Reference to SYS\_CLKOUT

The following SMC specifications with respect to SYS\_CLKOUT are given to accommodate the connection of the SMC to programmable logic devices. These specifications assume that SYS\_CLKOUT is outputting a buffered version of SCLK0 by setting CGU\_CLKOUTSEL.CLKOUTSEL = 0x3. However, SCLK0 must not run faster than the maximum  $f_{OCLK}$  specification. For this example, RST = 0x2, RAT = 0x4, and RHT = 0x1.

Table 32. SMC Read Cycle Timing With Reference to SYS\_CLKOUT (BxMODE = b#00)

|                    |                                            | 1.8  | V <sub>DD_EXT</sub><br>BV Nominal | 3.3  | V <sub>DD_EXT</sub><br>BV Nominal |      |

|--------------------|--------------------------------------------|------|-----------------------------------|------|-----------------------------------|------|

| Paramet            | er                                         | Min  | Max                               | Min  | Max                               | Unit |

| Timing Re          | equirements                                |      |                                   |      |                                   |      |

| $t_{\text{SDAT}}$  | SMC0_Dx Setup Before SYS_CLKOUT            | 5.3  |                                   | 4.3  |                                   | ns   |

| $t_{HDAT}$         | SMC0_Dx Hold After SYS_CLKOUT              | 1.5  |                                   | 1.5  |                                   | ns   |

| t <sub>SARDY</sub> | SMC0_ARDY Setup Before SYS_CLKOUT          | 16.6 |                                   | 14.4 |                                   | ns   |

| $t_{HARDY}$        | SMC0_ARDY Hold After SYS_CLKOUT            | 0.7  |                                   | 0.7  |                                   | ns   |

| Switching          | Characteristics                            |      |                                   |      |                                   |      |

| $t_{DO}$           | Output Delay After SYS_CLKOUT <sup>1</sup> |      | 7                                 |      | 7                                 | ns   |

| $t_{HO}$           | Output Hold After SYS_CLKOUT 1             | -2.5 |                                   | -2.5 |                                   | ns   |

$<sup>^1</sup>$  Output signals are SMC0\_Ax,  $\overline{SMC0\_AMSx}, \overline{SMC0\_AOE},$  and  $\overline{SMC0\_ABEx}.$

Figure 11. Asynchronous Memory Read Cycle Timing

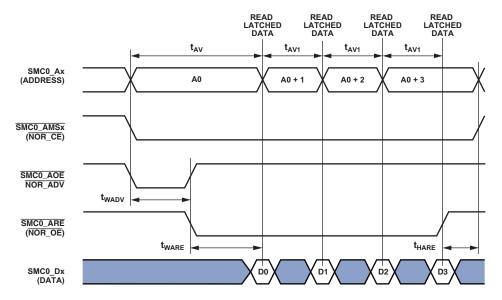

## Asynchronous Page Mode Read

Table 34 and Figure 13 show asynchronous memory page mode read timing, related to the static memory controller (SMC).

Table 34. Asynchronous Page Mode Read

|                     |                                                                    | V <sub>DD_EXT</sub> 1.8 V /3.3 V Nomina             |     |      |

|---------------------|--------------------------------------------------------------------|-----------------------------------------------------|-----|------|

| Parame              | ter                                                                | Min                                                 | Max | Unit |

| Switchin            | g Characteristics                                                  |                                                     |     |      |

| $t_{AV}$            | SMC0_Ax (Address) Valid for First Address Min Width <sup>1</sup>   | $(PREST + RST + PREAT + RAT) \times t_{SCLK0} - 2$  |     | ns   |

| t <sub>AV1</sub>    | SMC0_Ax (Address) Valid for Subsequent SMC0_Ax (Address) Min Width | PGWS × t <sub>SCLK0</sub> – 2                       |     | ns   |

| t <sub>WADV</sub>   | SMC0_NORDV Active Low Width <sup>2</sup>                           | $RST \times t_{SCLK0} - 2$                          |     | ns   |

| t <sub>HARE</sub>   | Output <sup>3</sup> Hold After SMC0_ARE High <sup>4</sup>          | RHT × t <sub>SCLK0</sub> – 2                        |     | ns   |

| t <sub>WARE</sub> 5 | SMC0_ARE Active Low Width <sup>6</sup>                             | $(RAT + (Nw - 1) \times PGWS) \times t_{SCLK0} - 2$ |     | ns   |

<sup>1</sup> PREST, RST, PREAT and RAT values set using the SMC\_BxETIM.PREST bits, SMC\_BxTIM.RST bits, SMC\_BxETIM.PREAT bits, and the SMC\_BxTIM.RAT bits.

<sup>&</sup>lt;sup>6</sup>RAT value set using the SMC\_BxTIM.RAT bits.

Figure 13. Asynchronous Page Mode Read

<sup>&</sup>lt;sup>2</sup>RST value set using the SMC\_BxTIM.RST bits.

<sup>&</sup>lt;sup>3</sup> Output signals are SMC0\_Ax, SMC0\_AMSx, SMC0\_AOE.

<sup>&</sup>lt;sup>4</sup>RHT value set using the SMC\_BxTIM.RHT bits.

$<sup>^{5}</sup>$  SMC\_BxCTL.ARDYEN bit = 0.

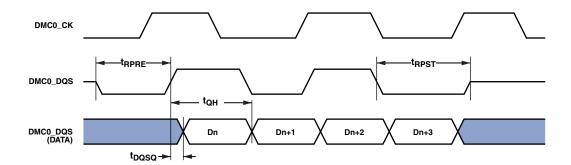

## **Mobile DDR SDRAM Read Cycle Timing**

Table 43 and Figure 21 show mobile DDR SDRAM read cycle timing, related to the dynamic memory controller (DMC).

Table 43. Mobile DDR SDRAM Read Cycle Timing,  $V_{DD\_DMC}$  Nominal 1.8  $\rm V$

|                   |                                                                   |     | 200 MHz |                 |

|-------------------|-------------------------------------------------------------------|-----|---------|-----------------|

| Parameter         |                                                                   | Min | Max     | Unit            |

| Timing Requirer   | ments                                                             |     |         |                 |

| $t_QH$            | DMC0_DQ, DMC0_DQS Output Hold Time From DMC0_DQS                  | 1.5 |         | ns              |

| t <sub>DQSQ</sub> | DMC0_DQS-DMC0_DQ Skew for DMC0_DQS and Associated DMC0_DQ Signals |     | 0.7     | ns              |

| t <sub>RPRE</sub> | Read Preamble                                                     | 0.9 | 1.1     | t <sub>CK</sub> |

| t <sub>RPST</sub> | Read Postamble                                                    | 0.4 | 0.6     | t <sub>CK</sub> |

Figure 21. Mobile DDR SDRAM Controller Input AC Timing

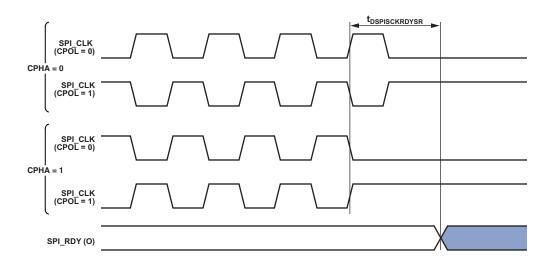

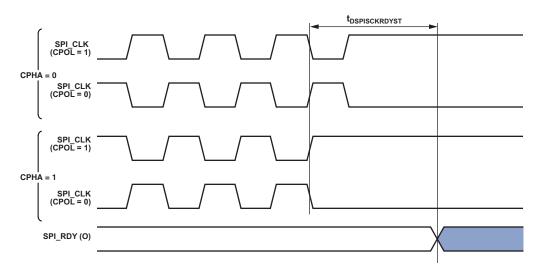

## Serial Peripheral Interface (SPI) Port—SPI\_RDY Slave Timing

Table 56. SPI Port—SPI\_RDY Slave Timing

|                           |                                                                           | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal |                                     |      |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|------|

| Parameter                 |                                                                           | Min                                        | Max                                 | Unit |

| Switching C               | haracteristics                                                            |                                            |                                     |      |

| t <sub>DSPISCKRDYSR</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Receive  | $2.5 \times t_{SCLK0} + t_{HDSPID}$        | $3.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

| t <sub>DSPISCKRDYST</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Transmit | $3.5 \times t_{SCLK0} + t_{HDSPID}$        | $4.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

$Figure~33.~~SPI\_RDY~De-assertion~from~Valid~Input~SPI\_CLK~Edge~in~Slave~Mode~Receive~(FCCH=0)$

Figure 34. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Transmit (FCCH = 1)

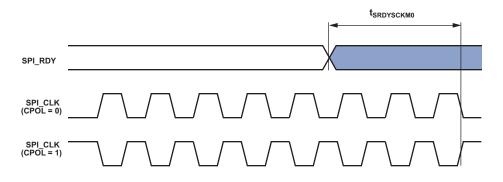

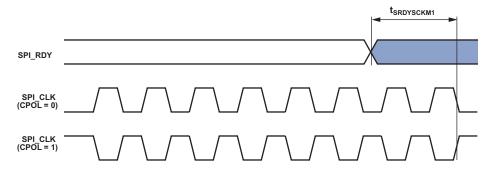

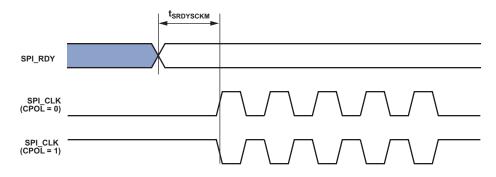

## Serial Peripheral Interface (SPI) Port—SPI\_RDY Timing

SPI\_RDY is used to provide flow control. The CPOL and CPHA bits are set in SPI\_CTL, while LEADX, LAGX, and STOP are in SPI\_DLY.

Table 59. SPI Port—SPI\_RDY Timing

|                        |                                                                                                                                                                | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal            |                                                     |      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|------|

| Paramete               | er                                                                                                                                                             | Min                                                   | Max                                                 | Unit |

| Timing Re              | quirements                                                                                                                                                     |                                                       |                                                     |      |

| t <sub>SRDYSCKM0</sub> | Minimum Setup Time for SPI_RDY De-assertion in Master Mode Before Last SPI_CLK Edge of Valid Data Transfer to Block Subsequent Transfer with CPHA = 0          | $(2.5 + 1.5 \times BAUD^{1}) \times t_{SCLK0} + 14.5$ |                                                     | ns   |

| t <sub>SRDYSCKM1</sub> | Minimum Setup Time for SPI_RDY De-assertion in<br>Master Mode Before Last SPI_CLK Edge of Valid<br>Data Transfer to Block Subsequent Transfer with<br>CPHA = 1 | $(2.5 + BAUD^1) \times t_{SCLK0} + 14.5$              |                                                     | ns   |

| Switching              | Characteristic                                                                                                                                                 |                                                       |                                                     |      |

| t <sub>SRDYSCKM</sub>  | Time Between Assertion of SPI_RDY by Slave and First Edge of SPI_CLK for New SPI Transfer with CPHA = 0 and BAUD = 0 (STOP, LEADX, LAGX = 0)                   | $3 \times t_{SCLK0}$                                  | $4 \times t_{SCLK0} + 17.5$                         | ns   |

|                        | Time Between Assertion of SPI_RDY by Slave and First Edge of SPI_CLK for New SPI Transfer with CPHA = 0 and BAUD ≥ 1 (STOP, LEADX, LAGX = 0)                   | $(4 + 1.5 \times BAUD^1) \times t_{SCLKO}$            | $(5 + 1.5 \times BAUD^{1}) \times t_{SCLK0} + 17.5$ | ns   |

|                        | Time Between Assertion of SPI_RDY by Slave and First Edge of SPI_CLK for New SPI Transfer with CPHA = 1 (STOP, LEADX, LAGX = 0)                                | $(3 + 0.5 \times BAUD^1) \times t_{SCLKO}$            | $(4 + 0.5 \times BAUD^{1}) \times t_{SCLK0} + 17.5$ | ns   |

$<sup>^{1}\,\</sup>mathrm{BAUD}$  value set using the SPI\_CLK.BAUD bits.

Figure 37. SPI\_RDY Setup Before SPI\_CLK with CPHA = 0

Figure 38. SPI\_RDY Setup Before SPI\_CLK with CPHA = 1

Figure 39.  $SPI\_CLK$  Switching Diagram after  $SPI\_RDY$  Assertion, CPHA = x

## PLANNED AUTOMOTIVE PRODUCTION PRODUCTS

| -                        |                 |             | Temperature        |                     | Package  |

|--------------------------|-----------------|-------------|--------------------|---------------------|----------|

| Model <sup>1, 2, 3</sup> | Max. Core Clock | L2 SRAM     | Grade <sup>4</sup> | Package Description | Option   |

| ADBF702WCCPZ3xx          | 300 MHz         | 256K bytes  | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF702WCCPZ4xx          | 400 MHz         | 256K bytes  | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF703WCBCZ3xx          | 300 MHz         | 256K bytes  | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF703WCBCZ4xx          | 400 MHz         | 256K bytes  | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF704WCCPZ3xx          | 300 MHz         | 512K bytes  | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF704WCCPZ4xx          | 400 MHz         | 512K bytes  | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF705WCBCZ3xx          | 300 MHz         | 512K bytes  | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF705WCBCZ4xx          | 400 MHz         | 512K bytes  | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF706WCCPZ3xx          | 300 MHz         | 1024K bytes | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF706WCCPZ4xx          | 400 MHz         | 1024K bytes | -40°C to +105°C    | 88-Lead LFCSP_VQ    | CP-88-8  |

| ADBF707WCBCZ3xx          | 300 MHz         | 1024K bytes | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

| ADBF707WCBCZ4xx          | 400 MHz         | 1024K bytes | -40°C to +105°C    | 184-Ball CSP_BGA    | BC-184-1 |

$<sup>^1</sup>$  Select Automotive grade products, supporting  $-40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$  T\_{AMBIENT} condition, will be available when they appear in the Automotive Products table.  $^2$  Z = RoHS Compliant Part.

$<sup>^3\,\</sup>mathrm{xx}$  denotes the current die revision.

<sup>&</sup>lt;sup>4</sup> Referenced temperature is ambient temperature. The ambient temperature is not a specification. See Operating Conditions on Page 50 for the junction temperature (T<sub>J</sub>) specification which is the only temperature specification.