Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 400MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 512kB                                                                                     |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf705kbcz-4                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **GENERAL DESCRIPTION**

The ADSP-BF70x processor is a member of the Blackfin<sup>®</sup> family of products. The Blackfin processor combines a dual-MAC 16-bit state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture. New enhancements to the Blackfin+ core add 32-bit MAC and 16-bit complex MAC support, cache enhancements, branch prediction and other instruction set improvements—all while maintaining instruction set compatibility to previous Blackfin products. The processor offers performance up to 400 MHz, as well as low static power consumption. Produced with a low-power and low-voltage design methodology, they provide world-class power management and performance.

By integrating a rich set of industry-leading system peripherals and memory (shown in Table 1), the Blackfin processor is the platform of choice for next-generation applications that require RISC-like programmability, multimedia support, and leadingedge signal processing in one integrated package. These applications span a wide array of markets, from automotive systems to embedded industrial, instrumentation, video/image analysis, biometric and power/motor control applications.

#### Table 1. Processor Comparison

| D                              | ocessor Feature                                            | ADSP-   | ADSP-        | ADSP-   | ADSP-    | ADSP-<br>BF704 | ADSP-    | ADSP-   | ADSP-    |  |

|--------------------------------|------------------------------------------------------------|---------|--------------|---------|----------|----------------|----------|---------|----------|--|

|                                |                                                            | BF700   | <b>BF701</b> | BF702   | BF703    |                | BF705    | BF706   | BF707    |  |

|                                | ximum Speed Grade (MHz) <sup>1</sup><br>ximum SYSCLK (MHz) |         | 00           | 400 200 |          |                |          |         |          |  |

|                                |                                                            | 88-Lead | 184-Ball     | 88-Lead | 184-Ball | 2<br>88-Lead   | 184-Ball | 88-Lead | 184-Ball |  |

| Pd                             | ckage Options                                              | LFCSP   | CSP_BGA      | LFCSP   | CSP_BGA  | LFCSP          | CSP_BGA  | LFCSP   | CSP_BGA  |  |

| GP                             | IOs                                                        | 43      | 47           | 43      | 47       | 43             | 47       | 43      | 47       |  |

|                                | L1 Instruction SRAM                                        |         | •            |         | 48       | 3K             | •        |         | •        |  |

| _                              | L1 Instruction SRAM/Cache                                  |         |              |         | 16       | 5K             |          |         |          |  |

| Memory (bytes)                 | L1 Data SRAM                                               |         |              |         | 32       | 2K             |          |         |          |  |

| (d)                            | L1 Data SRAM/Cache                                         |         |              |         | 32       | 2K             |          |         |          |  |

| (Jor                           | L1 Scratchpad (L1 Data C)                                  |         |              |         | 8        | К              |          |         |          |  |

| Aem                            | L2 SRAM                                                    | 12      | 28K          | 25      | 6K       | 51             | 2K       | 10      | 24K      |  |

| 2                              | L2 ROM                                                     |         |              |         | 51       | 2K             |          |         |          |  |

|                                | DDR2/LPDDR (16-bit)                                        | No      | Yes          | No      | Yes      | No             | Yes      | No      | Yes      |  |

| I <sup>2</sup> C               |                                                            | 1       |              |         |          |                |          |         |          |  |

| Up                             | /Down/Rotary Counter                                       | 1       |              |         |          |                |          |         |          |  |

| GP                             | Timer                                                      | 8       |              |         |          |                |          |         |          |  |

| Wa                             | itchdog Timer                                              | 1       |              |         |          |                |          |         |          |  |

| GP                             | Counter                                                    | 1       |              |         |          |                |          |         |          |  |

| SP                             | ORTs                                                       | 2       |              |         |          |                |          |         |          |  |

| Qı                             | ad SPI                                                     |         |              |         |          | 2              |          |         |          |  |

| Du                             | al SPI                                                     |         |              |         |          | 1              |          |         |          |  |

| SP                             | Host Port                                                  |         |              |         |          | 1              |          |         |          |  |

| US                             | B 2.0 HS OTG                                               |         |              |         |          | 1              |          |         |          |  |

| Pa                             | rallel Peripheral Interface                                |         |              |         |          | 1              |          |         |          |  |

| CA                             | Ν                                                          |         |              |         |          | 2              |          |         |          |  |

| UA                             | RT                                                         | 2       |              |         |          |                |          |         |          |  |

| Re                             | al-Time Clock                                              |         |              |         |          | 1              |          |         |          |  |

| Static Memory Controller (SMC) |                                                            |         | Yes          |         |          |                |          |         |          |  |

| Se                             | curity Crypto Engine                                       |         | 1            |         | Ye       | es             | 1        |         | •        |  |

| SD                             | /SDIO (MSI)                                                | 4-bit   | 8-bit        | 4-bit   | 8-bit    | 4-bit          | 8-bit    | 4-bit   | 8-bit    |  |

| 4-(                            | Channel 12-Bit ADC                                         | No      | Yes          | No      | Yes      | No             | Yes      | No      | Yes      |  |

<sup>1</sup>Other speed grades available.

The CAN controller offers the following features:

- 32 mailboxes (8 receive only, 8 transmit only, 16 configurable for receive or transmit)

- Dedicated acceptance masks for each mailbox

- Additional data filtering on first two bytes

- Support for both the standard (11-bit) and extended (29-bit) identifier (ID) message formats

- Support for remote frames

- Active or passive network support

- CAN wake-up from hibernation mode (lowest static power consumption mode)

- Interrupts, including: TX complete, RX complete, error and global

An additional crystal is not required to supply the CAN clock, as the CAN clock is derived from a system clock through a programmable divider.

### USB 2.0 On-the-Go Dual-Role Device Controller

The USB 2.0 on-the-go (OTG) dual-role device controller provides a low-cost connectivity solution for the growing adoption of this bus standard in industrial applications, as well as consumer mobile devices such as cell phones, digital still cameras, and MP3 players. The USB 2.0 controller allows these devices to transfer data using a point-to-point USB connection without the need for a PC host. The module can operate in a traditional USB peripheral-only mode as well as the host mode presented in the OTG supplement to the USB 2.0 specification.

The USB clock is provided through a dedicated external crystal or crystal oscillator.

The USB OTG dual-role device controller includes a phase locked loop with programmable multipliers to generate the necessary internal clocking frequency for USB.

### Housekeeping ADC (HADC)

The HADC provides a general-purpose, multichannel successive approximation analog-to-digital converter. It supports the following features:

- 12-bit ADC core (10-bit accuracy) with built-in sample and hold

- 4 single-ended input channels

- Throughput rates up to 1 MSPS

- Single external reference with analog inputs between 0 V and 3.3 V

- Selectable ADC clock frequency including the ability to program a prescaler

- Adaptable conversion type: allows single or continuous conversion with option of autoscan

- Auto sequencing capability with up to 4 autoconversions in a single session. Each conversion can be programmed to select any input channel.

- Four data registers (individually addressable) to store conversion values

### System Crossbars (SCB)

The system crossbars (SCB) are the fundamental building blocks of a switch-fabric style for (on-chip) system bus interconnection. The SCBs connect system bus masters to system bus slaves, providing concurrent data transfer between multiple bus masters and multiple bus slaves. A hierarchical model built from multiple SCBs—provides a power and area efficient system interconnect, which satisfies the performance and flexibility requirements of a specific system.

The SCBs provide the following features:

- Highly efficient, pipelined bus transfer protocol for sustained throughput

- Full-duplex bus operation for flexibility and reduced latency

- Concurrent bus transfer support to allow multiple bus masters to access bus slaves simultaneously

- Protection model (privileged/secure) support for selective bus interconnect protection

### POWER AND CLOCK MANAGEMENT

The processor provides three operating modes, each with a different performance/power profile. Control of clocking to each of the processor peripherals also reduces power consumption. See Table 5 for a summary of the power settings for each mode.

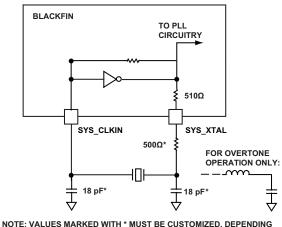

### System Crystal Oscillator and USB Crystal Oscillator

The processor can be clocked by an external crystal (see Figure 4), a sine wave input, or a buffered, shaped clock derived from an external clock oscillator. If an external clock is used, it should be a TTL compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the SYS\_CLKIN pin of the processor. When an external clock is used, the SYS\_XTAL pin must be left unconnected. Alternatively, because the processor includes an on-chip oscillator circuit, an external crystal may be used.

For fundamental frequency operation, use the circuit shown in Figure 4. A parallel-resonant, fundamental frequency, microprocessor grade crystal is connected across the SYS\_CLKIN and SYS\_XTAL pins. The on-chip resistance between SYS\_CLKIN and the SYS\_XTAL pin is in the 500 k $\Omega$  range. Further parallel resistors are typically not recommended.

The two capacitors and the series resistor shown in Figure 4 fine-tune phase and amplitude of the sine frequency. The capacitor and resistor values shown in Figure 4 are typical values only. The capacitor values are dependent upon the load capacitance recommendations of the crystal manufacturer and the PCB physical layout. The resistor value depends on the drive

level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations on multiple devices over the required temperature range.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18pF SHOULD BE TREATED AS A MAXIMUM.

Figure 4. External Crystal Connection

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone by adding a tuned inductor circuit as shown in Figure 4. A design procedure for third-overtone operation is discussed in detail in application note (EE-168) *Using Third Overtone Crystals with the ADSP-218x DSP* (www.analog.com/ee-168).

The same recommendations may be used for the USB crystal oscillator.

### **Real-Time Clock**

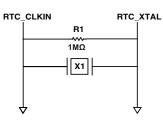

The real-time clock (RTC) provides a robust set of digital watch features, including current time, stopwatch, and alarm. The RTC is clocked by a 32.768 kHz crystal external to the processor. Connect RTC pins RTC\_CLKIN and RTC\_XTAL with external components as shown in Figure 5.

The RTC peripheral has dedicated power supply pins so that it can remain powered up and clocked even when the rest of the processor is in a low power state. The RTC provides several programmable interrupt options, including interrupt per second, minute, hour, or day clock ticks, interrupt on programmable stopwatch countdown, or interrupt at a programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60-second counter, a 60-minute counter, a 24-hour counter, and a 32,768-day counter. When the alarm interrupt is enabled, the alarm function generates an interrupt when the output of the timer matches the programmed value in the alarm control register. There are two alarms. The first alarm is for a time of day. The second alarm is for a specific day and time of that day.

NOTE: CRYSTAL LOAD CAPACITORS ARE NOT NECESSARY IN MOST CASES.

Figure 5. External Components for RTC

The stopwatch function counts down from a programmed value, with one-second resolution. When the stopwatch interrupt is enabled and the counter underflows, an interrupt is generated.

### **Clock Generation**

The clock generation unit (CGU) generates all on-chip clocks and synchronization signals. Multiplication factors are programmed to define the PLLCLK frequency. Programmable values divide the PLLCLK frequency to generate the core clock (CCLK), the system clocks (SYSCLK, SCLK0, and SCLK1), the LPDDR or DDR2 clock (DCLK), and the output clock (OCLK).

Writing to the CGU control registers does not affect the behavior of the PLL immediately. Registers are first programmed with a new value, and the PLL logic executes the changes so that it transitions smoothly from the current conditions to the new ones.

SYS\_CLKIN oscillations start when power is applied to the VDD\_EXT pins. The rising edge of SYS\_HWRST can be applied after all voltage supplies are within specifications, and SYS\_CLKIN oscillations are stable.

### Clock Out/External Clock

The SYS\_CLKOUT output pin has programmable options to output divided-down versions of the on-chip clocks. By default, the SYS\_CLKOUT pin drives a buffered version of the SYS\_ CLKIN input. Clock generation faults (for example, PLL unlock) may trigger a reset by hardware. The clocks shown in Table 3 can be output on the SYS\_CLKOUT pin.

| Port Name  | Direction | Description                                                                                                                                                                                                                                                                                               |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HADC_VREFN | Input     | <b>Ground Reference for ADC.</b> Connect to an external voltage reference that meets data sheet specifications.                                                                                                                                                                                           |

| HADC_VREFP | Input     | <b>External Reference for ADC.</b> Connect to an external voltage reference that meets data sheet specifications.                                                                                                                                                                                         |

| MSI_CD     | Input     | Card Detect. Connects to a pull-up resistor and to the card detect output of an SD socket.                                                                                                                                                                                                                |

| MSI_CLK    | Output    | <b>Clock.</b> The clock signal applied to the connected device from the MSI.                                                                                                                                                                                                                              |

| MSI_CMD    | I/O       | <b>Command.</b> Used to send commands to and receive responses from the connected device.                                                                                                                                                                                                                 |

| MSI_Dn     | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                                                           |

| MSI_INT    | Input     | <b>eSDIO Interrupt Input.</b> Used only for eSDIO. Connects to an eSDIO card's interrupt output. An interrupt may be sampled even when the MSI clock to the card is switched off.                                                                                                                         |

| Px_nn      | I/O       | <b>Position n.</b> General purpose input/output. See the GP Ports chapter of the HRM for programming information.                                                                                                                                                                                         |

| RTC_CLKIN  | Input     | Crystal input/external oscillator connection. Connect to an external clock source or crystal.                                                                                                                                                                                                             |

| RTC_XTAL   | Output    | <b>Crystal output.</b> Drives an external crystal. Must be left unconnected if an external clock is driving RTC_CLKIN.                                                                                                                                                                                    |

| SMC_ABEn   | Output    | <b>Byte Enable n.</b> Indicate whether the lower or upper byte of a memory is being accessed. When an asynchronous write is made to the upper byte of a 16-bit memory, SMC_ABE1b=0 and SMC_ABE0b=1. When an asynchronous write is made to the lower byte of a 16-bit memory, SMC_ABE1b=1 and SMC_ABE0b=0. |

| SMC_AMSn   | Output    | Memory Select n. Typically connects to the chip select of a memory device.                                                                                                                                                                                                                                |

| SMC_AOE    | Output    | Output Enable. Asserts at the beginning of the setup period of a read access.                                                                                                                                                                                                                             |

| SMC_ARDY   | Input     | <b>Asynchronous Ready.</b> Flow control signal used by memory devices to indicate to the SMC when further transactions may proceed.                                                                                                                                                                       |

| SMC_ARE    | Output    | Read Enable. Asserts at the beginning of a read access.                                                                                                                                                                                                                                                   |

| SMC_AWE    | Output    | Write Enable. Asserts for the duration of a write access period.                                                                                                                                                                                                                                          |

| SMC_Ann    | Output    | Address n. Address bus.                                                                                                                                                                                                                                                                                   |

| SMC_Dnn    | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                                                           |

| SPI_CLK    | I/O       | Clock. Input in slave mode, output in master mode.                                                                                                                                                                                                                                                        |

| SPI_D2     | I/O       | Data 2. Used to transfer serial data in Quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                                                                   |

| SPI_D3     | I/O       | Data 3. Used to transfer serial data in Quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                                                                   |

| SPI_MISO   | I/O       | <b>Master In, Slave Out.</b> Used to transfer serial data. Operates in the same direction as SPI_MOSI in Dual and Quad modes. Open-drain when ODM mode is enabled.                                                                                                                                        |

| SPI_MOSI   | I/O       | <b>Master Out, Slave In.</b> Used to transfer serial data. Operates in the same direction as SPI_MISO in Dual and Quad modes. Open-drain when ODM mode is enabled.                                                                                                                                        |

| SPI_RDY    | I/O       | Ready. Optional flow signal. Output in slave mode, input in master mode.                                                                                                                                                                                                                                  |

| SPI_SELn   | Output    | Slave Select Output n. Used in Master mode to enable the desired slave.                                                                                                                                                                                                                                   |

| SPI_SS     | Input     | <b>Slave Select Input.</b> Slave mode - Acts as the slave select input. Master mode- Optionally serves as an error detection input for the SPI when there are multiple masters.                                                                                                                           |

| SPT_ACLK   | I/O       | <b>Channel A Clock.</b> Data and Frame Sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                                                                  |

| SPT_AD0    | I/O       | <b>Channel A Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                       |

| SPT_AD1    | I/O       | <b>Channel A Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                     |

| SPT_AFS    | I/O       | <b>Channel A Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                                                                                                                            |

| SPT_ATDV   | Output    | <b>Channel A Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                                                                |

### Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name | Description                                  | Port      | Pin Name      |

|-------------|----------------------------------------------|-----------|---------------|

| DMC0_DQ07   | DMC0 Data 7                                  | Not Muxed | DMC0_DQ07     |

| DMC0_DQ08   | DMC0 Data 8                                  | Not Muxed | DMC0_DQ08     |

| MC0_DQ09    | DMC0 Data 9                                  | Not Muxed | DMC0_DQ09     |

| DMC0_DQ10   | DMC0 Data 10                                 | Not Muxed | DMC0_DQ10     |

| DMC0_DQ11   | DMC0 Data 11                                 | Not Muxed | DMC0_DQ11     |

| DMC0_DQ12   | DMC0 Data 12                                 | Not Muxed | DMC0_DQ12     |

| DMC0_DQ13   | DMC0 Data 13                                 | Not Muxed | DMC0_DQ13     |

| MC0_DQ14    | DMC0 Data 14                                 | Not Muxed | DMC0_DQ14     |

| MC0_DQ15    | DMC0 Data 15                                 | Not Muxed | DMC0_DQ15     |

| MC0_LDM     | DMC0 Data Mask for Lower Byte                | Not Muxed | DMC0_LDM      |

| MC0_LDQS    | DMC0 Data Strobe for Lower Byte              | Not Muxed | DMC0_LDQS     |

| MC0_LDQS    | DMC0 Data Strobe for Lower Byte (complement) | Not Muxed | DMC0_LDQS     |

| MC0_ODT     | DMC0 On-die termination                      | Not Muxed | DMC0_ODT      |

| MC0_RAS     | DMC0 Row Address Strobe                      | Not Muxed | DMC0_RAS      |

| MC0_UDM     | DMC0 Data Mask for Upper Byte                | Not Muxed | DMC0_UDM      |

| MC0_UDQS    | DMC0 Data Strobe for Upper Byte              | Not Muxed | DMC0_UDQS     |

| DMC0_UDQS   | DMC0 Data Strobe for Upper Byte (complement) | Not Muxed | DMC0_UDQS     |

| MC0_VREF    | DMC0 Voltage Reference                       | Not Muxed | DMC0_VREF     |

| DMC0_WE     | DMC0 Write Enable                            | Not Muxed | DMC0_WE       |

| ND          | Ground                                       | Not Muxed | GND           |

| ND_HADC     | Ground HADC                                  | Not Muxed | GND_HADC      |

| IADC0_VIN0  | HADC0 Analog Input at channel 0              | Not Muxed | HADC0_VIN0    |

| IADC0_VIN1  | HADC0 Analog Input at channel 1              | Not Muxed | HADC0_VIN1    |

| IADC0_VIN2  | HADC0 Analog Input at channel 2              | Not Muxed | HADC0_VIN2    |

| IADC0_VIN3  | HADC0 Analog Input at channel 3              | Not Muxed | HADC0_VIN3    |

| IADC0_VREFN | HADC0 Ground Reference for ADC               | Not Muxed | HADC0_VREFN   |

| IADC0_VREFP | HADC0 External Reference for ADC             | Not Muxed | HADC0_VREFP   |

| TG_SWCLK    | TAPC0 Serial Wire Clock                      | Not Muxed | JTG_TCK_SWCLK |

| TG_SWDIO    | TAPC0 Serial Wire DIO                        | Not Muxed | JTG_TMS_SWDIO |

| TG_SWO      | TAPC0 Serial Wire Out                        | Not Muxed | JTG_TDO_SWO   |

| TG_TCK      | TAPC0 JTAG Clock                             | Not Muxed | JTG_TCK_SWCLK |

| TG_TDI      | TAPC0 JTAG Serial Data In                    | Not Muxed | JTG_TDI       |

| TG_TDO      | TAPC0 JTAG Serial Data Out                   | Not Muxed | JTG_TDO_SWO   |

| TG_TMS      | TAPC0 JTAG Mode Select                       | Not Muxed | JTG_TMS_SWDIO |

| TG_TRST     | TAPC0 JTAG Reset                             | Not Muxed | JTG_TRST      |

| ISI0_CD     | MSI0 Card Detect                             | A         | PA_08         |

| ISI0_CLK    | MSI0 Clock                                   | С         | PC_09         |

| ISI0_CMD    | MSI0 Command                                 | С         | PC_05         |

| ISI0_D0     | MSI0 Data 0                                  | С         | PC_08         |

| 1SI0_D1     | MSI0 Data 1                                  | С         | PC_04         |

| 1SI0_D2     | MSI0 Data 2                                  | С         | PC_07         |

| ISI0_D3     | MSI0 Data 3                                  | С         | PC_06         |

| ISI0_D4     | MSI0 Data 4                                  | С         | PC_10         |

| 1SI0_D5     | MSI0 Data 5                                  | С         | PC_11         |

| 1SI0_D6     | MSI0 Data 6                                  | С         | PC_12         |

| ASIO_D7     | MSI0 Data 7                                  | С         | PC_13         |

|             |      | Driver   | Int   | Reset | Reset | Hiber | Hiber | Power     | Description                                         |

|-------------|------|----------|-------|-------|-------|-------|-------|-----------|-----------------------------------------------------|

| Signal Name | Туре | Туре     | Term  | Term  | Drive | Term  | Drive | Domain    | and Notes                                           |

| DMC0_A06    | 1/0  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 6                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A07    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 7                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A08    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 8                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A09    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 9                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A10    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 10                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A11    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 11                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A12    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 12                               |

| DMC0 442    | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A13    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 13                               |

|             | 1/0  | <b>D</b> |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_BA0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 0<br>Notes: No notes. |

| DMC0_BA1    | I/O  | В        | nono  | nono  | nono  | nono  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 1                     |

| DIVICO_BAT  | 1/0  | D        | none  | none  | none  | none  | none  | VDD_DIVIC | Notes: No notes.                                    |

| DMC0_BA2    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 2                     |

| DIVICO_DIV2 | 1/0  |          | none  | none  | none  | none  | none  | VDD_DIMC  | Notes: For LPDDR, leave unconnected.                |

| DMC0_CAS    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Column Address Strobe                    |

| bineo_erio  | ., 0 |          | lione | none  | none  | none  | none  |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | с        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock                                    |

|             |      | -        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | С        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock (complement)                       |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CKE    | I/O  | В        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock enable                             |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CS0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Chip Select 0                            |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ00   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 0                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ01   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 1                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ02   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 2                                   |

|             | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ03   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 3                                   |

|             | 1/0  | D        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ04   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 4<br>Notes: No notes.               |

| DMC0_DQ05   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 5                                   |

|             | "0   |          | none  | none  | none  | none  | lione |           | Notes: No notes.                                    |

| DMC0_DQ06   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 6                                   |

| 2           |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ07   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 7                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

|             |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|--------|------|-------|-------|-------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Туре   | Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                                                                                                                                                                                                                                                                                          |

| PB_04       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 3   SPT0 Channel B Clock<br>  SPI0 Slave Select Output 4   SMC0 Data<br>3   TM0 Alternate Clock 6<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                               |

| PB_05       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 2   SPT0 Channel B Data<br>0   SPI0 Slave Select Output 5   SMC0<br>Data 2<br>Notes: SPI slave select outputs require a                                                                                                                                                                                                                                            |

|             |      |        |      |       |       |       |       |         | pull-up when used.                                                                                                                                                                                                                                                                                                                                                                 |

| PB_06       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 1   SPT0 Channel B<br>Frame Sync   SPI0 Slave Select Output 6<br>  SMC0 Data 1   TM0 Clock                                                                                                                                                                                                                                                                         |

|             |      |        |      |       |       |       |       |         | Notes: SPI slave select outputs require a pull-up when used.                                                                                                                                                                                                                                                                                                                       |

| PB_07       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 0   SPT0 Channel B Data<br>1   SPI0 Data 3   SMC0 Data 0   SYS Power<br>Saving Mode Wakeup 0                                                                                                                                                                                                                                                                       |

|             |      |        |      |       |       |       |       |         | Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down.                                                                                                                                                                                   |

| PB_08       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Transmit   PPI0 Data 16  <br>SPI2 Slave Select Output 2   SMC0 Data<br>8   SYS Power Saving Mode Wakeup 1<br>Notes: SPI slave select outputs require a<br>pull-up when used. If hibernate mode is<br>used, one of the following must be true<br>during hibernate. Either this pin must<br>be actively driven by another IC, or it<br>must have a pull-up or pull-down. |

| PB_09       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Receive   PPI0 Data 17  <br>SPI2 Slave Select Output 3   SMC0 Data<br>9   TM0 Alternate Capture Input 3<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                             |

| PB_10       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Clock   TRACE0 Trace Clock  <br>SMC0 Data 10   TM0 Alternate Clock 4<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.                                                                                                                                                                                                            |

| PB_11       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Master In, Slave Out   TRACE0<br>Trace Data 4   SMC0 Data 11<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.                                                                                                                                                                                                                                     |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                     |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_13       | 1/0  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 1   MSI0 Data<br>7<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                |

| PC_14       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Transmit Data<br>Valid   MSI0 eSDIO Interrupt Input<br>Notes: No notes.                                                                                                 |

| RTC0_CLKIN  | a    | na             | none        | none          | none           | none          | none           | VDD_RTC         | Desc: RTC0 Crystal input / external oscil-<br>lator connection<br>Notes: If RTC is not used, connect to<br>ground.                                                                           |

| RTC0_XTAL   | а    | na             | none        | none          | none           | none          | none           | VDD_RTC         | Desc: RTC0 Crystal output<br>Notes: No notes.                                                                                                                                                |

| SYS_BMODE0  | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Boot Mode Control 0<br>Notes: A pull-down is required for<br>setting to 0 and a pull-up is required for<br>setting to 1.                                                           |

| SYS_BMODE1  | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Boot Mode Control 1<br>Notes: A pull-down is required for<br>setting to 0 and a pull-up is required for<br>setting to 1.                                                           |

| SYS_CLKIN   | а    | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Clock/Crystal Input<br>Notes: No notes.                                                                                                                                            |

| SYS_CLKOUT  | I/O  | A              | none        | none          | L              | none          | none           | VDD_EXT         | Desc: SYS Processor Clock Output<br>Notes: During reset, SYS_CLKOUT<br>drives out SYS_CLKIN Frequency.                                                                                       |

| SYS_EXTWAKE | I/O  | A              | none        | none          | н              | none          | L              | VDD_EXT         | Desc: SYS External Wake Control<br>Notes: Drives low during hibernate and<br>high all other times including reset.                                                                           |

| SYS_FAULT   | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Complementary Fault Output<br>Notes: Open drain, requires an external<br>pull-up resistor.                                                                                         |

| SYS_HWRST   | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Processor Hardware Reset<br>Control<br>Notes: Active during reset, must be<br>externally driven.                                                                                   |

| SYS_NMI     | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Non-maskable Interrupt<br>Notes: Requires an external pull-up<br>resistor.                                                                                                         |

| SYS_RESOUT  | I/O  | А              | none        | none          | L              | none          | none           | VDD_EXT         | Desc: SYS Reset Output<br>Notes: Active during reset.                                                                                                                                        |

| SYS_XTAL    | a    | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Crystal Output<br>Notes: Leave unconnected if an oscil-<br>lator is used to provide SYS_CLKIN.<br>Active during reset. State during<br>hibernate is controlled by DPM_HIB_<br>DIS. |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

### **SPECIFICATIONS**

For information about product specifications, contact your Analog Devices, Inc. representative.

### **OPERATING CONDITIONS**

| Parameter                          |                                    | Test Conditions/Comments                               | Min                      | Nominal                  | Max                                    | Unit |

|------------------------------------|------------------------------------|--------------------------------------------------------|--------------------------|--------------------------|----------------------------------------|------|

| V <sub>DD_INT</sub>                | Internal Supply Voltage            | CCLK ≤ 400 MHz                                         | 1.045                    | 1.100                    | 1.155                                  | V    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 1.7                      | 1.8                      | 1.9                                    | V    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 3.13                     | 3.30                     | 3.47                                   | V    |

| V <sub>DD_DMC</sub>                | DDR2/LPDDR Supply Voltage          |                                                        | 1.7                      | 1.8                      | 1.9                                    | v    |

| $V_{DD_USB}^{2}$                   | USB Supply Voltage                 |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_{RTC}}$                     | Real-Time Clock Supply Voltage     |                                                        | 2.00                     | 3.30                     | 3.47                                   | V    |

| $V_{DD\_HADC}$                     | Housekeeping ADC Supply<br>Voltage |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_OTP}^{1}$                   | OTP Supply Voltage                 |                                                        |                          |                          |                                        |      |

|                                    | For Reads                          |                                                        | 2.25                     | 3.30                     | 3.47                                   | V    |

|                                    | For Writes                         |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| V <sub>DDR_VREF</sub>              | DDR2 Reference Voltage             |                                                        | $0.49 \times V_{DD_DMC}$ | $0.50 \times V_{DD_DMC}$ | $0.51 \times V_{DD_DMC}$               | v    |

| $V_{HADC_{REF}}^{3}$               | HADC Reference Voltage             |                                                        | 2.5                      | 3.30                     | V <sub>DD_HADC</sub>                   | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD_{EXT}} = 3.47 V$                                | 2.0                      |                          |                                        | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD\_EXT} = 1.9 V$                                  | $0.7 \times V_{DD\_EXT}$ |                          |                                        | V    |

| V <sub>IHTWI</sub> <sup>5, 6</sup> | High Level Input Voltage           | $V_{DD\_EXT} = maximum$                                | $0.7 \times V_{VBUSTWI}$ |                          | V <sub>VBUSTWI</sub>                   | V    |

| $V_{\text{IH}_{DDR2}}^{7}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $V_{DDR\_REF} + 0.25$    |                          |                                        | v    |

| $V_{\text{IH\_LPDDR}}^{8}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $0.8 \times V_{DD_DMC}$  |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 1.075 V$                                     | 0.50                     |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 0.725 V$                                     | 0.55                     |                          |                                        | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD_{EXT}} = 3.13 V$                                |                          |                          | 0.8                                    | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD\_EXT} = 1.7 V$                                  |                          |                          | $0.3 \times V_{\text{DD}\_\text{EXT}}$ | V    |

| V <sub>ILTWI</sub> 5, 6            | Low Level Input Voltage            | $V_{DD\_EXT} = minimum$                                |                          |                          | $0.3 	imes V_{VBUSTWI}$                | V    |

| $V_{IL_DDR2}^{7}$                  |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $V_{DDR_{REF}} - 0.25$                 | V    |

| $V_{IL\_LPDDR}^{8}$                |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $0.2 \times V_{DD_DMC}$                | V    |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = 0^{\circ}C \text{ to } +70^{\circ}C$    | 0                        |                          | 105                                    | °C   |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +85^{\circ}C$  | -40                      |                          | +105                                   | °C   |

| T                                  | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +105^{\circ}C$ | -40                      |                          | +125                                   | °C   |

<sup>1</sup>Must remain powered (even if the associated function is not used).

<sup>2</sup> If not used, connect to 1.8 V or 3.3 V.

$^{3}\mathrm{V}_{\mathrm{HADC\_VREF}}$  should always be less than  $\mathrm{V}_{\mathrm{DD\_HADC}}.$

<sup>4</sup> Parameter value applies to all input and bidirectional signals except RTC signals, TWI signals, DMC0 signals, and USB0 signals.

<sup>5</sup> Parameter applies to TWI signals.

$^{6}$  TWI signals are pulled up to  $V_{BUSTWI}$ . See Table 16.

<sup>7</sup> Parameter applies to DMC0 signals in DDR2 mode.

<sup>8</sup> Parameter applies to DMC0 signals in LPDDR mode.

<sup>9</sup> Parameter applies to signals DMC0\_LDQS, <u>DMC0\_LDQS</u>, DMC0\_UDQS, <u>DMC0\_UDQS</u> when used in DDR2 differential input mode.

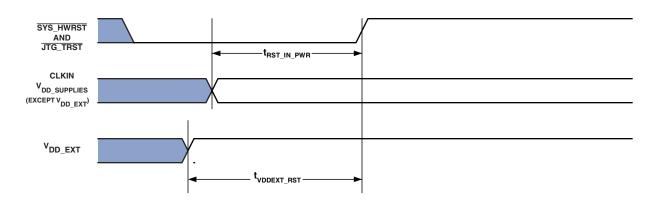

#### Power-Up Reset Timing

A power-up reset is required to place the processor in a known state after power-up. A power-up reset is initiated by asserting SYS\_HWRST and JTG\_TRST. During power-up reset, all pins are high impedance except for those noted in the ADSP-BF70x Designer Quick Reference on Page 38.

Both JTG\_TRST and SYS\_HWRST need to be asserted upon power-up, but only SYS\_HWRST needs to be released for the device to boot properly. JTG\_TRST may be asserted indefinitely for normal operation. JTG\_TRST only needs to be released when using an emulator to connect to the DAP for debug or boundary scan. There is an internal pull-down on JTG\_TRST to ensure internal emulation logic will always be properly initialized during power-up reset.

Table 30 and Figure 9 show the relationship between power supply startup and processor reset timing, related to the clock generation unit (CGU) and reset control unit (RCU). In Figure 9,  $V_{DD_{\_SUPPLIES}}$  are  $V_{DD_{\_INT}}$ ,  $V_{DD_{\_EXT}}$ ,  $V_{DD_{\_DMC}}$ ,  $V_{DD_{\_USB}}$ ,  $V_{DD_{\_CTC}}$ ,  $V_{DD_{\_OTP}}$ , and  $V_{DD_{\_HADC}}$ .

There is no power supply sequencing requirement for the ADSP-BF70x processor. However, if saving power during power-on is important, bringing up  $V_{DD_{INT}}$  last is recommended. This avoids a small current drain in the  $V_{DD_{INT}}$  domain during the transition period of I/O voltages from 0 V to within the voltage specification.

#### Table 30. Power-Up Reset Timing

| Paramete                | r                                                                                                                                                                                                                                                                  | Min                  | Max | Unit |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|

| Timing Red              | quirement                                                                                                                                                                                                                                                          |                      |     |      |

| t <sub>rst_in_pwr</sub> | $\label{eq:starsest} \overrightarrow{SYS_HWRST} and \ \overrightarrow{JTG_TRST} \ Deasserted \ After \ V_{DD\_INT}, \ V_{DD\_DMC}, \ V_{DD\_USB}, \\ V_{DD\_RTC}, \ V_{DD\_OTP}, \ V_{DD\_HADC}, \ and \ SYS\_CLKIN \ are \ Stable \ and \ Within \ Specification$ | $11 \times t_{CKIN}$ |     | ns   |

| t <sub>VDDEXT_RST</sub> | SYS_HWRST Deasserted After V <sub>DD_EXT</sub> is Stable and Within Specifications (No External Pull-Down on JTG_TRST)                                                                                                                                             | 10                   |     | μs   |

| t <sub>VDDEXT_RST</sub> | $\overline{SYS}_{HWRST}$ Deasserted After $V_{DD\_EXT}$ is Stable and Within Specifications (10k External Pull-Down on $\overline{JTG}_{TRST}$ )                                                                                                                   | 1                    |     | μs   |

Figure 9. Power-Up Reset Timing

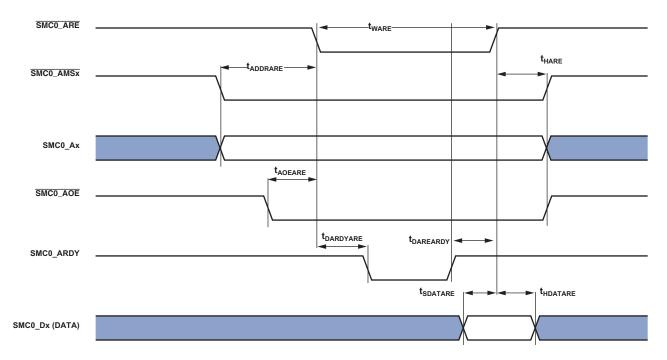

Figure 10. Asynchronous Read

#### Asynchronous Flash Read

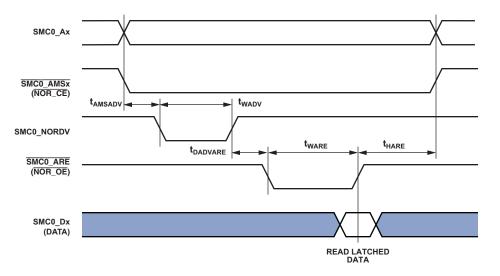

Table 33 and Figure 12 show asynchronous flash memory read timing, related to the static memory controller (SMC).

#### Table 33. Asynchronous Flash Read

|                     |                                                                             | V <sub>DD_E</sub> )<br>1.8 V/3.3 V M |     |      |

|---------------------|-----------------------------------------------------------------------------|--------------------------------------|-----|------|

| Parameter           |                                                                             | Min                                  | Max | Unit |

| Switching C         | haracteristics                                                              |                                      |     |      |

| t <sub>amsadv</sub> | SMC0_Ax (Address)/SMC0_AMSx Assertion Before SMC0_NORDV<br>Low <sup>1</sup> | PREST × t <sub>SCLK0</sub> – 2       |     | ns   |

| t <sub>wadv</sub>   | SMC0_NORDV Active Low Width <sup>2</sup>                                    | $RST \times t_{SCLK0} - 2$           |     | ns   |

| DADVARE             | SMC0_ARE Low Delay From SMC0_NORDV High <sup>3</sup>                        | $PREAT \times t_{SCLK0} - 2$         |     | ns   |

| t <sub>HARE</sub>   | Output <sup>4</sup> Hold After SMC0_ARE High <sup>5</sup>                   | $RHT \times t_{SCLK0} - 2$           |     | ns   |

| t <sub>ware</sub> 6 | SMC0_ARE Active Low Width <sup>7</sup>                                      | $RAT \times t_{SCLK0} - 2$           |     | ns   |

<sup>1</sup> PREST value set using the SMC\_BxETIM.PREST bits.

<sup>2</sup> RST value set using the SMC\_BxTIM.RST bits.

<sup>3</sup> PREAT value set using the SMC\_BxETIM.PREAT bits.

<sup>4</sup>Output signals are SMC0\_Ax, <u>SMC0\_AMS</u>, <u>SMC0\_AOE</u>.

<sup>5</sup> RHT value set using the SMC\_BxTIM.RHT bits.

<sup>6</sup>SMC0\_BxCTL.ARDYEN bit = 0.

$^7\,\rm RAT$  value set using the SMC\_BxTIM.RAT bits.

Figure 12. Asynchronous Flash Read

### General-Purpose I/O Port Timing (GPIO)

Table 45 and Figure 23 describe I/O timing, related to the general-purpose ports (PORT).

### Table 45. General-Purpose I/O Port Timing

|                  |                                            | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal |     |      |  |  |

|------------------|--------------------------------------------|--------------------------------------------|-----|------|--|--|

| Paramet          | er                                         | Min                                        | Max | Unit |  |  |

| Timing Re        | equirement                                 |                                            |     |      |  |  |

| t <sub>WFI</sub> | General-Purpose Port Pin Input Pulse Width | $2 \times t_{SCLK0} - 1.5$                 | 5   | ns   |  |  |

Figure 23. General-Purpose I/O Port Timing

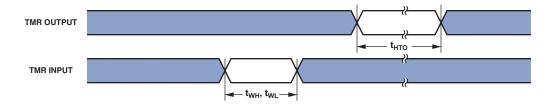

### **Timer Cycle Timing**

Table 46 and Figure 24 describe timer expired operations, related to the general-purpose timer (TIMER). The input signal is asynchronous in width capture mode and external clock mode and has an ideal maximum input frequency of ( $f_{SCLK0}/4$ ) MHz. The Period Value (VALUE) is the timer period assigned in the TMx\_TMRn\_PER register and can range from 2 to  $2^{32} - 1$ .

### Table 46. Timer Cycle Timing

|                  |                                           | 1                          | V <sub>DD_EXT</sub><br>.8 V Nominal | 3.                         | V <sub>DD_EXT</sub><br>3.3V Nominal |      |  |

|------------------|-------------------------------------------|----------------------------|-------------------------------------|----------------------------|-------------------------------------|------|--|

| Param            | eter                                      | Min                        | Max                                 | Min                        | Max                                 | Unit |  |

| Timing           | Requirements                              |                            |                                     |                            |                                     |      |  |

| t <sub>WL</sub>  | Timer Pulse Width Input Low <sup>1</sup>  | $2 \times t_{SCLK0} - 1.5$ |                                     | $2 \times t_{SCLK0} - 1.5$ | $2 \times t_{SCLK0} - 1.5$          |      |  |

| t <sub>wH</sub>  | Timer Pulse Width Input High <sup>1</sup> | $2 \times t_{SCLK0} - 1.5$ |                                     | $2 \times t_{SCLK0} - 1.5$ |                                     | ns   |  |

| Switch           | ing Characteristic                        |                            |                                     |                            |                                     |      |  |

| t <sub>HTO</sub> | Timer Pulse Width Output                  | $t_{SCLK0} \times VALUE$   | – 1                                 | $t_{SCLK0} \times VALUE$   | – 1                                 | ns   |  |

<sup>1</sup>This specification indicates the minimum instantaneous width that can be tolerated due to duty cycle variation or jitter for TMx signals in width capture and external clock modes. The ideal maximum frequency for TMx signals is listed in Timer Cycle Timing on this page.

Figure 24. Timer Cycle Timing

#### **Serial Ports**

To determine whether serial port (SPORT) communication is possible between two devices at clock speed n, the following specifications must be confirmed: 1) frame sync delay and frame sync setup and hold, 2) data delay and data setup and hold, and 3) serial clock (SPT\_CLK) width. In Figure 27 either the rising edge or the falling edge of SPT\_CLK (external or internal) can be used as the active sampling edge.

When externally generated the SPORT clock is called  $f_{SPTCLKEXT}$ :

$$t_{SPTCLKEXT} = \frac{1}{f_{SPTCLKEXT}}$$

When internally generated, the programmed SPORT clock ( $f_{SPTCLKPROG}$ ) frequency in MHz is set by the following equation where CLKDIV is a field in the SPORT\_DIV register that can be set from 0 to 65,535:

$$f_{SPTCLKPROG} = \frac{f_{SCLK0}}{(CLKDIV + 1)}$$

$$t_{SPTCLKPROG} = \frac{1}{f_{SPTCLKPROG}}$$

#### Table 49. Serial Ports-External Clock

|                      |                                                                                                                         | V <sub>DD_EXT</sub><br>1.8V Nominal |     | V <sub>DD_EXT</sub><br>3.3 V Nominal |     |      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----|--------------------------------------|-----|------|

| Parameter            |                                                                                                                         | Min                                 | Мах | Min                                  | Max | Unit |

| Timing R             | equirements                                                                                                             |                                     |     |                                      |     |      |

| t <sub>SFSE</sub>    | Frame Sync Setup Before SPT_CLK<br>(Externally Generated Frame Sync in Either<br>Transmit or Receive Mode) <sup>1</sup> | 1.5                                 |     | 1                                    |     | ns   |

| t <sub>HFSE</sub>    | Frame Sync Hold After SPT_CLK<br>(Externally Generated Frame Sync in Either<br>Transmit or Receive Mode) <sup>1</sup>   | 3                                   |     | 3                                    |     | ns   |

| t <sub>SDRE</sub>    | Receive Data Setup Before Receive SPT_CLK <sup>1</sup>                                                                  | 1.5                                 |     | 1                                    |     | ns   |

| t <sub>HDRE</sub>    | Receive Data Hold After SPT_CLK <sup>1</sup>                                                                            | 3                                   |     | 3                                    |     | ns   |

| t <sub>SCLKW</sub>   | SPT_CLK Width <sup>2</sup>                                                                                              | $(0.5 \times t_{SPTCLKEXT}) - 1$    |     | $(0.5 \times t_{SPTCLKEXT}) - 1$     |     | ns   |

| t <sub>sptclke</sub> | SPT_CLK Period <sup>2</sup>                                                                                             | t <sub>sptclkext</sub> – 1          |     | t <sub>sptclkext</sub> – 1           |     | ns   |

| Switching            | g Characteristics                                                                                                       |                                     |     |                                      |     |      |

| t <sub>DFSE</sub>    | Frame Sync Delay After SPT_CLK<br>(Internally Generated Frame Sync in Either<br>Transmit or Receive Mode) <sup>3</sup>  |                                     | 18  |                                      | 15  | ns   |

| t <sub>HOFSE</sub>   | Frame Sync Hold After SPT_CLK<br>(Internally Generated Frame Sync in Either<br>Transmit or Receive Mode) <sup>3</sup>   | 2.5                                 |     | 2.5                                  |     | ns   |

| t <sub>DDTE</sub>    | Transmit Data Delay After Transmit SPT_CLK <sup>3</sup>                                                                 |                                     | 18  |                                      | 15  | ns   |

| t <sub>HDTE</sub>    | Transmit Data Hold After Transmit SPT_CLK <sup>3</sup>                                                                  | 2.5                                 |     | 2.5                                  |     | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external SPT\_CLK. For the external SPT\_CLK ideal maximum frequency, see the f<sub>SPTCLKEXT</sub> specification in Table 18 on Page 52 in Clock Related Operating Conditions.

<sup>3</sup>Referenced to drive edge.

# ADSP-BF700/701/702/703/704/70

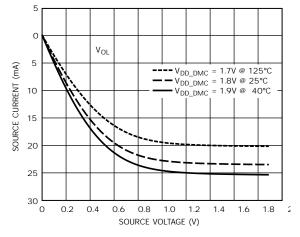

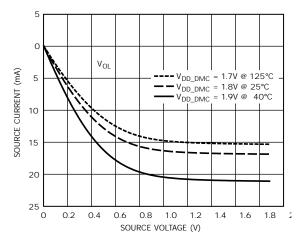

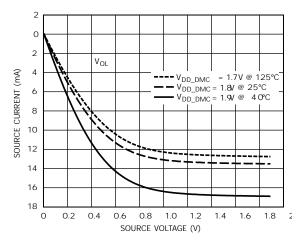

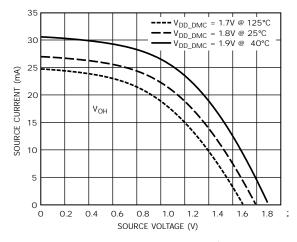

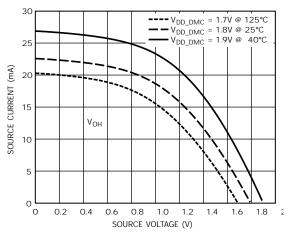

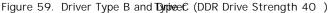

Figure 55. Driver Type B and Dynpixe C (DDR Drive Strength 40)

Figure 56. Driver Type B and Dynpixee C (DDR Drive Strength 50)

Figure 57. Driver Type B and Dynpace C (DDR Drive Strength 60)

Figure 58. Driver Type B and Dynpixee€ (DDR Drive Strength 34)

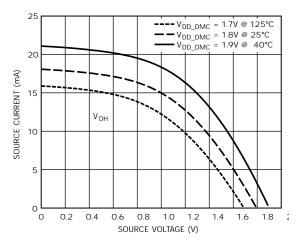

Figure 60. Driver Type B and Dynpixee€ (DDR Drive Strength 50)