Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 1MB                                                                                       |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 88-VFQFN Exposed Pad, CSP                                                                 |

| Supplier Device Package | 88-LFCSP-VQ (12x12)                                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf706bcpz-3                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

output enable and the input enable of a GPIO pin are both active, the data signal before the pad driver is looped back to the receive path for the same GPIO pin.

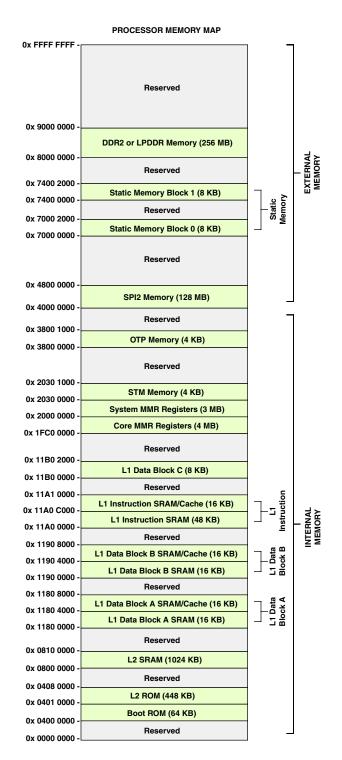

#### MEMORY ARCHITECTURE

The processor views memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low-latency core-accessible memory as cache or SRAM, and larger, lower-cost and performance interface-accessible memory systems. See Figure 3.

#### Internal (Core-Accessible) Memory

The L1 memory system is the highest-performance memory available to the Blackfin+ processor core.

The core has its own private L1 memory. The modified Harvard architecture supports two concurrent 32-bit data accesses along with an instruction fetch at full processor speed which provides high-bandwidth processor performance. In the core, a 64K byte block of data memory partners with an 64K byte memory block for instruction storage. Each data block is multibanked for efficient data exchange through DMA and can be configured as SRAM. Alternatively, 16K bytes of each block can be configured in L1 cache mode. The four-way set-associative instruction cache and the 2 two-way set-associative data caches greatly accelerate memory access performance, especially when accessing external memories.

The L1 memory domain also features a 8K byte data SRAM block which is ideal for storing local variables and the software stack. All L1 memory is protected by a multi-parity-bit concept, regardless of whether the memory is operating in SRAM or cache mode.

Outside of the L1 domain, L2 and L3 memories are arranged using a Von Neumann topology. The L2 memory domain is a unified instruction and data memory and can hold any mixture of code and data required by the system design. The L2 memory domain is accessible by the Blackfin+ core through a dedicated 64-bit interface. It operates at SYSCLK frequency.

The processor features up to 1M byte of L2 SRAM, which is ECC-protected and organized in eight banks. Individual banks can be made private to any system master. There is also a 512K byte single-bank ROM in the L2 domain. It contains boot code, security code, and general-purpose ROM space.

#### **OTP Memory**

The processor features 4 kB of one-time-programmable (OTP) memory which is memory-map accessible. This memory stores a unique chip identification and is used to support secure-boot and secure operation.

Figure 3. ADSP-BF706/ADSP-BF707 Internal/External Memory Map

#### **General-Purpose Timers**

There is one GP timer unit, and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TIMER\_TMRx pins, an external TIMER\_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The GP timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals through the TRU (for instance, to signal a fault). Each timer may also be started and/or stopped by any TRU master without core intervention.

#### **Core Timer**

The processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### Watchdog Timer

The core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, through generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts down to zero from the programmed value. This protects the system from remaining in an unknown state where software that would normally reset the timer has stopped running due to an external noise condition or software error.

After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in its timer control register that is set only upon a watchdog-generated reset.

#### Serial Ports (SPORTs)

Two synchronous serial ports (comprised of four half-SPORTs) provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices' audio codecs, ADCs, and DACs. Each half-SPORT is made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial port data can be automatically transferred to and from on-chip memory/external memory through dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. In this configuration, one SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in six modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- Left-justified mode

- Right-justified mode

#### **General-Purpose Counters**

A 32-bit counter is provided that can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is either controlled by a levelsensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumbwheel devices. All three pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable this timer to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmed count values are exceeded.

#### Parallel Peripheral Interface (PPI)

The processor provides a parallel peripheral interface (PPI) that supports data widths up to 18 bits. The PPI supports direct connection to TFT LCD panels, parallel analog-to-digital and digital-to-analog converters, video encoders and decoders, image sensor modules, and other general-purpose peripherals.

The following features are supported in the PPI module:

- Programmable data length: 8 bits, 10 bits, 12 bits, 14 bits, 16 bits, and 18 bits per clock.

- Various framed, non-framed, and general-purpose operating modes. Frame syncs can be generated internally or can be supplied by an external device.

- ITU-656 status word error detection and correction for ITU-656 receive modes and ITU-656 preamble and status word decode.

- Optional packing and unpacking of data to/from 32 bits from/to 8 bits, 16 bits and 24 bits. If packing/unpacking is enabled, endianness can be configured to change the order of packing/unpacking of bytes/words.

- RGB888 can be converted to RGB666 or RGB565 for transmit modes.

- Various de-interleaving/interleaving modes for receiving/transmitting 4:2:2 YCrCb data.

- Configurable LCD data enable (DEN) output available on Frame Sync 3.

Target defined:

- Hardware Reset—All functional units are set to their default states without exception. History is lost.

- System Reset—All functional units except the RCU are set to their default states.

- Core-only Reset—Affects the core only. The system software should guarantee that the core, while in reset state, is not accessed by any bus master.

Source defined:

- Hardware Reset—The <u>SYS\_HWRST</u> input signal is asserted active (pulled down).

- System Reset—May be triggered by software (writing to the RCU\_CTL register) or by another functional unit such as the dynamic power management (DPM) unit (hibernate) or any of the system event controller (SEC), trigger routing unit (TRU), or emulator inputs.

- Core-only Reset—Triggered by software.

- Trigger request (peripheral).

#### Voltage Regulation

The processor requires an external voltage regulator to power the VDD\_INT pins. To reduce standby power consumption, the external voltage regulator can be signaled through SYS\_EXTWAKE to remove power from the processor core. This signal is high-true for power-up and may be connected directly to the low-true shut-down input of many common regulators.

While in the hibernate state, all external supply pins (VDD\_ EXT, VDD\_USB, and VDD\_DMC) can still be powered, eliminating the need for external buffers. The external voltage regulator can be activated from this power down state by asserting the SYS\_HWRST pin, which then initiates a boot sequence. SYS\_EXTWAKE indicates a wake-up to the external voltage regulator.

### SYSTEM DEBUG

The processor includes various features that allow for easy system debug. These are described in the following sections.

#### System Watchpoint Unit

The system watchpoint unit (SWU) is a single module which connects to a single system bus and provides for transaction monitoring. One SWU is attached to the bus going to each system slave. The SWU provides ports for all system bus address channel signals. Each SWU contains four match groups of registers with associated hardware. These four SWU match groups operate independently, but share common event (interrupt, trigger, and others) outputs.

#### **Debug Access Port**

The debug access port (DAP) provides IEEE-1149.1 JTAG interface support through its JTAG debug and serial wire debug port (SWJ-DP). SWJ-DP is a combined JTAG-DP and SW-DP that enables either serial wire debug (SWD) or a JTAG emulator to be connected to a target. SWD signals share the same pins as

JTAG. The DAP provides an optional instrumentation trace for both the core and system. It provides a trace stream that conforms to MIPI System Trace Protocol version 2 (STPv2).

### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (CrossCore<sup>®</sup> Embedded Studio), evaluation products, emulators, and a wide variety of software add-ins.

#### Integrated Development Environments (IDEs)

CrossCore Embedded Studio is based on the Eclipse<sup>™</sup> framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information, visit www.analog.com/cces.

#### EZ-KIT Lite Evaluation Board

For processor evaluation, Analog Devices provides a wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information, visit www.analog.com and search on "ezkit" or "ezextender".

### **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE, a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

#### ADSP-BF706 EZ-KIT Mini

The ADSP-BF706 EZ-KIT Mini<sup>™</sup> product (ADZS-BF706-EZMini) contains the ADSP-BF706 processor and is shipped with all of the necessary hardware. Users can start their evaluation immediately. The EZ-KIT Mini product includes the standalone evaluation board and USB cable. The EZ-KIT Mini ships with an on-board debug agent.

The evaluation board is designed to be used in conjunction with the CrossCore Embedded Studio (CCES) development tools to test capabilities of the ADSP-BF706 Blackfin processor.

### **184-BALL CSP\_BGA SIGNAL DESCRIPTIONS**

The processor's pin definitions are shown in Table 7. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

#### Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

| Signal Name | Description                 | Port      | Pin Name  |

|-------------|-----------------------------|-----------|-----------|

| CAN0_RX     | CAN0 Receive                | С         | PC_02     |

| CAN0_TX     | CAN0 Transmit               | С         | PC_03     |

| CAN1_RX     | CAN1 Receive                | A         | PA_12     |

| CAN1_TX     | CAN1 Transmit               | A         | PA_13     |

| CNT0_DG     | CNT0 Count Down and Gate    | A         | PA_07     |

| CNT0_UD     | CNT0 Count Up and Direction | A         | PA_15     |

| CNT0_ZM     | CNT0 Count Zero Marker      | A         | PA_13     |

| DMC0_A00    | DMC0 Address 0              | Not Muxed | DMC0_A00  |

| DMC0_A01    | DMC0 Address 1              | Not Muxed | DMC0_A01  |

| DMC0_A02    | DMC0 Address 2              | Not Muxed | DMC0_A02  |

| DMC0_A03    | DMC0 Address 3              | Not Muxed | DMC0_A03  |

| DMC0_A04    | DMC0 Address 4              | Not Muxed | DMC0_A04  |

| DMC0_A05    | DMC0 Address 5              | Not Muxed | DMC0_A05  |

| DMC0_A06    | DMC0 Address 6              | Not Muxed | DMC0_A06  |

| DMC0_A07    | DMC0 Address 7              | Not Muxed | DMC0_A07  |

| DMC0_A08    | DMC0 Address 8              | Not Muxed | DMC0_A08  |

| DMC0_A09    | DMC0 Address 9              | Not Muxed | DMC0_A09  |

| DMC0_A10    | DMC0 Address 10             | Not Muxed | DMC0_A10  |

| DMC0_A11    | DMC0 Address 11             | Not Muxed | DMC0_A11  |

| DMC0_A12    | DMC0 Address 12             | Not Muxed | DMC0_A12  |

| DMC0_A13    | DMC0 Address 13             | Not Muxed | DMC0_A13  |

| DMC0_BA0    | DMC0 Bank Address Input 0   | Not Muxed | DMC0_BA0  |

| DMC0_BA1    | DMC0 Bank Address Input 1   | Not Muxed | DMC0_BA1  |

| DMC0_BA2    | DMC0 Bank Address Input 2   | Not Muxed | DMC0_BA2  |

| DMC0_CAS    | DMC0 Column Address Strobe  | Not Muxed | DMC0_CAS  |

| DMC0_CK     | DMC0 Clock                  | Not Muxed | DMC0_CK   |

| DMC0_CKE    | DMC0 Clock enable           | Not Muxed | DMC0_CKE  |

| DMC0_CK     | DMC0 Clock (complement)     | Not Muxed | DMC0_CK   |

| DMC0_CS0    | DMC0 Chip Select 0          | Not Muxed | DMC0_CS0  |

| DMC0_DQ00   | DMC0 Data 0                 | Not Muxed | DMC0_DQ00 |

| DMC0_DQ01   | DMC0 Data 1                 | Not Muxed | DMC0_DQ01 |

| DMC0_DQ02   | DMC0 Data 2                 | Not Muxed | DMC0_DQ02 |

| DMC0_DQ03   | DMC0 Data 3                 | Not Muxed | DMC0_DQ03 |

| DMC0_DQ04   | DMC0 Data 4                 | Not Muxed | DMC0_DQ04 |

| DMC0_DQ05   | DMC0 Data 5                 | Not Muxed | DMC0_DQ05 |

| DMC0_DQ06   | DMC0 Data 6                 | Not Muxed | DMC0_DQ06 |

Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name | Description                                  | Port      | Pin Name      |

|-------------|----------------------------------------------|-----------|---------------|

| DMC0_DQ07   | DMC0 Data 7                                  | Not Muxed | DMC0_DQ07     |

| DMC0_DQ08   | DMC0 Data 8                                  | Not Muxed | DMC0_DQ08     |

| MC0_DQ09    | DMC0 Data 9                                  | Not Muxed | DMC0_DQ09     |

| DMC0_DQ10   | DMC0 Data 10                                 | Not Muxed | DMC0_DQ10     |

| DMC0_DQ11   | DMC0 Data 11                                 | Not Muxed | DMC0_DQ11     |

| DMC0_DQ12   | DMC0 Data 12                                 | Not Muxed | DMC0_DQ12     |

| DMC0_DQ13   | DMC0 Data 13                                 | Not Muxed | DMC0_DQ13     |

| MC0_DQ14    | DMC0 Data 14                                 | Not Muxed | DMC0_DQ14     |

| MC0_DQ15    | DMC0 Data 15                                 | Not Muxed | DMC0_DQ15     |

| MC0_LDM     | DMC0 Data Mask for Lower Byte                | Not Muxed | DMC0_LDM      |

| MC0_LDQS    | DMC0 Data Strobe for Lower Byte              | Not Muxed | DMC0_LDQS     |

| MC0_LDQS    | DMC0 Data Strobe for Lower Byte (complement) | Not Muxed | DMC0_LDQS     |

| MC0_ODT     | DMC0 On-die termination                      | Not Muxed | DMC0_ODT      |

| MC0_RAS     | DMC0 Row Address Strobe                      | Not Muxed | DMC0_RAS      |

| MC0_UDM     | DMC0 Data Mask for Upper Byte                | Not Muxed | DMC0_UDM      |

| MC0_UDQS    | DMC0 Data Strobe for Upper Byte              | Not Muxed | DMC0_UDQS     |

| DMC0_UDQS   | DMC0 Data Strobe for Upper Byte (complement) | Not Muxed | DMC0_UDQS     |

| MC0_VREF    | DMC0 Voltage Reference                       | Not Muxed | DMC0_VREF     |

| DMC0_WE     | DMC0 Write Enable                            | Not Muxed | DMC0_WE       |

| ND          | Ground                                       | Not Muxed | GND           |

| ND_HADC     | Ground HADC                                  | Not Muxed | GND_HADC      |

| IADC0_VIN0  | HADC0 Analog Input at channel 0              | Not Muxed | HADC0_VIN0    |

| IADC0_VIN1  | HADC0 Analog Input at channel 1              | Not Muxed | HADC0_VIN1    |

| IADC0_VIN2  | HADC0 Analog Input at channel 2              | Not Muxed | HADC0_VIN2    |

| IADC0_VIN3  | HADC0 Analog Input at channel 3              | Not Muxed | HADC0_VIN3    |

| IADC0_VREFN | HADC0 Ground Reference for ADC               | Not Muxed | HADC0_VREFN   |

| IADC0_VREFP | HADC0 External Reference for ADC             | Not Muxed | HADC0_VREFP   |

| TG_SWCLK    | TAPC0 Serial Wire Clock                      | Not Muxed | JTG_TCK_SWCLK |

| TG_SWDIO    | TAPC0 Serial Wire DIO                        | Not Muxed | JTG_TMS_SWDIO |

| TG_SWO      | TAPC0 Serial Wire Out                        | Not Muxed | JTG_TDO_SWO   |

| TG_TCK      | TAPC0 JTAG Clock                             | Not Muxed | JTG_TCK_SWCLK |

| TG_TDI      | TAPC0 JTAG Serial Data In                    | Not Muxed | JTG_TDI       |

| TG_TDO      | TAPC0 JTAG Serial Data Out                   | Not Muxed | JTG_TDO_SWO   |

| TG_TMS      | TAPC0 JTAG Mode Select                       | Not Muxed | JTG_TMS_SWDIO |

| TG_TRST     | TAPC0 JTAG Reset                             | Not Muxed | JTG_TRST      |

| ISI0_CD     | MSI0 Card Detect                             | A         | PA_08         |

| ISI0_CLK    | MSI0 Clock                                   | С         | PC_09         |

| ISI0_CMD    | MSI0 Command                                 | С         | PC_05         |

| ISI0_D0     | MSI0 Data 0                                  | С         | PC_08         |

| 1SI0_D1     | MSI0 Data 1                                  | С         | PC_04         |

| 1SI0_D2     | MSI0 Data 2                                  | С         | PC_07         |

| ISI0_D3     | MSI0 Data 3                                  | С         | PC_06         |

| ISI0_D4     | MSI0 Data 4                                  | С         | PC_10         |

| 1SI0_D5     | MSI0 Data 5                                  | С         | PC_11         |

| 1SI0_D6     | MSI0 Data 6                                  | С         | PC_12         |

| ASIO_D7     | MSI0 Data 7                                  | С         | PC_13         |

### Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name  | Description                                       | Port      | Pin Name    |

|--------------|---------------------------------------------------|-----------|-------------|

| MSIO_INT     | MSI0 eSDIO Interrupt Input                        | C         | PC_14       |

| PA_00-PA_15  | Position 00 through Position 15                   | A         | PA_00-PA_15 |

| PB_00-PB_15  | Position 00 through Position 15                   | В         | PB_00-PB_15 |

| PC_00-PC_14  | Position 00 through Position 14                   | с         | PC_00-PC_14 |

| PPI0_CLK     | EPPI0 Clock                                       | А         | PA_14       |

| PPI0_D00     | EPPIO Data 0                                      | В         | PB_07       |

| PPI0_D01     | EPPIO Data 1                                      | В         | PB_06       |

| PPI0_D02     | EPPIO Data 2                                      | В         | PB_05       |

| PPI0_D03     | EPPIO Data 3                                      | В         | PB_04       |

| PPI0_D04     | EPPIO Data 4                                      | В         | PB_03       |

| PPI0_D05     | EPPIO Data 5                                      | В         | PB_02       |

| PPI0_D06     | EPPIO Data 6                                      | В         | PB_01       |

| PPI0_D07     | EPPIO Data 7                                      | В         | PB_00       |

| PPI0_D08     | EPPIO Data 8                                      | A         | PA_11       |

| <br>PPI0_D09 | EPPIO Data 9                                      | A         | <br>PA_10   |

| PPI0_D10     | EPPIO Data 10                                     | A         | PA_09       |

| PPI0_D11     | EPPIO Data 11                                     | А         | PA_08       |

| PPI0_D12     | EPPIO Data 12                                     | с         | PC_03       |

| PPI0_D13     | EPPIO Data 13                                     | с         | PC_02       |

| PPI0_D14     | EPPIO Data 14                                     | С         | PC_01       |

| PPI0_D15     | EPPIO Data 15                                     | с         | PC_00       |

| PPI0_D16     | EPPIO Data 16                                     | В         | PB_08       |

| PPI0_D17     | EPPIO Data 17                                     | В         | PB_09       |

| PPI0_FS1     | EPPI0 Frame Sync 1 (HSYNC)                        | A         | PA_12       |

| PPI0_FS2     | EPPI0 Frame Sync 2 (VSYNC)                        | А         | PA_13       |

| PPI0_FS3     | EPPI0 Frame Sync 3 (FIELD)                        | А         | PA_15       |

| RTC0_CLKIN   | RTC0 Crystal input/external oscillator connection | Not Muxed | RTC0_CLKIN  |

| RTC0_XTAL    | RTC0 Crystal output                               | Not Muxed | RTC0_XTAL   |

| SMC0_A01     | SMC0 Address 1                                    | А         | PA_08       |

| 5MC0_A02     | SMC0 Address 2                                    | А         | PA_09       |

|              | SMC0 Address 3                                    | А         | <br>PA_10   |

|              | SMC0 Address 4                                    | A         | <br>PA_11   |

| SMC0_A05     | SMC0 Address 5                                    | A         | PA_07       |

|              | SMC0 Address 6                                    | А         | <br>PA_06   |

|              | SMC0 Address 7                                    | А         | <br>PA_05   |

|              | SMC0 Address 8                                    | А         | <br>PA_04   |

| SMC0_A09     | SMC0 Address 9                                    | С         | PC_01       |

| 5MC0_A10     | SMC0 Address 10                                   | C         | PC_02       |

| 5MC0_A11     | SMC0 Address 11                                   | C         | PC_03       |

| 5MC0_A12     | SMC0 Address 12                                   | C         | PC_04       |

| SMC0_ABE0    | SMC0 Byte Enable 0                                | A         | PA_00       |

| SMC0_ABE1    | SMC0 Byte Enable 1                                | A         | PA_01       |

| SMC0_AMS0    | SMC0 Memory Select 0                              | A         | PA_15       |

| SMC0_AMS1    | SMC0 Memory Select 1                              | A         | PA_02       |

| SMC0_AOE     | SMC0 Output Enable                                | A         | PA_12       |

| SMC0_ARDY    | SMC0 Asynchronous Ready                           | A         | PA_03       |

| Signal Name | Description              | Port      | Pin Name   |

|-------------|--------------------------|-----------|------------|

| UARTO_RX    | UARTO Receive            | В         | PB_09      |

| UART0_TX    | UARTO Transmit           | В         | PB_08      |

| UART1_CTS   | UART1 Clear to Send      | В         | PB_14      |

| UART1_RTS   | UART1 Request to Send    | В         | PB_13      |

| UART1_RX    | UART1 Receive            | С         | PC_01      |

| UART1_TX    | UART1 Transmit           | С         | PC_00      |

| USB0_CLKIN  | USB0 Clock/Crystal Input | Not Muxed | USB0_CLKIN |

| USB0_DM     | USB0 Data –              | Not Muxed | USB0_DM    |

| USB0_DP     | USB0 Data +              | Not Muxed | USB0_DP    |

| USB0_ID     | USB0 OTG ID              | Not Muxed | USB0_ID    |

| USB0_VBC    | USB0 VBUS Control        | Not Muxed | USB0_VBC   |

| USB0_VBUS   | USB0 Bus Voltage         | Not Muxed | USB0_VBUS  |

| USB0_XTAL   | USB0 Crystal             | Not Muxed | USB0_XTAL  |

| VDD_DMC     | VDD for DMC              | Not Muxed | VDD_DMC    |

| VDD_EXT     | External VDD             | Not Muxed | VDD_EXT    |

| VDD_HADC    | VDD for HADC             | Not Muxed | VDD_HADC   |

| VDD_INT     | Internal VDD             | Not Muxed | VDD_INT    |

| VDD_OTP     | VDD for OTP              | Not Muxed | VDD_OTP    |

| VDD_RTC     | VDD for RTC              | Not Muxed | VDD_RTC    |

| VDD_USB     | VDD for USB              | Not Muxed | VDD_USB    |

### Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name                      | Description                                                                   | Port   | Pin Name       |

|----------------------------------|-------------------------------------------------------------------------------|--------|----------------|

| SMC0_D11                         | SMC0 Data 11                                                                  | В      | PB_11          |

| SMC0_D12                         | SMC0 Data 12                                                                  | В      | PB_12          |

| SMC0_D13                         | SMC0 Data 13                                                                  | В      | PB_13          |

| SMC0_D14                         | SMC0 Data 14                                                                  | В      | PB_14          |

| SMC0_D15                         | SMC0 Data 15                                                                  | В      | PB_15          |

| SPI0_CLK                         | SPI0 Clock                                                                    | В      | PB_00          |

| SPI0_CLK                         | SPI0 Clock                                                                    | С      | PC_04          |

| SPI0_D2                          | SPI0 Data 2                                                                   | В      | PB_03          |

| SPI0_D2                          | SPI0 Data 2                                                                   | С      | PC_08          |

| SPI0_D3                          | SPI0 Data 3                                                                   | В      | PB_07          |

| SPI0_D3                          | SPI0 Data 3                                                                   | С      | PC_09          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                                     | В      | PB_01          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                                     | С      | PC_06          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                                     | В      | PB_02          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                                     | С      | PC_07          |

| SPI0_RDY                         | SPI0 Ready                                                                    | А      | PA_06          |

| SPI0_SEL1                        | SPI0 Slave Select Output 1                                                    | А      | PA_05          |

| SPI0_SEL2                        | SPI0 Slave Select Output 2                                                    | А      | PA_06          |

| SPI0_SEL4                        | SPI0 Slave Select Output 4                                                    | В      | PB_04          |

| SPI0_SEL5                        | SPI0 Slave Select Output 5                                                    | В      | PB_05          |

| SPI0_SEL6                        | SPI0 Slave Select Output 6                                                    | В      | PB_06          |

| SPI0_SS                          | SPI0 Slave Select Input                                                       | А      | PA_05          |

| SPI1_CLK                         | SPI1 Clock                                                                    | А      | PA_00          |

| SPI1_MISO                        | SPI1 Master In, Slave Out                                                     | А      | PA_01          |

| SPI1_MOSI                        | SPI1 Master Out, Slave In                                                     | А      | PA_02          |

|                                  | SPI1 Ready                                                                    | А      | <br>PA_03      |

| SPI1_SEL1                        | SPI1 Slave Select Output 1                                                    | А      | <br>PA_04      |

|                                  | SPI1 Slave Select Output 2                                                    | А      | <br>PA_03      |

|                                  | SPI1 Slave Select Output 3                                                    | с      | <br>PC_10      |

| SPI1_SEL4                        | SPI1 Slave Select Output 4                                                    | A      | PA_14          |

| SPI1_SS                          | SPI1 Slave Select Input                                                       | A      | PA_04          |

| SPI2_CLK                         | SPI2 Clock                                                                    | В      | PB_10          |

| SPI2_D2                          | SPI2 Data 2                                                                   | В      | PB_13          |

| SPI2_D3                          | SPI2 Data 3                                                                   | В      | PB_14          |

| SPI2_MISO                        | SPI2 Master In, Slave Out                                                     | В      | PB_11          |

| SPI2_MOSI                        | SPI2 Master Out, Slave In                                                     | В      | PB_12          |

| SPI2_RDY                         | SPI2 Ready                                                                    | A      | PA_04          |

| SPI2_SEL1                        | SPI2 Slave Select Output 1                                                    | В      | PB_15          |

| SPI2_SEL2                        | SPI2 Slave Select Output 1                                                    | В      | PB_08          |

| SPI2_SEL3                        | SPI2 Slave Select Output 2<br>SPI2 Slave Select Output 3                      | B      | PB_09          |

| SPI2_SELS                        | SPI2 Slave Select Output                                                      | B      | PB_15          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                                        | A      | PA_13          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                                        | C      | PC_09          |

| SPT0_ACLK<br>SPT0_AD0            | SPORTO Channel A Data 0                                                       |        | PC_09<br>PA_14 |

|                                  |                                                                               | A      |                |

|                                  |                                                                               |        |                |

| SPT0_AD0<br>SPT0_AD0<br>SPT0_AD1 | SPORTO Channel A Data 0<br>SPORTO Channel A Data 0<br>SPORTO Channel A Data 1 | C<br>C | PC_08<br>PC_00 |

Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

### GPIO MULTIPLEXING FOR 12 mm × 12 mm 88-LEAD LFCSP (QFN)

Table 12 through Table 14 identify the pin functions that aremultiplexed on the general-purpose I/O pins of the12 mm  $\times$  12 mm 88-Lead LFCSP (QFN) package.

#### Table 12. Signal Multiplexing for Port A

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed            |

|-------------|-------------|-------------|-------------|-------------|------------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap     |

| PA_00       | SPI1_CLK    |             | TRACE0_D07  | SMC0_ABE0   |                        |

| PA_01       | SPI1_MISO   |             | TRACE0_D06  | SMC0_ABE1   |                        |

| PA_02       | SPI1_MOSI   |             | TRACE0_D05  | SMC0_AMS1   |                        |

| PA_03       | SPI1_SEL2   | SPI1_RDY    |             | SMC0_ARDY   |                        |

| PA_04       | SPI1_SEL1   | TM0_TMR7    | SPI2_RDY    | SMC0_A08    | SPI1_SS                |

| PA_05       | TM0_TMR0    | SPI0_SEL1   |             | SMC0_A07    | SPI0_SS                |

| PA_06       | TM0_TMR1    | SPI0_SEL2   | SPI0_RDY    | SMC0_A06    |                        |

| PA_07       | TM0_TMR2    | SPT1_BTDV   | SPT1_ATDV   | SMC0_A05    | CNT0_DG                |

| PA_08       | PPI0_D11    | MSI0_CD     | SPT1_ACLK   | SMC0_A01    |                        |

| PA_09       | PPI0_D10    | TM0_TMR4    | SPT1_AFS    | SMC0_A02    |                        |

| PA_10       | PPI0_D09    | TM0_TMR5    | SPT1_AD0    | SMC0_A03    |                        |

| PA_11       | PPI0_D08    | TM0_TMR6    | SPT1_AD1    | SMC0_A04    |                        |

| PA_12       | PPI0_FS1    | CAN1_RX     | SPTO_AFS    | SMC0_AOE    | TM0_ACI6/SYS_<br>WAKE4 |

| PA_13       | PPI0_FS2    | CAN1_TX     | SPT0_ACLK   | SMC0_ARE    | CNT0_ZM                |

| PA_14       | PPI0_CLK    | SPI1_SEL4   | SPT0_AD0    | SMC0_AWE    | TM0_ACLK5              |

| PA_15       | PPI0_FS3    | SPT0_ATDV   | SPT0_BTDV   | SMC0_AMS0   | CNT0_UD                |

#### Table 13. Signal Multiplexing for Port B

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PB_00       | PPI0_D07    | SPT1_BCLK   | SPI0_CLK    | SMC0_D07    | TM0_ACLK3          |

| PB_01       | PPI0_D06    | SPT1_BFS    | SPI0_MISO   | SMC0_D06    | TM0_ACI1           |

| PB_02       | PPI0_D05    | SPT1_BD0    | SPI0_MOSI   | SMC0_D05    |                    |

| PB_03       | PPI0_D04    | SPT1_BD1    | SPI0_D2     | SMC0_D04    |                    |

| PB_04       | PPI0_D03    | SPT0_BCLK   | SPI0_SEL4   | SMC0_D03    | TM0_ACLK6          |

| PB_05       | PPI0_D02    | SPT0_BD0    | SPI0_SEL5   | SMC0_D02    |                    |

| PB_06       | PPI0_D01    | SPT0_BFS    | SPI0_SEL6   | SMC0_D01    | TM0_CLK            |

| PB_07       | PPI0_D00    | SPT0_BD1    | SPI0_D3     | SMC0_D00    | SYS_WAKE0          |

| PB_08       | UART0_TX    | PPI0_D16    | SPI2_SEL2   | SMC0_D08    | SYS_WAKE1          |

| PB_09       | UARTO_RX    | PPI0_D17    | SPI2_SEL3   | SMC0_D09    | TM0_ACI3           |

| PB_10       | SPI2_CLK    |             | TRACE0_CLK  | SMC0_D10    | TM0_ACLK4          |

| PB_11       | SPI2_MISO   |             | TRACE0_D04  | SMC0_D11    |                    |

| PB_12       | SPI2_MOSI   |             | TRACE0_D03  | SMC0_D12    | SYS_WAKE2          |

| PB_13       | SPI2_D2     | UART1_RTS   | TRACE0_D02  | SMC0_D13    |                    |

| PB_14       | SPI2_D3     | UART1_CTS   | TRACE0_D01  | SMC0_D14    |                    |

| PB_15       | SPI2_SEL1   |             | TRACE0_D00  | SMC0_D15    | SPI2_SS            |

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_12       | 1/0  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 1 (HSYNC)   CAN1<br>Receive   SPORT0 Channel A Frame Sync<br> SMC0 Output Enable  SYS Power<br>Saving Mode Wakeup 4   TM0 Alternate<br>Capture Input 6<br>Notes: If hibernate mode is used one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down. |

| PA_13       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 2 (VSYNC)   CAN1<br>Transmit   SPORT0 Channel A Clock  <br>SMC0 Read Enable   CNT0 Count Zero<br>Marker<br>Notes: No notes.                                                                                                                                                                                                                               |

| PA_14       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Clock   SPI1 Slave Select<br>Output 4   SPORT0 Channel A Data 0  <br>SMC0 Write Enable   TM0 Alternate<br>Clock 5<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                 |

| PA_15       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 3 (FIELD)   SPT0<br>Channel A Transmit Data Valid   SPT0<br>Channel B Transmit Data Valid   SMC0<br>Memory Select 0   CNT0 Count Up and<br>Direction<br>Notes: May require a pull-up if used as<br>an SMC memory select. Check the data<br>sheet requirements of the IC it connects<br>to.                                                                |

| PB_00       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 7   SPT1 Channel B Clock<br>  SPI0 Clock   SMC0 Data 7   TM0<br>Alternate Clock 3<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.                                                                                                                                                                                       |

| PB_01       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 6   SPT1 Channel B<br>Frame Sync   SPI0 Master In, Slave Out  <br>SMC0 Data 6   TM0 Alternate Capture<br>Input 1<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.                                                                                                                                                                         |

| PB_02       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 5   SPT1 Channel B Data<br>0   SPI0 Master Out, Slave In   SMC0 Data<br>5<br>Notes: No notes.                                                                                                                                                                                                                                                                   |

| PB_03       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 4   SPT1 Channel B Data<br>1   SPI0 Data 2   SMC0 Data 4<br>Notes: No notes.                                                                                                                                                                                                                                                                                    |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

#### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                             |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TWI0_SCL    | 1/0  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Clock<br>Notes: Open drain, requires external<br>pull up. Consult version 2.1 of the I2C<br>specification for the proper resistor<br>value. If TWI is not used, connect to<br>ground.                              |

| TWI0_SDA    | 1/0  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Data<br>Notes: Open drain, requires external<br>pull up. Consult version 2.1 of the I2C<br>specification for the proper resistor<br>value. If TWI is not used, connect to<br>ground.                               |

| USB0_CLKIN  | a    | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Clock/Crystal Input<br>Notes: If USB is not used, connect to<br>ground. Active during reset                                                                                                                               |

| USB0_DM     | I/O  | F              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Data –<br>Notes: Pull low if not using USB. For<br>complete documentation of hibernate<br>behavior when USB is used, see the USB<br>chapter in the HRM.                                                                   |

| USB0_DP     | I/O  | F              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Data +<br>Notes: Pull low if not using USB. For<br>complete documentation of hibernate<br>behavior when USB is used, see the USB<br>chapter in the HRM.                                                                   |

| USB0_ID     | 1/0  | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 OTG ID<br>Notes: If USB is not used connect to<br>ground. When USB is being used, the<br>internal pull-up that is present during<br>hibernate is programmable. See the<br>USB chapter in the HRM. Active during<br>reset. |

| USB0_VBC    | I/O  | E              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 VBUS Control<br>Notes: If USB is not, used pull low.                                                                                                                                                                      |

| USB0_VBUS   | I/O  | G              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Bus Voltage<br>Notes: If USB is not used, connect to<br>ground.                                                                                                                                                           |

| USB0_XTAL   | а    | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Crystal<br>Notes: No notes.                                                                                                                                                                                               |

| VDD_DMC     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for DMC<br>Notes: If the DMC is not used, connect<br>to VDD_INT.                                                                                                                                                           |

| VDD_EXT     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: External VDD<br>Notes: Must be powered.                                                                                                                                                                                        |

| VDD_HADC    | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for HADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                                                                                                              |

| VDD_INT     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: Internal VDD<br>Notes: Must be powered.                                                                                                                                                                                        |

### **SPECIFICATIONS**

For information about product specifications, contact your Analog Devices, Inc. representative.

### **OPERATING CONDITIONS**

| Parameter                          |                                    | Test Conditions/Comments                               | Min                      | Nominal                  | Max                                    | Unit |

|------------------------------------|------------------------------------|--------------------------------------------------------|--------------------------|--------------------------|----------------------------------------|------|

| V <sub>DD_INT</sub>                | Internal Supply Voltage            | CCLK ≤ 400 MHz                                         | 1.045                    | 1.100                    | 1.155                                  | V    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 1.7                      | 1.8                      | 1.9                                    | v    |

| $V_{DD\_EXT}^{1}$                  | External Supply Voltage            |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| V <sub>DD_DMC</sub>                | DDR2/LPDDR Supply Voltage          |                                                        | 1.7                      | 1.8                      | 1.9                                    | v    |

| $V_{DD_USB}^{2}$                   | USB Supply Voltage                 |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_{RTC}}$                     | Real-Time Clock Supply Voltage     |                                                        | 2.00                     | 3.30                     | 3.47                                   | v    |

| $V_{DD\_HADC}$                     | Housekeeping ADC Supply<br>Voltage |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| $V_{DD_OTP}^{1}$                   | OTP Supply Voltage                 |                                                        |                          |                          |                                        |      |

|                                    | For Reads                          |                                                        | 2.25                     | 3.30                     | 3.47                                   | V    |

|                                    | For Writes                         |                                                        | 3.13                     | 3.30                     | 3.47                                   | v    |

| V <sub>DDR_VREF</sub>              | DDR2 Reference Voltage             |                                                        | $0.49 \times V_{DD_DMC}$ | $0.50 \times V_{DD_DMC}$ | $0.51 \times V_{DD_DMC}$               | v    |

| $V_{HADC_{REF}}^{3}$               | HADC Reference Voltage             |                                                        | 2.5                      | 3.30                     | V <sub>DD_HADC</sub>                   | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD_{EXT}} = 3.47 V$                                | 2.0                      |                          |                                        | v    |

| $V_{IH}^{4}$                       | High Level Input Voltage           | $V_{DD\_EXT} = 1.9 V$                                  | $0.7 \times V_{DD\_EXT}$ |                          |                                        | V    |

| V <sub>IHTWI</sub> <sup>5, 6</sup> | High Level Input Voltage           | $V_{DD\_EXT} = maximum$                                | $0.7 \times V_{VBUSTWI}$ |                          | V <sub>VBUSTWI</sub>                   | V    |

| $V_{\text{IH}_{DDR2}}^{7}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $V_{DDR\_REF} + 0.25$    |                          |                                        | v    |

| $V_{\text{IH\_LPDDR}}^{8}$         |                                    | $V_{DD_DMC} = 1.9 V$                                   | $0.8 \times V_{DD_DMC}$  |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 1.075 V$                                     | 0.50                     |                          |                                        | V    |

| V <sub>ID_DDR2</sub> 9             | Differential Input Voltage         | $V_{IX} = 0.725 V$                                     | 0.55                     |                          |                                        | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD_{EXT}} = 3.13 V$                                |                          |                          | 0.8                                    | V    |

| $V_{IL}^{4}$                       | Low Level Input Voltage            | $V_{DD\_EXT} = 1.7 V$                                  |                          |                          | $0.3 \times V_{\text{DD}\_\text{EXT}}$ | V    |

| V <sub>ILTWI</sub> 5, 6            | Low Level Input Voltage            | $V_{DD\_EXT} = minimum$                                |                          |                          | $0.3 	imes V_{VBUSTWI}$                | V    |

| $V_{IL_DDR2}^{7}$                  |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $V_{DDR_{REF}} - 0.25$                 | V    |

| $V_{IL\_LPDDR}^{8}$                |                                    | $V_{DD_DMC} = 1.7 V$                                   |                          |                          | $0.2 \times V_{DD_DMC}$                | V    |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = 0^{\circ}C \text{ to } +70^{\circ}C$    | 0                        |                          | 105                                    | °C   |

| TJ                                 | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +85^{\circ}C$  | -40                      |                          | +105                                   | °C   |

| T                                  | Junction Temperature               | $T_{AMBIENT} = -40^{\circ}C \text{ to } +105^{\circ}C$ | -40                      |                          | +125                                   | °C   |

<sup>1</sup>Must remain powered (even if the associated function is not used).

<sup>2</sup> If not used, connect to 1.8 V or 3.3 V.

$^{3}\mathrm{V}_{\mathrm{HADC\_VREF}}$  should always be less than  $\mathrm{V}_{\mathrm{DD\_HADC}}.$

<sup>4</sup> Parameter value applies to all input and bidirectional signals except RTC signals, TWI signals, DMC0 signals, and USB0 signals.

<sup>5</sup> Parameter applies to TWI signals.

$^{6}$  TWI signals are pulled up to  $V_{BUSTWI}$ . See Table 16.

<sup>7</sup> Parameter applies to DMC0 signals in DDR2 mode.

<sup>8</sup> Parameter applies to DMC0 signals in LPDDR mode.

<sup>9</sup> Parameter applies to signals DMC0\_LDQS, <u>DMC0\_LDQS</u>, DMC0\_UDQS, <u>DMC0\_UDQS</u> when used in DDR2 differential input mode.

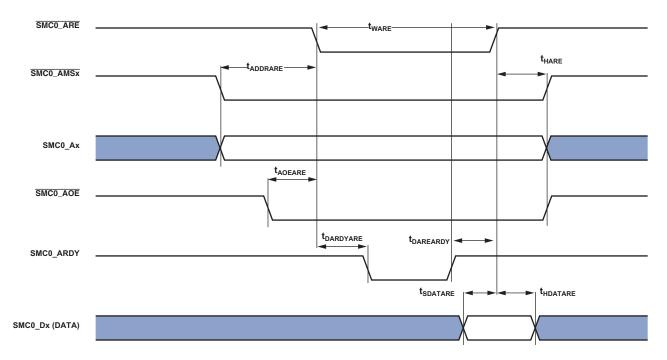

Figure 10. Asynchronous Read

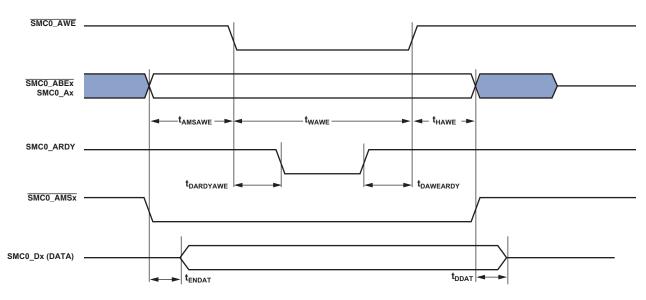

#### Asynchronous Write

Table 35 and Figure 14 show asynchronous memory write timing, related to the static memory controller (SMC).

#### Table 35. Asynchronous Memory Write (BxMODE = b#00)

|                                |                                                                 | V <sub>DD</sub><br>1.8V N                    | _ <sub>EXT</sub><br>ominal                 | V <sub>DD</sub><br>3.3 V No                  |                                            |      |

|--------------------------------|-----------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------------|--------------------------------------------|------|

| Parameter                      | r                                                               | Min                                          | Max                                        | Min                                          | Max                                        | Unit |

| Timing Req                     | uirement                                                        |                                              |                                            |                                              |                                            |      |

| t <sub>DARDYAWE</sub> 1        | SMC0_ARDY Valid After<br>SMC0_AWE Low <sup>2</sup>              |                                              | (WAT – 2.5) ×<br>t <sub>SCLK0</sub> – 17.5 |                                              | (WAT – 2.5) ×<br>t <sub>SCLK0</sub> – 17.5 | ns   |

| Switching (                    | Characteristics                                                 |                                              |                                            |                                              |                                            |      |

| t <sub>endat</sub>             | DATA Enable After SMC0_AMSx<br>Assertion                        | -3                                           |                                            | -2                                           |                                            | ns   |

| t <sub>DDAT</sub>              | DATA Disable After <u>SMC0_AMSx</u><br>Deassertion              |                                              | 4.5                                        |                                              | 4                                          | ns   |

| t <sub>AMSAWE</sub>            | SMC0_Ax/SMC0_AMSx Assertion<br>Before SMC0_AWE Low <sup>3</sup> | $(PREST + WST + PREAT) \times t_{SCLK0} - 2$ |                                            | $(PREST + WST + PREAT) \times t_{SCLK0} - 4$ |                                            | ns   |

| t <sub>HAWE</sub>              | Output <sup>4</sup> Hold After <mark>SMC0_AWE</mark> High⁵      | $WHT \times t_{SCLK0}$                       |                                            | $WHT \times t_{SCLK0}$                       |                                            | ns   |

| t <sub>WAWE</sub> <sup>6</sup> | SMC0_AWE Active Low Width <sup>6</sup>                          | WAT $\times$ t <sub>SCLK0</sub> – 2          |                                            | WAT $\times$ t <sub>SCLK0</sub> – 2          |                                            | ns   |

| t <sub>DAWEARDY</sub> 1        | SMC0_AWE High Delay After<br>SMC0_ARDY Assertion                |                                              | $3.5 \times t_{SCLK0} + 17.5$              |                                              | $3.5 \times t_{SCLK0} + 17.5$              | ns   |

<sup>1</sup>SMC\_BxCTL.ARDYEN bit = 1.

$^2\,\rm WAT$  value set using the SMC\_BxTIM.WAT bits.

<sup>3</sup> PREST, WST, PREAT values set using the SMC\_BxETIM.PREST bits, SMC\_BxTIM.WST bits, SMC\_BxETIM.PREAT bits, and the SMC\_BxTIM.RAT bits.

<sup>4</sup> Output signals are DATA, SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_ABEx</u>.

<sup>5</sup> WHT value set using the SMC\_BxTIM.WHT bits.

<sup>6</sup>SMC\_BxCTL.ARDYEN bit = 0.

Figure 14. Asynchronous Write

#### Mobile DDR SDRAM Clock and Control Cycle Timing

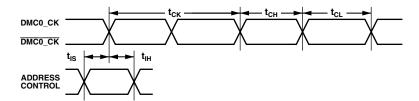

Table 42 and Figure 20 show mobile DDR SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

#### Table 42. Mobile DDR SDRAM Clock and Control Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

| Parameter       |                                                | Min  | Мах  | Unit            |

|-----------------|------------------------------------------------|------|------|-----------------|

| Switching       | Characteristics                                |      |      |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |      | ns              |

| t <sub>CH</sub> | Minimum Clock Pulse Width                      | 0.45 | 0.55 | t <sub>CK</sub> |

| t <sub>CL</sub> | Maximum Clock Pulse Width                      | 0.45 | 0.55 | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 1.5  |      | ns              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMC0_CK Rise  | 1.5  |      | ns              |

NOTE: CONTROL = DMC0\_CS0, DMC0\_CKE, DMC0\_RAS, DMC0\_CAS, AND DMC0\_WE. ADDRESS = DMC0\_A00-13, AND DMC0\_BA0-2.

Figure 20. Mobile DDR SDRAM Clock and Control Cycle Timing

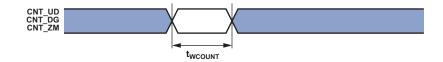

#### Up/Down Counter/Rotary Encoder Timing

Table 47 and Figure 25 describe timing, related to the general-purpose counter (CNT).

#### Table 47. Up/Down Counter/Rotary Encoder Timing

|                     |                                                  | V <sub>DD_EXT</sub><br>1.8 V Nominal |     | V <sub>DD_EXT</sub><br>3.3 V Nominal |     |      |

|---------------------|--------------------------------------------------|--------------------------------------|-----|--------------------------------------|-----|------|

| Parameter           |                                                  | Min                                  | Max | Min                                  | Max | Unit |

| Timing Requirement  |                                                  |                                      |     |                                      |     |      |

| t <sub>wcount</sub> | Up/Down Counter/Rotary Encoder Input Pulse Width | $2 \times t_{SCLK0}$                 |     | $2 \times t_{SCLK0}$                 |     | ns   |

Figure 25. Up/Down Counter/Rotary Encoder Timing

#### Serial Peripheral Interface (SPI) Port—Slave Timing

Table 55 and Figure 32 describe serial peripheral interface (SPI) port slave operations. Note that:

- In dual mode data transmit, the SPI\_MOSI signal is also an output.

- In quad mode data transmit, the SPI\_MOSI, SPI\_D2, and SPI\_D3 signals are also outputs.

- In dual mode data receive, the SPI\_MISO signal is also an input.

- In quad mode data receive, the SPI\_MISO, SPI\_D2, and SPI\_D3 signals are also inputs.

- In SPI slave mode, the SPI clock is supplied externally and is called f<sub>SPICLKEXT</sub>:

$$t_{SPICLKEXT} = \frac{1}{f_{SPICLKEXT}}$$

#### Table 55. Serial Peripheral Interface (SPI) Port—Slave Timing

|                     |                                                        |                               | V <sub>DD_EXT</sub><br>1.8V Nominal |                              | V <sub>DD_EXT</sub><br>3.3V Nominal |      |

|---------------------|--------------------------------------------------------|-------------------------------|-------------------------------------|------------------------------|-------------------------------------|------|

| Parameter           |                                                        | Min                           | Мах                                 | Min                          | Max                                 | Unit |

| Timing Red          | quirements                                             |                               |                                     |                              |                                     |      |

| t <sub>SPICHS</sub> | SPI_CLK High Period <sup>1</sup>                       | $(0.5 \times t_{SPICLKEXT})$  | - 1.5                               | $(0.5 \times t_{SPICLKEXT})$ | <sub>r</sub> ) – 1.5                | ns   |

| t <sub>SPICLS</sub> | SPI_CLK Low Period <sup>1</sup>                        | $(0.5 \times t_{SPICLKEXT})$  | - 1.5                               | $(0.5 \times t_{SPICLKEXT})$ | <sub>r</sub> ) – 1.5                | ns   |

| t <sub>SPICLK</sub> | SPI_CLK Period <sup>1</sup>                            | t <sub>SPICLKEXT</sub> – 1.5  |                                     | t <sub>SPICLKEXT</sub> – 1.5 |                                     | ns   |

| t <sub>HDS</sub>    | Last SPI_CLK Edge to SPI_SS Not Asserted (NonSPIHP)    | 5                             |                                     | 5                            |                                     | ns   |

| t <sub>HDS</sub>    | Last SPI_CLK Edge to SPI_SS Not Asserted (Using SPIHP) | $1.5 \times t_{SCLK0}$        |                                     | $1.5 	imes t_{SCLK0}$        |                                     | ns   |

| t <sub>SPITDS</sub> | Sequential Transfer Delay (NonSPIHP)                   | $0.5 \times t_{SPICLK} - 1.5$ | 5                                   | $0.5 \times t_{SPICLK} - 1$  | 1.5                                 | ns   |

| t <sub>SPITDS</sub> | Sequential Transfer Delay (Using SPIHP)                | $3 \times t_{\text{SCLK0}}$   |                                     | $3 \times t_{SCLK0}$         |                                     | ns   |

| t <sub>SDSCI</sub>  | SPI_SS Assertion to First SPI_CLK Edge                 | 11.5                          |                                     | 11.5                         |                                     | ns   |

| t <sub>SSPID</sub>  | Data Input Valid to SPI_CLK Edge (Data Input<br>Setup) | 1.5                           |                                     | 1                            |                                     | ns   |

| t <sub>HSPID</sub>  | SPI_CLK Sampling Edge to Data Input Invalid            | 3.3                           |                                     | 3                            |                                     | ns   |

| Switching           | Characteristics                                        |                               |                                     |                              |                                     |      |

| t <sub>DSOE</sub>   | SPI_SS Assertion to Data Out Active                    | 0                             | 17.5                                | 0                            | 14.5                                | ns   |

| t <sub>DSDHI</sub>  | SPI_SS Deassertion to Data High Impedance              | 0                             | 13                                  | 0                            | 11.5                                | ns   |

| t <sub>DDSPID</sub> | SPI_CLK Edge to Data Out Valid (Data Out Delay)        |                               | 17.5                                |                              | 14.5                                | ns   |

| t <sub>HDSPID</sub> | SPI_CLK Edge to Data Out Invalid (Data Out Hold)       | 2.5                           |                                     | 2.5                          |                                     | ns   |

<sup>1</sup>This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external SPI\_CLK. For the external SPI\_CLK ideal maximum frequency see the f<sub>SPICLKTEXT</sub> specification in Table 18 on Page 52 of Clock Related Operating Conditions.

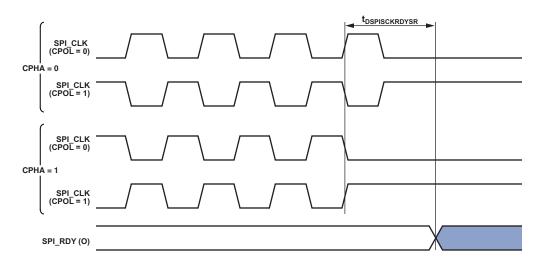

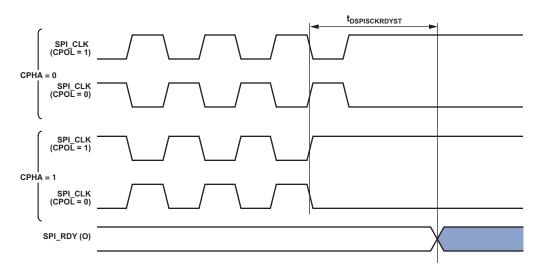

#### Serial Peripheral Interface (SPI) Port—SPI\_RDY Slave Timing

Table 56. SPI Port—SPI\_RDY Slave Timing

|                           |                                                                           | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal       |                                     |      |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|------|

| Parameter                 |                                                                           | Min                                              | Max                                 | Unit |

| Switching C               | haracteristics                                                            |                                                  |                                     |      |

| t <sub>dspisckrdysr</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Receive  | $2.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $3.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

| t <sub>dspisckrdyst</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Transmit | $3.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $4.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

Figure 33. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Receive (FCCH = 0)

Figure 34. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Transmit (FCCH = 1)

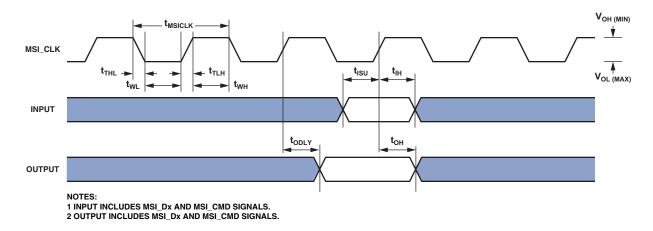

Figure 49. MSI Controller Timing

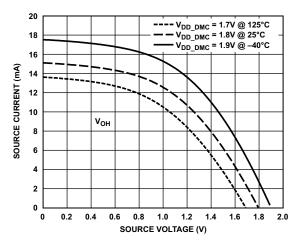

Figure 61. Driver Type B and Device Driver C (DDR Drive Strength  $60 \Omega$ )

#### **TEST CONDITIONS**

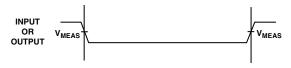

All timing requirements appearing in this data sheet were measured under the conditions described in this section. Figure 62 shows the measurement point for ac measurements (except output enable/disable). The measurement point  $V_{\text{MEAS}}$  is  $V_{\text{DD}\_\text{EXT}}/2$  for  $V_{\text{DD}\_\text{EXT}}$  (nominal) = 1.8 V/3.3 V.

Figure 62. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

#### **Output Enable Time Measurement**

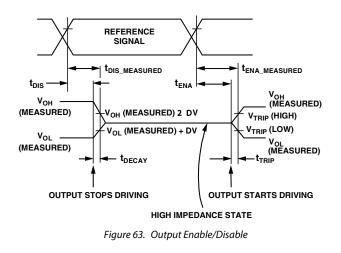

Output balls are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving.

The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown on the right side of Figure 63.

The time  $t_{ENA\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage reaches  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low). For  $V_{DD\_EXT}$  (nominal) = 1.8 V,  $V_{TRIP}$  (high) is 1.05 V, and  $V_{TRIP}$  (low) is 0.75 V. For  $V_{DD\_EXT}$  (nominal) = 3.3 V,  $V_{TRIP}$  (high) is 1.9 V, and  $V_{TRIP}$  (low) is 1.4 V. Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low) trip voltage.

Time  $t_{ENA}$  is calculated as shown in the equation:

$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$

If multiple balls (such as the data bus) are enabled, the measurement value is that of the first ball to start driving.

#### **Output Disable Time Measurement**

Output balls are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEASURED}$  and  $t_{DECAY}$  as shown on the left side of Figure 63.

$$t_{DIS} = t_{DIS\_MEASURED} - t_{DECAY}$$

The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load,  $C_L$  and the load current,  $I_L$ . This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The time  $t_{DECAY}$  is calculated with test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.25 V for  $V_{DD\_EXT}$  (nominal) = 3.3 V and 0.15 V for  $V_{DD\_EXT}$  (nominal) = 1.8V.

The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches, to when the output voltage decays  $\Delta V$  from the measured output high or output low voltage.

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the previous equation. Choose  $\Delta V$  to be the difference between the processor's output voltage and the input threshold for the device requiring the hold time.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the various output disable times as specified in the Timing Specifications on Page 60.