Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| 2 0 0 0 0 0             |                                                                                           |

|-------------------------|-------------------------------------------------------------------------------------------|

| Product Status          | Active                                                                                    |

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 1MB                                                                                       |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                             |

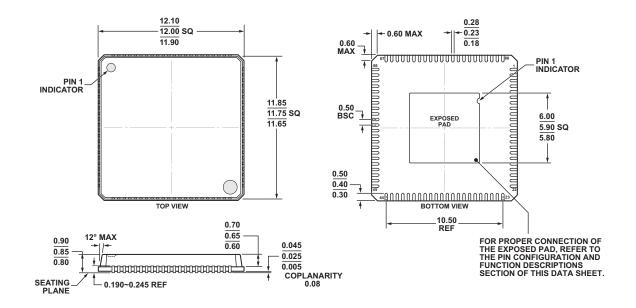

| Package / Case          | 88-VFQFN Exposed Pad, CSP                                                                 |

| Supplier Device Package | 88-LFCSP-VQ (12x12)                                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf706kcpz-3                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

system event or fault if enabled. ECC protection is fully transparent to the user, even if L2 memory is read or written by 8-bit or 16-bit entities.

## **CRC-Protected Memories**

While parity bit and ECC protection mainly protect against random soft errors in L1 and L2 memory cells, the CRC engines can be used to protect against systematic errors (pointer errors) and static content (instruction code) of L1, L2, and even L3 memories (DDR2, LPDDR). The processor features two CRC engines which are embedded in the memory-to-memory DMA controllers. CRC checksums can be calculated or compared on the fly during memory transfers, or one or multiple memory regions can be continuously scrubbed by a single DMA work unit as per DMA descriptor chain instructions. The CRC engine also protects data loaded during the boot process.

### **Memory Protection**

The Blackfin+ core features a memory protection concept, which grants data and/or instruction accesses to enabled memory regions only. A supervisor mode vs. user mode programming model supports dynamically varying access rights. Increased flexibility in memory page size options supports a simple method of static memory partitioning.

## System Protection

The system protection unit (SPU) guards against accidental or unwanted access to the MMR space of a peripheral by providing a write-protection mechanism. The user is able to choose and configure the peripherals that are protected as well as configure which ones of the four system MMR masters (core, memory DMA, the SPI host port, and Coresight debug) the peripherals are guarded against.

The SPU is also part of the security infrastructure. Along with providing write-protection functionality, the SPU is employed to define which resources in the system are secure or non-secure and to block access to secure resources from non-secure masters.

Synonymously, the system memory protection unit (SMPU) provides memory protection against read and/or write transactions to defined regions of memory. There are two SMPU units in the ADSP-BF70x processors. One is for the L2 memory and the other is for the external DDR memory.

The SMPU is also part of the security infrastructure. It allows the user to not only protect against arbitrary read and/or write transactions, but it also allows regions of memory to be defined as secure and prevent non-secure masters from accessing those memory regions.

## Watchpoint Protection

The primary purpose of watchpoints and hardware breakpoints is to serve emulator needs. When enabled, they signal an emulator event whenever user-defined system resources are accessed or the core executes from user-defined addresses. Watchpoint events can be configured such that they signal the events to the fault management unit of the SEC.

### Watchdog

The on-chip software watchdog timer can supervise the Blackfin+ core.

#### **Bandwidth Monitor**

Memory-to-memory DMA channels are equipped with a bandwidth monitor mechanism. They can signal a system event or fault when transactions tend to starve because system buses are fully loaded with higher-priority traffic.

## Signal Watchdogs

The eight general-purpose timers feature modes to monitor offchip signals. The watchdog period mode monitors whether external signals toggle with a period within an expected range. The watchdog width mode monitors whether the pulse widths of external signals are within an expected range. Both modes help to detect undesired toggling (or lack thereof) of system-level signals.

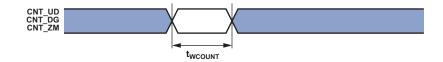

## **Up/Down Count Mismatch Detection**

The GP counter can monitor external signal pairs, such as request/grant strobes. If the edge count mismatch exceeds the expected range, the GP counter can flag this to the processor or to the fault management unit of the SEC.

### Fault Management

The fault management unit is part of the system event controller (SEC). Any system event, whether a dual-bit uncorrectable ECC error, or any peripheral status interrupt, can be defined as being a fault. Additionally, the system events can be defined as an interrupt to the core. If defined as such, the SEC forwards the event to the fault management unit, which may automatically reset the entire device for reboot, or simply toggle the SYS\_FAULT output pin to signal off-chip hardware. Optionally, the fault management unit can delay the action taken through a keyed sequence, to provide a final chance for the Blackfin+ core to resolve the issue and to prevent the fault action from being taken.

## ADDITIONAL PROCESSOR PERIPHERALS

The processor contains a rich set of peripherals connected to the core through several high-bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the block diagram on Page 1). The processor contains high-speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

The following sections describe additional peripherals that were not previously described.

#### Timers

The processor includes several timers which are described in the following sections.

### **General-Purpose Timers**

There is one GP timer unit, and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TIMER\_TMRx pins, an external TIMER\_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The GP timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals through the TRU (for instance, to signal a fault). Each timer may also be started and/or stopped by any TRU master without core intervention.

## **Core Timer**

The processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

### Watchdog Timer

The core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, through generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts down to zero from the programmed value. This protects the system from remaining in an unknown state where software that would normally reset the timer has stopped running due to an external noise condition or software error.

After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in its timer control register that is set only upon a watchdog-generated reset.

## Serial Ports (SPORTs)

Two synchronous serial ports (comprised of four half-SPORTs) provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices' audio codecs, ADCs, and DACs. Each half-SPORT is made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial port data can be automatically transferred to and from on-chip memory/external memory through dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. In this configuration, one SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in six modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- Left-justified mode

- Right-justified mode

### **General-Purpose Counters**

A 32-bit counter is provided that can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is either controlled by a levelsensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumbwheel devices. All three pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable this timer to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmed count values are exceeded.

## Parallel Peripheral Interface (PPI)

The processor provides a parallel peripheral interface (PPI) that supports data widths up to 18 bits. The PPI supports direct connection to TFT LCD panels, parallel analog-to-digital and digital-to-analog converters, video encoders and decoders, image sensor modules, and other general-purpose peripherals.

The following features are supported in the PPI module:

- Programmable data length: 8 bits, 10 bits, 12 bits, 14 bits, 16 bits, and 18 bits per clock.

- Various framed, non-framed, and general-purpose operating modes. Frame syncs can be generated internally or can be supplied by an external device.

- ITU-656 status word error detection and correction for ITU-656 receive modes and ITU-656 preamble and status word decode.

- Optional packing and unpacking of data to/from 32 bits from/to 8 bits, 16 bits and 24 bits. If packing/unpacking is enabled, endianness can be configured to change the order of packing/unpacking of bytes/words.

- RGB888 can be converted to RGB666 or RGB565 for transmit modes.

- Various de-interleaving/interleaving modes for receiving/transmitting 4:2:2 YCrCb data.

- Configurable LCD data enable (DEN) output available on Frame Sync 3.

### Table 3. Clock Dividers

|                                                            | Divider (if Available on    |

|------------------------------------------------------------|-----------------------------|

| Clock Source                                               | SYS_CLKOUT)                 |

| CCLK (Core Clock)                                          | By 16                       |

| SYSCLK (System Clock)                                      | Ву 8                        |

| SCLK0 (System Clock, All Peripherals not Covered by SCLK1) | Not available on SYS_CLKOUT |

| SCLK1 (System Clock for Crypto<br>Engines and MDMA)        | Ву 8                        |

| DCLK (LPDDR/DDR2 Clock)                                    | Ву 8                        |

| OCLK (Output Clock)                                        | Programmable                |

| CLKBUF                                                     | None, direct from SYS_CLKIN |

## **Power Management**

As shown in Table 4, the processor supports multiple power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate Specifications table for processor operating conditions; even if the feature/peripheral is not used.

### Table 4. Power Domains

| Power Domain                                       | V <sub>DD</sub> Range |

|----------------------------------------------------|-----------------------|

| All Internal Logic                                 | V <sub>DD_INT</sub>   |

| DDR2/LPDDR                                         | V <sub>DD_DMC</sub>   |

| USB                                                | $V_{DD_{USB}}$        |

| OTP Memory                                         | V <sub>DD_OTP</sub>   |

| HADC                                               | V <sub>DD_HADC</sub>  |

| RTC                                                | V <sub>DD_RTC</sub>   |

| All Other I/O (Includes SYS, JTAG, and Ports Pins) | V <sub>DD_EXT</sub>   |

The dynamic power management feature of the processor allows the processor's core clock frequency ( $f_{CCLK}$ ) to be dynamically controlled.

The power dissipated by a processor is largely a function of its clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

See Table 5 for a summary of the power settings for each mode.

## Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed, providing capability for maximum operational frequency. This is the power-up default execution state in which maximum performance can be achieved. The processor core and all enabled peripherals run at full speed.

## Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core and to all synchronous peripherals. Asynchronous peripherals may still be running but cannot access internal resources or external memory.

#### Table 5. Power Settings

| Mode/State | PLL      | PLL<br>Bypassed |          | f <sub>sysclk</sub> ,<br>f <sub>DCLK</sub> ,<br>f <sub>sclk0</sub> ,<br>f <sub>sclk1</sub> | Core<br>Power |

|------------|----------|-----------------|----------|--------------------------------------------------------------------------------------------|---------------|

| Full On    | Enabled  | No              | Enabled  | Enabled                                                                                    | On            |

| Deep Sleep | Disabled | _               | Disabled | Disabled                                                                                   | On            |

| Hibernate  | Disabled | —               | Disabled | Disabled                                                                                   | Off           |

### Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling the voltage and clocks to the processor core and to all of the peripherals. This setting signals the external voltage regulator supplying the VDD\_INT pins to shut off using the SYS\_ EXTWAKE signal, which provides the lowest static power dissipation.

Any critical information stored internally (for example, memory contents, register contents, and other information) must be written to a nonvolatile storage device (or self-refreshed DRAM) prior to removing power if the processor state is to be preserved.

Because the  $V_{DD\_EXT}$  pins can still be supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to still have power applied without drawing unwanted current.

## **Reset Control Unit**

Reset is the initial state of the whole processor or the core and is the result of a hardware- or software-triggered event. In this state, all control registers are set to their default values and functional units are idle. Exiting a full system reset starts with the core being ready to boot.

The reset control unit (RCU) controls how all the functional units enter and exit reset. Differences in functional requirements and clocking constraints define how reset signals are generated. Programs must guarantee that none of the reset functions puts the system into an undefined state or causes resources to stall. This is particularly important when the core is reset (programs must ensure that there is no pending system activity involving the core when it is being reset).

From a system perspective, reset is defined by both the reset target and the reset source described as follows in the following list.

Target defined:

- Hardware Reset—All functional units are set to their default states without exception. History is lost.

- System Reset—All functional units except the RCU are set to their default states.

- Core-only Reset—Affects the core only. The system software should guarantee that the core, while in reset state, is not accessed by any bus master.

Source defined:

- Hardware Reset—The <u>SYS\_HWRST</u> input signal is asserted active (pulled down).

- System Reset—May be triggered by software (writing to the RCU\_CTL register) or by another functional unit such as the dynamic power management (DPM) unit (hibernate) or any of the system event controller (SEC), trigger routing unit (TRU), or emulator inputs.

- Core-only Reset—Triggered by software.

- Trigger request (peripheral).

## Voltage Regulation

The processor requires an external voltage regulator to power the VDD\_INT pins. To reduce standby power consumption, the external voltage regulator can be signaled through SYS\_EXTWAKE to remove power from the processor core. This signal is high-true for power-up and may be connected directly to the low-true shut-down input of many common regulators.

While in the hibernate state, all external supply pins (VDD\_ EXT, VDD\_USB, and VDD\_DMC) can still be powered, eliminating the need for external buffers. The external voltage regulator can be activated from this power down state by asserting the SYS\_HWRST pin, which then initiates a boot sequence. SYS\_EXTWAKE indicates a wake-up to the external voltage regulator.

## SYSTEM DEBUG

The processor includes various features that allow for easy system debug. These are described in the following sections.

## System Watchpoint Unit

The system watchpoint unit (SWU) is a single module which connects to a single system bus and provides for transaction monitoring. One SWU is attached to the bus going to each system slave. The SWU provides ports for all system bus address channel signals. Each SWU contains four match groups of registers with associated hardware. These four SWU match groups operate independently, but share common event (interrupt, trigger, and others) outputs.

## **Debug Access Port**

The debug access port (DAP) provides IEEE-1149.1 JTAG interface support through its JTAG debug and serial wire debug port (SWJ-DP). SWJ-DP is a combined JTAG-DP and SW-DP that enables either serial wire debug (SWD) or a JTAG emulator to be connected to a target. SWD signals share the same pins as

JTAG. The DAP provides an optional instrumentation trace for both the core and system. It provides a trace stream that conforms to MIPI System Trace Protocol version 2 (STPv2).

## **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (CrossCore<sup>®</sup> Embedded Studio), evaluation products, emulators, and a wide variety of software add-ins.

## Integrated Development Environments (IDEs)

CrossCore Embedded Studio is based on the Eclipse<sup>™</sup> framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information, visit www.analog.com/cces.

## EZ-KIT Lite Evaluation Board

For processor evaluation, Analog Devices provides a wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information, visit www.analog.com and search on "ezkit" or "ezextender".

## **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE, a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

## ADSP-BF706 EZ-KIT Mini

The ADSP-BF706 EZ-KIT Mini<sup>™</sup> product (ADZS-BF706-EZMini) contains the ADSP-BF706 processor and is shipped with all of the necessary hardware. Users can start their evaluation immediately. The EZ-KIT Mini product includes the standalone evaluation board and USB cable. The EZ-KIT Mini ships with an on-board debug agent.

The evaluation board is designed to be used in conjunction with the CrossCore Embedded Studio (CCES) development tools to test capabilities of the ADSP-BF706 Blackfin processor.

| Port Name  | Direction | Description                                                                                                                                                                                                                                                                                               |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HADC_VREFN | Input     | <b>Ground Reference for ADC.</b> Connect to an external voltage reference that meets data sheet specifications.                                                                                                                                                                                           |

| HADC_VREFP | Input     | <b>External Reference for ADC.</b> Connect to an external voltage reference that meets data sheet specifications.                                                                                                                                                                                         |

| MSI_CD     | Input     | Card Detect. Connects to a pull-up resistor and to the card detect output of an SD socket.                                                                                                                                                                                                                |

| MSI_CLK    | Output    | <b>Clock.</b> The clock signal applied to the connected device from the MSI.                                                                                                                                                                                                                              |

| MSI_CMD    | I/O       | <b>Command.</b> Used to send commands to and receive responses from the connected device.                                                                                                                                                                                                                 |

| MSI_Dn     | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                                                           |

| MSI_INT    | Input     | <b>eSDIO Interrupt Input.</b> Used only for eSDIO. Connects to an eSDIO card's interrupt output. An interrupt may be sampled even when the MSI clock to the card is switched off.                                                                                                                         |

| Px_nn      | I/O       | <b>Position n.</b> General purpose input/output. See the GP Ports chapter of the HRM for programming information.                                                                                                                                                                                         |

| RTC_CLKIN  | Input     | Crystal input/external oscillator connection. Connect to an external clock source or crystal.                                                                                                                                                                                                             |

| RTC_XTAL   | Output    | <b>Crystal output.</b> Drives an external crystal. Must be left unconnected if an external clock is driving RTC_CLKIN.                                                                                                                                                                                    |

| SMC_ABEn   | Output    | <b>Byte Enable n.</b> Indicate whether the lower or upper byte of a memory is being accessed. When an asynchronous write is made to the upper byte of a 16-bit memory, SMC_ABE1b=0 and SMC_ABE0b=1. When an asynchronous write is made to the lower byte of a 16-bit memory, SMC_ABE1b=1 and SMC_ABE0b=0. |

| SMC_AMSn   | Output    | Memory Select n. Typically connects to the chip select of a memory device.                                                                                                                                                                                                                                |

| SMC_AOE    | Output    | Output Enable. Asserts at the beginning of the setup period of a read access.                                                                                                                                                                                                                             |

| SMC_ARDY   | Input     | <b>Asynchronous Ready.</b> Flow control signal used by memory devices to indicate to the SMC when further transactions may proceed.                                                                                                                                                                       |

| SMC_ARE    | Output    | Read Enable. Asserts at the beginning of a read access.                                                                                                                                                                                                                                                   |

| SMC_AWE    | Output    | Write Enable. Asserts for the duration of a write access period.                                                                                                                                                                                                                                          |

| SMC_Ann    | Output    | Address n. Address bus.                                                                                                                                                                                                                                                                                   |

| SMC_Dnn    | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                                                           |

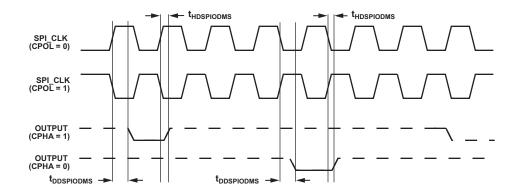

| SPI_CLK    | I/O       | Clock. Input in slave mode, output in master mode.                                                                                                                                                                                                                                                        |

| SPI_D2     | I/O       | Data 2. Used to transfer serial data in Quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                                                                   |

| SPI_D3     | I/O       | Data 3. Used to transfer serial data in Quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                                                                   |

| SPI_MISO   | I/O       | <b>Master In, Slave Out.</b> Used to transfer serial data. Operates in the same direction as SPI_MOSI in Dual and Quad modes. Open-drain when ODM mode is enabled.                                                                                                                                        |

| SPI_MOSI   | I/O       | <b>Master Out, Slave In.</b> Used to transfer serial data. Operates in the same direction as SPI_MISO in Dual and Quad modes. Open-drain when ODM mode is enabled.                                                                                                                                        |

| SPI_RDY    | I/O       | Ready. Optional flow signal. Output in slave mode, input in master mode.                                                                                                                                                                                                                                  |

| SPI_SELn   | Output    | Slave Select Output n. Used in Master mode to enable the desired slave.                                                                                                                                                                                                                                   |

| SPI_SS     | Input     | <b>Slave Select Input.</b> Slave mode - Acts as the slave select input. Master mode- Optionally serves as an error detection input for the SPI when there are multiple masters.                                                                                                                           |

| SPT_ACLK   | I/O       | <b>Channel A Clock.</b> Data and Frame Sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                                                                  |

| SPT_AD0    | I/O       | <b>Channel A Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                       |

| SPT_AD1    | I/O       | <b>Channel A Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                     |

| SPT_AFS    | I/O       | <b>Channel A Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                                                                                                                            |

| SPT_ATDV   | Output    | <b>Channel A Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                                                                |

## Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

## **184-BALL CSP\_BGA SIGNAL DESCRIPTIONS**

The processor's pin definitions are shown in Table 7. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

## Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

| Signal Name | Description                 | Port      | Pin Name  |

|-------------|-----------------------------|-----------|-----------|

| CAN0_RX     | CAN0 Receive                | С         | PC_02     |

| CAN0_TX     | CAN0 Transmit               | С         | PC_03     |

| CAN1_RX     | CAN1 Receive                | A         | PA_12     |

| CAN1_TX     | CAN1 Transmit               | A         | PA_13     |

| CNT0_DG     | CNT0 Count Down and Gate    | A         | PA_07     |

| CNT0_UD     | CNT0 Count Up and Direction | A         | PA_15     |

| CNT0_ZM     | CNT0 Count Zero Marker      | A         | PA_13     |

| DMC0_A00    | DMC0 Address 0              | Not Muxed | DMC0_A00  |

| DMC0_A01    | DMC0 Address 1              | Not Muxed | DMC0_A01  |

| DMC0_A02    | DMC0 Address 2              | Not Muxed | DMC0_A02  |

| DMC0_A03    | DMC0 Address 3              | Not Muxed | DMC0_A03  |

| DMC0_A04    | DMC0 Address 4              | Not Muxed | DMC0_A04  |

| DMC0_A05    | DMC0 Address 5              | Not Muxed | DMC0_A05  |

| DMC0_A06    | DMC0 Address 6              | Not Muxed | DMC0_A06  |

| DMC0_A07    | DMC0 Address 7              | Not Muxed | DMC0_A07  |

| DMC0_A08    | DMC0 Address 8              | Not Muxed | DMC0_A08  |

| DMC0_A09    | DMC0 Address 9              | Not Muxed | DMC0_A09  |

| DMC0_A10    | DMC0 Address 10             | Not Muxed | DMC0_A10  |

| DMC0_A11    | DMC0 Address 11             | Not Muxed | DMC0_A11  |

| DMC0_A12    | DMC0 Address 12             | Not Muxed | DMC0_A12  |

| DMC0_A13    | DMC0 Address 13             | Not Muxed | DMC0_A13  |

| DMC0_BA0    | DMC0 Bank Address Input 0   | Not Muxed | DMC0_BA0  |

| DMC0_BA1    | DMC0 Bank Address Input 1   | Not Muxed | DMC0_BA1  |

| DMC0_BA2    | DMC0 Bank Address Input 2   | Not Muxed | DMC0_BA2  |

| DMC0_CAS    | DMC0 Column Address Strobe  | Not Muxed | DMC0_CAS  |

| DMC0_CK     | DMC0 Clock                  | Not Muxed | DMC0_CK   |

| DMC0_CKE    | DMC0 Clock enable           | Not Muxed | DMC0_CKE  |

| DMC0_CK     | DMC0 Clock (complement)     | Not Muxed | DMC0_CK   |

| DMC0_CS0    | DMC0 Chip Select 0          | Not Muxed | DMC0_CS0  |

| DMC0_DQ00   | DMC0 Data 0                 | Not Muxed | DMC0_DQ00 |

| DMC0_DQ01   | DMC0 Data 1                 | Not Muxed | DMC0_DQ01 |

| DMC0_DQ02   | DMC0 Data 2                 | Not Muxed | DMC0_DQ02 |

| DMC0_DQ03   | DMC0 Data 3                 | Not Muxed | DMC0_DQ03 |

| DMC0_DQ04   | DMC0 Data 4                 | Not Muxed | DMC0_DQ04 |

| DMC0_DQ05   | DMC0 Data 5                 | Not Muxed | DMC0_DQ05 |

| DMC0_DQ06   | DMC0 Data 6                 | Not Muxed | DMC0_DQ06 |

## Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name  | Description                                       | Port      | Pin Name    |

|--------------|---------------------------------------------------|-----------|-------------|

| MSIO_INT     | MSI0 eSDIO Interrupt Input                        | C         | PC_14       |

| PA_00-PA_15  | Position 00 through Position 15                   | A         | PA_00-PA_15 |

| PB_00-PB_15  | Position 00 through Position 15                   | В         | PB_00-PB_15 |

| PC_00-PC_14  | Position 00 through Position 14                   | с         | PC_00-PC_14 |

| PPI0_CLK     | EPPI0 Clock                                       | А         | PA_14       |

| PPI0_D00     | EPPIO Data 0                                      | В         | PB_07       |

| PPI0_D01     | EPPIO Data 1                                      | В         | PB_06       |

| PPI0_D02     | EPPIO Data 2                                      | В         | PB_05       |

| PPI0_D03     | EPPIO Data 3                                      | В         | PB_04       |

| PPI0_D04     | EPPIO Data 4                                      | В         | PB_03       |

| PPI0_D05     | EPPIO Data 5                                      | В         | PB_02       |

| PPI0_D06     | EPPIO Data 6                                      | В         | PB_01       |

| PPI0_D07     | EPPIO Data 7                                      | В         | PB_00       |

| PPI0_D08     | EPPIO Data 8                                      | A         | PA_11       |

| <br>PPI0_D09 | EPPI0 Data 9                                      | A         | <br>PA_10   |

| PPI0_D10     | EPPIO Data 10                                     | A         | PA_09       |

| PPI0_D11     | EPPIO Data 11                                     | А         | PA_08       |

| PPI0_D12     | EPPIO Data 12                                     | с         | PC_03       |

| PPI0_D13     | EPPIO Data 13                                     | с         | PC_02       |

| PPI0_D14     | EPPIO Data 14                                     | С         | PC_01       |

| PPI0_D15     | EPPIO Data 15                                     | с         | PC_00       |

| PPI0_D16     | EPPIO Data 16                                     | В         | PB_08       |

| PPI0_D17     | EPPIO Data 17                                     | В         | PB_09       |

| PPI0_FS1     | EPPI0 Frame Sync 1 (HSYNC)                        | А         | PA_12       |

| PPI0_FS2     | EPPI0 Frame Sync 2 (VSYNC)                        | A         | PA_13       |

| PPI0_FS3     | EPPI0 Frame Sync 3 (FIELD)                        | A         | PA_15       |

| RTC0_CLKIN   | RTC0 Crystal input/external oscillator connection | Not Muxed | RTC0_CLKIN  |

| RTC0_XTAL    | RTC0 Crystal output                               | Not Muxed | RTC0_XTAL   |

| SMC0_A01     | SMC0 Address 1                                    | А         | PA_08       |

| 5MC0_A02     | SMC0 Address 2                                    | А         | PA_09       |

|              | SMC0 Address 3                                    | А         | <br>PA_10   |

|              | SMC0 Address 4                                    | A         | <br>PA_11   |

| SMC0_A05     | SMC0 Address 5                                    | А         | PA_07       |

|              | SMC0 Address 6                                    | А         | <br>PA_06   |

|              | SMC0 Address 7                                    | А         | <br>PA_05   |

|              | SMC0 Address 8                                    | А         | <br>PA_04   |

| SMC0_A09     | SMC0 Address 9                                    | С         | PC_01       |

| 5MC0_A10     | SMC0 Address 10                                   | C         | PC_02       |

| 5MC0_A11     | SMC0 Address 11                                   | C         | PC_03       |

| 5MC0_A12     | SMC0 Address 12                                   | C         | PC_04       |

| SMC0_ABE0    | SMC0 Byte Enable 0                                | A         | PA_00       |

| SMC0_ABE1    | SMC0 Byte Enable 1                                | A         | PA_01       |

| SMC0_AMS0    | SMC0 Memory Select 0                              | A         | PA_15       |

| SMC0_AMS1    | SMC0 Memory Select 1                              | A         | PA_02       |

| SMC0_AOE     | SMC0 Output Enable                                | A         | PA_12       |

| SMC0_ARDY    | SMC0 Asynchronous Ready                           | A         | PA_03       |

| Signal Name  | Description                      | Port      | Pin Name       |

|--------------|----------------------------------|-----------|----------------|

| SYS_FAULT    | Active-Low Fault Output          | Not Muxed | SYS_FAULT      |

| SYS_HWRST    | Processor Hardware Reset Control | Not Muxed | SYS_HWRST      |

| SYS_NMI      | Nonmaskable Interrupt            | Not Muxed | SYS_NMI        |

| SYS_RESOUT   | Reset Output                     | Not Muxed | SYS_RESOUT     |

| SYS_WAKE0    | Power Saving Mode Wake-up 0      | В         | PB_07          |

| SYS_WAKE1    | Power Saving Mode Wake-up 1      | В         | PB_08          |

| SYS_WAKE2    | Power Saving Mode Wake-up 2      | В         | PB_12          |

| SYS_WAKE3    | Power Saving Mode Wake-up 3      | с         | PC_02          |

| SYS_WAKE4    | Power Saving Mode Wake-up 4      | А         | PA_12          |

| SYS_XTAL     | Crystal Output                   | Not Muxed | SYS_XTAL       |

|              | TIMER0 Alternate Capture Input 0 | с         | PC_03          |

| <br>FM0_ACI1 | TIMER0 Alternate Capture Input 1 | В         | <br>PB_01      |

| M0_ACI2      | TIMER0 Alternate Capture Input 2 | C         | PC_07          |

| FM0_ACI3     | TIMERO Alternate Capture Input 3 | В         | PB_09          |

| TM0_ACI4     | TIMERO Alternate Capture Input 4 | C         | PC_01          |

| FM0_ACI5     | TIMERO Alternate Capture Input 5 | c         | PC_02          |

| FM0_ACI6     | TIMERO Alternate Capture Input 6 | A         | PA_12          |

| FM0_ACLK0    | TIMERO Alternate Clock 0         | c         | PC_04          |

| TM0_ACLK1    | TIMERO Alternate Clock 1         | c         | PC_10          |

| TM0_ACLK2    | TIMERO Alternate Clock 2         | c         | PC_09          |

| TM0_ACLK3    | TIMERO Alternate Clock 3         | В         | PB_00          |

| FM0_ACLK4    | TIMERO Alternate Clock 4         | В         | PB_10          |

| TM0_ACLK5    | TIMERO Alternate Clock 5         | A         | PA_14          |

| TM0_ACLK6    | TIMERO Alternate Clock 6         | В         | PB_04          |

| TM0_CLK      | TIMERO Clock                     | В         | PB_06          |

| TM0_TMR0     | TIMERO Timer 0                   | A         | PA_05          |

| TM0_TMR1     | TIMERO Timer 1                   | A         | PA_06          |

| TM0_TMR2     | TIMERO Timer 2                   | A         | PA_07          |

| TM0_TMR2     | TIMERO Timer 3                   | c         | PC_05          |

| TM0_TMR4     | TIMERO Timer 4                   | A         | PA_09          |

| TM0_TMR5     | TIMERO Timer 5                   | A         | PA_10          |

| TM0_TMR6     | TIMERO Timer 6                   | A         | PA_11          |

| TMO_TMR7     | TIMERO Timer 7                   | A         | PA_04          |

| TRACE0_CLK   | TPIU0 Trace Clock                | В         | PB_10          |

| TRACE0_CER   | TPIU0 Trace Data 0               | В         | PB_15          |

| TRACE0_D00   | TPIU0 Trace Data 1               | В         | PB_14          |

| TRACE0_D01   | TPIU0 Trace Data 2               | В         | PB_14<br>PB_13 |

| TRACE0_D02   | TPIU0 Trace Data 3               | В         | PB_12          |

|              |                                  |           |                |

| TRACE0_D04   | TPIU0 Trace Data 4               | В         | PB_11          |

| TRACEO_DOS   | TPIU0 Trace Data 5               | A         | PA_02          |

| TRACE0_D06   | TPIU0 Trace Data 6               | A         | PA_01          |

| TRACE0_D07   | TPIU0 Trace Data 7               | A         | PA_00          |

| TWI0_SCL     | TWI0 Serial Clock                | Not Muxed | TWI0_SCL       |

| TWIO_SDA     | TWI0 Serial Data                 | Not Muxed | TWI0_SDA       |

| JARTO_CTS    | UARTO Clear to Send              | C         | PC_03          |

| JARTO_RTS    | UARTO Request to Send            | C         | PC_02          |

## Table 7. ADSP-BF70x 184-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name  | Description              | Port      | Pin Name   |

|--------------|--------------------------|-----------|------------|

| TM0_ACLK1    | TIMER0 Alternate Clock 1 | С         | PC_10      |

| TM0_ACLK2    | TIMER0 Alternate Clock 2 | С         | PC_09      |

| TM0_ACLK3    | TIMER0 Alternate Clock 3 | В         | PB_00      |

| TM0_ACLK4    | TIMER0 Alternate Clock 4 | В         | PB_10      |

| TM0_ACLK5    | TIMER0 Alternate Clock 5 | А         | PA_14      |

| TM0_ACLK6    | TIMER0 Alternate Clock 6 | В         | PB_04      |

| TM0_CLK      | TIMER0 Clock             | В         | <br>PB_06  |

| TM0_TMR0     | TIMER0 Timer 0           | А         | <br>PA_05  |

| <br>TM0_TMR1 | TIMER0 Timer 1           | А         | _<br>PA_06 |

| TM0_TMR2     | TIMER0 Timer 2           | А         | PA_07      |

| TM0_TMR3     | TIMERO Timer 3           | C         | PC_05      |

| TM0_TMR4     | TIMER0 Timer 4           | A         | PA_09      |

| TM0_TMR5     | TIMERO Timer 5           | A         | PA_10      |

| TM0_TMR6     | TIMERO Timer 6           | A         | PA_11      |

| TM0_TMR7     | TIMERO Timer 7           | A         | PA_04      |

| TRACE0_CLK   | TPIU0 Trace Clock        | В         | PB_10      |

| TRACE0_CER   | TPIU0 Trace Data 0       | В         | PB_15      |

| TRACE0_D00   | TPIU0 Trace Data 1       | В         | PB_14      |

| TRACE0_D01   | TPIU0 Trace Data 2       | В         | PB_13      |

|              | TPIU0 Trace Data 3       | В         |            |

| TRACE0_D03   |                          |           | PB_12      |

| TRACE0_D04   | TPIU0 Trace Data 4       | В         | PB_11      |

| TRACE0_D05   | TPIU0 Trace Data 5       | A         | PA_02      |

| TRACE0_D06   | TPIU0 Trace Data 6       | A         | PA_01      |

| TRACE0_D07   | TPIU0 Trace Data 7       | A         | PA_00      |

| TWI0_SCL     | TWI0 Serial Clock        | Not Muxed | TWI0_SCL   |

| TWI0_SDA     | TWI0 Serial Data         | Not Muxed | TWI0_SDA   |

| UARTO_CTS    | UARTO Clear to Send      | С         | PC_03      |

| UARTO_RTS    | UARTO Request to Send    | C         | PC_02      |

| UARTO_RX     | UARTO Receive            | В         | PB_09      |

| UARTO_TX     | UARTO Transmit           | В         | PB_08      |

| UART1_CTS    | UART1 Clear to Send      | В         | PB_14      |

| UART1_RTS    | UART1 Request to Send    | В         | PB_13      |

| UART1_RX     | UART1 Receive            | С         | PC_01      |

| UART1_TX     | UART1 Transmit           | С         | PC_00      |

| USB0_CLKIN   | USB0 Clock/Crystal Input | Not Muxed | USB0_CLKIN |

| USB0_DM      | USB0 Data –              | Not Muxed | USB0_DM    |

| USB0_DP      | USB0 Data +              | Not Muxed | USB0_DP    |

| USB0_ID      | USB0 OTG ID              | Not Muxed | USB0_ID    |

| USB0_VBC     | USB0 VBUS Control        | Not Muxed | USB0_VBC   |

| USB0_VBUS    | USB0 Bus Voltage         | Not Muxed | USB0_VBUS  |

| USB0_XTAL    | USB0 Crystal             | Not Muxed | USB0_XTAL  |

| VDD_EXT      | External VDD             | Not Muxed | VDD_EXT    |

| VDD_INT      | Internal VDD             | Not Muxed | VDD_INT    |

| VDD_OTP      | VDD for OTP              | Not Muxed | VDD_OTP    |

| VDD_RTC      | VDD for RTC              | Not Muxed | VDD_RTC    |

| VDD_USB      | VDD for USB              | Not Muxed | VDD_USB    |

## Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

|             |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                                                                                                                                                                                                                                                                               |

|-------------|------|--------|------|-------|-------|-------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Туре   | Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                                                                                                                                                                                                                                                                 |

| PB_12       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Master Out, Slave In   TRACE0<br>Trace Data 3   SMC0 Data 12   SYS Power<br>Saving Mode Wakeup 2                                                                                                                                                                                                                                               |

|             |      |        |      |       |       |       |       |         | Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down.                                                                                                                                                          |

| PB_13       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 2   UART1 Request to<br>Send   TRACE0 Trace Data 2   SMC0 Data<br>13<br>Notes: No notes.                                                                                                                                                                                                                                                  |

| PB_14       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 3   UART1 Clear to Send<br>  TRACE0 Trace Data 1   SMC0 Data 14<br>Notes: No notes.                                                                                                                                                                                                                                                       |

| PB_15       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Slave Select Output 1  <br>TRACE0 Trace Data 0   SMC0 Data 15  <br>SPI2 Slave Select Input<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                  |

| PC_00       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Transmit   SPT0 Channel A<br>Data 1   PPI0 Data 15<br>Notes: No notes.                                                                                                                                                                                                                                                                        |

| PC_01       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Receive   SPT0 Channel B<br>Data 1   PPI0 Data 14   SMC0 Address 9  <br>TM0 Alternate Capture Input 4<br>Notes: No notes.                                                                                                                                                                                                                     |

| PC_02       | Ι/Ο  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART0 Request to Send   CAN0<br>Receive   PPI0 Data 13   SMC0 Address<br>10   SYS Power Saving Mode Wakeup 3  <br>TM0 Alternate Capture Input 5<br>Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down. |

| PC_03       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Clear to Send   CANO<br>Transmit   PPIO Data 12   SMCO Address<br>11   TMO Alternate Capture Input 0<br>Notes: No notes.                                                                                                                                                                                                                      |

| PC_04       | Ι/Ο  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPT0 Channel B Clock   SPI0 Clock<br>  MSI0 Data 1   SMC0 Address 12   TM0<br>Alternate Clock 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                    |

## Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| Parameter                                  |                                                             | <b>Test Conditions/Comments</b>                                                                                                                                                                                                                              | Min | Тур | Мах | Uni |

|--------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| I <sub>OZH_TWI</sub> <sup>14</sup>         | Three-State Leakage Current                                 | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V}, V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 5.5 \text{ V}$                                                                                                                                            |     |     | 10  | μΑ  |

| ADSP-BF701/                                | 703/705/707 Input Capacitance                               |                                                                                                                                                                                                                                                              |     |     |     |     |

| C <sub>IN</sub> (GPIO) <sup>15</sup>       | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 5.2 | 6.0 | pF  |

| C <sub>IN_TWI</sub> <sup>14</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.9 | 7.4 | pF  |

| C <sub>IN_DDR</sub> <sup>16</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.1 | 6.9 | pF  |

| ADSP-BF700/                                | 702/704/706 Input Capacitance                               | 1                                                                                                                                                                                                                                                            |     |     |     |     |

| C <sub>IN</sub> (GPIO) <sup>15</sup>       | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 5.0 | 5.3 | pF  |

| C <sub>IN_TWI</sub> <sup>14</sup>          | Input Capacitance                                           | $T_{AMBIENT} = 25^{\circ}C$                                                                                                                                                                                                                                  |     | 6.8 | 7.4 | pF  |

| I <sub>DD_DEEPSLEEP</sub> <sup>17, 1</sup> | <sup>8</sup> V <sub>DD_INT</sub> Current in Deep Sleep Mode | Clocks disabled<br>T <sub>1</sub> = 25°C                                                                                                                                                                                                                     |     | 1.4 |     | mA  |

| I <sub>DD_IDLE</sub> <sup>18</sup>         | V <sub>DD_INT</sub> Current in Idle                         | $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 100 \text{ MHz}$ $ASF = 0.05 \text{ (idle)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_1 = 25^{\circ}C$                                   |     | 13  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 800 \text{ MHz}$ $f_{CCLK} = 400 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$                                             |     | 90  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $T_{J} = 25^{\circ}C$ $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 300 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_{J} = 25^{\circ}C$ |     | 66  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 400 \text{ MHz}$ $f_{CCLK} = 200 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_J = 25^{\circ}C$                         |     | 49  |     | mA  |

| I <sub>DD_TYP</sub> <sup>18</sup>          | V <sub>DD_INT</sub> Current                                 | $f_{PLLCLK} = 300 \text{ MHz}$ $f_{CCLK} = 100 \text{ MHz}$ $ASF = 1.0 \text{ (full-on typical)}$ $f_{SYSCLK} = f_{SCLK0} = 25 \text{ MHz}$ $USBCLK = DCLK = OUTCLK =$ $SCLK1 = DISABLED$ $Peripherals disabled$ $T_J = 25^{\circ}C$                         |     | 30  |     | mA  |

| Parameter                                   |                                                     | Test Conditions/Comments                                                                                                                                                                                                          | Min | Тур | Max                                                     | Unit |

|---------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------|------|

| I <sub>DD_HIBERNATE</sub> <sup>17, 15</sup> | <sup>9</sup> Hibernate State Current                |                                                                                                                                                                                                                                   |     | 33  |                                                         | μΑ   |

| I <sub>DD_HIBERNATE</sub> <sup>17, 15</sup> | <sup>9</sup> Hibernate State Current<br>Without USB | $V_{DD_{INT}} = 0 V,$ $V_{DD_{DMC}} = 1.8 V,$ $V_{DD_{EXT}} = V_{DD_{HADC}} = V_{DD_{OTP}} =$ $V_{DD_{RTC}} = V_{DD_{USB}} = 3.3 V,$ $T_{J} = 25^{\circ}C,$ $f_{CLKIN} = 0,$ $USB protection disabled$ $(USB_{PHY_{CTLDIS}} = 1)$ |     | 15  |                                                         | μΑ   |

| I <sub>DD_INT</sub> <sup>18</sup>           | V <sub>DD_INT</sub> Current                         | V <sub>DD_INT</sub> within operating conditions table specifications                                                                                                                                                              |     |     | See I <sub>DDINT_TOT</sub><br>equation on<br>on Page 56 |      |

| I <sub>DD_RTC</sub>                         | I <sub>DD_RTC</sub> Current                         | $V_{DD_{RTC}} = 3.3 \text{ V}, \text{ T}_{J} = 125^{\circ}\text{C}$                                                                                                                                                               |     |     | 10                                                      | μA   |

<sup>1</sup> Applies to all output and bidirectional signals except DMC0 signals, TWI signals, and USB0 signals.

<sup>2</sup> Applies to DMC0\_Axx, DMC0\_CAS, DMC0\_CKE, DMC0\_CK, DMC0\_CK, DMC0\_CS, DMC0\_DQxx, DMC0\_LDM, DMC0\_LDQS, DMC0\_LDQS,

DMC0\_ODT, DMC0\_RAS, DMC0\_UDM, DMC0\_UDQS, DMC0\_UDQS, and DMC0\_WE signals.

<sup>3</sup> Applies to all output and bidirectional signals except DMC0 signals and USB0 signals.

<sup>4</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TDI, and JTG\_TMS\_SWDIO signals.

<sup>5</sup> Applies to DMC0\_VREF signal.

<sup>6</sup> Applies to JTG\_TCK\_SWCLK and JTG\_TRST signals.

<sup>7</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TCK, and <u>JTG\_TRST</u> signals.

<sup>8</sup> Applies to JTG\_TDI, JTG\_TMS\_SWDIO, PA\_xx, PB\_xx, and PC\_xx signals when internal GPIO pull-ups are enabled. For information on when internal pull-ups are enabled for GPIOs. See ADSP-BF70x Designer Quick Reference on Page 38.

<sup>9</sup> Applies to USB0\_CLKIN signal.

<sup>10</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_AMS0</u>, <u>SMC0\_ARE</u>, <u>SMC0\_AWE</u>, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, JTG\_TDO\_SWO, USB0\_DM, USB0\_DP, USB0\_ID, and USB0\_VBC signals.

<sup>11</sup> Applies to DMC0\_Axx, DMC0\_BAxx, DMC0\_CAS, DMC0\_CS0, DMC0\_DQxx, DMC0\_LDQS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_UDQS, DMC0\_LDM, DMC0\_UDM, DMC0\_ODT, DMC0\_RAS, and DMC0\_WE signals.

<sup>12</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, <u>JTG\_TDO\_SWO</u>, <u>USB0\_DP</u>, <u>USB0\_ID</u>, <u>USB0\_ID</u>, <u>USB0\_VBC</u>, <u>U</u>

<sup>13</sup>Applies to USB0\_VBUS signals.

<sup>14</sup>Applies to all TWI signals.

<sup>15</sup>Applies to all signals, except DMC0 and TWI signals.

<sup>16</sup>Applies to all DMC0 signals.

<sup>17</sup>See the ADSP-BF70x Blackfin+ Processor Hardware Reference for definition of deep sleep and hibernate operating modes.

<sup>18</sup>Additional information can be found at Total Internal Power Dissipation.

<sup>19</sup>Applies to VDD\_EXT, VDD\_DMC, and VDD\_USB supply signals only. Clock inputs are tied high or low.

| Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |       |       |

|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| (°C) رT                        | 1.045 | 1.050 | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| -40                            | 0.6   | 0.6   | 0.7   | 0.7   | 0.7   | 0.8   | 0.8   | 0.8   | 0.9   | 0.9   | 0.9   | 1.0   | 1.0   |

| -20                            | 1.1   | 1.1   | 1.2   | 1.2   | 1.2   | 1.3   | 1.4   | 1.4   | 1.5   | 1.5   | 1.6   | 1.7   | 1.7   |

| 0                              | 2.0   | 2.0   | 2.1   | 2.2   | 2.3   | 2.4   | 2.5   | 2.5   | 2.6   | 2.7   | 2.8   | 3.0   | 3.0   |

| 25                             | 4.3   | 4.3   | 4.5   | 4.7   | 4.8   | 5.0   | 5.2   | 5.3   | 5.5   | 5.7   | 5.9   | 6.1   | 6.2   |

| 40                             | 6.7   | 6.8   | 7.0   | 7.3   | 7.5   | 7.8   | 8.0   | 8.3   | 8.6   | 8.8   | 9.1   | 9.4   | 9.6   |

| 55                             | 10.3  | 10.5  | 10.8  | 11.2  | 11.5  | 11.9  | 12.3  | 12.6  | 13.0  | 13.4  | 13.9  | 14.3  | 14.5  |

| 70                             | 15.7  | 15.9  | 16.4  | 16.8  | 17.4  | 17.9  | 18.4  | 18.9  | 19.5  | 20.1  | 20.7  | 21.3  | 21.6  |

| 85                             | 23.3  | 23.6  | 24.3  | 25.0  | 25.7  | 26.4  | 27.2  | 27.9  | 28.7  | 29.5  | 30.4  | 31.2  | 31.7  |

| 100                            | 34.2  | 34.6  | 35.5  | 36.5  | 37.5  | 38.5  | 39.5  | 40.6  | 41.7  | 42.8  | 43.9  | 45.1  | 45.7  |

| 105                            | 38.7  | 39.2  | 40.2  | 41.3  | 42.4  | 43.5  | 44.6  | 45.8  | 47.0  | 48.2  | 49.5  | 50.8  | 51.5  |

| 115                            | 48.9  | 49.5  | 50.7  | 52.0  | 53.4  | 54.7  | 56.0  | 57.5  | 59.0  | 60.5  | 62.0  | 63.6  | 64.4  |

| 125                            | 61.5  | 62.1  | 63.6  | 65.1  | 66.7  | 68.3  | 69.9  | 71.7  | 73.4  | 75.2  | 77.0  | 79.0  | 79.9  |

## Table 21. Static Current—IDD\_DEEPSLEEP (mA)

## Table 22. Activity Scaling Factors (ASF)

| I <sub>DDINT</sub> Power Vector | ASF  |

|---------------------------------|------|

| I <sub>DD-IDLE1</sub>           | 0.05 |

| I <sub>DD-IDLE2</sub>           | 0.05 |

| I <sub>DD-NOP1</sub>            | 0.56 |

| I <sub>DD-NOP2</sub>            | 0.59 |

| I <sub>DD-APP3</sub>            | 0.78 |

| I <sub>DD-APP1</sub>            | 0.79 |

| I <sub>DD-APP2</sub>            | 0.83 |

| I <sub>DD-TYP1</sub>            | 1.00 |

| I <sub>DD-TYP3</sub>            | 1.01 |

| I <sub>DD-TYP2</sub>            | 1.03 |

| I <sub>DD-HIGH1</sub>           | 1.39 |

| I <sub>DD-HIGH3</sub>           | 1.39 |

| I <sub>DD-HIGH2</sub>           | 1.54 |

| Table 23. | <b>CCLK Dynamic</b> | Current per core | (mA, with ASF = 1) |

|-----------|---------------------|------------------|--------------------|

|-----------|---------------------|------------------|--------------------|

|                         |       | Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |

|-------------------------|-------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| f <sub>CCLK</sub> (MHz) | 1.045 | 1.050                          | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| 400                     | 66.7  | 67.2                           | 67.9  | 68.7  | 69.4  | 70.2  | 71.1  | 71.8  | 72.6  | 73.4  | 74.2  | 74.9  | 75.4  |

| 350                     | 58.6  | 59.0                           | 59.6  | 60.3  | 61.0  | 61.7  | 62.4  | 63.0  | 63.7  | 64.4  | 65.1  | 65.8  | 66.1  |

| 300                     | 50.2  | 50.5                           | 51.1  | 51.7  | 52.3  | 52.9  | 53.5  | 54.1  | 54.7  | 55.3  | 55.9  | 56.4  | 56.8  |

| 250                     | 42.1  | 42.3                           | 42.8  | 43.3  | 43.8  | 44.3  | 44.7  | 45.3  | 45.8  | 46.3  | 46.8  | 47.4  | 47.6  |

| 200                     | 33.7  | 33.9                           | 34.3  | 34.7  | 35.1  | 35.5  | 35.9  | 36.3  | 36.7  | 37.1  | 37.5  | 37.9  | 38.0  |

| 150                     | 25.4  | 25.5                           | 25.8  | 26.1  | 26.4  | 26.7  | 27.0  | 27.3  | 27.6  | 27.9  | 28.2  | 28.5  | 28.8  |

| 100                     | 17.0  | 17.1                           | 17.3  | 17.5  | 17.7  | 17.9  | 18.1  | 18.3  | 18.5  | 18.6  | 18.8  | 19.0  | 19.1  |

## Asynchronous Page Mode Read

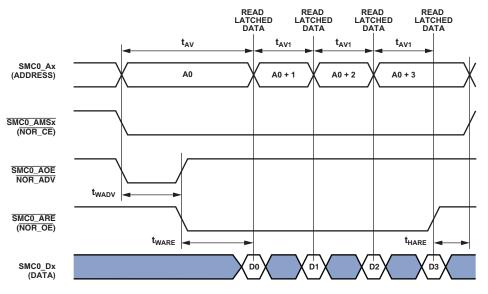

Table 34 and Figure 13 show asynchronous memory page mode read timing, related to the static memory controller (SMC).

### Table 34. Asynchronous Page Mode Read

|                     |                                                                       | V <sub>DD_EXT</sub><br>1.8V /3.3V Nominal           |     |      |

|---------------------|-----------------------------------------------------------------------|-----------------------------------------------------|-----|------|

| Parame              | ter                                                                   | Min                                                 | Max | Unit |

| Switchin            | g Characteristics                                                     |                                                     |     |      |

| t <sub>AV</sub>     | SMC0_Ax (Address) Valid for First Address Min Width <sup>1</sup>      | $(PREST + RST + PREAT + RAT) \times t_{SCLK0} - 2$  |     | ns   |

| AV1                 | SMC0_Ax (Address) Valid for Subsequent SMC0_Ax<br>(Address) Min Width | $PGWS \times t_{SCLK0} - 2$                         |     | ns   |

| WADV                | SMC0_NORDV Active Low Width <sup>2</sup>                              | $RST \times t_{SCLK0} - 2$                          |     | ns   |

| HARE                | Output <sup>3</sup> Hold After SMC0_ARE High <sup>4</sup>             | $RHT \times t_{SCLK0} - 2$                          |     | ns   |

| t <sub>WARE</sub> 5 | SMC0_ARE Active Low Width <sup>6</sup>                                | $(RAT + (Nw - 1) \times PGWS) \times t_{SCLK0} - 2$ |     | ns   |

<sup>1</sup>PREST, RST, PREAT and RAT values set using the SMC\_BXETIM.PREST bits, SMC\_BXTIM.RST bits, SMC\_BXETIM.PREAT bits, and the SMC\_BXTIM.RAT bits.

<sup>2</sup> RST value set using the SMC\_BxTIM.RST bits.

<sup>3</sup>Output signals are SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_AOE</u>.

<sup>4</sup> RHT value set using the SMC\_BxTIM.RHT bits.

<sup>5</sup> SMC\_BxCTL.ARDYEN bit = 0.

$^6\,\rm RAT$  value set using the SMC\_BxTIM.RAT bits.

Figure 13. Asynchronous Page Mode Read

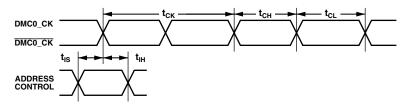

## DDR2 SDRAM Clock and Control Cycle Timing

Table 39 and Figure 17 show DDR2 SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

## Table 39. DDR2 SDRAM Read Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                 |                                                |      | 200 MHz |                 |

|-----------------|------------------------------------------------|------|---------|-----------------|

| Paramete        | r                                              | Min  | Мах     | Unit            |

| Switching       | Characteristics                                |      |         |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |         | ns              |

| t <sub>CH</sub> | High Clock Pulse Width                         | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>CL</sub> | Low Clock Pulse Width                          | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 350  |         | ps              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMC0_CK Rise  | 475  |         | ps              |

NOTE: CONTROL = DMC0\_CS0, DMC0\_CKE, DMC0\_RAS, DMC0\_CAS, AND DMC0\_WE. ADDRESS = DMC0\_A00-13, AND DMC0\_BA0-2.

Figure 17. DDR2 SDRAM Clock and Control Cycle Timing

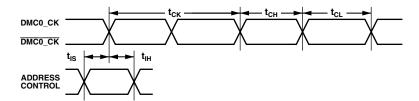

## Mobile DDR SDRAM Clock and Control Cycle Timing

Table 42 and Figure 20 show mobile DDR SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

### Table 42. Mobile DDR SDRAM Clock and Control Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                 |                                                |      | 200 MHz |                 |

|-----------------|------------------------------------------------|------|---------|-----------------|

| Paramete        | er                                             | Min  | Мах     | Unit            |

| Switching       | Characteristics                                |      |         |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |         | ns              |

| t <sub>CH</sub> | Minimum Clock Pulse Width                      | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>CL</sub> | Maximum Clock Pulse Width                      | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 1.5  |         | ns              |