Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 400MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 1MB                                                                                       |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 88-VFQFN Exposed Pad, CSP                                                                 |

| Supplier Device Package | 88-LFCSP-VQ (12x12)                                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf706kcpz-4                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **BLACKFIN+ PROCESSOR CORE**

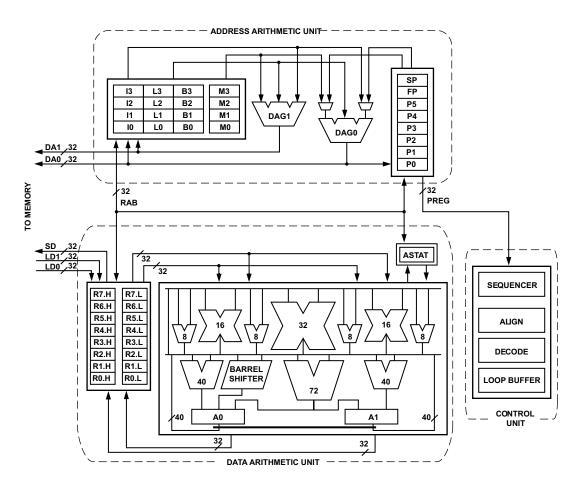

As shown in Figure 1, the processor integrates a Blackfin+ processor core. The core, shown in Figure 2, contains two 16-bit multipliers, one 32-bit multiplier, two 40-bit accumulators (which may be used together as a 72-bit accumulator), two 40-bit ALUs, one 72-bit ALU, four video ALUs, and a 40-bit shifter. The computation units process 8-, 16-, or 32-bit data from the register file.

The compute register file contains eight 32-bit registers. When performing compute operations on 16-bit operand data, the register file operates as 16 independent 16-bit registers. All operands for compute operations come from the multiported register file and instruction constant fields.

The core can perform two 16-bit by 16-bit multiply-accumulates or one 32-bit multiply-accumulate in each cycle. Signed and unsigned formats, rounding, saturation, and complex multiplies are supported. The ALUs perform a traditional set of arithmetic and logical operations on 16-bit or 32-bit data. In addition, many special instructions are included to accelerate various signal processing tasks. These include bit operations such as field extract and population count, divide primitives, saturation and rounding, and sign/exponent detection. The set of video instructions include byte alignment and packing operations, 16-bit and 8-bit adds with clipping, 8-bit average operations, and 8-bit subtract/absolute value/accumulate (SAA) operations. Also provided are the compare/select and vector search instructions.

For certain instructions, two 16-bit ALU operations can be performed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). If a second ALU is used, quad 16-bit operations are possible.

The 40-bit shifter can perform shifts and rotates and is used to support normalization, field extract, and field deposit instructions.

Figure 2. Blackfin+ Processor Core

system event or fault if enabled. ECC protection is fully transparent to the user, even if L2 memory is read or written by 8-bit or 16-bit entities.

## **CRC-Protected Memories**

While parity bit and ECC protection mainly protect against random soft errors in L1 and L2 memory cells, the CRC engines can be used to protect against systematic errors (pointer errors) and static content (instruction code) of L1, L2, and even L3 memories (DDR2, LPDDR). The processor features two CRC engines which are embedded in the memory-to-memory DMA controllers. CRC checksums can be calculated or compared on the fly during memory transfers, or one or multiple memory regions can be continuously scrubbed by a single DMA work unit as per DMA descriptor chain instructions. The CRC engine also protects data loaded during the boot process.

### **Memory Protection**

The Blackfin+ core features a memory protection concept, which grants data and/or instruction accesses to enabled memory regions only. A supervisor mode vs. user mode programming model supports dynamically varying access rights. Increased flexibility in memory page size options supports a simple method of static memory partitioning.

## System Protection

The system protection unit (SPU) guards against accidental or unwanted access to the MMR space of a peripheral by providing a write-protection mechanism. The user is able to choose and configure the peripherals that are protected as well as configure which ones of the four system MMR masters (core, memory DMA, the SPI host port, and Coresight debug) the peripherals are guarded against.

The SPU is also part of the security infrastructure. Along with providing write-protection functionality, the SPU is employed to define which resources in the system are secure or non-secure and to block access to secure resources from non-secure masters.

Synonymously, the system memory protection unit (SMPU) provides memory protection against read and/or write transactions to defined regions of memory. There are two SMPU units in the ADSP-BF70x processors. One is for the L2 memory and the other is for the external DDR memory.

The SMPU is also part of the security infrastructure. It allows the user to not only protect against arbitrary read and/or write transactions, but it also allows regions of memory to be defined as secure and prevent non-secure masters from accessing those memory regions.

## Watchpoint Protection

The primary purpose of watchpoints and hardware breakpoints is to serve emulator needs. When enabled, they signal an emulator event whenever user-defined system resources are accessed or the core executes from user-defined addresses. Watchpoint events can be configured such that they signal the events to the fault management unit of the SEC.

### Watchdog

The on-chip software watchdog timer can supervise the Blackfin+ core.

### **Bandwidth Monitor**

Memory-to-memory DMA channels are equipped with a bandwidth monitor mechanism. They can signal a system event or fault when transactions tend to starve because system buses are fully loaded with higher-priority traffic.

## Signal Watchdogs

The eight general-purpose timers feature modes to monitor offchip signals. The watchdog period mode monitors whether external signals toggle with a period within an expected range. The watchdog width mode monitors whether the pulse widths of external signals are within an expected range. Both modes help to detect undesired toggling (or lack thereof) of system-level signals.

## **Up/Down Count Mismatch Detection**

The GP counter can monitor external signal pairs, such as request/grant strobes. If the edge count mismatch exceeds the expected range, the GP counter can flag this to the processor or to the fault management unit of the SEC.

### Fault Management

The fault management unit is part of the system event controller (SEC). Any system event, whether a dual-bit uncorrectable ECC error, or any peripheral status interrupt, can be defined as being a fault. Additionally, the system events can be defined as an interrupt to the core. If defined as such, the SEC forwards the event to the fault management unit, which may automatically reset the entire device for reboot, or simply toggle the SYS\_FAULT output pin to signal off-chip hardware. Optionally, the fault management unit can delay the action taken through a keyed sequence, to provide a final chance for the Blackfin+ core to resolve the issue and to prevent the fault action from being taken.

## ADDITIONAL PROCESSOR PERIPHERALS

The processor contains a rich set of peripherals connected to the core through several high-bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the block diagram on Page 1). The processor contains high-speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

The following sections describe additional peripherals that were not previously described.

#### Timers

The processor includes several timers which are described in the following sections.

### Table 3. Clock Dividers

|                                                            | Divider (if Available on    |

|------------------------------------------------------------|-----------------------------|

| Clock Source                                               | SYS_CLKOUT)                 |

| CCLK (Core Clock)                                          | By 16                       |

| SYSCLK (System Clock)                                      | Ву 8                        |

| SCLK0 (System Clock, All Peripherals not Covered by SCLK1) | Not available on SYS_CLKOUT |

| SCLK1 (System Clock for Crypto<br>Engines and MDMA)        | Ву 8                        |

| DCLK (LPDDR/DDR2 Clock)                                    | Ву 8                        |

| OCLK (Output Clock)                                        | Programmable                |

| CLKBUF                                                     | None, direct from SYS_CLKIN |

## **Power Management**

As shown in Table 4, the processor supports multiple power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate Specifications table for processor operating conditions; even if the feature/peripheral is not used.

### Table 4. Power Domains

| Power Domain                                       | V <sub>DD</sub> Range |

|----------------------------------------------------|-----------------------|

| All Internal Logic                                 | V <sub>DD_INT</sub>   |

| DDR2/LPDDR                                         | V <sub>DD_DMC</sub>   |

| USB                                                | $V_{DD_{USB}}$        |

| OTP Memory                                         | V <sub>DD_OTP</sub>   |

| HADC                                               | V <sub>DD_HADC</sub>  |

| RTC                                                | V <sub>DD_RTC</sub>   |

| All Other I/O (Includes SYS, JTAG, and Ports Pins) | V <sub>DD_EXT</sub>   |

The dynamic power management feature of the processor allows the processor's core clock frequency ( $f_{CCLK}$ ) to be dynamically controlled.

The power dissipated by a processor is largely a function of its clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

See Table 5 for a summary of the power settings for each mode.

## Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed, providing capability for maximum operational frequency. This is the power-up default execution state in which maximum performance can be achieved. The processor core and all enabled peripherals run at full speed.

## Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core and to all synchronous peripherals. Asynchronous peripherals may still be running but cannot access internal resources or external memory.

#### Table 5. Power Settings

| Mode/State | PLL      | PLL<br>Bypassed |          | f <sub>sysclk</sub> ,<br>f <sub>DCLK</sub> ,<br>f <sub>sclk0</sub> ,<br>f <sub>sclk1</sub> | Core<br>Power |

|------------|----------|-----------------|----------|--------------------------------------------------------------------------------------------|---------------|

| Full On    | Enabled  | No              | Enabled  | Enabled                                                                                    | On            |

| Deep Sleep | Disabled | _               | Disabled | Disabled                                                                                   | On            |

| Hibernate  | Disabled | —               | Disabled | Disabled                                                                                   | Off           |

### Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling the voltage and clocks to the processor core and to all of the peripherals. This setting signals the external voltage regulator supplying the VDD\_INT pins to shut off using the SYS\_ EXTWAKE signal, which provides the lowest static power dissipation.

Any critical information stored internally (for example, memory contents, register contents, and other information) must be written to a nonvolatile storage device (or self-refreshed DRAM) prior to removing power if the processor state is to be preserved.

Because the  $V_{DD\_EXT}$  pins can still be supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to still have power applied without drawing unwanted current.

## **Reset Control Unit**

Reset is the initial state of the whole processor or the core and is the result of a hardware- or software-triggered event. In this state, all control registers are set to their default values and functional units are idle. Exiting a full system reset starts with the core being ready to boot.

The reset control unit (RCU) controls how all the functional units enter and exit reset. Differences in functional requirements and clocking constraints define how reset signals are generated. Programs must guarantee that none of the reset functions puts the system into an undefined state or causes resources to stall. This is particularly important when the core is reset (programs must ensure that there is no pending system activity involving the core when it is being reset).

From a system perspective, reset is defined by both the reset target and the reset source described as follows in the following list.

## **ADSP-BF70x DETAILED SIGNAL DESCRIPTIONS**

Table 6 provides a detailed description of each pin.

### Table 6. ADSP-BF70x Detailed Signal Descriptions

| Port Name | Direction | Description                                                                                                                                                                                                                                                              |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN_RX    | Input     | Receive. Typically an external CAN transceiver's RX output.                                                                                                                                                                                                              |

| CAN_TX    | Output    | Transmit. Typically an external CAN transceiver's TX input.                                                                                                                                                                                                              |

| CNT_DG    | Input     | <b>Count Down and Gate.</b> Depending on the mode of operation this input acts either as a count down signal or a gate signal Count Down - This input causes the GP counter to decrement Gate - Stops the GP counter from incrementing or decrementing.                  |

| CNT_UD    | Input     | <b>Count Up and Direction.</b> Depending on the mode of operation this input acts either as a count up signal or a direction signal Count Up - This input causes the GP counter to increment Direction - Selects whether the GP counter is incrementing or decrementing. |

| CNT_ZM    | Input     | <b>Count Zero Marker.</b> Input that connects to the zero marker output of a rotary device or detects the pressing of a pushbutton.                                                                                                                                      |

| DMC_Ann   | Output    | Address n. Address bus.                                                                                                                                                                                                                                                  |

| DMC_BAn   | Output    | Bank Address Input n. Defines which internal bank an ACTIVATE, READ, WRITE, or PRECHARGE                                                                                                                                                                                 |

| Dime_DAin | output    | command is being applied to on the dynamic memory. Also defines which mode registers (MR, EMR, EMR2, and/or EMR3) are loaded during the LOAD MODE REGISTER command.                                                                                                      |

| DMC_CAS   | Output    | <b>Column Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the CAS input of dynamic memory.                                                                                    |

| DMC_CK    | Output    | Clock. Outputs DCLK to external dynamic memory.                                                                                                                                                                                                                          |

| DMC_CK    | Output    | Clock (Complement). Complement of DMC_CK.                                                                                                                                                                                                                                |

| DMC_CKE   | Output    | Clock enable. Active high clock enables. Connects to the dynamic memory's CKE input.                                                                                                                                                                                     |

| DMC_CSn   | Output    | Chip Select n. Commands are recognized by the memory only when this signal is asserted.                                                                                                                                                                                  |

| DMC_DQnn  | I/O       | Data n. Bidirectional Data bus.                                                                                                                                                                                                                                          |

| DMC_LDM   | Output    | <b>Data Mask for Lower Byte.</b> Mask for DMC_DQ07:DMC_DQ00 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_LDQS  | I/O       | <b>Data Strobe for Lower Byte.</b> DMC_DQ07:DMC_DQ00 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_LDQS  | I/O       | Data Strobe for Lower Byte (complement). Complement of LDQS. Not used in single-ended mode.                                                                                                                                                                              |

| DMC_ODT   | Output    | <b>On-die termination.</b> Enables dynamic memory termination resistances when driven high (assuming the memory is properly configured). ODT is enabled/disabled regardless of read or write commands.                                                                   |

| DMC_RAS   | Output    | <b>Row Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the RAS input of dynamic memory.                                                                                       |

| DMC_UDM   | Output    | <b>Data Mask for Upper Byte.</b> Mask for DMC_DQ15:DMC_DQ08 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |

| DMC_UDQS  | I/O       | <b>Data Strobe for Upper Byte.</b> DMC_DQ15:DMC_DQ08 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |

| DMC_UDQS  | I/O       | Data Strobe for Upper Byte (complement). Complement of UDQSb. Not used in single-ended mode.                                                                                                                                                                             |

| DMC_VREF  | Input     | Voltage Reference. Connect to half of the VDD_DMC voltage.                                                                                                                                                                                                               |

| DMC_WE    | Output    | Write Enable. Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the WE input of dynamic memory.                                                                                                     |

| PPI_CLK   | I/O       | <b>Clock.</b> Input in external clock mode, output in internal clock mode.                                                                                                                                                                                               |

| PPI_Dnn   | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                          |

| PPI_FS1   | I/O       | Frame Sync 1 (HSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS2   | I/O       | Frame Sync 2 (VSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| PPI_FS3   | I/O       | Frame Sync 3 (FIELD). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |

| HADC_VINn | Input     | <b>Analog Input at channel n.</b> Analog voltage inputs for digital conversion.                                                                                                                                                                                          |

## Table 6. ADSP-BF70x Detailed Signal Descriptions (Continued)

| Port Name   | Direction | Description                                                                                                                                                                          |  |  |  |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SPT_BCLK    | I/O       | <b>Channel B Clock.</b> Data and Frame Sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                             |  |  |  |

| SPT_BD0     | I/O       | <b>Channel B Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                  |  |  |  |

| SPT_BD1     | I/O       | <b>Channel B Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                |  |  |  |

| SPT_BFS     | I/O       | <b>Channel B Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                       |  |  |  |

| SPT_BTDV    | Output    | <b>Channel B Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots.          |  |  |  |

| SYS_BMODEn  | Input     | Boot Mode Control n. Selects the boot mode of the processor.                                                                                                                         |  |  |  |

| SYS_CLKIN   | Input     | Clock/Crystal Input. Connect to an external clock source or crystal.                                                                                                                 |  |  |  |

| SYS_CLKOUT  | Output    | <b>Processor Clock Output.</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter of the HRM for more details.                                                 |  |  |  |

| SYS_EXTWAKE | Output    | <b>External Wake Control.</b> Drives low during hibernate and high all other times. Typically connected to the enable input of the voltage regulator controlling the VDD_INT supply. |  |  |  |

| SYS_FAULT   | I/O       | Active-Low Fault Output. Indicates internal faults or senses external faults depending on the operating mode.                                                                        |  |  |  |

| SYS_HWRST   | Input     | Processor Hardware Reset Control. Resets the device when asserted.                                                                                                                   |  |  |  |

| SYS_NMI     | Input     | Non-maskable Interrupt. See the processor hardware and programming references for more details.                                                                                      |  |  |  |

| SYS_RESOUT  | Output    | Reset Output. Indicates that the device is in the reset or hibernate state.                                                                                                          |  |  |  |

| SYS_WAKEn   | Input     | Power Saving Mode Wakeup n. Wake-up source input for deep sleep and/or hibernate mode.                                                                                               |  |  |  |

| SYS_XTAL    | Output    | <b>Crystal Output.</b> Drives an external crystal. Must be left unconnected if an external clock is driving CLKIN.                                                                   |  |  |  |

| JTG_SWCLK   | I/O       | Serial Wire Clock. Clocks data into and out of the target during debug.                                                                                                              |  |  |  |

| JTG_SWDIO   | I/O       | Serial Wire DIO. Sends and receives serial data to and from the target during debug.                                                                                                 |  |  |  |

| JTG_SWO     | Output    | Serial Wire Out. Provides trace data to the emulator.                                                                                                                                |  |  |  |

| JTG_TCK     | Input     | JTAG Clock. JTAG test access port clock.                                                                                                                                             |  |  |  |

| JTG_TDI     | Input     | JTAG Serial Data In. JTAG test access port data input.                                                                                                                               |  |  |  |

| JTG_TDO     | Output    | JTAG Serial Data Out. JTAG test access port data output.                                                                                                                             |  |  |  |

| JTG_TMS     | Input     | JTAG Mode Select. JTAG test access port mode select.                                                                                                                                 |  |  |  |

| JTG_TRST    | Input     | JTAG Reset. JTAG test access port reset.                                                                                                                                             |  |  |  |

| TM_ACIn     | Input     | Alternate Capture Input n. Provides an additional input for WIDCAP, WATCHDOG, and PININT modes.                                                                                      |  |  |  |

| TM_ACLKn    | Input     | Alternate Clock n. Provides an additional time base for use by an individual timer.                                                                                                  |  |  |  |

| TM_CLK      | Input     | <b>Clock.</b> Provides an additional global time base for use by all the GP timers.                                                                                                  |  |  |  |

| TM_TMRn     | I/O       | Timer n. The main input/output signal for each timer.                                                                                                                                |  |  |  |

| TRACE_CLK   | Output    | Trace Clock. Clock output.                                                                                                                                                           |  |  |  |

| TRACE_Dnn   | Output    | Trace Data n. Unidirectional data bus.                                                                                                                                               |  |  |  |

| TWI_SCL     | I/O       | Serial Clock. Clock output when master, clock input when slave.                                                                                                                      |  |  |  |

| TWI_SDA     | I/O       | Serial Data. Receives or transmits data.                                                                                                                                             |  |  |  |

| UART_CTS    | Input     | Clear to Send. Flow control signal.                                                                                                                                                  |  |  |  |

| UART_RTS    | Output    | Request to Send. Flow control signal.                                                                                                                                                |  |  |  |

| UART_RX     | Input     | <b>Receive.</b> Receive input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                     |  |  |  |

| UART_TX     | Output    | <b>Transmit.</b> Transmit output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                  |  |  |  |

| USB_CLKIN   | Input     | <b>Clock/Crystal Input.</b> This clock input is multiplied by a PLL to form the USB clock. See data sheet specifications for frequency/tolerance information.                        |  |  |  |

## 12 mm × 12 mm 88-LEAD LFCSP (QFN) SIGNAL DESCRIPTIONS

The processor's pin definitions are shown in Table 11. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Description: The Description column in the table provides a verbose (descriptive) name for the signal.

- General-Purpose Port: The Port column in the table shows whether or not the signal is multiplexed with other signals on a general-purpose I/O port pin.

- Pin Name: The Pin Name column in the table identifies the name of the package pin (at power on reset) on which the signal is located (if a single function pin) or is multiplexed (if a general-purpose I/O pin).

## Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions

| Signal Name | Description                     | Port      | Pin Name      |

|-------------|---------------------------------|-----------|---------------|

| CAN0_RX     | CAN0 Receive                    | С         | PC_02         |

| CAN0_TX     | CAN0 Transmit                   | С         | PC_03         |

| CAN1_RX     | CAN1 Receive                    | A         | PA_12         |

| CAN1_TX     | CAN1 Transmit                   | A         | PA_13         |

| CNT0_DG     | CNT0 Count Down and Gate        | A         | PA_07         |

| CNT0_UD     | CNT0 Count Up and Direction     | A         | PA_15         |

| CNT0_ZM     | CNT0 Count Zero Marker          | A         | PA_13         |

| GND         | Ground                          | Not Muxed | GND           |

| JTG_SWCLK   | TAPC0 Serial Wire Clock         | Not Muxed | JTG_TCK_SWCLK |

| JTG_SWDIO   | TAPC0 Serial Wire DIO           | Not Muxed | JTG_TMS_SWDIO |

| JTG_SWO     | TAPC0 Serial Wire Out           | Not Muxed | JTG_TDO_SWO   |

| JTG_TCK     | TAPC0 JTAG Clock                | Not Muxed | JTG_TCK_SWCLK |

| JTG_TDI     | TAPC0 JTAG Serial Data In       | Not Muxed | JTG_TDI       |

| JTG_TDO     | TAPC0 JTAG Serial Data Out      | Not Muxed | JTG_TDO_SWO   |

| JTG_TMS     | TAPC0 JTAG Mode Select          | Not Muxed | JTG_TMS_SWDIO |

| JTG_TRST    | TAPC0 JTAG Reset                | Not Muxed | JTG_TRST      |

| MSI0_CD     | MSI0 Card Detect                | A         | PA_08         |

| MSI0_CLK    | MSI0 Clock                      | С         | PC_09         |

| MSI0_CMD    | MSI0 Command                    | С         | PC_05         |

| MSI0_D0     | MSI0 Data 0                     | С         | PC_08         |

| MSI0_D1     | MSI0 Data 1                     | С         | PC_04         |

| MSI0_D2     | MSI0 Data 2                     | С         | PC_07         |

| MSI0_D3     | MSI0 Data 3                     | С         | PC_06         |

| MSI0_D4     | MSI0 Data 4                     | С         | PC_10         |

| PA_00-PA_15 | Position 00 through Position 15 | A         | PA_00-PA_15   |

| PB_00-PB_15 | Position 00 through Position 15 | В         | PB_00-PB_15   |

| PC_00-PC_10 | Position 00 through Position 10 | С         | PC_00-PC_10   |

| PPI0_CLK    | EPPI0 Clock                     | A         | PA_14         |

| PPI0_D00    | EPPI0 Data 0                    | В         | PB_07         |

| PPI0_D01    | EPPI0 Data 1                    | В         | PB_06         |

| PPI0_D02    | EPPI0 Data 2                    | В         | PB_05         |

| PPI0_D03    | EPPI0 Data 3                    | В         | PB_04         |

| PPI0_D04    | EPPI0 Data 4                    | В         | PB_03         |

| PPI0_D05    | EPPI0 Data 5                    | В         | PB_02         |

| PPI0_D06    | EPPI0 Data 6                    | В         | PB_01         |

| PPI0_D07    | EPPIO Data 7                    | В         | PB_00         |

| Signal Name        | Description                                       | Port      | Pin Name       |

|--------------------|---------------------------------------------------|-----------|----------------|

| PPI0_D08           | EPPIO Data 8                                      | A         | PA_11          |

| PPI0_D09           | EPPI0 Data 9                                      | A         | PA_10          |

| PPI0_D10           | EPPI0 Data 10                                     | A         | PA_09          |

| PPI0_D11           | EPPI0 Data 11                                     | A         | PA_08          |

| PPI0_D12           | EPPI0 Data 12                                     | с         | PC_03          |

| PI0_D13            | EPPIO Data 13                                     | с         | PC_02          |

| PPI0_D14           | EPPIO Data 14                                     | с         | PC_01          |

| PI0_D15            | EPPIO Data 15                                     | с         | PC_00          |

| PI0_D16            | EPPIO Data 16                                     | В         | PB_08          |

| PI0_D17            | EPPIO Data 17                                     | В         | PB_09          |

| PIO_FS1            | EPPI0 Frame Sync 1 (HSYNC)                        | А         | PA_12          |

| PI0_FS2            | EPPI0 Frame Sync 2 (VSYNC)                        | А         | PA_13          |

| PI0_FS3            | EPPI0 Frame Sync 3 (FIELD)                        | А         | PA_15          |

| TC0_CLKIN          | RTC0 Crystal input/external oscillator connection | Not Muxed | <br>RTC0_CLKIN |

| RTC0_XTAL          | RTC0 Crystal output                               | Not Muxed | RTC0_XTAL      |

| MC0_A01            | SMC0 Address 1                                    | A         | PA_08          |

| MC0_A02            | SMC0 Address 2                                    | А         | PA_09          |

| MC0_A03            | SMC0 Address 3                                    | А         | PA_10          |

| MC0_A04            | SMC0 Address 4                                    | A         | PA_11          |

| MC0_A05            | SMC0 Address 5                                    | A         | PA_07          |

| MC0_A06            | SMC0 Address 6                                    | A         | PA_06          |

| MC0_A07            | SMC0 Address 7                                    | A         | PA_05          |

| MC0_A08            | SMC0 Address 8                                    | A         | PA_04          |

| MC0_A09            | SMC0 Address 9                                    | C         | PC_01          |

| MC0_A10            | SMC0 Address 10                                   | C         | PC_02          |

| MC0_A11            | SMC0 Address 11                                   | C         | PC_03          |

| <br>MC0_A12        | SMC0 Address 12                                   | С         | _<br>PC_04     |

| MC0_ABE0           | SMC0 Byte Enable 0                                | A         | PA_00          |

| MC0_ABE1           | SMC0 Byte Enable 1                                | A         | PA_01          |

| MC0_AMS0           | SMC0 Memory Select 0                              | A         | PA_15          |

| MC0_AMS1           | SMC0 Memory Select 1                              | A         | PA_02          |

| MC0_AOE            | SMC0 Output Enable                                | A         | PA_12          |

| MC0_ARDY           | SMC0 Asynchronous Ready                           | A         | PA_03          |

| MC0_ARE            | SMC0 Read Enable                                  | A         | PA_13          |

| MC0_AWE            | SMC0 Write Enable                                 | A         | PA_14          |

| MC0_D00            | SMC0 Data 0                                       | В         | PB_07          |

| MC0_D01            | SMC0 Data 1                                       | B         | PB_06          |

| MC0_D02            | SMC0 Data 2                                       | B         | PB_05          |

| MC0_D03            | SMC0 Data 3                                       | B         | PB_04          |

| MC0_D03<br>MC0_D04 | SMC0 Data 4                                       | B         | PB_03          |

| MC0_D04            | SMC0 Data 5                                       | B         | PB_02          |

| MC0_D05            | SMC0 Data 5                                       | B         | PB_01          |

| SMC0_D00           | SMC0 Data 0                                       | B         | PB_00          |

| MC0_D07            | SMC0 Data 7                                       | B         | PB_08          |

| MC0_D08            | SMC0 Data 9                                       | B         | PB_09          |

| 5MC0_D09           | SMC0 Data 9                                       | B         | PB_10          |

| Signal Name | Multiplexed<br>Function 0 | Multiplexed<br>Function 1 | Multiplexed<br>Function 2 | Multiplexed<br>Function 3 | Multiplexed<br>Function Input Tap |

|-------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------|

| PC_00       | UART1_TX                  | SPT0_AD1                  | PPI0_D15                  |                           |                                   |

| PC_01       | UART1_RX                  | SPT0_BD1                  | PPI0_D14                  | SMC0_A09                  | TM0_ACI4                          |

| PC_02       | UARTO_RTS                 | CAN0_RX                   | PPI0_D13                  | SMC0_A10                  | TM0_ACI5/SYS_<br>WAKE3            |

| PC_03       | UARTO_CTS                 | CAN0_TX                   | PPI0_D12                  | SMC0_A11                  | TM0_ACI0                          |

| PC_04       | SPT0_BCLK                 | SPI0_CLK                  | MSI0_D1                   | SMC0_A12                  | TM0_ACLK0                         |

| PC_05       | SPT0_AFS                  | TM0_TMR3                  | MSI0_CMD                  |                           |                                   |

| PC_06       | SPT0_BD0                  | SPI0_MISO                 | MSI0_D3                   |                           |                                   |

| PC_07       | SPT0_BFS                  | SPI0_MOSI                 | MSI0_D2                   |                           | TM0_ACI2                          |

| PC_08       | SPT0_AD0                  | SPI0_D2                   | MSI0_D0                   |                           |                                   |

| PC_09       | SPT0_ACLK                 | SPI0_D3                   | MSI0_CLK                  |                           | TM0_ACLK2                         |

| PC_10       | SPT1_BCLK                 | MSI0_D4                   | SPI1_SEL3                 |                           | TM0_ACLK1                         |

## Table 14. Signal Multiplexing for Port C

### Table 18. Peripheral Clock Operating Conditions

| Parameter                      | Parameter                                                             |                                              | Min | Тур | Мах | Unit |

|--------------------------------|-----------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>OCLK</sub>              | Output Clock Frequency                                                |                                              |     |     | 50  | MHz  |

| f <sub>sys_clkoutj</sub>       | SYS_CLKOUT Period Jitter <sup>1, 2</sup>                              |                                              |     | ±2  |     | %    |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Transmitting Data                           |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Receiving Data                              |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKEXT</sub>  | External SPI Clock When Receiving Data <sup>3, 4</sup>                | $f_{SPICLKEXT} \leq f_{SCLK0}$               |     |     | 50  | MHz  |

| <b>f</b> <sub>spiclkext</sub>  | External SPI Clock When Transmitting Data <sup>3, 4</sup>             | $f_{\text{SPICLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| f <sub>MSICLKPROG</sub>        | Programmed MSI Clock                                                  |                                              |     |     | 50  | MHz  |

<sup>1</sup>SYS\_CLKOUT jitter is dependent on the application system design including pin switching activity, board layout, and the jitter characteristics of the SYS\_CLKIN source. Due to the dependency on these factors the measured jitter may be higher or lower than this typical specification for each end application.

<sup>2</sup> The value in the Typ field is the percentage of the SYS\_CLKOUT period.

<sup>3</sup> The maximum achievable frequency for any peripheral in external clock mode is dependent on being able to meet the setup and hold times in the ac timing specifications section for that peripheral. Pay particular attention to setup and hold times for VDD\_EXT = 1.8 V which may preclude the maximum frequency listed here.

$^4$  The peripheral external clock frequency must also be less than or equal to the  $f_{SCLK}$  that clocks the peripheral.

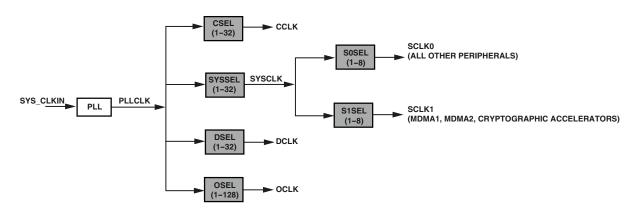

Figure 6. Clock Relationships and Divider Values

## Table 19. Phase-Locked Loop Operating Conditions

| Parameter                  |                     |       | Max | Unit |

|----------------------------|---------------------|-------|-----|------|

| <b>f</b> <sub>PLLCLK</sub> | PLL Clock Frequency | 230.2 | 800 | MHz  |

| CGU_CTL.MSEL <sup>1</sup>  | PLL Multiplier      | 8     | 41  |      |

<sup>1</sup>The CGU\_CTL.MSEL setting must also be chosen to ensure that the f<sub>PLLCLK</sub> specification is not violated.

| Parameter                                   |                                                     | Test Conditions/Comments                                                                                                                                                                                      | Min | Тур | Max                                                     | Unit |

|---------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------------------------------------------|------|

| I <sub>DD_HIBERNATE</sub> <sup>17, 15</sup> | <sup>9</sup> Hibernate State Current                |                                                                                                                                                                                                               |     | 33  |                                                         | μΑ   |

| I <sub>DD_HIBERNATE</sub> <sup>17, 19</sup> | <sup>9</sup> Hibernate State Current<br>Without USB | $V_{DD_INT} = 0 V,$ $V_{DD_DMC} = 1.8 V,$ $V_{DD_EXT} = V_{DD_HADC} = V_{DD_OTP} =$ $V_{DD_RTC} = V_{DD_USB} = 3.3 V,$ $T_J = 25^{\circ}C,$ $f_{CLKIN} = 0,$ $USB protection disabled$ $(USB_PHY_CTLDIS = 1)$ |     | 15  |                                                         | μΑ   |

| I <sub>DD_INT</sub> <sup>18</sup>           | V <sub>DD_INT</sub> Current                         | V <sub>DD_INT</sub> within operating conditions table specifications                                                                                                                                          |     |     | See I <sub>DDINT_TOT</sub><br>equation on<br>on Page 56 |      |

| I <sub>DD_RTC</sub>                         | I <sub>DD_RTC</sub> Current                         | $V_{DD_{RTC}} = 3.3 V, T_{J} = 125^{\circ}C$                                                                                                                                                                  |     |     | 10                                                      | μA   |

<sup>1</sup> Applies to all output and bidirectional signals except DMC0 signals, TWI signals, and USB0 signals.

<sup>2</sup> Applies to DMC0\_Axx, DMC0\_CAS, DMC0\_CKE, DMC0\_CK, DMC0\_CK, DMC0\_CS, DMC0\_DQxx, DMC0\_LDM, DMC0\_LDQS, DMC0\_LDQS,

DMC0\_ODT, DMC0\_RAS, DMC0\_UDM, DMC0\_UDQS, DMC0\_UDQS, and DMC0\_WE signals.

<sup>3</sup> Applies to all output and bidirectional signals except DMC0 signals and USB0 signals.

<sup>4</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TDI, and JTG\_TMS\_SWDIO signals.

<sup>5</sup> Applies to DMC0\_VREF signal.

<sup>6</sup> Applies to JTG\_TCK\_SWCLK and JTG\_TRST signals.

<sup>7</sup> Applies to SMC0\_ARDY, SYS\_BMODEx, SYS\_CLKIN, <u>SYS\_HWRST</u>, JTG\_TCK, and <u>JTG\_TRST</u> signals.

<sup>8</sup> Applies to JTG\_TDI, JTG\_TMS\_SWDIO, PA\_xx, PB\_xx, and PC\_xx signals when internal GPIO pull-ups are enabled. For information on when internal pull-ups are enabled for GPIOs. See ADSP-BF70x Designer Quick Reference on Page 38.

<sup>9</sup> Applies to USB0\_CLKIN signal.

<sup>10</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_AMS0</u>, <u>SMC0\_ARE</u>, <u>SMC0\_AWE</u>, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, JTG\_TDO\_SWO, USB0\_DM, USB0\_DP, USB0\_ID, and USB0\_VBC signals.

<sup>11</sup> Applies to DMC0\_Axx, DMC0\_BAxx, DMC0\_CAS, DMC0\_CS0, DMC0\_DQxx, DMC0\_LDQS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_UDQS, DMC0\_LDM, DMC0\_UDM, DMC0\_ODT, DMC0\_RAS, and DMC0\_WE signals.

<sup>12</sup>Applies to PA\_xx, PB\_xx, PC\_xx, <u>SMC0\_A0E</u>, <u>SMC0\_A0E</u>, <u>SMC0\_Dxx</u>, <u>SYS\_FAULT</u>, <u>JTG\_TDO\_SWO</u>, <u>USB0\_DP</u>, <u>USB0\_ID</u>, <u>USB0\_ID</u>, <u>USB0\_VBC</u>, <u>U</u>

<sup>13</sup>Applies to USB0\_VBUS signals.

<sup>14</sup>Applies to all TWI signals.

<sup>15</sup>Applies to all signals, except DMC0 and TWI signals.

<sup>16</sup>Applies to all DMC0 signals.

<sup>17</sup>See the ADSP-BF70x Blackfin+ Processor Hardware Reference for definition of deep sleep and hibernate operating modes.

<sup>18</sup>Additional information can be found at Total Internal Power Dissipation.

<sup>19</sup>Applies to VDD\_EXT, VDD\_DMC, and VDD\_USB supply signals only. Clock inputs are tied high or low.

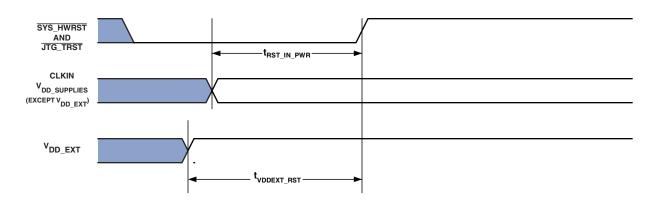

### Power-Up Reset Timing

A power-up reset is required to place the processor in a known state after power-up. A power-up reset is initiated by asserting SYS\_HWRST and JTG\_TRST. During power-up reset, all pins are high impedance except for those noted in the ADSP-BF70x Designer Quick Reference on Page 38.

Both JTG\_TRST and SYS\_HWRST need to be asserted upon power-up, but only SYS\_HWRST needs to be released for the device to boot properly. JTG\_TRST may be asserted indefinitely for normal operation. JTG\_TRST only needs to be released when using an emulator to connect to the DAP for debug or boundary scan. There is an internal pull-down on JTG\_TRST to ensure internal emulation logic will always be properly initialized during power-up reset.

Table 30 and Figure 9 show the relationship between power supply startup and processor reset timing, related to the clock generation unit (CGU) and reset control unit (RCU). In Figure 9,  $V_{DD_{\_SUPPLIES}}$  are  $V_{DD_{\_INT}}$ ,  $V_{DD_{\_EXT}}$ ,  $V_{DD_{\_DMC}}$ ,  $V_{DD_{\_USB}}$ ,  $V_{DD_{\_CTC}}$ ,  $V_{DD_{\_OTP}}$ , and  $V_{DD_{\_HADC}}$ .

There is no power supply sequencing requirement for the ADSP-BF70x processor. However, if saving power during power-on is important, bringing up  $V_{DD_{INT}}$  last is recommended. This avoids a small current drain in the  $V_{DD_{INT}}$  domain during the transition period of I/O voltages from 0 V to within the voltage specification.

### Table 30. Power-Up Reset Timing

| Paramete                | r                                                                                                                                                                                                                                                                  | Min                  | Max | Unit |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|

| Timing Red              | quirement                                                                                                                                                                                                                                                          |                      |     |      |

| t <sub>rst_in_pwr</sub> | $\label{eq:starsest} \overrightarrow{SYS_HWRST} and \ \overrightarrow{JTG_TRST} \ Deasserted \ After \ V_{DD\_INT}, \ V_{DD\_DMC}, \ V_{DD\_USB}, \\ V_{DD\_RTC}, \ V_{DD\_OTP}, \ V_{DD\_HADC}, \ and \ SYS\_CLKIN \ are \ Stable \ and \ Within \ Specification$ | $11 \times t_{CKIN}$ |     | ns   |

| t <sub>VDDEXT_RST</sub> | SYS_HWRST Deasserted After V <sub>DD_EXT</sub> is Stable and Within Specifications (No External Pull-Down on JTG_TRST)                                                                                                                                             | 10                   |     | μs   |

| t <sub>VDDEXT_RST</sub> | $\overline{SYS}_{HWRST}$ Deasserted After $V_{DD\_EXT}$ is Stable and Within Specifications (10k External Pull-Down on $\overline{JTG}_{TRST}$ )                                                                                                                   | 1                    |     | μs   |

Figure 9. Power-Up Reset Timing

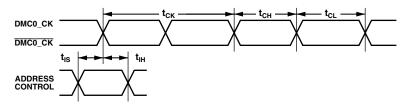

## DDR2 SDRAM Clock and Control Cycle Timing

Table 39 and Figure 17 show DDR2 SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

## Table 39. DDR2 SDRAM Read Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                 |                                                |      | 200 MHz |                 |

|-----------------|------------------------------------------------|------|---------|-----------------|

| Parameter       |                                                | Min  | Мах     | Unit            |

| Switching       | Characteristics                                |      |         |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |         | ns              |

| t <sub>CH</sub> | High Clock Pulse Width                         | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>CL</sub> | Low Clock Pulse Width                          | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 350  |         | ps              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMC0_CK Rise  | 475  |         | ps              |

NOTE: CONTROL = DMC0\_CS0, DMC0\_CKE, DMC0\_RAS, DMC0\_CAS, AND DMC0\_WE. ADDRESS = DMC0\_A00-13, AND DMC0\_BA0-2.

Figure 17. DDR2 SDRAM Clock and Control Cycle Timing

## Mobile DDR SDRAM Clock and Control Cycle Timing

Table 42 and Figure 20 show mobile DDR SDRAM clock and control cycle timing, related to the dynamic memory controller (DMC).

### Table 42. Mobile DDR SDRAM Clock and Control Cycle Timing, $V_{\text{DD}\_\text{DMC}}$ Nominal 1.8 V

|                 |                                                |      | 200 MHz |                 |

|-----------------|------------------------------------------------|------|---------|-----------------|

| Parameter       |                                                | Min  | Мах     | Unit            |

| Switching       | Characteristics                                |      |         |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |         | ns              |

| t <sub>CH</sub> | Minimum Clock Pulse Width                      | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>CL</sub> | Maximum Clock Pulse Width                      | 0.45 | 0.55    | t <sub>CK</sub> |

| t <sub>IS</sub> | Control/Address Setup Relative to DMC0_CK Rise | 1.5  |         | ns              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMC0_CK Rise  | 1.5  |         | ns              |

NOTE: CONTROL = DMC0\_CS0, DMC0\_CKE, DMC0\_RAS, DMC0\_CAS, AND DMC0\_WE. ADDRESS = DMC0\_A00-13, AND DMC0\_BA0-2.

Figure 20. Mobile DDR SDRAM Clock and Control Cycle Timing

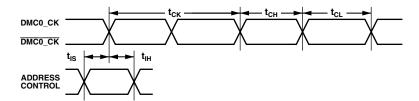

Figure 27. Serial Ports

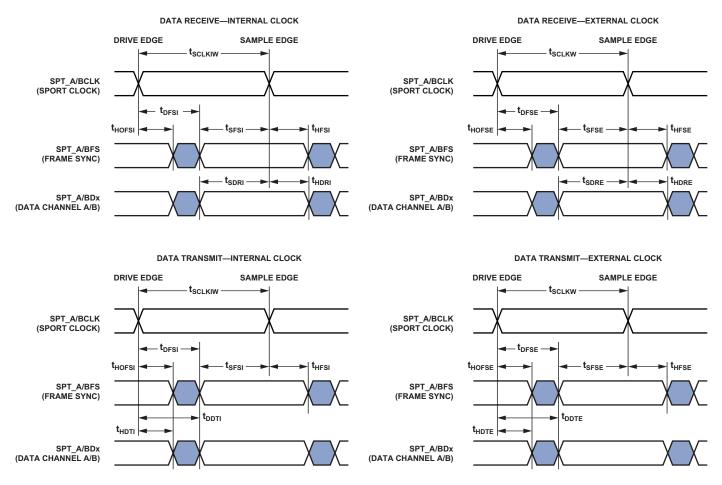

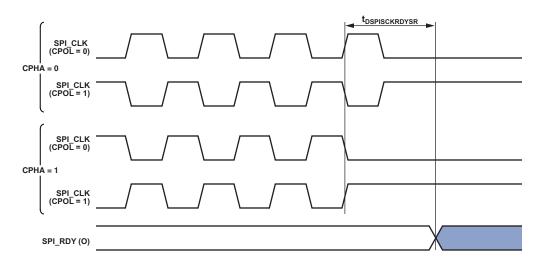

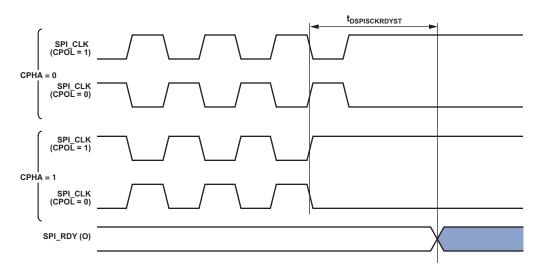

### Serial Peripheral Interface (SPI) Port—SPI\_RDY Slave Timing

Table 56. SPI Port—SPI\_RDY Slave Timing

|                           |                                                                           | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal       |                                     |      |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|------|

| Parameter                 |                                                                           | Min                                              | Max                                 | Unit |

| Switching C               | haracteristics                                                            |                                                  |                                     |      |

| t <sub>dspisckrdysr</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Receive  | $2.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $3.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

| t <sub>dspisckrdyst</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Transmit | $3.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $4.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

Figure 33. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Receive (FCCH = 0)

Figure 34. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Transmit (FCCH = 1)

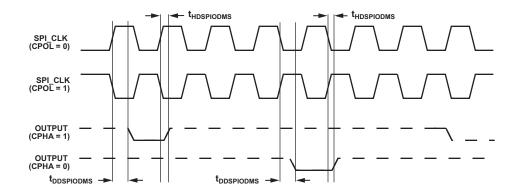

Table 58. SPI Port—ODM Slave Mode

|                           |                                                    | 1   | V <sub>DD_EXT</sub><br>.8 V Nominal | 3.3 | V <sub>DD_EXT</sub><br>SV Nominal |      |

|---------------------------|----------------------------------------------------|-----|-------------------------------------|-----|-----------------------------------|------|

| Parameter                 |                                                    | Min | Max                                 | Min | Max                               | Unit |

| Switching Characteristics |                                                    |     |                                     |     |                                   |      |

| t <sub>hdspiodms</sub>    | SPI_CLK Edge to High Impedance from Data Out Valid | 2.5 |                                     | 2.5 |                                   | ns   |

| t <sub>DDSPIODMS</sub>    | SPI_CLK Edge to Data Out Valid from High Impedance |     | 17.5                                |     | 14.5                              | ns   |

Figure 36. ODM Slave

### Universal Asynchronous Receiver-Transmitter (UART) Ports—Receive and Transmit Timing

The universal asynchronous receiver-transmitter (UART) ports receive and transmit operations are described in the *ADSP-BF70x Blackfin+ Processor Hardware Reference*.

### Controller Area Network (CAN) Interface

The controller area network (CAN) interface timing is described in the ADSP-BF70x Blackfin+ Processor Hardware Reference.

## Universal Serial Bus (USB) On-The-Go—Receive and Transmit Timing

Table 62 describes the universal serial bus (USB) on-the-go receive and transmit operations.

## Table 62. USB On-The-Go—Receive and Transmit Timing

|                   |                                  | V <sub>DD_USB</sub><br>3.3 V Nominal |     |      |

|-------------------|----------------------------------|--------------------------------------|-----|------|

| Parameter         |                                  |                                      | Max | Unit |

| Timing Requirem   | ents                             |                                      |     |      |

| f <sub>USBS</sub> | USB_XI Frequency                 | 24                                   | 24  | MHz  |

| fs <sub>USB</sub> | USB_XI Clock Frequency Stability | -50                                  | +50 | ppm  |

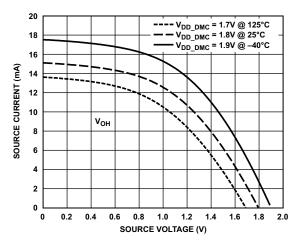

Figure 61. Driver Type B and Device Driver C (DDR Drive Strength  $60 \Omega$ )

## **TEST CONDITIONS**

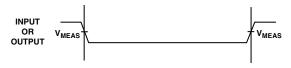

All timing requirements appearing in this data sheet were measured under the conditions described in this section. Figure 62 shows the measurement point for ac measurements (except output enable/disable). The measurement point  $V_{\text{MEAS}}$  is  $V_{\text{DD}\_\text{EXT}}/2$  for  $V_{\text{DD}\_\text{EXT}}$  (nominal) = 1.8 V/3.3 V.

Figure 62. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

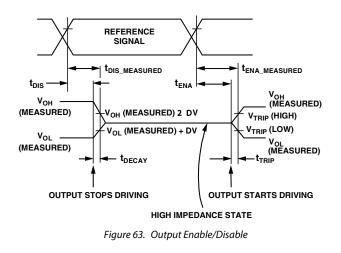

## **Output Enable Time Measurement**

Output balls are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving.

The output enable time  $t_{ENA}$  is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown on the right side of Figure 63.

The time  $t_{ENA\_MEASURED}$  is the interval from when the reference signal switches to when the output voltage reaches  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low). For  $V_{DD\_EXT}$  (nominal) = 1.8 V,  $V_{TRIP}$  (high) is 1.05 V, and  $V_{TRIP}$  (low) is 0.75 V. For  $V_{DD\_EXT}$  (nominal) = 3.3 V,  $V_{TRIP}$  (high) is 1.9 V, and  $V_{TRIP}$  (low) is 1.4 V. Time  $t_{TRIP}$  is the interval from when the output starts driving to when the output reaches the  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low) trip voltage.

Time  $t_{ENA}$  is calculated as shown in the equation:

$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$

If multiple balls (such as the data bus) are enabled, the measurement value is that of the first ball to start driving.

#### **Output Disable Time Measurement**

Output balls are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The output disable time  $t_{DIS}$  is the difference between  $t_{DIS\_MEASURED}$  and  $t_{DECAY}$  as shown on the left side of Figure 63.

$$t_{DIS} = t_{DIS\_MEASURED} - t_{DECAY}$$

The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load,  $C_L$  and the load current,  $I_L$ . This decay time can be approximated by the equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The time  $t_{DECAY}$  is calculated with test loads  $C_L$  and  $I_L$ , and with  $\Delta V$  equal to 0.25 V for  $V_{DD\_EXT}$  (nominal) = 3.3 V and 0.15 V for  $V_{DD\_EXT}$  (nominal) = 1.8V.

The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches, to when the output voltage decays  $\Delta V$  from the measured output high or output low voltage.

### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the previous equation. Choose  $\Delta V$  to be the difference between the processor's output voltage and the input threshold for the device requiring the hold time.  $C_L$  is the total bus capacitance (per data line), and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the various output disable times as specified in the Timing Specifications on Page 60.

Table 69 lists the 12 mm  $\times$  12 mm 88-Lead LFCSP (QFN) package by lead number for the ADSP-BF70x. Table 70 lists the12 mm  $\times$  12 mm 88-Lead LFCSP (QFN) package by signal.

| Lead No.    | Signal Name            | Lead No.     | Signal Name              | Lead No.    | Signal Name   | Lead No. | Signal Name   |

|-------------|------------------------|--------------|--------------------------|-------------|---------------|----------|---------------|

| 1           | PC_10                  | 24           | PB_14                    | 47          | PB_02         | 70       | PA_07         |

| 2           | PC_09                  | 25           | PB_13                    | 48          | PB_01         | 71       | PA_06         |

| 3           | PC_08                  | 26           | VDD_EXT                  | 49          | VDD_OTP       | 72       | VDD_EXT       |

| 4           | VDD_EXT                | 27           | PB_12                    | 50          | VDD_EXT       | 73       | PA_05         |

| 5           | PC_07                  | 28           | PB_11                    | 51          | VDD_INT       | 74       | PA_04         |

| 6           | PC_06                  | 29           | PB_10                    | 52          | PB_00         | 75       | PA_03         |

| 7           | PC_05                  | 30           | VDD_INT                  | 53          | PA_15         | 76       | GND           |

| 8           | PC_04                  | 31           | USB0_XTAL                | 54          | PA_14         | 77       | SYS_NMI       |

| 9           | PC_03                  | 32           | USB0_CLKIN               | 55          | VDD_EXT       | 78       | PA_02         |

| 10          | PC_02                  | 33           | USB0_ID                  | 56          | SYS_XTAL      | 79       | SYS_EXTWAKE   |

| 11          | VDD_EXT                | 34           | USB0_VBUS                | 57          | SYS_CLKIN     | 80       | PA_01         |

| 12          | SYS_CLKOUT             | 35           | USB0_DP                  | 58          | PA_13         | 81       | VDD_INT       |

| 13          | PC_01                  | 36           | VDD_USB                  | 59          | PA_12         | 82       | VDD_EXT       |

| 14          | VDD_INT                | 37           | USB0_DM                  | 60          | PA_11         | 83       | JTG_TDO_SWO   |

| 15          | SYS_RESOUT             | 38           | USB0_VBC                 | 61          | VDD_INT       | 84       | JTG_TMS_SWDIO |

| 16          | PC_00                  | 39           | PB_09                    | 62          | VDD_EXT       | 85       | JTG_TCK_SWCLK |

| 17          | VDD_EXT                | 40           | PB_08                    | 63          | PA_10         | 86       | JTG_TDI       |

| 18          | TWI0_SDA               | 41           | VDD_EXT                  | 64          | PA_09         | 87       | JTG_TRST      |

| 19          | TWI0_SCL               | 42           | PB_07                    | 65          | SYS_FAULT     | 88       | PA_00         |

| 20          | RTC0_XTAL              | 43           | PB_06                    | 66          | SYS_BMODE0    | 89*      | GND           |

| 21          | RTC0_CLKIN             | 44           | PB_05                    | 67          | SYS_BMODE1    |          |               |

| 22          | VDD_RTC                | 45           | PB_04                    | 68          | SYS_HWRST     |          |               |

| 23          | PB_15                  | 46           | PB_03                    | 69          | PA_08         |          |               |

| *Pin no. 89 | is the GND supply (see | Figure 70) f | or the processor; this p | ad must cor | nnect to GND. |          |               |

## Table 69. 12 mm × 12 mm 88-Lead LFCSP (QFN) Lead Assignment (Numerical by Lead Number)

## **ORDERING GUIDE**

| Model <sup>1</sup> | Max. Core Clock | L2 SRAM     | Temperature<br>Grade <sup>2</sup> | Package Description | Package<br>Option |

|--------------------|-----------------|-------------|-----------------------------------|---------------------|-------------------|

| ADSP-BF700KCPZ-1   | 100 MHz         | 128K bytes  | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF700KCPZ-2   | 200 MHz         | 128K bytes  | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF700BCPZ-2   | 200 MHz         | 128K bytes  | -40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF701KBCZ-1   | 100 MHz         | 128K bytes  | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF701KBCZ-2   | 200 MHz         | 128K bytes  | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF701BBCZ-2   | 200 MHz         | 128K bytes  | –40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF702KCPZ-3   | 300 MHz         | 256K bytes  | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF702BCPZ-3   | 300 MHz         | 256K bytes  | –40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF702KCPZ-4   | 400 MHz         | 256K bytes  | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF702BCPZ-4   | 400 MHz         | 256K bytes  | –40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF703KBCZ-3   | 300 MHz         | 256K bytes  | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF703BBCZ-3   | 300 MHz         | 256K bytes  | –40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF703KBCZ-4   | 400 MHz         | 256K bytes  | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF703BBCZ-4   | 400 MHz         | 256K bytes  | –40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF704KCPZ-3   | 300 MHz         | 512K bytes  | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF704BCPZ-3   | 300 MHz         | 512K bytes  | –40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF704KCPZ-4   | 400 MHz         | 512K bytes  | 0C to +70C                        | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF704BCPZ-4   | 400 MHz         | 512K bytes  | –40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF705KBCZ-3   | 300 MHz         | 512K bytes  | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF705BBCZ-3   | 300 MHz         | 512K bytes  | -40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF705KBCZ-4   | 400 MHz         | 512K bytes  | 0C to +70C                        | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF705BBCZ-4   | 400 MHz         | 512K bytes  | -40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF706KCPZ-3   | 300 MHz         | 1024K bytes | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF706BCPZ-3   | 300 MHz         | 1024K bytes | -40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF706KCPZ-4   | 400 MHz         | 1024K bytes | 0°C to +70°C                      | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF706BCPZ-4   | 400 MHz         | 1024K bytes | –40°C to +85°C                    | 88-Lead LFCSP_VQ    | CP-88-8           |

| ADSP-BF707KBCZ-3   | 300 MHz         | 1024K bytes | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF707BBCZ-3   | 300 MHz         | 1024K bytes | –40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF707KBCZ-4   | 400 MHz         | 1024K bytes | 0°C to +70°C                      | 184-Ball CSP_BGA    | BC-184-1          |

| ADSP-BF707BBCZ-4   | 400 MHz         | 1024K bytes | -40°C to +85°C                    | 184-Ball CSP_BGA    | BC-184-1          |

$^{1}$ Z = RoHS Compliant Part.

$^{2}$  Referenced temperature is ambient temperature. The ambient temperature is not a specification. See Operating Conditions on Page 50 for the junction temperature (T<sub>j</sub>) specification which is the only temperature specification.

©2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12396-0-9/15(A)

www.analog.com