Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 1MB                                                                                       |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf707bbcz-3                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Static Memory Controller (SMC)

The SMC can be programmed to control up to two blocks of external memories or memory-mapped devices, with very flexible timing parameters. Each block occupies a 8K byte segment regardless of the size of the device used.

### Dynamic Memory Controller (DMC)

The DMC includes a controller that supports JESD79-2E compatible double-data-rate (DDR2) SDRAM and JESD209A lowpower DDR (LPDDR) SDRAM devices. The DMC PHY features on-die termination on all data and data strobe pins that can be used during reads.

### I/O Memory Space

The processor does not define a separate I/O space. All resources are mapped through the flat 32-bit address space. Onchip I/O devices have their control registers mapped into memory-mapped registers (MMRs) at addresses in a region of the 4G byte address space. These are separated into two smaller blocks, one which contains the control MMRs for all core functions, and the other which contains the registers needed for setup and control of the on-chip peripherals outside of the core. The MMRs are accessible only in supervisor mode and appear as reserved space to on-chip peripherals.

#### Booting

The processor has several mechanisms for automatically loading internal and external memory after a reset. The boot mode is defined by the SYS\_BMODE input pins dedicated for this purpose. There are two categories of boot modes. In master boot mode, the processor actively loads data from serial memories. In slave boot modes, the processor receives data from external host devices.

The boot modes are shown in Table 2. These modes are implemented by the SYS\_BMODE bits of the reset configuration register and are sampled during power-on resets and softwareinitiated resets.

#### Table 2. Boot Modes

| SYS_BMODE Setting | Boot Mode    |

|-------------------|--------------|

| 00                | No Boot/Idle |

| 01                | SPI2 Master  |

| 10                | SPI2 Slave   |

| 11                | UART0 Slave  |

### **SECURITY FEATURES**

The ADSP-BF70x processor supports standards-based hardware-accelerated encryption, decryption, authentication, and true random number generation. The following hardware-accelerated cryptographic ciphers are supported:

- AES in ECB, CBC, ICM, and CTR modes with 128-, 192-, and 256-bit keys

- DES in ECB and CBC mode with 56-bit key

- 3DES in ECB and CBC mode with 3x 56-bit key

The following hardware-accelerated hash functions are supported:

- SHA-1

- SHA-2 with 224-bit and 256-bit digest

- HMAC transforms for SHA-1 and SHA-2

Public key accelerator is available to offload computation-intensive public key cryptography operations.

Both a hardware-based nondeterministic random number generator and pseudo-random number generator are available. The TRNG also provides HW post-processing to meet NIST requirements of FIPS 140-2, while the PRNG is ANSI X9.31 compliant.

Secure boot is also available with 224-bit elliptic curve digital signatures ensuring integrity and authenticity of the boot stream. Optionally, confidentiality is also ensured through AES-128 encryption.

#### CAUTION

This product includes security features that can be used to protect embedded nonvolatile memory contents and prevent execution of unauthorized code. When security is enabled on this device (either by the ordering party or the subsequent receiving parties), the ability of Analog Devices to conduct failure analysis on returned devices is limited. Contact Analog Devices for details on the failure analysis limitations for this device.

Secure debug is also employed to allow only trusted users to access the system with debug tools.

### **PROCESSOR SAFETY FEATURES**

The ADSP-BF70x processor has been designed for functional safety applications. While the level of safety is mainly dominated by the system concept, the following primitives are provided by the devices to build a robust safety concept.

#### Multi-Parity-Bit-Protected L1 Memories

In the processor's L1 memory space, whether SRAM or cache, each word is protected by multiple parity bits to detect the single event upsets that occur in all RAMs. This applies both to L1 instruction and data memory spaces.

#### **ECC-Protected L2 Memories**

Error correcting codes (ECC) are used to correct single event upsets. The L2 memory is protected with a single error correctdouble error detect (SEC-DED) code. By default ECC is enabled, but it can be disabled on a per-bank basis. Single-bit errors are transparently corrected. Dual-bit errors can issue a

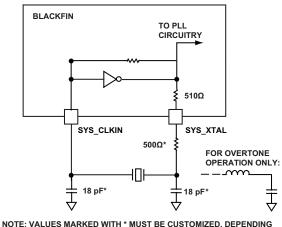

level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations on multiple devices over the required temperature range.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18pF SHOULD BE TREATED AS A MAXIMUM.

Figure 4. External Crystal Connection

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone by adding a tuned inductor circuit as shown in Figure 4. A design procedure for third-overtone operation is discussed in detail in application note (EE-168) *Using Third Overtone Crystals with the ADSP-218x DSP* (www.analog.com/ee-168).

The same recommendations may be used for the USB crystal oscillator.

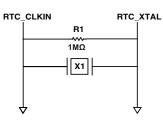

#### **Real-Time Clock**

The real-time clock (RTC) provides a robust set of digital watch features, including current time, stopwatch, and alarm. The RTC is clocked by a 32.768 kHz crystal external to the processor. Connect RTC pins RTC\_CLKIN and RTC\_XTAL with external components as shown in Figure 5.

The RTC peripheral has dedicated power supply pins so that it can remain powered up and clocked even when the rest of the processor is in a low power state. The RTC provides several programmable interrupt options, including interrupt per second, minute, hour, or day clock ticks, interrupt on programmable stopwatch countdown, or interrupt at a programmed alarm time.

The 32.768 kHz input clock frequency is divided down to a 1 Hz signal by a prescaler. The counter function of the timer consists of four counters: a 60-second counter, a 60-minute counter, a 24-hour counter, and a 32,768-day counter. When the alarm interrupt is enabled, the alarm function generates an interrupt when the output of the timer matches the programmed value in the alarm control register. There are two alarms. The first alarm is for a time of day. The second alarm is for a specific day and time of that day.

NOTE: CRYSTAL LOAD CAPACITORS ARE NOT NECESSARY IN MOST CASES.

Figure 5. External Components for RTC

The stopwatch function counts down from a programmed value, with one-second resolution. When the stopwatch interrupt is enabled and the counter underflows, an interrupt is generated.

#### **Clock Generation**

The clock generation unit (CGU) generates all on-chip clocks and synchronization signals. Multiplication factors are programmed to define the PLLCLK frequency. Programmable values divide the PLLCLK frequency to generate the core clock (CCLK), the system clocks (SYSCLK, SCLK0, and SCLK1), the LPDDR or DDR2 clock (DCLK), and the output clock (OCLK).

Writing to the CGU control registers does not affect the behavior of the PLL immediately. Registers are first programmed with a new value, and the PLL logic executes the changes so that it transitions smoothly from the current conditions to the new ones.

SYS\_CLKIN oscillations start when power is applied to the VDD\_EXT pins. The rising edge of SYS\_HWRST can be applied after all voltage supplies are within specifications, and SYS\_CLKIN oscillations are stable.

### Clock Out/External Clock

The SYS\_CLKOUT output pin has programmable options to output divided-down versions of the on-chip clocks. By default, the SYS\_CLKOUT pin drives a buffered version of the SYS\_ CLKIN input. Clock generation faults (for example, PLL unlock) may trigger a reset by hardware. The clocks shown in Table 3 can be output on the SYS\_CLKOUT pin.

#### Table 3. Clock Dividers

|                                                            | Divider (if Available on    |

|------------------------------------------------------------|-----------------------------|

| Clock Source                                               | SYS_CLKOUT)                 |

| CCLK (Core Clock)                                          | By 16                       |

| SYSCLK (System Clock)                                      | Ву 8                        |

| SCLK0 (System Clock, All Peripherals not Covered by SCLK1) | Not available on SYS_CLKOUT |

| SCLK1 (System Clock for Crypto<br>Engines and MDMA)        | Ву 8                        |

| DCLK (LPDDR/DDR2 Clock)                                    | Ву 8                        |

| OCLK (Output Clock)                                        | Programmable                |

| CLKBUF                                                     | None, direct from SYS_CLKIN |

#### **Power Management**

As shown in Table 4, the processor supports multiple power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate Specifications table for processor operating conditions; even if the feature/peripheral is not used.

#### Table 4. Power Domains

| Power Domain                                       | V <sub>DD</sub> Range |

|----------------------------------------------------|-----------------------|

| All Internal Logic                                 | V <sub>DD_INT</sub>   |

| DDR2/LPDDR                                         | V <sub>DD_DMC</sub>   |

| USB                                                | $V_{DD_{USB}}$        |

| OTP Memory                                         | V <sub>DD_OTP</sub>   |

| HADC                                               | V <sub>DD_HADC</sub>  |

| RTC                                                | V <sub>DD_RTC</sub>   |

| All Other I/O (Includes SYS, JTAG, and Ports Pins) | V <sub>DD_EXT</sub>   |

The dynamic power management feature of the processor allows the processor's core clock frequency ( $f_{CCLK}$ ) to be dynamically controlled.

The power dissipated by a processor is largely a function of its clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

See Table 5 for a summary of the power settings for each mode.

#### Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed, providing capability for maximum operational frequency. This is the power-up default execution state in which maximum performance can be achieved. The processor core and all enabled peripherals run at full speed.

### Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core and to all synchronous peripherals. Asynchronous peripherals may still be running but cannot access internal resources or external memory.

#### Table 5. Power Settings

| Mode/State | PLL      | PLL<br>Bypassed |          | f <sub>sysclk</sub> ,<br>f <sub>DCLK</sub> ,<br>f <sub>sclk0</sub> ,<br>f <sub>sclk1</sub> | Core<br>Power |

|------------|----------|-----------------|----------|--------------------------------------------------------------------------------------------|---------------|

| Full On    | Enabled  | No              | Enabled  | Enabled                                                                                    | On            |

| Deep Sleep | Disabled | _               | Disabled | Disabled                                                                                   | On            |

| Hibernate  | Disabled | —               | Disabled | Disabled                                                                                   | Off           |

#### Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling the voltage and clocks to the processor core and to all of the peripherals. This setting signals the external voltage regulator supplying the VDD\_INT pins to shut off using the SYS\_ EXTWAKE signal, which provides the lowest static power dissipation.

Any critical information stored internally (for example, memory contents, register contents, and other information) must be written to a nonvolatile storage device (or self-refreshed DRAM) prior to removing power if the processor state is to be preserved.

Because the  $V_{DD\_EXT}$  pins can still be supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to still have power applied without drawing unwanted current.

#### **Reset Control Unit**

Reset is the initial state of the whole processor or the core and is the result of a hardware- or software-triggered event. In this state, all control registers are set to their default values and functional units are idle. Exiting a full system reset starts with the core being ready to boot.

The reset control unit (RCU) controls how all the functional units enter and exit reset. Differences in functional requirements and clocking constraints define how reset signals are generated. Programs must guarantee that none of the reset functions puts the system into an undefined state or causes resources to stall. This is particularly important when the core is reset (programs must ensure that there is no pending system activity involving the core when it is being reset).

From a system perspective, reset is defined by both the reset target and the reset source described as follows in the following list.

#### SECURITY FEATURES DISCLAIMER

To our knowledge, the Security Features, when used in accordance with the data sheet and hardware reference manual specifications, provide a secure method of implementing code and data safeguards. However, Analog Devices does not guarantee that this technology provides absolute security. ACCORDINGLY, ANALOG DEVICES HEREBY DISCLAIMS ANY AND ALL EXPRESS AND IMPLIED WARRANTIES THAT THE SECURITY FEATURES CANNOT BE BREACHED, COMPROMISED, OR OTHERWISE CIRCUM-VENTED AND IN NO EVENT SHALL ANALOG DEVICES BE LIABLE FOR ANY LOSS, DAMAGE, DESTRUCTION, OR RELEASE OF DATA, INFORMATION, PHYSICAL PROP-ERTY, OR INTELLECTUAL PROPERTY.

### GPIO MULTIPLEXING FOR 184-BALL CSP\_BGA

Table 8 through Table 10 identify the pin functions that are multiplexed on the general-purpose I/O pins of the 184-ball CSP\_BGA package.

#### Table 8. Signal Multiplexing for Port A

| Cignal Nama | Multiplexed | Multiplexed | Multiplexed<br>Function 2 | Multiplexed | Multiplexed            |

|-------------|-------------|-------------|---------------------------|-------------|------------------------|

| Signal Name | Function 0  | Function 1  |                           | Function 3  | Function Input Tap     |

| PA_00       | SPI1_CLK    |             | TRACE0_D07                | SMC0_ABE0   |                        |

| PA_01       | SPI1_MISO   |             | TRACE0_D06                | SMC0_ABE1   |                        |

| PA_02       | SPI1_MOSI   |             | TRACE0_D05                | SMC0_AMS1   |                        |

| PA_03       | SPI1_SEL2   | SPI1_RDY    |                           | SMC0_ARDY   |                        |

| PA_04       | SPI1_SEL1   | TM0_TMR7    | SPI2_RDY                  | SMC0_A08    | SPI1_SS                |

| PA_05       | TM0_TMR0    | SPI0_SEL1   |                           | SMC0_A07    | SPI0_SS                |

| PA_06       | TM0_TMR1    | SPI0_SEL2   | SPI0_RDY                  | SMC0_A06    |                        |

| PA_07       | TM0_TMR2    | SPT1_BTDV   | SPT1_ATDV                 | SMC0_A05    | CNT0_DG                |

| PA_08       | PPI0_D11    | MSI0_CD     | SPT1_ACLK                 | SMC0_A01    |                        |

| PA_09       | PPI0_D10    | TM0_TMR4    | SPT1_AFS                  | SMC0_A02    |                        |

| PA_10       | PPI0_D09    | TM0_TMR5    | SPT1_AD0                  | SMC0_A03    |                        |

| PA_11       | PPI0_D08    | TM0_TMR6    | SPT1_AD1                  | SMC0_A04    |                        |

| PA_12       | PPI0_FS1    | CAN1_RX     | SPT0_AFS                  | SMC0_AOE    | TM0_ACI6/SYS_<br>WAKE4 |

| PA_13       | PPI0_FS2    | CAN1_TX     | SPT0_ACLK                 | SMC0_ARE    | CNT0_ZM                |

| PA_14       | PPI0_CLK    | SPI1_SEL4   | SPT0_AD0                  | SMC0_AWE    | TM0_ACLK5              |

| PA_15       | PPI0_FS3    | SPT0_ATDV   | SPT0_BTDV                 | SMC0_AMS0   | CNT0_UD                |

#### Table 9. Signal Multiplexing for Port B

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed               |

|-------------|-------------|-------------|-------------|-------------|---------------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | <b>Function Input Tap</b> |

| PB_00       | PPI0_D07    | SPT1_BCLK   | SPI0_CLK    | SMC0_D07    | TM0_ACLK3                 |

| PB_01       | PPI0_D06    | SPT1_BFS    | SPI0_MISO   | SMC0_D06    | TM0_ACI1                  |

| PB_02       | PPI0_D05    | SPT1_BD0    | SPI0_MOSI   | SMC0_D05    |                           |

| PB_03       | PPI0_D04    | SPT1_BD1    | SPI0_D2     | SMC0_D04    |                           |

| PB_04       | PPI0_D03    | SPT0_BCLK   | SPI0_SEL4   | SMC0_D03    | TM0_ACLK6                 |

| PB_05       | PPI0_D02    | SPT0_BD0    | SPI0_SEL5   | SMC0_D02    |                           |

| PB_06       | PPI0_D01    | SPT0_BFS    | SPI0_SEL6   | SMC0_D01    | TM0_CLK                   |

| PB_07       | PPI0_D00    | SPT0_BD1    | SPI0_D3     | SMC0_D00    | SYS_WAKE0                 |

| PB_08       | UART0_TX    | PPI0_D16    | SPI2_SEL2   | SMC0_D08    | SYS_WAKE1                 |

| PB_09       | UART0_RX    | PPI0_D17    | SPI2_SEL3   | SMC0_D09    | TM0_ACI3                  |

| PB_10       | SPI2_CLK    |             | TRACE0_CLK  | SMC0_D10    | TM0_ACLK4                 |

| PB_11       | SPI2_MISO   |             | TRACE0_D04  | SMC0_D11    |                           |

| PB_12       | SPI2_MOSI   |             | TRACE0_D03  | SMC0_D12    | SYS_WAKE2                 |

| PB_13       | SPI2_D2     | UART1_RTS   | TRACE0_D02  | SMC0_D13    |                           |

| PB_14       | SPI2_D3     | UART1_CTS   | TRACE0_D01  | SMC0_D14    |                           |

| PB_15       | SPI2_SEL1   |             | TRACE0_D00  | SMC0_D15    | SPI2_SS                   |

### ADSP-BF70x DESIGNER QUICK REFERENCE

Table 15 provides a quick reference summary of pin related information for circuit board design. The columns in this table provide the following information:

- Signal Name: The Signal Name column in the table includes the signal name for every pin and (where applicable) the GPIO multiplexed pin function for every pin.

- Pin Type: The Type column in the table identifies the I/O type or supply type of the pin. The abbreviations used in this column are na (none), I/O (input/output), a (analog), s (supply), and g (ground).

- Driver Type: The Driver Type column in the table identifies the driver type used by the pin. The driver types are defined in the output drive currents section of this data sheet.

- Internal Termination: The Int Term column in the table specifies the termination present when the processor is not in the reset or hibernate state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Reset Termination: The Reset Term column in the table specifies the termination present when the processor is in the reset state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Reset Drive: The Reset Drive column in the table specifies the active drive on the signal when the processor is in the reset state.

- Hibernate Termination: The Hiber Term column in the table specifies the termination present when the processor is in the hibernate state. The abbreviations used in this column are wk (weak keeper, weakly retains previous value driven on the pin), pu (pull-up), or pd (pull-down).

- Hibernate Drive: The Hiber Drive column in the table specifies the active drive on the signal when the processor is in the hibernate state.

- Power Domain: The Power Domain column in the table specifies the power supply domain in which the signal resides.

- Description and Notes: The Description and Notes column in the table identifies any special requirements or characteristics for the signal. If no special requirements are listed the signal may be left unconnected if it is not used. Also, for multiplexed general-purpose I/O pins, this column identifies the functions available on the pin.

If an external pull-up or pull-down resistor is required for any signal, 100  $k\Omega$  is the maximum value that can be used unless otherwise noted.

Note that for Port A, Port B, and Port C (PA\_00 to PC\_14), when <u>SYS\_HWRST</u> is low, these pads are three-state. After <u>SYS\_HWRST</u> is released, but before code execution begins, these pins are internally pulled up. Subsequently, the state depends on the input enable and output enable which are controlled by software.

Software control of internal pull-ups works according to the following settings in the PADS\_PCFG0 register. When PADS\_PCFG0 = 0: For PA\_15:PA\_00, PB\_15:PB\_00, and PC\_14:PC\_00, the internal pull-up is enabled when both the input enable and output enable of a particular pin are deasserted. When PADS\_PCFG0 = 1: For PA\_15:PA\_00, PB\_15:PB\_00, and PC\_14:PC\_00, the internal pull-up is enabled as long as the output enable of a particular pin is deasserted.

There are some exceptions to this scheme:

- Internal pull-ups are always disabled if MSI mode is selected for that signal.

- The following signals enabled the internal pull-down when the output enable is de-asserted: <u>SMC0\_AMS[1:0]</u>, <u>SMC0\_ARE</u>, <u>SMC0\_AWE</u>, <u>SMC0\_AOE</u>, <u>SMC0\_ARDY</u>, <u>SPI0\_SEL[6:1]</u>, <u>SPI1\_SEL[4:1]</u>, and <u>SPI2\_SEL[3:1]</u>.

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                 |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|------------------------------------------|

| DMC0_A00    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 0<br>Notes: No notes. |

| DMC0_A01    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 1<br>Notes: No notes. |

| DMC0_A02    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 2<br>Notes: No notes. |

| DMC0_A03    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 3<br>Notes: No notes. |

| DMC0_A04    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 4<br>Notes: No notes. |

| DMC0_A05    | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC         | Desc: DMC0 Address 5<br>Notes: No notes. |

#### Table 15. ADSP-BF70x Designer Quick Reference

|             |      | Driver   | Int   | Reset | Reset | Hiber | Hiber | Power     | Description                                         |

|-------------|------|----------|-------|-------|-------|-------|-------|-----------|-----------------------------------------------------|

| Signal Name | Туре | Туре     | Term  | Term  | Drive | Term  | Drive | Domain    | and Notes                                           |

| DMC0_A06    | 1/0  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 6                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A07    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 7                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A08    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 8                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A09    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 9                                |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A10    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 10                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A11    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 11                               |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A12    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 12                               |

| DMC0 442    | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_A13    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Address 13                               |

|             | 1/0  | <b>D</b> |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_BA0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 0<br>Notes: No notes. |

| DMC0_BA1    | I/O  | В        | nono  | nono  | nono  | nono  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 1                     |

| DIVICO_BAT  | 1/0  | D        | none  | none  | none  | none  | none  | VDD_DIVIC | Notes: No notes.                                    |

| DMC0_BA2    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Bank Address Input 2                     |

| DIVICO_DIV2 | 1/0  |          | none  | none  | none  | none  | none  | VDD_DIMC  | Notes: For LPDDR, leave unconnected.                |

| DMC0_CAS    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Column Address Strobe                    |

| bineo_erio  | ., 0 |          | lione | none  | none  | none  | none  |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | с        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock                                    |

|             |      | -        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CK     | I/O  | С        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock (complement)                       |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CKE    | I/O  | В        | none  | none  | L     | none  | L     | VDD_DMC   | Desc: DMC0 Clock enable                             |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_CS0    | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Chip Select 0                            |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ00   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 0                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ01   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 1                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ02   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 2                                   |

|             | 1/0  |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ03   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 3                                   |

|             | 1/0  | D        |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ04   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 4<br>Notes: No notes.               |

| DMC0_DQ05   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 5                                   |

|             | "0   |          | none  | none  | none  | none  | lione |           | Notes: No notes.                                    |

| DMC0_DQ06   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 6                                   |

| 2           |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| DMC0_DQ07   | I/O  | В        | none  | none  | none  | none  | none  | VDD_DMC   | Desc: DMC0 Data 7                                   |

|             |      |          |       |       |       |       |       |           | Notes: No notes.                                    |

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_12       | 1/0  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 1 (HSYNC)   CAN1<br>Receive   SPORT0 Channel A Frame Sync<br> SMC0 Output Enable  SYS Power<br>Saving Mode Wakeup 4   TM0 Alternate<br>Capture Input 6<br>Notes: If hibernate mode is used one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down. |

| PA_13       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 2 (VSYNC)   CAN1<br>Transmit   SPORT0 Channel A Clock  <br>SMC0 Read Enable   CNT0 Count Zero<br>Marker<br>Notes: No notes.                                                                                                                                                                                                                               |

| PA_14       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Clock   SPI1 Slave Select<br>Output 4   SPORT0 Channel A Data 0  <br>SMC0 Write Enable   TM0 Alternate<br>Clock 5<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                 |

| PA_15       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Frame Sync 3 (FIELD)   SPT0<br>Channel A Transmit Data Valid   SPT0<br>Channel B Transmit Data Valid   SMC0<br>Memory Select 0   CNT0 Count Up and<br>Direction<br>Notes: May require a pull-up if used as<br>an SMC memory select. Check the data<br>sheet requirements of the IC it connects<br>to.                                                                |

| PB_00       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 7   SPT1 Channel B Clock<br>  SPI0 Clock   SMC0 Data 7   TM0<br>Alternate Clock 3<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.                                                                                                                                                                                       |

| PB_01       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 6   SPT1 Channel B<br>Frame Sync   SPI0 Master In, Slave Out  <br>SMC0 Data 6   TM0 Alternate Capture<br>Input 1<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.                                                                                                                                                                         |

| PB_02       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 5   SPT1 Channel B Data<br>0   SPI0 Master Out, Slave In   SMC0 Data<br>5<br>Notes: No notes.                                                                                                                                                                                                                                                                   |

| PB_03       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: PPI0 Data 4   SPT1 Channel B Data<br>1   SPI0 Data 2   SMC0 Data 4<br>Notes: No notes.                                                                                                                                                                                                                                                                                    |

|             |      | Driver | Int       | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                                                                                                                                                                                                                                                                               |

|-------------|------|--------|-----------|-------|-------|-------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Туре   | Type Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                                                                                                                                                                                                                                                                 |

| PB_12       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Master Out, Slave In   TRACE0<br>Trace Data 3   SMC0 Data 12   SYS Power<br>Saving Mode Wakeup 2                                                                                                                                                                                                                                               |

|             |      |        |           |       |       |       |       |         | Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down.                                                                                                                                                          |

| PB_13       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 2   UART1 Request to<br>Send   TRACE0 Trace Data 2   SMC0 Data<br>13<br>Notes: No notes.                                                                                                                                                                                                                                                  |

| PB_14       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 3   UART1 Clear to Send<br>  TRACE0 Trace Data 1   SMC0 Data 14<br>Notes: No notes.                                                                                                                                                                                                                                                       |

| PB_15       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Slave Select Output 1  <br>TRACE0 Trace Data 0   SMC0 Data 15  <br>SPI2 Slave Select Input<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                  |

| PC_00       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Transmit   SPT0 Channel A<br>Data 1   PPI0 Data 15<br>Notes: No notes.                                                                                                                                                                                                                                                                        |

| PC_01       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Receive   SPT0 Channel B<br>Data 1   PPI0 Data 14   SMC0 Address 9  <br>TM0 Alternate Capture Input 4<br>Notes: No notes.                                                                                                                                                                                                                     |

| PC_02       | Ι/Ο  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: UART0 Request to Send   CAN0<br>Receive   PPI0 Data 13   SMC0 Address<br>10   SYS Power Saving Mode Wakeup 3  <br>TM0 Alternate Capture Input 5<br>Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down. |

| PC_03       | I/O  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Clear to Send   CANO<br>Transmit   PPIO Data 12   SMCO Address<br>11   TMO Alternate Capture Input 0<br>Notes: No notes.                                                                                                                                                                                                                      |

| PC_04       | Ι/Ο  | A      | none      | none  | none  | none  | none  | VDD_EXT | Desc: SPT0 Channel B Clock   SPI0 Clock<br>  MSI0 Data 1   SMC0 Address 12   TM0<br>Alternate Clock 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                    |

| Signal Name | Туре | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                      |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_05       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Frame Sync   TM0<br>Timer 3   MSI0 Command<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                              |

| PC_06       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Data 0   SPl0<br>Master In, Slave Out   MSI0 Data 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                     |

| PC_07       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel B Frame Sync   SPI0<br>Master Out, Slave In   MSI0 Data 2   TM0<br>Alternate Capture Input 2<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                              |

| PC_08       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Data 0   SPI0 Data<br>2   MSI0 Data 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                   |

| PC_09       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT0 Channel A Clock   SPI0 Data<br>3   MSI0 Clock   TM0 Alternate Clock 2<br>Notes: No notes.                                                                                                                                                                                          |

| PC_10       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Clock   MSI0 Data<br>4   SPI1 Slave Select Output 3   TM0<br>Alternate Clock 1<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used. |

| PC_11       | I/O  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Frame Sync   MSI0<br>Data 5   SPI0 Slave Select Output 3<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details. SPI slave select outputs require<br>a pull-up when used.                       |

| PC_12       | Ι/Ο  | A              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SPT1 Channel B Data 0   MSI0 Data<br>6<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                 |

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                             |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TWI0_SCL    | 1/0  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Clock<br>Notes: Open drain, requires external<br>pull up. Consult version 2.1 of the I2C<br>specification for the proper resistor<br>value. If TWI is not used, connect to<br>ground.                              |

| TWI0_SDA    | I/O  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Data<br>Notes: Open drain, requires external<br>pull up. Consult version 2.1 of the I2C<br>specification for the proper resistor<br>value. If TWI is not used, connect to<br>ground.                               |

| USB0_CLKIN  | a    | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Clock/Crystal Input<br>Notes: If USB is not used, connect to<br>ground. Active during reset                                                                                                                               |

| USB0_DM     | I/O  | F              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Data –<br>Notes: Pull low if not using USB. For<br>complete documentation of hibernate<br>behavior when USB is used, see the USB<br>chapter in the HRM.                                                                   |

| USB0_DP     | I/O  | F              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Data +<br>Notes: Pull low if not using USB. For<br>complete documentation of hibernate<br>behavior when USB is used, see the USB<br>chapter in the HRM.                                                                   |

| USB0_ID     | I/O  | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 OTG ID<br>Notes: If USB is not used connect to<br>ground. When USB is being used, the<br>internal pull-up that is present during<br>hibernate is programmable. See the<br>USB chapter in the HRM. Active during<br>reset. |

| USB0_VBC    | I/O  | E              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 VBUS Control<br>Notes: If USB is not, used pull low.                                                                                                                                                                      |

| USB0_VBUS   | I/O  | G              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Bus Voltage<br>Notes: If USB is not used, connect to<br>ground.                                                                                                                                                           |

| USB0_XTAL   | а    | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Crystal<br>Notes: No notes.                                                                                                                                                                                               |

| VDD_DMC     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for DMC<br>Notes: If the DMC is not used, connect<br>to VDD_INT.                                                                                                                                                           |

| VDD_EXT     | S    | na             | none        | none          | none           | none          | none           | na              | Desc: External VDD<br>Notes: Must be powered.                                                                                                                                                                                        |

| VDD_HADC    | S    | na             | none        | none          | none           | none          | none           | na              | Desc: VDD for HADC<br>Notes: If HADC is not used, connect to<br>ground.                                                                                                                                                              |

| VDD_INT     | s    | na             | none        | none          | none           | none          | none           | na              | Desc: Internal VDD<br>Notes: Must be powered.                                                                                                                                                                                        |

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                     |                                                                       | Test Conditions/Comments                                                                                                   | Min T                       | ур Мах | Unit |

|-----------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|------|

| V <sub>OH</sub> <sup>1</sup>                  | High Level Output Voltage                                             | $V_{DD_{EXT}} = 1.7 \text{ V}, I_{OH} = -1.0 \text{ mA}$                                                                   | $0.8 \times V_{DD_{EXT}}$   |        | V    |

| V <sub>OH</sub> <sup>1</sup>                  | High Level Output Voltage                                             | $V_{DD EXT} = 3.13 \text{ V}, I_{OH} = -2.0 \text{ mA}$                                                                    | $0.9 \times V_{DD EXT}$     |        | V    |

| V <sub>OH_DDR2</sub> <sup>2</sup>             | High Level Output Voltage, DDR2,                                      | $V_{DD_{DMC}} = 1.70 \text{ V}, I_{OH} = -7.1 \text{ mA}$                                                                  | V <sub>DD_DMC</sub> - 0.320 |        | V    |

|                                               | Programmed Impedance = 34 $\Omega$                                    |                                                                                                                            |                             |        |      |

| V <sub>OH_DDR2</sub> <sup>2</sup>             | High Level Output Voltage, DDR2,                                      | $V_{DD_DMC} = 1.70 \text{ V}, I_{OH} = -5.8 \text{ mA}$                                                                    | $V_{DD_DMC} - 0.320$        |        | V    |

|                                               | Programmed Impedance = 40 $\Omega$                                    |                                                                                                                            |                             |        |      |

| V <sub>OH_DDR2</sub> <sup>2</sup>             | High Level Output Voltage, DDR2,                                      | $V_{DD_DMC} = 1.70 \text{ V}, I_{OH} = -4.1 \text{ mA}$                                                                    | V <sub>DD_DMC</sub> – 0.320 |        | V    |

|                                               | Programmed Impedance = $50 \Omega$                                    |                                                                                                                            |                             |        |      |

| V <sub>OH_DDR2</sub> <sup>2</sup>             | High Level Output Voltage, DDR2,                                      | $V_{DD_{DMC}} = 1.70 \text{ V}, I_{OH} = -3.4 \text{ mA}$                                                                  | $V_{DD_DMC} - 0.320$        |        | V    |

| <u>, , , , , , , , , , , , , , , , , , , </u> | Programmed Impedance = $60 \Omega$                                    |                                                                                                                            |                             |        |      |

| V <sub>OH_LPDDR</sub> <sup>2</sup>            | High Level Output Voltage, LPDDR                                      | $V_{DD_{DMC}} = 1.70 \text{ V}, I_{OH} = -2.0 \text{ mA}$                                                                  | V <sub>DD_DMC</sub> - 0.320 |        | V    |

| V <sub>OL</sub> <sup>3</sup>                  | Low Level Output Voltage                                              | $V_{DD_{EXT}} = 1.7 \text{ V}, I_{OL} = 1.0 \text{ mA}$                                                                    |                             | 0.400  | V    |

| V <sub>OL</sub> <sup>3</sup>                  | Low Level Output Voltage                                              | $V_{DD_{EXT}} = 3.13 \text{ V}, I_{OL} = 2.0 \text{ mA}$                                                                   |                             | 0.400  | V    |

| V <sub>OL_DDR2</sub> <sup>2</sup>             | Low Level Output Voltage, DDR2,                                       | $V_{DD_DMC} = 1.70 \text{ V}, I_{OL} = 7.1 \text{ mA}$                                                                     |                             | 0.320  | V    |

|                                               | Programmed Impedance = $34 \Omega$                                    |                                                                                                                            |                             |        |      |

| V <sub>OL_DDR2</sub> <sup>2</sup>             | Low Level Output Voltage, DDR2,                                       | $V_{DD_{DMC}} = 1.70 \text{ V}, I_{OL} = 5.8 \text{ mA}$                                                                   |                             | 0.320  | V    |

| 2                                             | Programmed Impedance = $40 \Omega$                                    |                                                                                                                            |                             | 0.220  |      |

| V <sub>OL_DDR2</sub> <sup>2</sup>             | Low Level Output Voltage, DDR2,                                       | $V_{DD_DMC} = 1.70 \text{ V}, I_{OL} = 4.1 \text{ mA}$                                                                     |                             | 0.320  | V    |

| <u>V</u> 2                                    | Programmed Impedance = $50 \Omega$                                    | 1/2 - 170 / 1 - 24 m A                                                                                                     |                             | 0.320  | v    |

| V <sub>OL_DDR2</sub> <sup>2</sup>             | Low Level Output Voltage, DDR2,<br>Programmed Impedance = 60 $\Omega$ | $V_{DD_DMC} = 1.70 \text{ V}, I_{OL} = 3.4 \text{ mA}$                                                                     |                             | 0.320  | v    |

| V <sub>OL_LPDDR</sub> <sup>2</sup>            | Low Level Output Voltage, LPDDR                                       | $V_{DD DMC} = 1.70 \text{ V}, I_{OL} = 2.0 \text{ mA}$                                                                     |                             | 0.320  | V    |

| VOL_LPDDR                                     | High Level Input Current                                              | $V_{DD_{DMC}} = 1.70$ V, $V_{OL} = 2.0$ M/A                                                                                |                             | 10     | μA   |

| ΙΗ                                            | High Level Input Current                                              | $v_{DD_{EXT}} = 3.47 \text{ V}, v_{DD_{DMC}} = 1.9 \text{ V},$<br>$V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$ |                             | 10     | μΑ   |

| I <sub>IH_DMC0_VREF</sub> 5                   | High Level Input Current                                              | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                                 |                             | 1      | μA   |

| "IH_DMC0_VREF                                 | ngh Level input current                                               | $V_{DD_{USB}} = 3.47 \text{ V}, V_{DD_{DMC}} = 3.47 \text{ V}$                                                             |                             | •      | μ    |

| I <sub>IH_PD</sub> <sup>6</sup>               | High Level Input Current with Pull-                                   | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                                 |                             | 100    | μA   |

|                                               | down Resistor                                                         | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                                   |                             |        | r.   |

| R <sub>PD</sub> <sup>6</sup>                  | Internal Pull-down Resistance                                         | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                                 | 57                          | 130    | kΩ   |

|                                               |                                                                       | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                                   |                             |        |      |

| I <sub>IL</sub> <sup>7</sup>                  | Low Level Input Current                                               | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$                                                             |                             | 10     | μΑ   |

|                                               |                                                                       | $V_{DD_{-}USB} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$                                                                     |                             |        |      |

| IIL_DMC0_VREF                                 | Low Level Input Current                                               | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$                                                             |                             | 1      | μA   |

|                                               |                                                                       | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$                                                                      |                             |        |      |

| I <sub>IL_PU</sub> <sup>8</sup>               | Low Level Input Current with Pull-up                                  |                                                                                                                            |                             | 100    | μΑ   |

|                                               | Resistor                                                              | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$                                                                      |                             |        |      |

| R <sub>PU</sub> <sup>8</sup>                  | Internal Pull-up Resistance                                           | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$                                                             | 53                          | 129    | kΩ   |

| 0                                             |                                                                       | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$                                                                      |                             |        |      |

| I <sub>IH_USB0</sub> 9                        | High Level Input Current                                              | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$                                                             |                             | 10     | μΑ   |

| 9                                             |                                                                       | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                                   |                             | 10     |      |

| I <sub>IL_USB0</sub> 9                        | Low Level Input Current                                               | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$<br>$V_{DD USB} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$      |                             | 10     | μA   |

| I <sub>OZH</sub> <sup>10</sup>                | Three-State Leakage Current                                           | $V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$<br>$V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$    |                             | 10     | μA   |

| OZH                                           | Three-State Leakage Current                                           | $V_{DD_{EXT}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$<br>$V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$ |                             | 10     | μΑ   |

| I <sub>OZH</sub> <sup>11</sup>                | Three-State Leakage Current                                           | $V_{DD_{DSB}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$                                                             |                             | 10     | μA   |

| •UZH                                          | mee State Leakage Current                                             | $V_{DD_{LSB}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.9 \text{ V},$<br>$V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 1.9 \text{ V}$  |                             | 10     | μΛ   |

| I <sub>OZL</sub> <sup>12</sup>                | Three-State Leakage Current                                           | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                                 |                             | 10     | μA   |

| ·02L                                          | ee state Leanage current                                              | $V_{DD_{USB}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.5 \text{ V},$<br>$V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$    |                             | 10     | P''' |

| I <sub>OZH_PD</sub> <sup>13</sup>             | Three-State Leakage Current                                           | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                                 |                             | 100    | μA   |

| ·02n_ru                                       |                                                                       | $V_{DD_{USB}} = 3.47 \text{ V}, V_{DD_{DMC}} = 1.5 \text{ V},$<br>$V_{DD_{USB}} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$ |                             | 100    | P    |

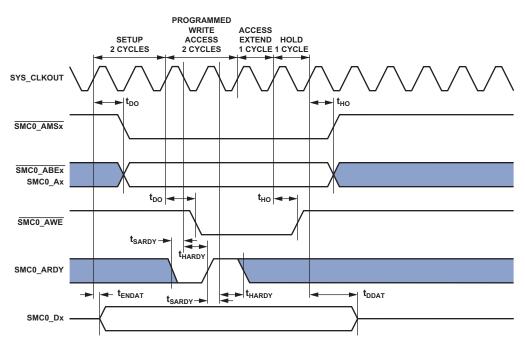

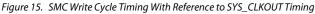

#### SMC Write Cycle Timing With Reference to SYS\_CLKOUT

The following SMC specifications with respect to SYS\_CLKOUT are given to accommodate the connection of the SMC to programmable logic devices. These specifications assume that SYS\_CLKOUT is outputting a buffered version of SCLK0 by setting CGU\_CLKOUTSEL.CLKOUTSEL = 0x3. However, SCLK0 must not run faster than the maximum  $f_{OCLK}$  specification. For this example WST = 0x2, WAT = 0x2, and WHT = 0x1.

#### Table 36. SMC Write Cycle Timing With Reference to SYS\_CLKOUT (BxMODE = b#00)

|                    |                                            | 1.8V/ | V <sub>DD_EXT</sub><br>1.8 V/3.3 V Nominal |      |

|--------------------|--------------------------------------------|-------|--------------------------------------------|------|

| Parameter          | Parameter                                  |       |                                            | Unit |

| Timing Requ        | lirements                                  |       |                                            |      |

| t <sub>SARDY</sub> | SMC0_ARDY Setup Before SYS_CLKOUT          | 14.4  |                                            | ns   |

| t <sub>HARDY</sub> | SMC0_ARDY Hold After SYS_CLKOUT            | 0.7   |                                            | ns   |

| Switching Cl       | haracteristics                             |       |                                            |      |

| t <sub>DDAT</sub>  | SMC0_Dx Disable After SYS_CLKOUT           |       | 7                                          | ns   |

| t <sub>ENDAT</sub> | SMC0_Dx Enable After SYS_CLKOUT            | -2.5  |                                            | ns   |

| t <sub>DO</sub>    | Output Delay After SYS_CLKOUT <sup>1</sup> |       | 7                                          | ns   |

| t <sub>HO</sub>    | Output Hold After SYS_CLKOUT <sup>1</sup>  | -2.5  |                                            | ns   |

$^{1} Output \ pins/balls \ include \ \overline{SMC0\_AMSx}, \ \overline{SMC0\_ABEx}, \ SMC0\_Ax, \ SMC0\_Dx, \ \overline{SMC0\_AOE}, \ and \ \overline{SMC0\_AWE}.$

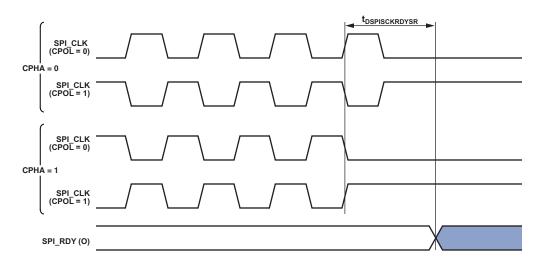

### Debug Interface (JTAG Emulation Port) Timing

Table 48 and Figure 26 provide I/O timing, related to the debug interface (JTAG emulator port).

#### Table 48. JTAG Port Timing

|                    |                                                                | 1.  | V <sub>DD_EXT</sub><br>.8V Nominal | 3.  | V <sub>DD_EXT</sub><br>3 V Nominal |                  |

|--------------------|----------------------------------------------------------------|-----|------------------------------------|-----|------------------------------------|------------------|

| Parameter          |                                                                | Min | Max                                | Min | Max                                | Unit             |

| Timing Requi       | rements                                                        |     |                                    |     |                                    |                  |

| t <sub>TCK</sub>   | JTG_TCK Period                                                 | 20  |                                    | 20  |                                    | ns               |

| t <sub>STAP</sub>  | JTG_TDI, JTG_TMS Setup Before JTG_TCK High                     | 5   |                                    | 4   |                                    | ns               |

| t <sub>HTAP</sub>  | JTG_TDI, JTG_TMS Hold After JTG_TCK High                       | 4   |                                    | 4   |                                    | ns               |

| t <sub>ssys</sub>  | System Inputs Setup Before JTG_TCK High <sup>1</sup>           | 4   |                                    | 4   |                                    | ns               |

| t <sub>HSYS</sub>  | System Inputs Hold After JTG_TCK High <sup>1</sup>             | 4   |                                    | 4   |                                    | ns               |

| t <sub>TRSTW</sub> | JTG_TRST Pulse Width (Measured in JTG_TCK Cycles) <sup>2</sup> | 4   |                                    | 4   |                                    | t <sub>TCK</sub> |

| Switching Ch       | aracteristics                                                  |     |                                    |     |                                    |                  |

| t <sub>DTDO</sub>  | JTG_TDO Delay From JTG_TCK Low                                 |     | 16.5                               |     | 14.5                               | ns               |

| t <sub>DSYS</sub>  | System Outputs Delay After JTG_TCK Low <sup>3</sup>            |     | 18                                 |     | 16.5                               | ns               |

| t <sub>DTMS</sub>  | TMS Delay After TCK High in SWD Mode                           | 3.5 | 16.5                               | 3.5 | 14.5                               | ns               |

<sup>1</sup> System inputs = DMC0\_DQxx, DMC0\_LDQS, <u>DMC0\_LDQS</u>, DMC0\_UDQS, <u>DMC0\_UDQS</u>, PA\_xx, PB\_xx, PC\_xx, SYS\_BMODEx, <u>SYS\_HWRST</u>, <u>SYS\_FAULT</u>, <u>SYS\_NMI</u>, TWI0\_SCL, TWI0\_SDA, and SYS\_EXTWAKE.

<sup>2</sup> 50 MHz maximum.

<sup>3</sup> System outputs = DMC0\_Axx, DMC0\_BAx, DMC0\_CAS, DMC0\_CK, DMC0\_CK, DMC0\_CKE, DMC0\_CS0, DMC0\_DQxx, DMC0\_LDM, DMC0\_LDQS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_WE, PA\_xx, PB\_xx, PC\_xx, SYS\_CLKOUT, SYS\_FAULT, SYS\_RESOUT, and SYS\_NMI.

Figure 26. JTAG Port Timing

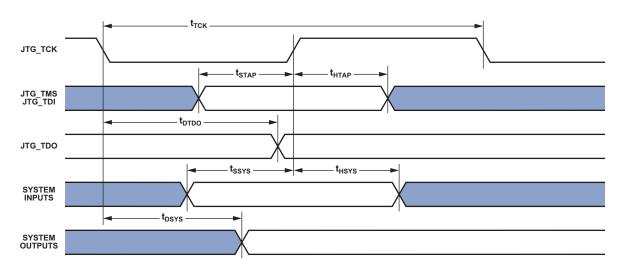

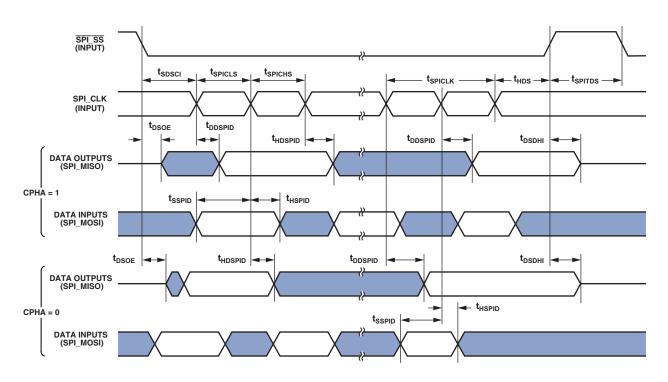

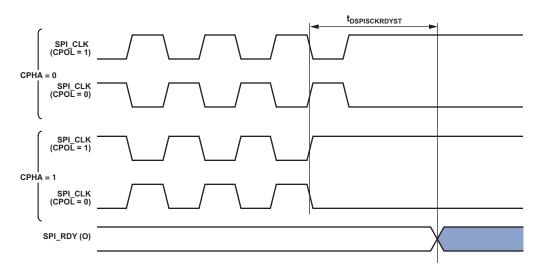

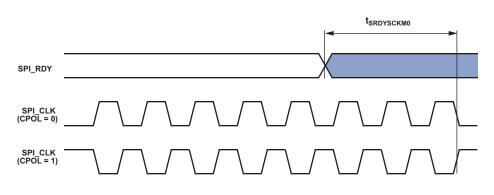

#### Serial Peripheral Interface (SPI) Port—Master Timing

Table 54 and Figure 31 describe serial peripheral interface (SPI) port master operations.

When internally generated, the programmed SPI clock ( $f_{SPICLKPROG}$ ) frequency in MHz is set by the following equation where BAUD is a field in the SPI\_CLK register that can be set from 0 to 65,535:

$$f_{SPICLKPROG} = \frac{f_{SCLK0}}{(BAUD+1)}$$

$$t_{SPICLKPROG} = \frac{1}{f_{SPICLKPROG}}$$

Note that:

- In dual mode data transmit, the SPI\_MISO signal is also an output.

- In quad mode data transmit, the SPI\_MISO, SPI\_D2, and SPI\_D3 signals are also outputs.

- In dual mode data receive, the SPI\_MOSI signal is also an input.

- In quad mode data receive, the SPI\_MOSI, SPI\_D2, and SPI\_D3 signals are also inputs.

- To add additional frame delays, see the documentation for the SPI\_DLY register in the hardware reference manual.

#### Table 54. Serial Peripheral Interface (SPI) Port-Master Timing

|                      |                                                        | V <sub>DD_EX</sub><br>1.8V Non                        |     | V <sub>DD_EXT</sub><br>3.3 V Nominal                  |     |      |

|----------------------|--------------------------------------------------------|-------------------------------------------------------|-----|-------------------------------------------------------|-----|------|

| Parameter            |                                                        | Min                                                   | Max | Min                                                   | Max | Unit |

| Timing Requ          | irements                                               |                                                       |     |                                                       |     |      |

| t <sub>sspidm</sub>  | Data Input Valid to SPI_CLK Edge (Data Input<br>Setup) | 6.5                                                   |     | 5.5                                                   |     | ns   |

| t <sub>hspidm</sub>  | SPI_CLK Sampling Edge to Data Input Invalid            | 1                                                     |     | 1                                                     |     | ns   |

| Switching Ch         | aracteristics                                          |                                                       |     |                                                       |     |      |

| t <sub>sdscim</sub>  | SPI_SEL low to First SPI_CLK Edge                      | $0.5 \times t_{SCLK0} - 2.5$                          |     | $0.5 	imes t_{SCLK0} - 1.5$                           |     | ns   |

| t <sub>spichm</sub>  | SPI_CLK High Period <sup>1</sup>                       | $0.5 	imes t_{SPICLKPROG} - 1.5$                      |     | $0.5 	imes t_{SPICLKPROG} - 1.5$                      |     | ns   |

| t <sub>spiclm</sub>  | SPI_CLK Low Period <sup>1</sup>                        | $0.5 \times t_{SPICLKPROG} - 1.5$                     |     | $0.5 \times t_{SPICLKPROG} - 1.5$                     |     | ns   |

| t <sub>spiclk</sub>  | SPI_CLK Period <sup>1</sup>                            | t <sub>spiclkprog</sub> – 1.5                         |     | t <sub>SPICLKPROG</sub> – 1.5                         |     | ns   |