Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------|

| Туре                    | Blackfin+                                                                                 |

| Interface               | CAN, DSPI, EBI/EMI, I <sup>2</sup> C, PPI, QSPI, SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                    |

| Non-Volatile Memory     | ROM (512kB)                                                                               |

| On-Chip RAM             | 1MB                                                                                       |

| Voltage - I/O           | 1.8V, 3.3V                                                                                |

| Voltage - Core          | 1.10V                                                                                     |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                             |

| Package / Case          | 184-LFBGA, CSPBGA                                                                         |

| Supplier Device Package | 184-CSPBGA (12x12)                                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf707kbcz-3                      |

|                         |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The program sequencer controls the flow of instruction execution, including instruction alignment and decoding. For program flow control, the sequencer supports PC relative and indirect conditional jumps (with dynamic branch prediction), and subroutine calls. Hardware supports zero-overhead looping. The architecture is fully interlocked, meaning that the programmer need not manage the pipeline when executing instructions with data dependencies.

The address arithmetic unit provides two addresses for simultaneous dual fetches from memory. It contains a multiported register file consisting of four sets of 32-bit index, modify, length, and base registers (for circular buffering), and eight additional 32-bit pointer registers (for C-style indexed stack manipulation).

The Blackfin processor supports a modified Harvard architecture in combination with a hierarchical memory structure. Level 1 (L1) memories are those that typically operate at the full processor speed with little or no latency. At the L1 level, the instruction memory holds instructions only. The data memory holds data, and a dedicated scratchpad data memory stores stack and local variable information.

In addition, multiple L1 memory blocks are provided, offering a configurable mix of SRAM and cache. The memory management unit (MMU) provides memory protection for individual tasks that may be operating on the core and can protect system registers from unintended access.

The architecture provides three modes of operation: user mode, supervisor mode, and emulation mode. User mode has restricted access to certain system resources, thus providing a protected software environment, while supervisor mode has unrestricted access to the system and core resources.

#### INSTRUCTION SET DESCRIPTION

The Blackfin processor instruction set has been optimized so that 16-bit opcodes represent the most frequently used instructions, resulting in excellent compiled code density. Complex DSP instructions are encoded into 32-bit opcodes, representing fully featured multifunction instructions. The Blackfin processor supports a limited multi-issue capability, where a 32-bit instruction can be issued in parallel with two 16-bit instructions, allowing the programmer to use many of the core resources in a single instruction cycle.

The Blackfin processor family assembly language instruction set employs an algebraic syntax designed for ease of coding and readability. The instructions have been specifically tuned to provide a flexible, densely encoded instruction set that compiles to a very small final memory size. The instruction set also provides fully featured multifunction instructions that allow the programmer to use many of the processor core resources in a single instruction. Coupled with many features more often seen on microcontrollers, this instruction set is very efficient when compiling C and C++ source code. In addition, the architecture supports both user (algorithm/application code) and supervisor (O/S kernel, device drivers, debuggers, ISRs) modes of operation, allowing multiple levels of access to core processor resources. The assembly language, which takes advantage of the processor's unique architecture, offers the following advantages:

- Seamlessly integrated DSP/MCU features are optimized for both 8-bit and 16-bit operations.

- A multi-issue load/store modified-Harvard architecture, which supports two 16-bit MAC or four 8-bit ALU + two load/store + two pointer updates per cycle.

- All registers, I/O, and memory are mapped into a unified 4G byte memory space, providing a simplified programming model.

- Control of all asynchronous and synchronous events to the processor is handled by two subsystems: the core event controller (CEC) and the system event controller (SEC).

- Microcontroller features, such as arbitrary bit and bit-field manipulation, insertion, and extraction; integer operations on 8-, 16-, and 32-bit data-types; and separate user and supervisor stack pointers.

- Code density enhancements, which include intermixing of 16-bit and 32-bit instructions (no mode switching, no code segregation). Frequently used instructions are encoded in 16 bits.

#### PROCESSOR INFRASTRUCTURE

The following sections provide information on the primary infrastructure components of the ADSP-BF70x processor.

#### **DMA Controllers**

The processor uses direct memory access (DMA) to transfer data within memory spaces or between a memory space and a peripheral. The processor can specify data transfer operations and return to normal processing while the fully integrated DMA controller carries out the data transfers independent of processor activity.

DMA transfers can occur between memory and a peripheral or between one memory and another memory. Each memory-tomemory DMA stream uses two channels, where one channel is the source channel, and the second is the destination channel.

All DMAs can transport data to and from all on-chip and offchip memories. Programs can use two types of DMA transfers, descriptor-based or register-based. Register-based DMA allows the processor to directly program DMA control registers to initiate a DMA transfer. On completion, the control registers may be automatically updated with their original setup values for continuous transfer. Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. Descriptor-based DMA transfers allow multiple DMA sequences to be chained together and a DMA channel can be programmed to automatically set up and start another DMA transfer after the current sequence completes.

The DMA controller supports the following DMA operations.

- A single linear buffer that stops on completion.

- A linear buffer with negative, positive, or zero stride length.

- A circular, auto-refreshing buffer that interrupts when each buffer becomes full.

#### **General-Purpose Timers**

There is one GP timer unit, and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TIMER\_TMRx pins, an external TIMER\_CLK input pin, or to the internal SCLK0.

These timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The GP timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals through the TRU (for instance, to signal a fault). Each timer may also be started and/or stopped by any TRU master without core intervention.

#### **Core Timer**

The processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### Watchdog Timer

The core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, through generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts down to zero from the programmed value. This protects the system from remaining in an unknown state where software that would normally reset the timer has stopped running due to an external noise condition or software error.

After a reset, software can determine if the watchdog was the source of the hardware reset by interrogating a status bit in its timer control register that is set only upon a watchdog-generated reset.

#### Serial Ports (SPORTs)

Two synchronous serial ports (comprised of four half-SPORTs) provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices' audio codecs, ADCs, and DACs. Each half-SPORT is made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial port data can be automatically transferred to and from on-chip memory/external memory through dedicated DMA channels. Each of the serial ports can work in conjunction with another serial port to provide TDM support. In this configuration, one SPORT provides two transmit signals while the other SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in six modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- Left-justified mode

- Right-justified mode

#### **General-Purpose Counters**

A 32-bit counter is provided that can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is either controlled by a levelsensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumbwheel devices. All three pins have a programmable debouncing circuit.

Internal signals forwarded to a GP timer enable this timer to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmed count values are exceeded.

#### Parallel Peripheral Interface (PPI)

The processor provides a parallel peripheral interface (PPI) that supports data widths up to 18 bits. The PPI supports direct connection to TFT LCD panels, parallel analog-to-digital and digital-to-analog converters, video encoders and decoders, image sensor modules, and other general-purpose peripherals.

The following features are supported in the PPI module:

- Programmable data length: 8 bits, 10 bits, 12 bits, 14 bits, 16 bits, and 18 bits per clock.

- Various framed, non-framed, and general-purpose operating modes. Frame syncs can be generated internally or can be supplied by an external device.

- ITU-656 status word error detection and correction for ITU-656 receive modes and ITU-656 preamble and status word decode.

- Optional packing and unpacking of data to/from 32 bits from/to 8 bits, 16 bits and 24 bits. If packing/unpacking is enabled, endianness can be configured to change the order of packing/unpacking of bytes/words.

- RGB888 can be converted to RGB666 or RGB565 for transmit modes.

- Various de-interleaving/interleaving modes for receiving/transmitting 4:2:2 YCrCb data.

- Configurable LCD data enable (DEN) output available on Frame Sync 3.

### **ADSP-BF70x DETAILED SIGNAL DESCRIPTIONS**

Table 6 provides a detailed description of each pin.

#### Table 6. ADSP-BF70x Detailed Signal Descriptions

| Port Name | Direction | Description                                                                                                                                                                                                                                                              |  |  |  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CAN_RX    | Input     | Receive. Typically an external CAN transceiver's RX output.                                                                                                                                                                                                              |  |  |  |

| CAN_TX    | Output    | Transmit. Typically an external CAN transceiver's TX input.                                                                                                                                                                                                              |  |  |  |

| CNT_DG    | Input     | <b>Count Down and Gate.</b> Depending on the mode of operation this input acts either as a count down signal or a gate signal Count Down - This input causes the GP counter to decrement Gate - Stops the GP counter from incrementing or decrementing.                  |  |  |  |

| CNT_UD    | Input     | <b>Count Up and Direction.</b> Depending on the mode of operation this input acts either as a count up signal or a direction signal Count Up - This input causes the GP counter to increment Direction - Selects whether the GP counter is incrementing or decrementing. |  |  |  |

| CNT_ZM    | Input     | <b>Count Zero Marker.</b> Input that connects to the zero marker output of a rotary device or detects the pressing of a pushbutton.                                                                                                                                      |  |  |  |

| DMC_Ann   | Output    | Address n. Address bus.                                                                                                                                                                                                                                                  |  |  |  |

| DMC_BAn   | Output    | Bank Address Input n. Defines which internal bank an ACTIVATE, READ, WRITE, or PRECHARGE                                                                                                                                                                                 |  |  |  |

| Dime_DAin | output    | command is being applied to on the dynamic memory. Also defines which mode registers (MR, EMR, EMR2, and/or EMR3) are loaded during the LOAD MODE REGISTER command.                                                                                                      |  |  |  |

| DMC_CAS   | Output    | <b>Column Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the CAS input of dynamic memory.                                                                                    |  |  |  |

| DMC_CK    | Output    | Clock. Outputs DCLK to external dynamic memory.                                                                                                                                                                                                                          |  |  |  |

| DMC_CK    | Output    | Clock (Complement). Complement of DMC_CK.                                                                                                                                                                                                                                |  |  |  |

| DMC_CKE   | Output    | Clock enable. Active high clock enables. Connects to the dynamic memory's CKE input.                                                                                                                                                                                     |  |  |  |

| DMC_CSn   | Output    | Chip Select n. Commands are recognized by the memory only when this signal is asserted.                                                                                                                                                                                  |  |  |  |

| DMC_DQnn  | I/O       | Data n. Bidirectional Data bus.                                                                                                                                                                                                                                          |  |  |  |

| DMC_LDM   | Output    | <b>Data Mask for Lower Byte.</b> Mask for DMC_DQ07:DMC_DQ00 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |  |  |  |

| DMC_LDQS  | I/O       | <b>Data Strobe for Lower Byte.</b> DMC_DQ07:DMC_DQ00 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |  |  |  |

| DMC_LDQS  | I/O       | Data Strobe for Lower Byte (complement). Complement of LDQS. Not used in single-ended mode.                                                                                                                                                                              |  |  |  |

| DMC_ODT   | Output    | <b>On-die termination.</b> Enables dynamic memory termination resistances when driven high (assuming the memory is properly configured). ODT is enabled/disabled regardless of read or write commands.                                                                   |  |  |  |

| DMC_RAS   | Output    | <b>Row Address Strobe.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the RAS input of dynamic memory.                                                                                       |  |  |  |

| DMC_UDM   | Output    | <b>Data Mask for Upper Byte.</b> Mask for DMC_DQ15:DMC_DQ08 write data when driven high. Sampled on both edges of the data strobe by the dynamic memory.                                                                                                                 |  |  |  |

| DMC_UDQS  | I/O       | <b>Data Strobe for Upper Byte.</b> DMC_DQ15:DMC_DQ08 data strobe. Output with Write Data. Input with Read Data. May be single-ended or differential depending on register settings.                                                                                      |  |  |  |

| DMC_UDQS  | I/O       | Data Strobe for Upper Byte (complement). Complement of UDQSb. Not used in single-ended mode.                                                                                                                                                                             |  |  |  |

| DMC_VREF  | Input     | Voltage Reference. Connect to half of the VDD_DMC voltage.                                                                                                                                                                                                               |  |  |  |

| DMC_WE    | Output    | <b>Write Enable.</b> Defines the operation for external dynamic memory to perform in conjunction with other DMC command signals. Connect to the $\overline{WE}$ input of dynamic memory.                                                                                 |  |  |  |

| PPI_CLK   | I/O       | <b>Clock.</b> Input in external clock mode, output in internal clock mode.                                                                                                                                                                                               |  |  |  |

| PPI_Dnn   | I/O       | Data n. Bidirectional data bus.                                                                                                                                                                                                                                          |  |  |  |

| PPI_FS1   | I/O       | Frame Sync 1 (HSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |  |  |  |

| PPI_FS2   | I/O       | Frame Sync 2 (VSYNC). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |  |  |  |

| PPI_FS3   | I/O       | Frame Sync 3 (FIELD). Behavior depends on EPPI mode. See the EPPI HRM chapter for more details.                                                                                                                                                                          |  |  |  |

| HADC_VINn | Input     | <b>Analog Input at channel n.</b> Analog voltage inputs for digital conversion.                                                                                                                                                                                          |  |  |  |

#### Multiplexed Multiplexed Multiplexed Multiplexed Multiplexed Signal Name **Function 0 Function 1 Function 2** Function 3 Function Input Tap PC\_00 UART1\_TX SPT0\_AD1 PPI0\_D15 PC\_01 UART1\_RX SPT0\_BD1 PPI0\_D14 SMC0\_A09 TM0\_ACI4 PC\_02 UARTO\_RTS CAN0\_RX PPI0\_D13 SMC0\_A10 TM0\_ACI5/SYS\_ WAKE3 UARTO\_CTS PC\_03 CAN0\_TX PPI0\_D12 SMC0\_A11 TM0\_ACI0 PC\_04 SPT0\_BCLK SPI0\_CLK MSI0\_D1 SMC0\_A12 TM0\_ACLK0 SPT0\_AFS TM0\_TMR3 MSI0\_CMD PC\_05 PC\_06 SPT0\_BD0 SPI0\_MISO MSI0\_D3 SPI0\_MOSI MSI0\_D2 PC\_07 SPT0\_BFS TM0\_ACI2 MSI0\_D0 PC\_08 SPT0\_AD0 SPI0\_D2 SPI0\_D3 MSI0\_CLK PC\_09 SPT0\_ACLK TM0\_ACLK2 SPI1\_SEL3 PC\_10 SPT1\_BCLK MSI0\_D4 TM0\_ACLK1 SPI0\_SEL3 PC\_11 SPT1\_BFS MSI0\_D5 PC\_12 SPT1\_BD0 MSI0\_D6 PC\_13 SPT1\_BD1 MSI0\_D7 MSI0\_INT PC\_14 SPT1\_BTDV

#### Table 10. Signal Multiplexing for Port C

| Signal Name                      | Description                                              | Port   | Pin Name       |

|----------------------------------|----------------------------------------------------------|--------|----------------|

| SMC0_D11                         | SMC0 Data 11                                             | В      | PB_11          |

| SMC0_D12                         | SMC0 Data 12                                             | В      | PB_12          |

| SMC0_D13                         | SMC0 Data 13                                             | В      | PB_13          |

| SMC0_D14                         | SMC0 Data 14                                             | В      | PB_14          |

| SMC0_D15                         | SMC0 Data 15                                             | В      | PB_15          |

| SPI0_CLK                         | SPI0 Clock                                               | В      | PB_00          |

| SPI0_CLK                         | SPI0 Clock                                               | С      | PC_04          |

| SPI0_D2                          | SPI0 Data 2                                              | В      | PB_03          |

| SPI0_D2                          | SPI0 Data 2                                              | С      | PC_08          |

| SPI0_D3                          | SPI0 Data 3                                              | В      | PB_07          |

| SPI0_D3                          | SPI0 Data 3                                              | С      | PC_09          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                | В      | PB_01          |

| SPI0_MISO                        | SPI0 Master In, Slave Out                                | С      | PC_06          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                | В      | PB_02          |

| SPI0_MOSI                        | SPI0 Master Out, Slave In                                | С      | PC_07          |

| SPI0_RDY                         | SPI0 Ready                                               | А      | PA_06          |

| SPI0_SEL1                        | SPI0 Slave Select Output 1                               | А      | PA_05          |

| SPI0_SEL2                        | SPI0 Slave Select Output 2                               | А      | PA_06          |

| SPI0_SEL4                        | SPI0 Slave Select Output 4                               | В      | PB_04          |

| SPI0_SEL5                        | SPI0 Slave Select Output 5                               | В      | PB_05          |

| SPI0_SEL6                        | SPI0 Slave Select Output 6                               | В      | PB_06          |

| SPI0_SS                          | SPI0 Slave Select Input                                  | А      | PA_05          |

| SPI1_CLK                         | SPI1 Clock                                               | А      | PA_00          |

| SPI1_MISO                        | SPI1 Master In, Slave Out                                | А      | PA_01          |

| SPI1_MOSI                        | SPI1 Master Out, Slave In                                | А      | PA_02          |

|                                  | SPI1 Ready                                               | А      | <br>PA_03      |

| SPI1_SEL1                        | SPI1 Slave Select Output 1                               | А      | <br>PA_04      |

|                                  | SPI1 Slave Select Output 2                               | А      | <br>PA_03      |

|                                  | SPI1 Slave Select Output 3                               | с      | <br>PC_10      |

| SPI1_SEL4                        | SPI1 Slave Select Output 4                               | A      | PA_14          |

| SPI1_SS                          | SPI1 Slave Select Input                                  | A      | PA_04          |

| SPI2_CLK                         | SPI2 Clock                                               | В      | PB_10          |

| SPI2_D2                          | SPI2 Data 2                                              | В      | PB_13          |

| SPI2_D3                          | SPI2 Data 3                                              | В      | PB_14          |

| SPI2_MISO                        | SPI2 Master In, Slave Out                                | В      | PB_11          |

| SPI2_MOSI                        | SPI2 Master Out, Slave In                                | В      | PB_12          |

| SPI2_RDY                         | SPI2 Ready                                               | A      | PA_04          |

| SPI2_SEL1                        | SPI2 Slave Select Output 1                               | В      | PB_15          |

| SPI2_SEL2                        | SPI2 Slave Select Output 1                               | В      | PB_08          |

| SPI2_SEL3                        | SPI2 Slave Select Output 2<br>SPI2 Slave Select Output 3 | B      | PB_09          |

| SPI2_SELS                        | SPI2 Slave Select Output                                 | B      | PB_15          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                   | A      | PA_13          |

| SPT0_ACLK                        | SPORTO Channel A Clock                                   | C      | PC_09          |

| SPT0_ACLK<br>SPT0_AD0            | SPORTO Channel A Data 0                                  |        | PC_09<br>PA_14 |

|                                  |                                                          | A      |                |

|                                  |                                                          |        |                |

| SPT0_AD0<br>SPT0_AD0<br>SPT0_AD1 | SPORTO Channel A Data 0<br>SPORTO Channel A Data 1       | C<br>C | PC_08<br>PC_00 |

Table 11. ADSP-BF70x 12 mm × 12 mm 88-Lead LFCSP (QFN) Signal Descriptions (Continued)

|             |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|--------|------|-------|-------|-------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Туре   | Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                                                                                                                                                                                                                                                                                          |

| PB_04       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 3   SPT0 Channel B Clock<br>  SPI0 Slave Select Output 4   SMC0 Data<br>3   TM0 Alternate Clock 6<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                               |

| PB_05       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 2   SPT0 Channel B Data<br>0   SPI0 Slave Select Output 5   SMC0<br>Data 2<br>Notes: SPI slave select outputs require a                                                                                                                                                                                                                                            |

|             |      |        |      |       |       |       |       |         | pull-up when used.                                                                                                                                                                                                                                                                                                                                                                 |

| PB_06       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 1   SPT0 Channel B<br>Frame Sync   SPI0 Slave Select Output 6<br>  SMC0 Data 1   TM0 Clock                                                                                                                                                                                                                                                                         |

|             |      |        |      |       |       |       |       |         | Notes: SPI slave select outputs require a pull-up when used.                                                                                                                                                                                                                                                                                                                       |

| PB_07       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: PPI0 Data 0   SPT0 Channel B Data<br>1   SPI0 Data 3   SMC0 Data 0   SYS Power<br>Saving Mode Wakeup 0                                                                                                                                                                                                                                                                       |

|             |      |        |      |       |       |       |       |         | Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down.                                                                                                                                                                                   |

| PB_08       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Transmit   PPI0 Data 16  <br>SPI2 Slave Select Output 2   SMC0 Data<br>8   SYS Power Saving Mode Wakeup 1<br>Notes: SPI slave select outputs require a<br>pull-up when used. If hibernate mode is<br>used, one of the following must be true<br>during hibernate. Either this pin must<br>be actively driven by another IC, or it<br>must have a pull-up or pull-down. |

| PB_09       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Receive   PPI0 Data 17  <br>SPI2 Slave Select Output 3   SMC0 Data<br>9   TM0 Alternate Capture Input 3<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                             |

| PB_10       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Clock   TRACE0 Trace Clock  <br>SMC0 Data 10   TM0 Alternate Clock 4<br>Notes: SPI clock requires a pull-down<br>when controlling most SPI flash<br>devices.                                                                                                                                                                                                            |

| PB_11       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Master In, Slave Out   TRACE0<br>Trace Data 4   SMC0 Data 11<br>Notes: Pull-up required for SPI_MISO if<br>SPI master boot is used.                                                                                                                                                                                                                                     |

#### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

|             |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                                                                                                                                                                                                                                                                               |

|-------------|------|--------|------|-------|-------|-------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Туре   | Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                                                                                                                                                                                                                                                                 |

| PB_12       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Master Out, Slave In   TRACE0<br>Trace Data 3   SMC0 Data 12   SYS Power<br>Saving Mode Wakeup 2                                                                                                                                                                                                                                               |

|             |      |        |      |       |       |       |       |         | Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down.                                                                                                                                                          |

| PB_13       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 2   UART1 Request to<br>Send   TRACE0 Trace Data 2   SMC0 Data<br>13<br>Notes: No notes.                                                                                                                                                                                                                                                  |

| PB_14       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Data 3   UART1 Clear to Send<br>  TRACE0 Trace Data 1   SMC0 Data 14<br>Notes: No notes.                                                                                                                                                                                                                                                       |

| PB_15       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPI2 Slave Select Output 1  <br>TRACE0 Trace Data 0   SMC0 Data 15  <br>SPI2 Slave Select Input<br>Notes: SPI slave select outputs require a<br>pull-up when used.                                                                                                                                                                                  |

| PC_00       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Transmit   SPT0 Channel A<br>Data 1   PPI0 Data 15<br>Notes: No notes.                                                                                                                                                                                                                                                                        |

| PC_01       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART1 Receive   SPT0 Channel B<br>Data 1   PPI0 Data 14   SMC0 Address 9  <br>TM0 Alternate Capture Input 4<br>Notes: No notes.                                                                                                                                                                                                                     |

| PC_02       | Ι/Ο  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UART0 Request to Send   CAN0<br>Receive   PPI0 Data 13   SMC0 Address<br>10   SYS Power Saving Mode Wakeup 3  <br>TM0 Alternate Capture Input 5<br>Notes: If hibernate mode is used, one of<br>the following must be true during<br>hibernate. Either this pin must be<br>actively driven by another IC, or it must<br>have a pull-up or pull-down. |

| PC_03       | I/O  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: UARTO Clear to Send   CANO<br>Transmit   PPIO Data 12   SMCO Address<br>11   TMO Alternate Capture Input 0<br>Notes: No notes.                                                                                                                                                                                                                      |

| PC_04       | Ι/Ο  | A      | none | none  | none  | none  | none  | VDD_EXT | Desc: SPT0 Channel B Clock   SPI0 Clock<br>  MSI0 Data 1   SMC0 Address 12   TM0<br>Alternate Clock 0<br>Notes: An external pull-up may be<br>required for MSI modes, see the MSI<br>chapter in the hardware reference for<br>details.                                                                                                                    |

### Table 15. ADSP-BF70x Designer Quick Reference (Continued)

| TWI_DT Setting      | V <sub>DD_EXT</sub> Nominal | V <sub>BUSTWI</sub> Min | V <sub>BUSTWI</sub> Nominal | V <sub>BUSTWI</sub> Max | Unit |

|---------------------|-----------------------------|-------------------------|-----------------------------|-------------------------|------|

| TWI000 <sup>1</sup> | 3.30                        | 3.13                    | 3.30                        | 3.47                    | V    |

| TWI001              | 1.80                        | 1.70                    | 1.80                        | 1.90                    | V    |

| TWI011              | 1.80                        | 3.13                    | 3.30                        | 3.47                    | V    |

| TWI100              | 3.30                        | 4.75                    | 5.00                        | 5.25                    | V    |

| Table 16. | TWI | _VSEL | Selections and | V <sub>DD</sub> | EXT/VBUSTWI |

|-----------|-----|-------|----------------|-----------------|-------------|

|-----------|-----|-------|----------------|-----------------|-------------|

<sup>1</sup>Designs must comply with the V<sub>DD\_EXT</sub> and V<sub>BUSTWI</sub> voltages specified for the default TWI\_DT setting for correct JTAG boundary scan operation during reset.

#### **Clock Related Operating Conditions**

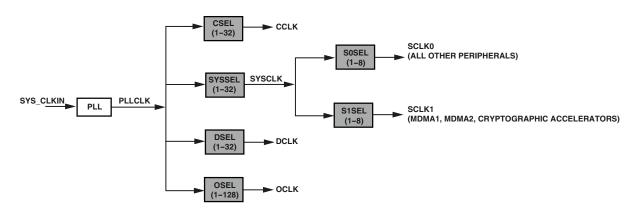

Table 17 and Table 18 describe the core clock, system clock, and peripheral clock timing requirements. The data presented in the tables applies to all speed grades (found in the Ordering Guide) except where expressly noted. Figure 6 provides a graphical representation of the various clocks and their available divider values.

Table 17. Core and System Clock Operating Conditions

| Param                      | eter                          | <b>Ratio Restriction</b>                  | PLLCLK Restriction     | Min | Max        | Unit |

|----------------------------|-------------------------------|-------------------------------------------|------------------------|-----|------------|------|

| $\mathbf{f}_{CCLK}$        | Core Clock Frequency          | $f_{CCLK} \ge f_{SYSCLK}$                 | PLLCLK = 800           |     | 400        | MHz  |

| $\mathbf{f}_{CCLK}$        | Core Clock Frequency          | $f_{CCLK} \geq f_{SYSCLK}$                | $600 \le PLLCLK < 800$ |     | 390        | MHz  |

| $\mathbf{f}_{CCLK}$        | Core Clock Frequency          | $f_{CCLK} \geq f_{SYSCLK}$                | $380 \le PLLCLK < 600$ |     | 380        | MHz  |

| $\mathbf{f}_{CCLK}$        | Core Clock Frequency          | $f_{CCLK} \geq f_{SYSCLK}$                | 230.2 ≤ PLLCLK < 380   |     | PLLCLK     | MHz  |

| <b>f</b> <sub>SYSCLK</sub> | SYSCLK Frequency <sup>1</sup> |                                           | PLLCLK = 800           | 60  | 200        | MHz  |

| <b>f</b> <sub>SYSCLK</sub> | SYSCLK Frequency <sup>1</sup> |                                           | $600 \le PLLCLK < 800$ | 60  | 195        | MHz  |

| <b>f</b> <sub>SYSCLK</sub> | SYSCLK Frequency <sup>1</sup> |                                           | 380 ≤ PLLCLK < 600     | 60  | 190        | MHz  |

| <b>f</b> <sub>SYSCLK</sub> | SYSCLK Frequency <sup>1</sup> |                                           | 230.2 ≤ PLLCLK < 380   | 60  | PLLCLK ÷ 2 | MHz  |

| f <sub>SCLK0</sub>         | SCLK0 Frequency <sup>1</sup>  | $f_{\text{SYSCLK}} \geq f_{\text{SCLK0}}$ |                        | 30  | 100        | MHz  |

| <b>f</b> <sub>SCLK1</sub>  | SCLK1 Frequency               | $f_{\text{SYSCLK}} \geq f_{\text{SCLK1}}$ |                        |     | 200        | MHz  |

| $\mathbf{f}_{DCLK}$        | DDR2 Clock Frequency          | $f_{\text{SYSCLK}} \geq f_{\text{DCLK}}$  |                        | 125 | 200        | MHz  |

| $\mathbf{f}_{DCLK}$        | LPDDR Clock Frequency         | $f_{\text{SYSCLK}} \geq f_{\text{DCLK}}$  |                        | 10  | 200        | MHz  |

<sup>1</sup> The minimum frequency for SYSCLK and SCLK0 applies only when the USB is used.

#### Table 18. Peripheral Clock Operating Conditions

| Parameter                      |                                                                       | Restriction                                  | Min | Тур | Мах | Unit |

|--------------------------------|-----------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>OCLK</sub>              | Output Clock Frequency                                                |                                              |     |     | 50  | MHz  |

| f <sub>sys_clkoutj</sub>       | SYS_CLKOUT Period Jitter <sup>1, 2</sup>                              |                                              |     | ±2  |     | %    |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKPROG</sub>   | Programmed PPI Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>PCLKEXT</sub>    | External PPI Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{PCLKEXT}} \leq f_{\text{SCLK0}}$   |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Transmitting Data and Frame Sync            |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKPROG</sub> | Programmed SPT Clock When Receiving Data or Frame Sync                |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock When Receiving Data and Frame Sync <sup>3, 4</sup> | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPTCLKEXT</sub>  | External SPT Clock Transmitting Data or Frame Sync <sup>3, 4</sup>    | $f_{\text{SPTCLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Transmitting Data                           |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKPROG</sub> | Programmed SPI Clock When Receiving Data                              |                                              |     |     | 50  | MHz  |

| <b>f</b> <sub>SPICLKEXT</sub>  | External SPI Clock When Receiving Data <sup>3, 4</sup>                | $f_{SPICLKEXT} \leq f_{SCLK0}$               |     |     | 50  | MHz  |

| <b>f</b> <sub>spiclkext</sub>  | External SPI Clock When Transmitting Data <sup>3, 4</sup>             | $f_{\text{SPICLKEXT}} \leq f_{\text{SCLK0}}$ |     |     | 50  | MHz  |

| f <sub>MSICLKPROG</sub>        | Programmed MSI Clock                                                  |                                              |     |     | 50  | MHz  |

<sup>1</sup>SYS\_CLKOUT jitter is dependent on the application system design including pin switching activity, board layout, and the jitter characteristics of the SYS\_CLKIN source. Due to the dependency on these factors the measured jitter may be higher or lower than this typical specification for each end application.

<sup>2</sup> The value in the Typ field is the percentage of the SYS\_CLKOUT period.

<sup>3</sup> The maximum achievable frequency for any peripheral in external clock mode is dependent on being able to meet the setup and hold times in the ac timing specifications section for that peripheral. Pay particular attention to setup and hold times for VDD\_EXT = 1.8 V which may preclude the maximum frequency listed here.

$^4$  The peripheral external clock frequency must also be less than or equal to the  $f_{SCLK}$  that clocks the peripheral.

Figure 6. Clock Relationships and Divider Values

#### Table 19. Phase-Locked Loop Operating Conditions

| Parameter                  |                     | Min   | Max | Unit |

|----------------------------|---------------------|-------|-----|------|

| <b>f</b> <sub>PLLCLK</sub> | PLL Clock Frequency | 230.2 | 800 | MHz  |

| CGU_CTL.MSEL <sup>1</sup>  | PLL Multiplier      | 8     | 41  |      |

<sup>1</sup>The CGU\_CTL.MSEL setting must also be chosen to ensure that the f<sub>PLLCLK</sub> specification is not violated.

|         |       | Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |

|---------|-------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| (°C) رT | 1.045 | 1.050                          | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| -40     | 0.6   | 0.6                            | 0.7   | 0.7   | 0.7   | 0.8   | 0.8   | 0.8   | 0.9   | 0.9   | 0.9   | 1.0   | 1.0   |

| -20     | 1.1   | 1.1                            | 1.2   | 1.2   | 1.2   | 1.3   | 1.4   | 1.4   | 1.5   | 1.5   | 1.6   | 1.7   | 1.7   |

| 0       | 2.0   | 2.0                            | 2.1   | 2.2   | 2.3   | 2.4   | 2.5   | 2.5   | 2.6   | 2.7   | 2.8   | 3.0   | 3.0   |

| 25      | 4.3   | 4.3                            | 4.5   | 4.7   | 4.8   | 5.0   | 5.2   | 5.3   | 5.5   | 5.7   | 5.9   | 6.1   | 6.2   |

| 40      | 6.7   | 6.8                            | 7.0   | 7.3   | 7.5   | 7.8   | 8.0   | 8.3   | 8.6   | 8.8   | 9.1   | 9.4   | 9.6   |

| 55      | 10.3  | 10.5                           | 10.8  | 11.2  | 11.5  | 11.9  | 12.3  | 12.6  | 13.0  | 13.4  | 13.9  | 14.3  | 14.5  |

| 70      | 15.7  | 15.9                           | 16.4  | 16.8  | 17.4  | 17.9  | 18.4  | 18.9  | 19.5  | 20.1  | 20.7  | 21.3  | 21.6  |

| 85      | 23.3  | 23.6                           | 24.3  | 25.0  | 25.7  | 26.4  | 27.2  | 27.9  | 28.7  | 29.5  | 30.4  | 31.2  | 31.7  |

| 100     | 34.2  | 34.6                           | 35.5  | 36.5  | 37.5  | 38.5  | 39.5  | 40.6  | 41.7  | 42.8  | 43.9  | 45.1  | 45.7  |

| 105     | 38.7  | 39.2                           | 40.2  | 41.3  | 42.4  | 43.5  | 44.6  | 45.8  | 47.0  | 48.2  | 49.5  | 50.8  | 51.5  |

| 115     | 48.9  | 49.5                           | 50.7  | 52.0  | 53.4  | 54.7  | 56.0  | 57.5  | 59.0  | 60.5  | 62.0  | 63.6  | 64.4  |

| 125     | 61.5  | 62.1                           | 63.6  | 65.1  | 66.7  | 68.3  | 69.9  | 71.7  | 73.4  | 75.2  | 77.0  | 79.0  | 79.9  |

#### Table 21. Static Current—IDD\_DEEPSLEEP (mA)

#### Table 22. Activity Scaling Factors (ASF)

| I <sub>DDINT</sub> Power Vector | ASF  |

|---------------------------------|------|

| I <sub>DD-IDLE1</sub>           | 0.05 |

| I <sub>DD-IDLE2</sub>           | 0.05 |

| I <sub>DD-NOP1</sub>            | 0.56 |

| I <sub>DD-NOP2</sub>            | 0.59 |

| I <sub>DD-APP3</sub>            | 0.78 |

| I <sub>DD-APP1</sub>            | 0.79 |

| I <sub>DD-APP2</sub>            | 0.83 |

| I <sub>DD-TYP1</sub>            | 1.00 |

| I <sub>DD-TYP3</sub>            | 1.01 |

| I <sub>DD-TYP2</sub>            | 1.03 |

| I <sub>DD-HIGH1</sub>           | 1.39 |

| I <sub>DD-HIGH3</sub>           | 1.39 |

| I <sub>DD-HIGH2</sub>           | 1.54 |

| Table 23. | <b>CCLK Dynamic</b> | Current per core | (mA, with ASF = 1) |

|-----------|---------------------|------------------|--------------------|

|-----------|---------------------|------------------|--------------------|

|                         | Voltage (V <sub>DD_INT</sub> ) |       |       |       |       |       |       |       |       |       |       |       |       |

|-------------------------|--------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| f <sub>CCLK</sub> (MHz) | 1.045                          | 1.050 | 1.060 | 1.070 | 1.080 | 1.090 | 1.100 | 1.110 | 1.120 | 1.130 | 1.140 | 1.150 | 1.155 |

| 400                     | 66.7                           | 67.2  | 67.9  | 68.7  | 69.4  | 70.2  | 71.1  | 71.8  | 72.6  | 73.4  | 74.2  | 74.9  | 75.4  |

| 350                     | 58.6                           | 59.0  | 59.6  | 60.3  | 61.0  | 61.7  | 62.4  | 63.0  | 63.7  | 64.4  | 65.1  | 65.8  | 66.1  |

| 300                     | 50.2                           | 50.5  | 51.1  | 51.7  | 52.3  | 52.9  | 53.5  | 54.1  | 54.7  | 55.3  | 55.9  | 56.4  | 56.8  |

| 250                     | 42.1                           | 42.3  | 42.8  | 43.3  | 43.8  | 44.3  | 44.7  | 45.3  | 45.8  | 46.3  | 46.8  | 47.4  | 47.6  |

| 200                     | 33.7                           | 33.9  | 34.3  | 34.7  | 35.1  | 35.5  | 35.9  | 36.3  | 36.7  | 37.1  | 37.5  | 37.9  | 38.0  |

| 150                     | 25.4                           | 25.5  | 25.8  | 26.1  | 26.4  | 26.7  | 27.0  | 27.3  | 27.6  | 27.9  | 28.2  | 28.5  | 28.8  |

| 100                     | 17.0                           | 17.1  | 17.3  | 17.5  | 17.7  | 17.9  | 18.1  | 18.3  | 18.5  | 18.6  | 18.8  | 19.0  | 19.1  |

#### TIMING SPECIFICATIONS

Specifications are subject to change without notice.

#### **Clock and Reset Timing**

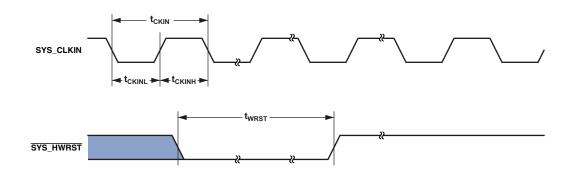

Table 29 and Figure 8 describe clock and reset operations related to the clock generation unit (CGU). Per the CCLK, SYSCLK, SCLK0, SCLK1, DCLK, and OCLK timing specifications in Table 17 on Page 51 and Table 18 on Page 52, combinations of SYS\_CLKIN and clock multipliers must not select clock rates in excess of the processor's maximum instruction rate.

#### Table 29. Clock and Reset Timing

|                          |                                                                         | 1.1                  | V <sub>DD_EXT</sub><br>3V Nominal | 3.:                  | V <sub>DD_EXT</sub><br>3V Nominal |      |

|--------------------------|-------------------------------------------------------------------------|----------------------|-----------------------------------|----------------------|-----------------------------------|------|

| Parameter                | r                                                                       | Min                  | Max                               | Min                  | Max                               | Unit |

| Timing Req               | uirement                                                                |                      |                                   |                      |                                   |      |

| f <sub>CKIN</sub>        | SYS_CLKIN Crystal Frequency (CGU_CTL.DF = 0) <sup>1, 2, 3</sup>         | 19.2                 | 35                                | 19.2                 | 50                                | MHz  |

| f <sub>CKIN</sub>        | SYS_CLKIN Crystal Frequency (CGU_CTL.DF = 1) <sup>1, 2, 3</sup>         | N/A                  | N/A                               | 38.4                 | 50                                | MHz  |

| f <sub>CKIN</sub>        | SYS_CLKIN External Source Frequency (CGU_CTL.DF = 0) <sup>1, 2, 3</sup> | 19.2                 | 60                                | 19.2                 | 60                                | MHz  |

| <b>f</b> <sub>CKIN</sub> | SYS_CLKIN External Source Frequency (CGU_CTL.DF = 1) <sup>1, 2, 3</sup> | 38.4                 | 60                                | 38.4                 | 60                                | MHz  |

| t <sub>CKINL</sub>       | SYS_CLKIN Low Pulse <sup>1</sup>                                        | 8.33                 |                                   | 8.33                 |                                   | ns   |

| t <sub>CKINH</sub>       | SYS_CLKIN High Pulse <sup>1</sup>                                       | 8.33                 |                                   | 8.33                 |                                   | ns   |

| t <sub>WRST</sub>        | SYS_HWRST Asserted Pulse Width Low <sup>4</sup>                         | $11 \times t_{CKIN}$ |                                   | $11 \times t_{CKIN}$ |                                   | ns   |

<sup>1</sup> Applies to PLL bypass mode and PLL nonbypass mode.

<sup>2</sup> The  $t_{CKIN}$  period (see Figure 8) equals  $1/f_{CKIN}$ .

$^{3}$  Combinations of the CLKIN frequency and the PLL clock multiplier must not exceed the allowed f<sub>PLLCLK</sub> setting discussed in Table 19.

<sup>4</sup> Applies after power-up sequence is complete. See Table 30 and Figure 9 for power-up reset timing.

Figure 8. Clock and Reset Timing

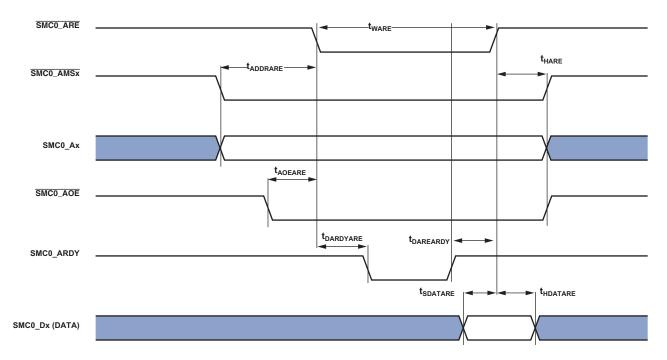

Figure 10. Asynchronous Read

#### Asynchronous Flash Write

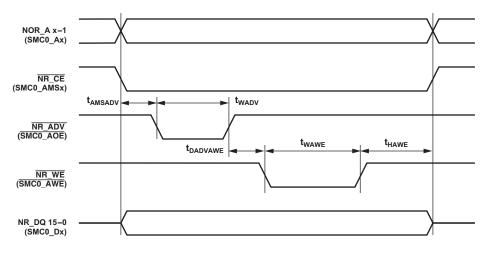

Table 37 and Figure 16 show asynchronous flash memory write timing, related to the static memory controller (SMC).

#### Table 37. Asynchronous Flash Write

|                      |                                                           | 1.8\                              | V <sub>DD_EXT</sub><br>//3.3 V Nominal |      |  |

|----------------------|-----------------------------------------------------------|-----------------------------------|----------------------------------------|------|--|

| Parameter            |                                                           | Min                               | Max                                    | Unit |  |

| Switching C          | haracteristics                                            |                                   |                                        |      |  |

| t <sub>AMSADV</sub>  | SMC0_Ax/SMC0_AMSx Assertion Before ADV Low <sup>1</sup>   | $PREST \times t_{SCLK0}$          | - 2                                    | ns   |  |

| t <sub>DADVAWE</sub> | SMC0_AWE Low Delay From ADV High <sup>2</sup>             | $PREAT \times t_{SCLK0}$          | - 4                                    | ns   |  |

| t <sub>WADV</sub>    | NR_ADV Active Low Width <sup>3</sup>                      | $WST \times t_{SCLK0} -$          | 2                                      | ns   |  |

| t <sub>HAWE</sub>    | Output <sup>4</sup> Hold After SMC0_AWE High <sup>5</sup> | $WHT \times t_{SCLK0}$            |                                        | ns   |  |

| t <sub>wawe</sub> 6  | SMC0_AWE Active Low Width <sup>7</sup>                    | WAT $\times$ t <sub>SCLK0</sub> – | 2                                      | ns   |  |

<sup>1</sup> PREST value set using the SMC\_BxETIM.PREST bits.

<sup>2</sup> PREAT value set using the SMC\_BxETIM.PREAT bits.

<sup>3</sup>WST value set using the SMC\_BxTIM.WST bits.

<sup>4</sup>Output signals are DATA, SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_ABEx</u>.

$^5\,\rm WHT$  value set using the SMC\_BxTIM.WHT bits.

<sup>6</sup> SMC\_BxCTL.ARDYEN bit = 0.

$^7\,\rm WAT$  value set using the SMC\_BxTIM.WAT bits.

#### **All Accesses**

Table 38 describes timing that applies to all memory accesses, related to the static memory controller (SMC).

#### Table 38. All Accesses

|                                            | 1.4                          | V <sub>DD_EXT</sub><br>1.8 V Nominal |                           | V <sub>DD_EXT</sub><br>3.3 V Nominal |      |

|--------------------------------------------|------------------------------|--------------------------------------|---------------------------|--------------------------------------|------|

| Parameter                                  | Min                          | Max                                  | Min                       | Max                                  | Unit |

| Switching Characteristic                   |                              |                                      |                           |                                      |      |

| t <sub>TURN</sub> SMC0_AMSx Inactive Width | $(IT + TT) \times t_{SCLKO}$ | - 2                                  | $(IT + TT) \times t_{SC}$ | <sub>LK0</sub> – 2                   | ns   |

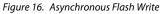

#### Table 51. Serial Ports—Enable and Three-State

|                    |                                                          | 1.8   | V <sub>DD_EXT</sub><br>SV Nominal | 3.3 | V <sub>DD_EXT</sub><br>SV Nominal |      |  |

|--------------------|----------------------------------------------------------|-------|-----------------------------------|-----|-----------------------------------|------|--|

| Paramete           | er                                                       | Min   | Max                               | Min | Max                               | Unit |  |

| Switching          | Characteristics                                          |       |                                   |     |                                   |      |  |

| t <sub>DDTEN</sub> | Data Enable from External Transmit SPT_CLK <sup>1</sup>  | 1     |                                   | 1   |                                   | ns   |  |

| t <sub>DDTTE</sub> | Data Disable from External Transmit SPT_CLK <sup>1</sup> |       | 14                                |     | 14                                | ns   |  |

| t <sub>DDTIN</sub> | Data Enable from Internal Transmit SPT_CLK <sup>1</sup>  | -1.12 |                                   | -1  |                                   | ns   |  |

| t <sub>DDTTI</sub> | Data Disable from Internal Transmit SPT_CLK <sup>1</sup> |       | 2.8                               |     | 2.8                               | ns   |  |

<sup>1</sup>Referenced to drive edge.

#### Serial Peripheral Interface (SPI) Port—Master Timing

Table 54 and Figure 31 describe serial peripheral interface (SPI) port master operations.

When internally generated, the programmed SPI clock ( $f_{SPICLKPROG}$ ) frequency in MHz is set by the following equation where BAUD is a field in the SPI\_CLK register that can be set from 0 to 65,535:

$$f_{SPICLKPROG} = \frac{f_{SCLK0}}{(BAUD+1)}$$

$$t_{SPICLKPROG} = \frac{1}{f_{SPICLKPROG}}$$

Note that:

- In dual mode data transmit, the SPI\_MISO signal is also an output.

- In quad mode data transmit, the SPI\_MISO, SPI\_D2, and SPI\_D3 signals are also outputs.

- In dual mode data receive, the SPI\_MOSI signal is also an input.

- In quad mode data receive, the SPI\_MOSI, SPI\_D2, and SPI\_D3 signals are also inputs.

- To add additional frame delays, see the documentation for the SPI\_DLY register in the hardware reference manual.

#### Table 54. Serial Peripheral Interface (SPI) Port-Master Timing

|                      |                                                        | V <sub>DD_EX</sub><br>1.8V Non                        |     | ۷ <sub>DD_</sub> ε)<br>3.3 V Nor                      |     |      |

|----------------------|--------------------------------------------------------|-------------------------------------------------------|-----|-------------------------------------------------------|-----|------|

| Parameter            |                                                        | Min                                                   | Max | Min                                                   | Max | Unit |

| Timing Requ          | irements                                               |                                                       |     |                                                       |     |      |

| t <sub>sspidm</sub>  | Data Input Valid to SPI_CLK Edge (Data Input<br>Setup) | 6.5                                                   |     | 5.5                                                   |     | ns   |

| t <sub>hspidm</sub>  | SPI_CLK Sampling Edge to Data Input Invalid            | 1                                                     |     | 1                                                     |     | ns   |

| Switching Ch         | aracteristics                                          |                                                       |     |                                                       |     |      |

| t <sub>sdscim</sub>  | SPI_SEL low to First SPI_CLK Edge                      | $0.5 \times t_{SCLK0} - 2.5$                          |     | $0.5 	imes t_{SCLK0} - 1.5$                           |     | ns   |

| t <sub>spichm</sub>  | SPI_CLK High Period <sup>1</sup>                       | $0.5 \times t_{SPICLKPROG} - 1.5$                     |     | $0.5 	imes t_{SPICLKPROG} - 1.5$                      |     | ns   |

| t <sub>spiclm</sub>  | SPI_CLK Low Period <sup>1</sup>                        | $0.5 \times t_{SPICLKPROG} - 1.5$                     |     | $0.5 \times t_{SPICLKPROG} - 1.5$                     |     | ns   |

| t <sub>spiclk</sub>  | SPI_CLK Period <sup>1</sup>                            | t <sub>spiclkprog</sub> – 1.5                         |     | t <sub>SPICLKPROG</sub> – 1.5                         |     | ns   |

| t <sub>HDSM</sub>    | Last SPI_CLK Edge to SPI_SEL High                      | $(0.5 \times t_{SCLK0}) - 2.5$                        |     | $(0.5 	imes t_{SCLK0}) - 1.5$                         |     | ns   |

| t <sub>spitdm</sub>  | Sequential Transfer Delay <sup>2</sup>                 | $(\text{STOP} \times \text{t}_{\text{SPICLK}}) - 1.5$ |     | $(\text{STOP} \times \text{t}_{\text{SPICLK}}) - 1.5$ |     | ns   |

| t <sub>DDSPIDM</sub> | SPI_CLK Edge to Data Out Valid (Data Out<br>Delay)     |                                                       | 2.5 |                                                       | 2   | ns   |

| t <sub>hdspidm</sub> | SPI_CLK Edge to Data Out Invalid (Data Out<br>Hold)    | -4.5                                                  |     | -3.5                                                  |     | ns   |

<sup>1</sup>See Table 18 on Page 52 in Clock Related Operating Conditions for details on the minimum period that may be programmed for t<sub>SPICLKPROG</sub>. <sup>2</sup>STOP value set using the SPI\_DLY.STOP bits.

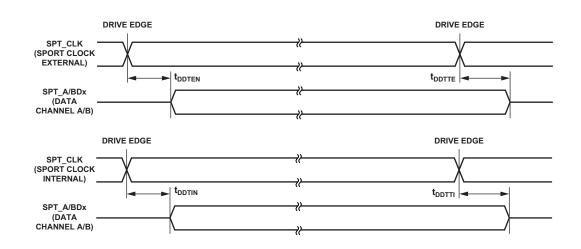

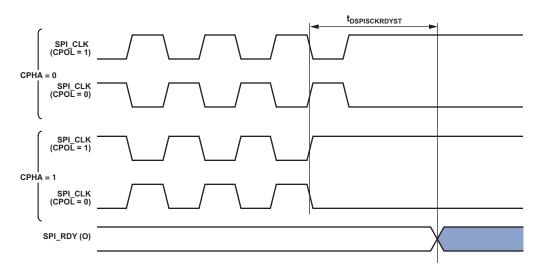

#### Serial Peripheral Interface (SPI) Port—SPI\_RDY Slave Timing

Table 56. SPI Port—SPI\_RDY Slave Timing

|                           |                                                                           |                                                  | D_EXT<br>V Nominal                  |      |

|---------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------|------|

| Parameter                 |                                                                           | Min                                              | Max                                 | Unit |

| Switching C               | haracteristics                                                            |                                                  |                                     |      |

| t <sub>dspisckrdysr</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Receive  | $2.5 	imes t_{SCLK0} + t_{HDSPID}$               | $3.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

| t <sub>dspisckrdyst</sub> | SPI_RDY De-assertion from Valid Input SPI_CLK Edge in Slave Mode Transmit | $3.5 	imes t_{\text{SCLK0}} + t_{\text{HDSPID}}$ | $4.5 \times t_{SCLK0} + t_{DDSPID}$ | ns   |

Figure 33. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Receive (FCCH = 0)

Figure 34. SPI\_RDY De-assertion from Valid Input SPI\_CLK Edge in Slave Mode Transmit (FCCH = 1)

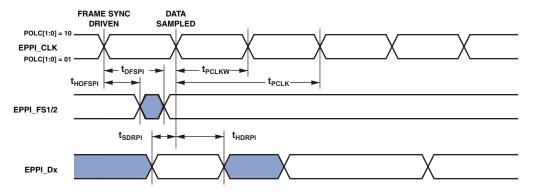

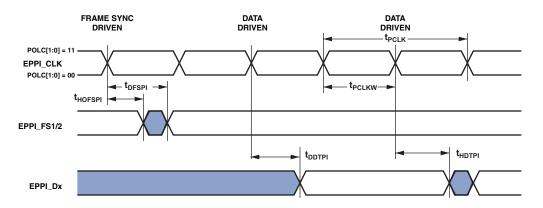

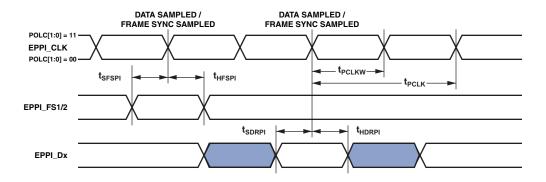

Figure 40. PPI Internal Clock GP Receive Mode with Internal Frame Sync Timing

Figure 42. PPI Internal Clock GP Receive Mode with External Frame Sync Timing

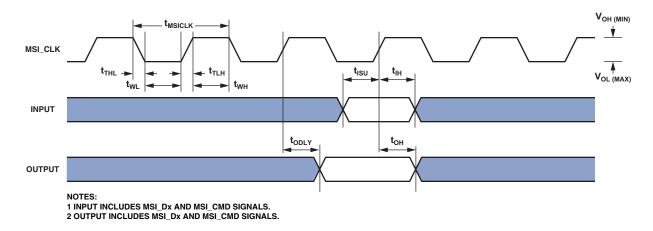

#### Mobile Storage Interface (MSI) Controller Timing

Table 64 and Figure 49 show I/O timing, related to the mobile storage interface (MSI).

The MSI timing depends on the period of the input clock that has been routed to the MSI peripheral ( $t_{MSICLKIN}$ ) by setting the MSI0\_UHS\_EXT register. See Table 63 for this information.

#### Table 63. t<sub>MSICLKIN</sub> Settings

| EXT_CLK_MUX_CTRL[31:30] | t <sub>MSICLKIN</sub>  |

|-------------------------|------------------------|

| 00                      | $t_{SCLK0} \times 2$   |

| 01                      | t <sub>SCLK0</sub>     |

| 10                      | t <sub>SCLK1</sub> × 3 |

$$t_{MSICLKIN} = \frac{1}{f_{MSICLKIN}}$$

$(f_{MSICLKPROG})$  frequency in MHz is set by the following equation where DIV0 is a field in the MSI\_CLKDIV register that can be set from 0 to 255. When DIV0 is set between 1 and 255, the following equation is used to determine  $f_{MSICLKPROG}$ :

$$f_{MSICLKPROG} = \frac{f_{MSICLKIN}}{DIV0 \times 2}$$

When DIV0 = 0,

$$f_{MSICLKPROG} = f_{MSICLKIN}$$

Also note the following:

$$t_{MSICLKPROG} = \frac{1}{f_{MSICLKPROG}}$$

#### Table 64. MSI Controller Timing

|                     |                                              |                                | <sup>DD_EXT</sup><br>Nominal      |                                | d_ext<br>Nominal                |      |

|---------------------|----------------------------------------------|--------------------------------|-----------------------------------|--------------------------------|---------------------------------|------|

| Param               | eter                                         | Min                            | Max                               | Min                            | Max                             | Unit |

| Timing              | Requirements                                 |                                |                                   |                                |                                 |      |

| t <sub>ISU</sub>    | Input Setup Time                             | 5.5                            |                                   | 4.7                            |                                 | ns   |

| t <sub>IH</sub>     | Input Hold Time                              | 2                              |                                   | 0.5                            |                                 | ns   |

| Switch              | ing Characteristics                          |                                |                                   |                                |                                 |      |

| t <sub>MSICLK</sub> | Clock Period Data Transfer Mode <sup>1</sup> | t <sub>MSICLKPROG</sub> – 1.5  |                                   | t <sub>MSICLKPROG</sub> – 1.5  |                                 | ns   |

| t <sub>WL</sub>     | Clock Low Time                               | 7                              |                                   | 7                              |                                 | ns   |

| $\mathbf{t}_{WH}$   | Clock High Time                              | 7                              |                                   | 7                              |                                 | ns   |

| t <sub>TLH</sub>    | Clock Rise Time                              |                                | 3                                 |                                | 3                               | ns   |

| $\mathbf{t}_{THL}$  | Clock Fall Time                              |                                | 3                                 |                                | 3                               | ns   |

| t <sub>ODLY</sub>   | Output Delay Time During Data Transfer Mode  |                                | $(0.5 \times t_{MSICLKIN}) + 3.2$ |                                | $(0.5 \times t_{MSICLKIN}) + 3$ | ns   |

| t <sub>OH</sub>     | Output Hold Time                             | $(0.5 	imes t_{MSICLKIN}) - 4$ |                                   | $(0.5 	imes t_{MSICLKIN}) - 3$ |                                 | ns   |

<sup>1</sup>See Table 18 on Page 52 in Clock Related Operating Conditions for details on the minimum period that may be programmed for t<sub>MSICLKPROG</sub>.

Figure 49. MSI Controller Timing

#### **ENVIRONMENTAL CONDITIONS**

To determine the junction temperature on the application printed circuit board, use the following equation:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C).

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{IT}$  = From Table 65 and Table 66.

$P_D$  = Power dissipation (see Total Internal Power Dissipation on Page 56 for the method to calculate  $P_D$ ).

Values of  $\theta_{JA}$  are provided for package comparison and printed circuit board design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_J$  by the equation:

$$T_J = T_A + (\theta_{JA} \times P_D)$$

where:

$T_A$  = Ambient temperature (°C).

Values of  $\theta_{JC}$  are provided for package comparison and printed circuit board design considerations when an external heat sink is required.

In Table 65 and Table 66, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6. The junction-to-case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board.

#### Table 65. Thermal Characteristics for CSP\_BGA

| Parameter            | Condition             | Typical | Unit |

|----------------------|-----------------------|---------|------|

| $\theta_{JA}$        | 0 linear m/s air flow | 28.7    | °C/W |

| $\theta_{JMA}$       | 1 linear m/s air flow | 26.2    | °C/W |

| $\theta_{JMA}$       | 2 linear m/s air flow | 25.2    | °C/W |

| $\theta_{\text{JC}}$ |                       | 10.1    | °C/W |

| $\Psi_{JT}$          | 0 linear m/s air flow | 0.24    | °C/W |

| $\Psi_{JT}$          | 1 linear m/s air flow | 0.40    | °C/W |

| $\Psi_{ m JT}$       | 2 linear m/s air flow | 0.51    | °C/W |

| Table 66. Thermal Characteristics for LFCSP (Q | )FN) | or LFCSP ( | Characteristics for | Thermal | Table 66. |

|------------------------------------------------|------|------------|---------------------|---------|-----------|

|------------------------------------------------|------|------------|---------------------|---------|-----------|

| Parameter            | Condition             | Typical | Unit |

|----------------------|-----------------------|---------|------|

| $\theta_{JA}$        | 0 linear m/s air flow | 22.9    | °C/W |

| $\theta_{JMA}$       | 1 linear m/s air flow | 17.9    | °C/W |

| $\theta_{JMA}$       | 2 linear m/s air flow | 16.4    | °C/W |

| $\theta_{\text{JC}}$ |                       | 2.26    | °C/W |

| $\Psi_{JT}$          | 0 linear m/s air flow | 0.14    | °C/W |

| $\Psi_{\text{JT}}$   | 1 linear m/s air flow | 0.27    | °C/W |

| $\Psi_{JT}$          | 2 linear m/s air flow | 0.30    | °C/W |