Welcome to **E-XFL.COM**

# **Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                            |  |

|-------------------------|------------------------------------------------------------|--|

| Product Status          | Active                                                     |  |

| Туре                    | Fixed Point                                                |  |

| Interface               | Host Interface, I <sup>2</sup> C, UART                     |  |

| Clock Rate              | 266MHz                                                     |  |

| Non-Volatile Memory     | ROM (8kB)                                                  |  |

| On-Chip RAM             | 400kB                                                      |  |

| Voltage - I/O           | 3.30V                                                      |  |

| Voltage - Core          | 1.20V                                                      |  |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                         |  |

| Mounting Type           | Surface Mount                                              |  |

| Package / Case          | 400-LFBGA                                                  |  |

| Supplier Device Package | 400-MAPBGA (17x17)                                         |  |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=msc7116vm1000 |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | Pin As   | signments4                                        | Figure 8.  | TDM Receive Signals                          | 28 |

|-----|----------|---------------------------------------------------|------------|----------------------------------------------|----|

|     | 1.1      | MAP-BGA Ball Layout Diagrams                      | Figure 9.  | TDM Transmit Signals                         | 29 |

|     |          | Signal List By Ball Location6                     | Figure 10. | Ethernet Receive Signal Timing               | 29 |

| 2   |          | cal Characteristics                               | Figure 11. |                                              |    |

|     | 2.1      | Maximum Ratings                                   | Figure 12. | Asynchronous Input Signal Timing             | 30 |

|     | 2.2      | Recommended Operating Conditions18                | Figure 13. |                                              |    |

|     |          | Thermal Characteristics                           | Figure 14. | Read Timing Diagram, Single Data Strobe      | 33 |

|     | 2.4      | DC Electrical Characteristics19                   |            | Read Timing Diagram, Double Data Strobe      |    |

|     | 2.5      | AC Timings                                        | Figure 16. | Write Timing Diagram, Single Data Strobe     | 34 |

| 3   |          | are Design Considerations41                       |            | Write Timing Diagram, Double Data Strobe     |    |

|     | 3.1      | Thermal Design Considerations                     | Figure 18. | Host DMA Read Timing Diagram, HPCR[OAD] = 0  | 35 |

|     | 3.2 F    | Power Supply Design Considerations42              | Figure 19. | Host DMA Write Timing Diagram, HPCR[OAD] = 0 | 35 |

|     |          | Estimated Power Usage Calculations49              |            | I2C Timing Diagram                           |    |

|     |          | Reset and Boot                                    | Figure 21. | UART Input Timing                            | 37 |

|     | 3.5      | DDR Memory System Guidelines                      |            | UART Output Timing                           |    |

| 4   |          | ng Information57                                  |            | EE Pin Timing                                |    |

| 5   | Packag   | ge Information58                                  |            | EVNT Pin Timing                              |    |

| 6   |          | ct Documentation                                  | Figure 25. |                                              |    |

| 7   | Revision | on History                                        | Figure 26. | Test Clock Input Timing Diagram              | 39 |

|     |          |                                                   | -          | Boundary Scan (JTAG) Timing Diagram          |    |

| LI  | St Of F  | igures                                            |            | Test Access Port Timing Diagram              |    |

| Fig | jure 1.  | MSC7116 Block Diagram                             |            | TRST Timing Diagram                          |    |

| Fig | jure 2.  | MSC7116 Molded Array Process-Ball Grid Array      | Figure 30. | Voltage Sequencing Case 1                    | 43 |

|     |          | (MAP-BGA), Top View                               |            | Voltage Sequencing Case 2                    |    |

| Fig | jure 3.  | MSC7116 Molded Array Process-Ball Grid Array      | Figure 32. | Voltage Sequencing Case 3                    | 45 |

|     |          | (MAP-BGA), Bottom View 5                          |            | Voltage Sequencing Case 4                    |    |

| Fig | jure 4.  | Timing Diagram for a Reset Configuration Write 25 | -          | Voltage Sequencing Case 5                    |    |

| Fig | jure 5.  | DDR DRAM Input Timing Diagram 26                  |            | PLL Power Supply Filter Circuits             |    |

| Fig | jure 6.  | DDR DRAM Output Timing Diagram 27                 |            | SSTL Termination Techniques                  |    |

| Fig | jure 7.  | DDR DRAM AC Test Load                             |            | SSTL Power Value                             |    |

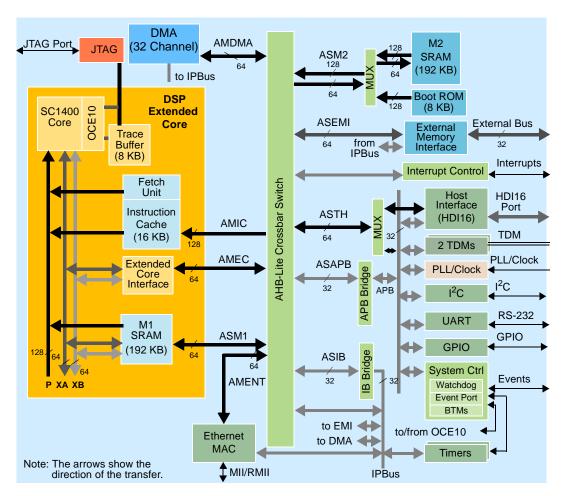

Figure 1. MSC7116 Block Diagram

# 1.2 Signal List By Ball Location

**Table 1** lists the signals sorted by ball number and configuration.

Table 1. MSC7116 Signals by Ball Designator

|        | Signal Names |                          |                      |                |          |            |  |  |

|--------|--------------|--------------------------|----------------------|----------------|----------|------------|--|--|

| Number |              | S                        | oftware Controlle    | ed             | Hardware | Controlled |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled    | Primary  | Alternate  |  |  |

| A1     |              |                          | G                    | ND             |          |            |  |  |

| A2     |              |                          | G                    | ND             |          |            |  |  |

| A3     |              |                          | DC                   | QM1            |          |            |  |  |

| A4     |              |                          | DC                   | QS2            |          |            |  |  |

| A5     |              |                          | C                    | CK             |          |            |  |  |

| A6     |              |                          | C                    | CK             |          |            |  |  |

| A7     |              | GPIC7                    |                      | GPOC7          | HI       | D15        |  |  |

| A8     |              | GPIC4                    |                      | GPOC4          | HI       | D12        |  |  |

| A9     |              | GPIC2                    |                      | GPOC2          | HI       | D10        |  |  |

| A10    |              | rese                     | erved                |                | Н        | ID7        |  |  |

| A11    |              | rese                     | erved                |                | Н        | ID6        |  |  |

| A12    |              | rese                     | erved                |                | Н        | ID4        |  |  |

| A13    |              | rese                     | erved                |                | Н        | ID1        |  |  |

| A14    |              | rese                     | erved                |                | Н        | ID0        |  |  |

| A15    |              |                          | G                    | ND             |          |            |  |  |

| A16    | ВМ3          | GP                       | ID8                  | GPOD8          | reserved |            |  |  |

| A17    |              | l                        | N                    | IC             |          |            |  |  |

| A18    |              |                          | N                    | IC             |          |            |  |  |

| A19    |              |                          | N                    | IC             |          |            |  |  |

| A20    |              |                          | N                    | IC             |          |            |  |  |

| B1     |              |                          | V <sub>E</sub>       | DDM            |          |            |  |  |

| B2     |              |                          |                      | IC             |          |            |  |  |

| В3     |              |                          | C                    | <del>S</del> 0 |          |            |  |  |

| B4     |              |                          | DC                   | QM2            |          |            |  |  |

| B5     |              |                          | DC                   | QS3            |          |            |  |  |

| B6     | DQS0         |                          |                      |                |          |            |  |  |

| B7     | CKE          |                          |                      |                |          |            |  |  |

| B8     | WE           |                          |                      |                |          |            |  |  |

| B9     |              | GPIC6 GPOC6              |                      |                |          | D14        |  |  |

| B10    |              | GPIC3 GPOC3              |                      |                | HI       | D11        |  |  |

| B11    |              | GPICO GPOCO              |                      |                |          | ID8        |  |  |

| B12    |              | rese                     | erved                | '              | Н        | ID5        |  |  |

| B13    |              | rese                     | erved                |                | H        | ID2        |  |  |

|        | Signal Names |                          |                      |             |          |            |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|

| Number |              | So                       | oftware Controlle    | ed          | Hardware | Controlled |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |

| F6     |              |                          | V <sub>I</sub>       | DDC         |          |            |  |  |

| F7     |              |                          | G                    | ND          |          |            |  |  |

| F8     |              |                          | G                    | ND          |          |            |  |  |

| F9     |              |                          | G                    | ND          |          |            |  |  |

| F10    |              |                          | V[                   | DDM         |          |            |  |  |

| F11    |              |                          | V <sub>[</sub>       | DDM         |          |            |  |  |

| F12    |              |                          | G                    | ND          |          |            |  |  |

| F13    |              |                          | G                    | ND          |          |            |  |  |

| F14    |              |                          | G                    | ND          |          |            |  |  |

| F15    |              |                          | V <sub>[</sub>       | DDIO        |          |            |  |  |

| F16    |              |                          | J/                   | DDC         |          |            |  |  |

| F17    |              |                          |                      | DDC         |          |            |  |  |

| F18    |              |                          |                      | 1C          |          |            |  |  |

| F19    |              |                          | ١                    | 1C          |          |            |  |  |

| F20    |              |                          | ١                    | 1C          |          |            |  |  |

| G1     |              |                          | G                    | ND          |          |            |  |  |

| G2     |              |                          | D                    | 113         |          |            |  |  |

| G3     |              |                          | G                    | ND          |          |            |  |  |

| G4     |              |                          | V <sub>[</sub>       | DDM         |          |            |  |  |

| G5     |              |                          |                      | DDM         |          |            |  |  |

| G6     |              |                          |                      | ND          |          |            |  |  |

| G7     |              |                          | G                    | ND          |          |            |  |  |

| G8     |              |                          | G                    | ND          |          |            |  |  |

| G9     |              |                          | G                    | ND          |          |            |  |  |

| G10    |              |                          | G                    | ND          |          |            |  |  |

| G11    |              |                          | G                    | ND          |          |            |  |  |

| G12    |              |                          | G                    | ND          |          |            |  |  |

| G13    |              |                          | G                    | ND          |          |            |  |  |

| G14    |              |                          | G                    | ND          |          |            |  |  |

| G15    |              | V <sub>DDIO</sub>        |                      |             |          |            |  |  |

| G16    |              | V <sub>DDIO</sub>        |                      |             |          |            |  |  |

| G17    |              | V <sub>DDC</sub>         |                      |             |          |            |  |  |

| G18    |              | NC NC                    |                      |             |          |            |  |  |

| G19    |              |                          | N                    | IC          |          |            |  |  |

| G20    |              |                          | N                    | IC          |          |            |  |  |

| H1     |              |                          |                      | 014         |          |            |  |  |

|        | Signal Names |                          |                      |             |          |               |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|---------------|--|--|

| Number |              | S                        | oftware Controlle    | ed          | Hardware | re Controlled |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate     |  |  |

| H2     |              |                          | D                    | 12          |          |               |  |  |

| Н3     |              |                          | D                    | 11          |          |               |  |  |

| H4     |              |                          | V <sub>D</sub>       | DM          |          |               |  |  |

| H5     |              |                          | V <sub>D</sub>       | DM          |          |               |  |  |

| H6     |              |                          | GI                   | ND          |          |               |  |  |

| H7     |              |                          | GI                   | ND          |          |               |  |  |

| H8     |              |                          | GI                   | ND          |          |               |  |  |

| Н9     |              |                          | GI                   | ND          |          |               |  |  |

| H10    |              |                          | GI                   | ND          |          |               |  |  |

| H11    |              |                          | GI                   | ND          |          |               |  |  |

| H12    |              |                          | GI                   | ND          |          |               |  |  |

| H13    |              |                          | GI                   | ND          |          |               |  |  |

| H14    |              |                          | GI                   | ND          |          |               |  |  |

| H15    |              |                          | V <sub>D</sub>       | DIO         |          |               |  |  |

| H16    |              |                          |                      | DIO         |          |               |  |  |

| H17    |              |                          |                      | DDC         |          |               |  |  |

| H18    |              |                          |                      | С           |          |               |  |  |

| H19    |              | rese                     | rved                 |             | Н        | IA2           |  |  |

| H20    |              | rese                     | rved                 |             | Н        | IA1           |  |  |

| J1     |              |                          | D                    | 10          |          |               |  |  |

| J2     |              |                          | V <sub>D</sub>       | DM          |          |               |  |  |

| J3     |              |                          |                      | 9           |          |               |  |  |

| J4     |              |                          | V <sub>D</sub>       | DM          |          |               |  |  |

| J5     |              |                          |                      | DM          |          |               |  |  |

| J6     |              |                          |                      | DM          |          |               |  |  |

| J7     |              |                          |                      | ND          |          |               |  |  |

| J8     |              |                          | GI                   | ND          |          |               |  |  |

| J9     |              |                          | GI                   | ND          |          |               |  |  |

| J10    |              | GND                      |                      |             |          |               |  |  |

| J11    |              | GND                      |                      |             |          |               |  |  |

| J12    |              |                          | GI                   | ND          |          |               |  |  |

| J13    |              |                          | GI                   | ND          |          |               |  |  |

| J14    |              | GND                      |                      |             |          |               |  |  |

| J15    |              |                          | GI                   | ND          |          |               |  |  |

| J16    |              |                          | V <sub>D</sub>       | DIO         |          |               |  |  |

| J17    |              |                          |                      | DDC         |          |               |  |  |

|        | Signal Names |                          |                      |             |            |              |  |  |

|--------|--------------|--------------------------|----------------------|-------------|------------|--------------|--|--|

| Number |              | S                        | ed                   | Hardware    | Controlled |              |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate    |  |  |

| J18    |              | GPIC11                   |                      | GPOC11      | Н          | A3           |  |  |

| J19    |              | rese                     | rved                 |             | HACK/HACK  | or HRRQ/HRRQ |  |  |

| J20    | HDSP         |                          | reserved             |             | HREQ/HREQ  | or HTRQ/HTRQ |  |  |

| K1     |              |                          | 1                    | 00          |            |              |  |  |

| K2     |              |                          | G                    | ND          |            |              |  |  |

| K3     |              |                          | 1                    | D8          |            |              |  |  |

| K4     |              |                          | V                    | DDC         |            |              |  |  |

| K5     |              |                          |                      | DDM         |            |              |  |  |

| K6     |              |                          |                      | ND          |            |              |  |  |

| K7     |              |                          | G                    | ND          |            |              |  |  |

| K8     |              |                          | G                    | ND          |            |              |  |  |

| K9     |              |                          | G                    | ND          |            |              |  |  |

| K10    |              |                          | G                    | ND          |            |              |  |  |

| K11    |              |                          | G                    | ND          |            |              |  |  |

| K12    |              |                          | G                    | ND          |            |              |  |  |

| K13    |              | GND                      |                      |             |            |              |  |  |

| K14    |              | GND                      |                      |             |            |              |  |  |

| K15    |              |                          | VI                   | DDIO        |            |              |  |  |

| K16    |              |                          |                      | DDIO        |            |              |  |  |

| K17    |              |                          | V                    | DDC         |            |              |  |  |

| K18    |              | rese                     |                      |             | Н          | A0           |  |  |

| K19    |              | rese                     | rved                 |             | Н          | DDS          |  |  |

| K20    |              | rese                     | rved                 |             | HDS/HDS o  | or HWR/HWR   |  |  |

| L1     |              |                          | 1                    | D1          |            |              |  |  |

| L2     |              |                          | G                    | ND          |            |              |  |  |

| L3     |              |                          | 1                    | D3          |            |              |  |  |

| L4     |              | V <sub>DDC</sub>         |                      |             |            |              |  |  |

| L5     |              |                          |                      | DDM         |            |              |  |  |

| L6     |              | GND                      |                      |             |            |              |  |  |

| L7     |              | GND                      |                      |             |            |              |  |  |

| L8     |              | GND                      |                      |             |            |              |  |  |

| L9     |              | GND                      |                      |             |            |              |  |  |

| L10    |              | GND                      |                      |             |            |              |  |  |

| L11    |              | GND                      |                      |             |            |              |  |  |

| L12    |              | GND                      |                      |             |            |              |  |  |

| L13    |              |                          | G                    | ND          |            |              |  |  |

|        | Signal Names |                          |                      |             |          |               |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|---------------|--|--|

| Number |              | S                        | oftware Controlle    | ed          | Hardware | re Controlled |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate     |  |  |

| N10    |              |                          | G                    | ND          |          | ·             |  |  |

| N11    |              |                          | G                    | ND          |          |               |  |  |

| N12    |              |                          | G                    | ND          |          |               |  |  |

| N13    |              |                          | G                    | ND          |          |               |  |  |

| N14    |              |                          | G                    | ND          |          |               |  |  |

| N15    |              |                          | V <sub>D</sub>       | DIO         |          |               |  |  |

| N16    |              |                          | V <sub>E</sub>       | DC          |          |               |  |  |

| N17    |              |                          | V <sub>E</sub>       | DDC         |          |               |  |  |

| N18    |              |                          |                      | KIN         |          |               |  |  |

| N19    | GPI          | A15                      | ĪRQ14                | GPOA15      | S        | CL            |  |  |

| N20    |              |                          | V <sub>S</sub>       | SPLL        |          |               |  |  |

| P1     |              |                          |                      | 7           |          |               |  |  |

| P2     |              |                          | D                    | 17          |          |               |  |  |

| P3     |              |                          | D                    | 16          |          |               |  |  |

| P4     |              |                          | V <sub>C</sub>       | DM          |          |               |  |  |

| P5     |              |                          |                      | DM          |          |               |  |  |

| P6     |              |                          |                      | DM          |          |               |  |  |

| P7     |              |                          |                      | ND          |          |               |  |  |

| P8     |              |                          | G                    | ND          |          |               |  |  |

| P9     |              |                          | G                    | ND          |          |               |  |  |

| P10    |              |                          | G                    | ND          |          |               |  |  |

| P11    |              |                          | G                    | ND          |          |               |  |  |

| P12    |              |                          | G                    | ND          |          |               |  |  |

| P13    |              |                          | G                    | ND          |          |               |  |  |

| P14    |              |                          | G                    | ND          |          |               |  |  |

| P15    |              |                          | V <sub>D</sub>       | DIO         |          |               |  |  |

| P16    |              |                          |                      | DIO         |          |               |  |  |

| P17    |              | V <sub>DDC</sub>         |                      |             |          |               |  |  |

| P18    | PORESET      |                          |                      |             |          |               |  |  |

| P19    |              | TPSEL                    |                      |             |          |               |  |  |

| P20    | $V_{DDPLL}$  |                          |                      |             |          |               |  |  |

| R1     | GND          |                          |                      |             |          |               |  |  |

| R2     |              | D19                      |                      |             |          |               |  |  |

| R3     |              | D18                      |                      |             |          |               |  |  |

| R4     |              |                          | V                    | DM          |          |               |  |  |

| R5     |              |                          |                      | DM          |          |               |  |  |

#### 2.3 Thermal Characteristics

**Table 4** describes thermal characteristics of the MSC7116 for the MAP-BGA package.

**Table 4. Thermal Characteristics for MAP-BGA Package**

|                                                       |                 | MAP-BGA               |                               |      |

|-------------------------------------------------------|-----------------|-----------------------|-------------------------------|------|

| Characteristic                                        | Symbol          | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow | Unit |

| Junction-to-ambient <sup>1, 2</sup>                   | $R_{\theta JA}$ | 39                    | 31                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup> | $R_{	heta JA}$  | 23                    | 20                            | °C/W |

| Junction-to-board <sup>4</sup>                        | $R_{	heta JB}$  | 12                    |                               | °C/W |

| Junction-to-case <sup>5</sup>                         | $R_{	heta JC}$  | 7                     |                               | °C/W |

| Junction-to-package-top <sup>6</sup>                  | $\Psi_{JT}$     | 2                     |                               | °C/W |

Notes:

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- **6.** Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

Section 3.1, Thermal Design Considerations explains these characteristics in detail.

### 2.4 DC Electrical Characteristics

This section describes the DC electrical characteristics for the MSC7116.

**Note:** The leakage current is measured for nominal voltage values must vary in the same direction (for example, both  $V_{DDIO}$  and  $V_{DDC}$  vary by +2 percent or both vary by -2 percent).

**Table 5. DC Electrical Characteristics**

| Characteristic                                             | Symbol                                 | Min                     | Typical   | Max                     | Unit |

|------------------------------------------------------------|----------------------------------------|-------------------------|-----------|-------------------------|------|

| Core and PLL voltage                                       | V <sub>DDC</sub><br>V <sub>DDPLL</sub> | 1.14                    | 1.2       | 1.26                    | V    |

| DRAM interface I/O voltage <sup>1</sup>                    | $V_{DDM}$                              | 2.375                   | 2.5       | 2.625                   | V    |

| I/O voltage                                                | V <sub>DDIO</sub>                      | 3.135                   | 3.3       | 3.465                   | V    |

| DRAM interface I/O reference voltage <sup>2</sup>          | $V_{REF}$                              | $0.49 \times V_{DDM}$   | 1.25      | $0.51 \times V_{DDM}$   | V    |

| DRAM interface I/O termination voltage <sup>3</sup>        | VTT                                    | V <sub>REF</sub> – 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V    |

| Input high CLKIN voltage                                   | V <sub>IHCLK</sub>                     | 2.4                     | 3.0       | 3.465                   | V    |

| DRAM interface input high I/O voltage                      | V <sub>IHM</sub>                       | V <sub>REF</sub> + 0.28 | $V_{DDM}$ | V <sub>DDM</sub> + 0.3  | V    |

| DRAM interface input low I/O voltage                       | V <sub>ILM</sub>                       | -0.3                    | GND       | V <sub>REF</sub> – 0.18 | V    |

| Input leakage current, V <sub>IN</sub> = V <sub>DDIO</sub> | I <sub>IN</sub>                        | -1.0                    | 0.09      | 1                       | μΑ   |

| V <sub>REF</sub> input leakage current                     | I <sub>VREF</sub>                      | _                       | _         | 5                       | μΑ   |

### 2.5.2.3 Multiplication Factor Range

The multiplier block output frequency ranges depend on the divided input clock frequency as shown in Table 10.

**Table 10. PLLMLTF Ranges**

|       | Multiplier Block (Loop) Output Range                                                                       | Minimum PLLMLTF Value             | Maximum PLLMLTF Value      |

|-------|------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|

|       | 266 ≤ [Divided Input Clock × (PLLMLTF + 1)] ≤ 532 MHz                                                      | 266/Divided Input Clock           | 532/Divided Input Clock    |

| Note: | This table results from the allowed range for $F_{Loop}$ . The minim frequency of the Divided Input Clock. | uum and maximum multiplication fa | ctors are dependent on the |

#### 2.5.2.4 Allowed Core Clock Frequency Range

The frequency delivered to the core, extended core, and peripherals depends on the value of the CLKCTRL[RNG] bit as shown in **Table 11**.

Table 11. F<sub>vco</sub> Frequency Ranges

| CLI   | KCTRL[RNG] Value                                                                                                      | Allowed Range of F <sub>vco</sub> |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

|       | 1                                                                                                                     | 266 ≤ F <sub>vco</sub> ≤ 532 MHz  |  |  |

| 0     |                                                                                                                       | 133 ≤ F <sub>vco</sub> ≤ 266 MHz  |  |  |

| Note: | This table results from the allowed range for F <sub>vco</sub> , which is F <sub>Loop</sub> modified by CLKCTRL[RNG]. |                                   |  |  |

This bit along with the CKSEL determines the frequency range of the core clock.

**Table 12. Resulting Ranges Permitted for the Core Clock**

| CLKCT | RL[CKSEL]                                                                                                            | CLKCTRL[RNG] | Resulting<br>Division<br>Factor | Allowed Range<br>of Core Clock | Comments                |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|--------------------------------|-------------------------|--|--|

|       | 11                                                                                                                   | 1            | 1                               | Reserved                       | Reserved                |  |  |

|       | 11                                                                                                                   | 0            | 2                               | 133 ≤ core clock ≤ 266 MHz     | Limited by range of PLL |  |  |

|       | 01                                                                                                                   | 1            | 2                               | 133 ≤ core clock ≤ 266 MHz     | Limited by range of PLL |  |  |

|       | 01                                                                                                                   | 0            | 4                               | 66.5 ≤ core clock ≤ 133 MHz    | Limited by range of PLL |  |  |

| Note: | This table results from the allowed range for F <sub>OUT</sub> , which depends on clock selected via CLKCTRL[CKSEL]. |              |                                 |                                |                         |  |  |

## 2.5.2.5 Core Clock Frequency Range When Using DDR Memory

The core clock can also be limited by the frequency range of the DDR devices in the system. **Table 13** summarizes this restriction.

Table 13. Core Clock Ranges When Using DDR

| DDR Type                               | Allowed Frequency<br>Range for DDR CK | Corresponding Range for the Core Clock | Comments                                  |

|----------------------------------------|---------------------------------------|----------------------------------------|-------------------------------------------|

| DDR 200 (PC-1600)                      | 83–100 MHz                            | 166 ≤ core clock ≤ 200 MHz             | Core limited to 2 × maximum DDR frequency |

| DDR 266 (PC-2100)<br>DDR 333 (PC-2600) | 83–133 MHz                            | 166 ≤ core clock ≤ 266 MHz             | Core limited to 2 × maximum DDR frequency |

## 2.5.3 Reset Timing

The MSC7116 device has several inputs to the reset logic. All MSC7116 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. **Table 14** describes the reset sources.

**Table 14. Reset Sources**

| Name                                       | Direction     | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)                | Input         | Initiates the power-on reset flow that resets the MSC7116 and configures various attributes of the MSC7116. On PORESET, the entire MSC7116 device is reset. SPLL and DLL states are reset, HRESET is driven, the SC1400 extended core is reset, and system configuration is sampled. The system is configured only when PORESET is asserted. |

| External Hard reset (HRESET)               | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC7116. While HRESET is asserted, HRESET is an open-drain output. Upon hard reset, HRESET is driven and the SC1400 extended core is reset.                                                                                                                          |

| Software watchdog reset                    | Internal      | When the MSC7116 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                    |

| Bus monitor reset                          | Internal      | When the MSC7116 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                         |

| JTAG EXTEST,<br>CLAMP, or<br>HIGHZ command | Internal      | When a Test Access Port (TAP) executes an EXTEST, CLAMP, or HIGHZ command, the TAP logic asserts an internal reset signal that generates an internal soft reset sequence.                                                                                                                                                                    |

**Table 15** summarizes the reset actions that occur as a result of the different reset sources.

**Table 15. Reset Actions for Each Reset Source**

|                                                                           | Power-On Reset<br>(PORESET) | H <u>ard Rese</u> t<br>(HRESET)                                  | S <u>oft Rese</u> t<br>(SRESET)             |

|---------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------|---------------------------------------------|

| Reset Action/Reset Source                                                 | External only               | External or<br>Internal (Software<br>Watchdog or Bus<br>Monitor) | JTAG Command:<br>EXTEST, CLAMP,<br>or HIGHZ |

| Configuration pins sampled (refer to <b>Section 2.5.3.1</b> for details). | Yes                         | No                                                               | No                                          |

| PLL and clock synthesis states Reset                                      | Yes                         | No                                                               | No                                          |

| HRESET Driven                                                             | Yes                         | Yes                                                              | No                                          |

| Software watchdog and bus time-out monitor registers                      | Yes                         | Yes                                                              | Yes                                         |

| Clock synthesis modules (STOPCTRL, HLTREQ, and HLTACK) reset              | Yes                         | Yes                                                              | Yes                                         |

| Extended core reset                                                       | Yes                         | Yes                                                              | Yes                                         |

| Peripheral modules reset                                                  | Yes                         | Yes                                                              | Yes                                         |

# 2.5.3.1 Power-On Reset (PORESET) Pin

Asserting  $\overline{\text{PORESET}}$  initiates the power-on reset flow.  $\overline{\text{PORESET}}$  must be asserted externally for at least 16 CLKIN cycles after external power to the MSC7116 reaches at least 2/3  $V_{DD}$ .

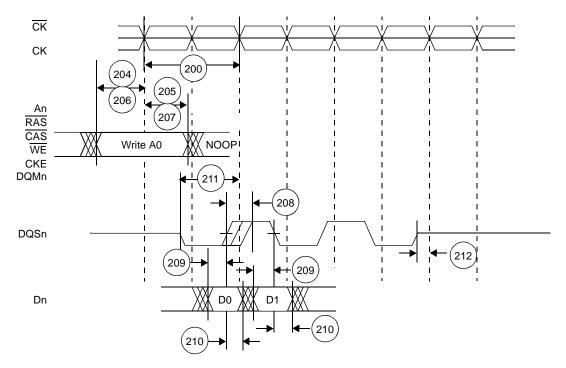

| No. | Parameter                                              | Symbol                                      | Min                          | Max | Unit |

|-----|--------------------------------------------------------|---------------------------------------------|------------------------------|-----|------|

| 209 | Dn/DQMn output setup with respect to DQSn <sup>3</sup> | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 0.25 × t <sub>CK</sub> – 750 | _   | ps   |

| 210 | Dn/DQMn output hold with respect to DQSn <sup>3</sup>  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> | 0.25 × t <sub>CK</sub> – 750 | _   | ps   |

| 211 | DQSn preamble start <sup>4</sup>                       | t <sub>DDKHMP</sub>                         | $-0.25 \times t_{CK}$        | _   | ps   |

| 212 | DQSn epilogue end <sup>5</sup>                         | t <sub>DDKHME</sub>                         | -600                         | 600 | ps   |

Notes:

- 1. All CK/CK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 2. t<sub>DDKHMH</sub> can be modified through the TCFG2[WRDD] DQSS override bits. The DRAM requires that the first write data strobe arrives 75–125% of a DRAM cycle after the write command is issued. Any skew between DQSn and CK must be considered when trying to achieve this 75%–125% goal. The TCFG2[WRDD] bits can be used to shift DQSn by 1/4 DRAM cycle increments. The skew in this case refers to an internal skew existing at the signal connections. By default, the CK/CK crossing occurs in the middle of the control signal (An/RAS/CAS/WE/CKE) tenure. Setting TCFG2[ACSM] bit shifts the control signal assertion 1/2 DRAM cycle earlier than the default timing. This means that the signal is asserted no earlier than 600 ps before the CK/CK crossing and no later than 600 ps after the crossing time; the device uses 1200 ps of the skew budget (the interval from –600 to +600 ps). Timing is verified by referencing the falling edge of CK. See Chapter 10 of the MSC711x Reference Manual for details.

- 3. Determined by maximum possible skew between a data strobe (DQS) and any corresponding bit of data. The data strobe should be centered inside of the data eye.

- 4. Please note that this spec is in reference to the DQSn first rising edge. It could also be referenced from CK(r), but due to programmable delay of the write strobes (TCFG2[WRDD]), there pre-amble may be extended for a full DRAM cycle. For this reason, we reference from DQSn.

- 5. All outputs are referenced to the rising edge of CK. Note that this is essentially the CK/DQSn skew in spec 208. In addition there is no real "maximum" time for the epilogue end. JEDEC does not require this is as a device limitation, but simply for the chip to guarantee fast enough write-to-read turn-around times. This is already guaranteed by the memory controller operation.

Figure 6 shows the DDR DRAM output timing diagram.

Figure 6. DDR DRAM Output Timing Diagram

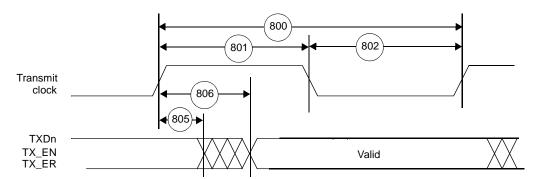

## 2.5.6.2 Transmit Signal Timing

#### **Table 22. Transmit Signal Timing**

| No. | Characteristics                                                                            | Min           | Max          | Unit          |

|-----|--------------------------------------------------------------------------------------------|---------------|--------------|---------------|

| 800 | Transmit clock period:  • MII: TXCLK  • RMII: REFCLK                                       | 40<br>20      |              | ns<br>ns      |

| 801 | Transmit clock pulse width high—as a percent of clock period  • MII: RXCLK  • RMII: REFCLK | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 802 | Transmit clock pulse width low—as a percent of clock period:  • MII: RXCLK  • RMII: REFCLK | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 805 | Transmit clock to TXDn, TX_EN, TX_ER invalid                                               | 4             | _            | ns            |

| 806 | Transmit clock to TXDn, TX_EN, TX_ER valid                                                 | _             | 14           | ns            |

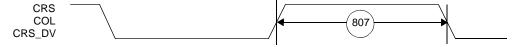

Figure 11. Ethernet Receive Signal Timing

## 2.5.6.3 Asynchronous Input Signal Timing

**Table 23. Asynchronous Input Signal Timing**

| No. | Characteristics                                             | Min | Max | Unit |

|-----|-------------------------------------------------------------|-----|-----|------|

| 807 | • MII: CRS and COL minimum pulse width (1.5 × TXCLK period) | 60  | _   | ns   |

|     | RMII: CRS_DV minimum pulse width (1.5 x REFCLK period)      | 30  | _   | ns   |

Figure 12. Asynchronous Input Signal Timing

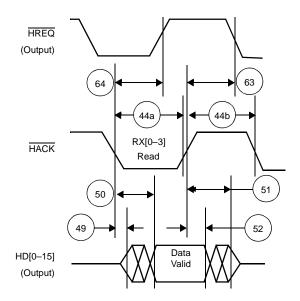

Figure 18. Host DMA Read Timing Diagram, HPCR[OAD] = 0

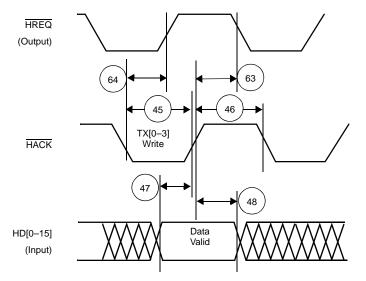

Figure 19. Host DMA Write Timing Diagram, HPCR[OAD] = 0

# 2.5.13 JTAG Signals

**Table 31. JTAG Timing**

| No.   | Characteristics                                                                                                                                                                                                            | All fred | 1124 |      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|

| NO.   | Characteristics                                                                                                                                                                                                            | Min      | Max  | Unit |

| 700   | TCK frequency of operation (1/( $T_C \times 3$ )  Note: $T_C = 1/\text{CLOCK}$ which is the period of the core clock. The TCK frequency must less than 1/3 of the core frequency with an absolute maximum limit of 40 MHz. | 0.0      | 40.0 | MHz  |

| 701   | TCK cycle time                                                                                                                                                                                                             | 25.0     | _    | ns   |

| 702   | TCK clock pulse width measured at V <sub>M =</sub> 1.6 V                                                                                                                                                                   | 11.0     | _    | ns   |

| 703   | TCK rise and fall times                                                                                                                                                                                                    | 0.0      | 3.0  | ns   |

| 704   | Boundary scan input data set-up time                                                                                                                                                                                       | 5.0      | _    | ns   |

| 705   | Boundary scan input data hold time                                                                                                                                                                                         | 14.0     | _    | ns   |

| 706   | TCK low to output data valid                                                                                                                                                                                               | 0.0      | 20.0 | ns   |

| 707   | TCK low to output high impedance                                                                                                                                                                                           | 0.0      | 20.0 | ns   |

| 708   | TMS, TDI data set-up time                                                                                                                                                                                                  | 5.0      | _    | ns   |

| 709   | TMS, TDI data hold time                                                                                                                                                                                                    | 14.0     | _    | ns   |

| 710   | TCK low to TDO data valid                                                                                                                                                                                                  | 0.0      | 24.0 | ns   |

| 711   | TCK low to TDO high impedance                                                                                                                                                                                              | 0.0      | 10.0 | ns   |

| 712   | TRST assert time                                                                                                                                                                                                           | 100.0    | _    | ns   |

| Note: | All timings apply to OCE module data transfers as the OCE module uses the JTAG port as an interface.                                                                                                                       |          |      |      |

TCK (Input) 703 703 703

Figure 26. Test Clock Input Timing Diagram

# 3 Hardware Design Considerations

This section described various areas to consider when incorporating the MSC7116 device into a system design.

## 3.1 Thermal Design Considerations

An estimation of the chip-junction temperature, T<sub>I</sub>, in °C can be obtained from the following:

$$T_{J} = T_{A} + (R_{\mathbf{Q}JA} \times P_{D})$$

Eqn. 1

where

$T_A$  = ambient temperature near the package (°C)

$R_{AIA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D = P_{INT} + P_{I/O} = power dissipation in the package (W)$

$P_{INT} = I_{DD} \times V_{DD} = internal power dissipation (W)$

$P_{I/O}$  = power dissipated from device on output pins (W)

The power dissipation values for the MSC7116 are listed in **Table 4**. The ambient temperature for the device is the air temperature in the immediate vicinity that would cool the device. The junction-to-ambient thermal resistances are JEDEC standard values that provide a quick and easy estimation of thermal performance. There are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. The value that more closely approximates a specific application depends on the power dissipated by other components on the printed circuit board (PCB). The value obtained using a single layer board is appropriate for tightly packed PCB configurations. The value obtained using a board with internal planes is more appropriate for boards with low power dissipation (less than 0.02 W/cm<sup>2</sup> with natural convection) and well separated components. Based on an estimation of junction temperature using this technique, determine whether a more detailed thermal analysis is required. Standard thermal management techniques can be used to maintain the device thermal junction temperature below its maximum. If T<sub>J</sub> appears to be too high, either lower the ambient temperature or the power dissipation of the chip.

You can verify the junction temperature by measuring the case temperature using a small diameter thermocouple (40 gauge is recommended) or an infrared temperature sensor on a spot on the device case. Use the following equation to determine T<sub>I</sub>:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Eqn. 2

where

$T_T$  = thermocouple (or infrared) temperature on top of the package (°C)

$\Psi_{IT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

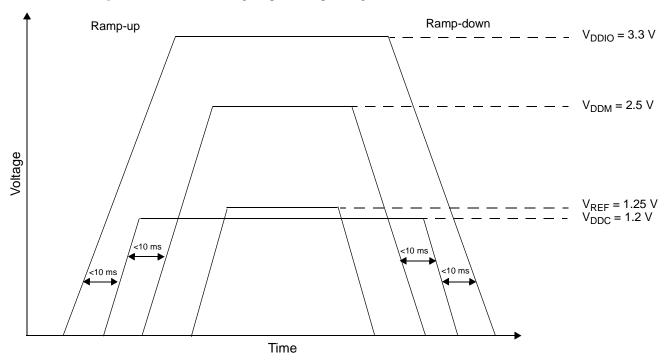

#### 3.2.2.1 Case 1

The power-up sequence is as follows:

- 1. Turn on the V<sub>DDIO</sub> (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn on the  $V_{DDM}$  (2.5 V) supply third.

- 4. Turn on the  $V_{REF}$  (1.25 V) supply fourth (last).

The power-down sequence is as follows:

- 1. Turn off the  $V_{REF}$  (1.25 V) supply first.

- 2. Turn off the  $V_{DDM}$  (2.5 V) supply second.

- 3. Turn off the  $V_{DDC}$  (1.2 V) supply third.

- 4. Turn of the V<sub>DDIO</sub> (3.3 V) supply fourth (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down of V<sub>DDIO</sub> and V<sub>DDC</sub> is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 10 ms for power-up and power-down.

- Refer to **Figure 30** for relative timing for power sequencing case 1.

Figure 30. Voltage Sequencing Case 1

#### 3.3.2 Peripheral Power

Peripherals include the DDR memory controller, Ethernet controller, DMA controller, HDI16, TDM, UART, timers, GPIOs, and the I<sup>2</sup>C module. Basic power consumption by each module is assumed to be the same and is computed by using the following equation which assumes an effective load of 20 pF, core voltage swing of 1.2 V, and a switching frequency of 133 MHz. This yields:

$$P_{PERIPHERAL} = 20 \ pF \times (1.2 \ V)^2 \times 133 \ MHz \times 10^{-3} = 3.83 \ mW \ per \ peripheral$$

Eqn. 6

Multiply this value by the number of peripherals used in the application to compute the total peripheral power consumption.

#### 3.3.3 External Memory Power

Estimation of power consumption by the DDR memory system is complex. It varies based on overall system signal line usage, termination and load levels, and switching rates. Because the DDR memory includes terminations external to the MSC7116 device, the 2.5 V power source provides the power for the termination, which is a static value of 16 mA per signal driven high. The dynamic power is computed, however, using a differential voltage swing of  $\pm 0.200$  V, yielding a peak-to-peak swing of 0.4 V. The equations for computing the DDR power are:

$$P_{DDRIO} = P_{STATIC} + P_{DYNAMIC}$$

Eqn. 7

$$P_{STATIC} = (unused pins \times \% driven high) \times 16 \text{ mA} \times 2.5 \text{ V}$$

Eqn. 8

$$P_{DYNAMIC} = (pin \ activity \ value) \times 20 \ pF \times (0.4 \ V)^2 \times 266 \ MHz \times 10^{-3} \ mW$$

Eqn. 9

pin activity value = (active data lines  $\times$  % activity  $\times$  % data switching) + (active address lines  $\times$  % activity) Eqn. 10

As an example, assume the following:

unused pins = 16 (DDR uses 16-pin mode)

% driven high = 50%

active data lines = 16

% activity = 60%

% data switching = 50%

active address lines = 3

In this example, the DDR memory power consumption is:

$$P_{DDRIO} = ((16 \times 0.5) \times 16 \times 2.5) + (((16 \times 0.6 \times 0.5) + (3 \times 0.6)) \times 20 \times (0.4)^{2} \times 266 \times 10^{-3}) = 326.3 \text{ mW}$$

Eqn. 11

#### 3.3.4 External I/O Power

The estimation of the I/O power is similar to the computation of the peripheral power estimates. The power consumption per signal line is computed assuming a maximum load of 20 pF, a voltage swing of 3.3 V, and a switching frequency of 33 MHz, which yields:

$$P_{IO} = 20 \text{ pF} \times (3.3 \text{ V})^2 \times 33 \text{ MHz} \times 10^{-3} = 7.19 \text{ mW per I/O line}$$

Eqn. 12

Multiply this number by the number of I/O signal lines used in the application design to compute the total I/O power.

**Note:** The signal loading depends on the board routing. For systems using a single DDR device, the load could be as low as 7 pF.

## 3.3.5 Leakage Power

The leakage power is for all power supplies combined at a specific temperature. The value is temperature dependent. The observed leakage value at room temperature is 64 mW.

MSC7116 Data Sheet, Rev. 13

# 3.5 DDR Memory System Guidelines

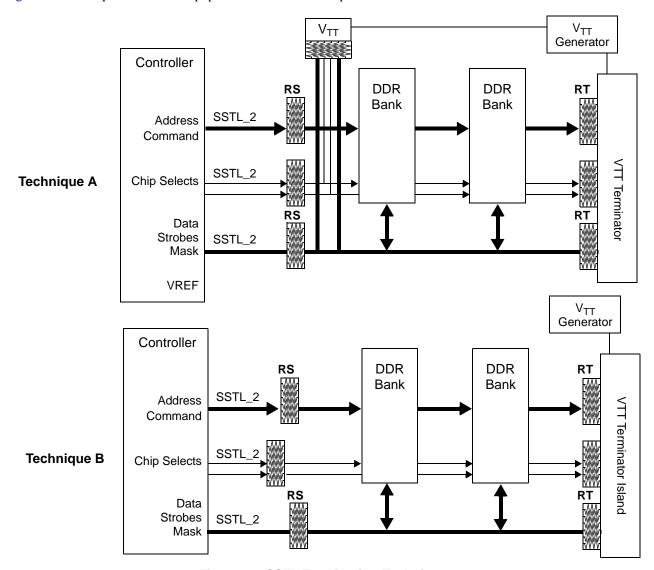

MSC7116 devices contain a memory controller that provides a glueless interface to external double data rate (DDR) SDRAM memory modules with Class 2 Series Stub Termination Logic 2.5 V (SSTL\_2). There are two termination techniques, as shown in Figure 36. Technique B is the most popular termination technique.

Figure 36. SSTL Termination Techniques

Figure 37 illustrates the power wattage for the resistors. Typical values for the resistors are as follows:

- $RS = 22 \Omega$

- $RT = 24 \Omega$

## 3.6 Connectivity Guidelines

This section summarizes the connections and special conditions, such as pull-up or pull-down resistors, for the MSC7116 device. Following are guidelines for signal groups and configuration settings:

- Clock and reset signals.

- SWTE is used to configure the MSC7116 device and is sampled on the deassertion of PORESET, so it should be tied to V<sub>DDC</sub> or GND either directly or through pull-up or pull-down resistors until PORESET is deasserted. After PORESET, this signal can be left floating.

- BM[0-1] configure the MSC7116 device and are sampled until PORESET is deasserted, so they should be tied to V<sub>DDIO</sub> or GND either directly or through pull-up or pull-down resistors.

- HRESET should be pulled up.

- Interrupt signals. When used,  $\overline{IRQ}$  pins must be pulled up.

- HDI16 signals.

- When they are configured for open-drain, the HREQ/HREQ or HTRQ/HTRQ signals require a pull-up resistor. However, these pins are also sampled at power-on reset to determine the HDI16 boot mode and may need to be pulled down. When these pins must be pulled down on reset and pulled up otherwise, a buffer can be used with the HRESET signal as the enable.

- When the device boots through the HDI16, the HDDS, HDSP and H8BIT pins should be pulled up or down, depending on the required boot mode settings.

- Ethernet MAC/TDM2 signals. The MDIO signal requires an external pull-up resistor.

- $I^2C$  signals. The SCL and SDA signals, when programmed for  $I^2C$ , requires an external pull-up resistor.

- General-purpose I/O (GPIO) signals. An unused GPIO pin can be disconnected. After boot, program it as an output pin.

- Other signals.

- The  $\overline{\mathsf{TEST0}}$  pin must be connected to ground.

- The TPSEL pin should be pulled up to enable debug access via the EOnCE port and pulled down for boundary scan.

- Pins labelled NO CONNECT (NC) must not be connected.

- When a 16-pin double data rate (DDR) interface is used, the 16 unused data pins should be no connects (floating) if the used lines are terminated.

- Do not connect DBREQ to DONE (as you would for the MSC8101 device). Connect DONE to one of the EVNT pins, and DBREQ to HRRQ.

# 4 Ordering Information

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Part    | Supply Voltage             | Package Type                                      | Pin<br>Count | Core<br>Frequency<br>(MHz) | Solder Spheres | Order Number  |

|---------|----------------------------|---------------------------------------------------|--------------|----------------------------|----------------|---------------|

| MSC7116 | 1.2 V core<br>2.5 V memory | Molded Array Process-Ball Grid<br>Array (MAP-BGA) | 400          | 266                        | Lead-free      | MSC7116VM1000 |

|         | 3.3 V I/O                  | rulay (Wirth Borty                                |              |                            | Lead-bearing   | MSC7116VF1000 |

59

# 7 Revision History

Table 36 provides a revision history for this data sheet.

**Table 36. Document Revision History**

| Revision | Date      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | Apr 2004  | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1        | May 2004  | Added ordering information and new package options.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2        | Aug. 2004 | <ul> <li>Updated clock parameter values.</li> <li>Updated DDR timing specifications.</li> <li>Updated I<sup>2</sup>C timing specifications.</li> </ul>                                                                                                                                                                                                                                                                                                                     |

| 3        | Sep. 2004 | <ul> <li>Updated Figures 1-2 and 1-2 to correct HDSP and DBREQ.</li> <li>Corrected EE0 port reference.</li> <li>Updated ball location for HDSP.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

| 4        | Jan. 2005 | <ul> <li>Added signal HA3.</li> <li>Updated absolute maximum ratings, DDR DRAM capacitance specifications, clock parameters, reset timing, and TDM timing.</li> <li>Added note for timing reference for I<sup>2</sup>C interface.</li> <li>Expanded GPIO timing information.</li> <li>Corrected pin T20 and K20 signal designation.</li> <li>Corrected signal names to GPAO15 and IRQ2.</li> <li>Expanded design guidelines in Chapter 4.</li> </ul>                       |

| 5        | Mar. 2005 | <ul> <li>Updated features list.</li> <li>Updated power specifications.</li> <li>Changed CLKIN frequency range.</li> <li>Added clock configuration information.</li> <li>Updated JTAG timings.</li> </ul>                                                                                                                                                                                                                                                                   |

| 6        | Apr. 2005 | Added recommended power supply ratings and updated equations to estimate power consumption.                                                                                                                                                                                                                                                                                                                                                                                |

| 7        | Oct. 2005 | Updated core and total power consumption examples.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8        | Dec. 2005 | Added information about the new mask set 1M88B. Affected all sections.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9        | Nov. 2006 | <ul> <li>Updated arrows in Host DMA Writing Timing figure.</li> <li>Updated boot overview in Section 4.4.3.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

| 10       | Apr. 2007 | Removed erroneous references to V <sub>CCSYN</sub> and V <sub>CCSYN1</sub> .                                                                                                                                                                                                                                                                                                                                                                                               |

| 11       | Jul. 2007 | <ul> <li>Updated to new data sheet format. Reorganized and renumbered sections, figures, and tables.</li> <li>Removed all references to obsolete mask set 1L44X and corresponding specification values.</li> <li>Added a note to clarify the definition of TCK timing 700 in new Table 31.</li> <li>Reworked reset and boot sections.</li> <li>Expanded I<sup>2</sup>C boot information and added SPI boot information.</li> <li>Removed obsolete part numbers.</li> </ul> |

| 12       | Aug 2007  | • The power-up and power-down sequences described in <b>Section 3.2</b> starting on page 42 have been expanded to five possible design scenarios/cases. These cases replace the previously recommended power-up/power-down sequence recommendations. <b>Section 3.2</b> has been clarified by adding subsection headings.                                                                                                                                                  |

| 13       | Apr 2008  | • Change the PLL filter resistor from 20 $\Omega$ to 2 $\Omega$ in <b>Section 3.2.5</b> .                                                                                                                                                                                                                                                                                                                                                                                  |