Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

## Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                      |

|-------------------------|----------------------------------------------------------------------|

| Product Status          | Obsolete                                                             |

| Туре                    | SC1400 Core                                                          |

| Interface               | Host Interface, I <sup>2</sup> C, UART                               |

| Clock Rate              | 200MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 400kB                                                                |

| Voltage - I/O           | 3.30V                                                                |

| Voltage - Core          | 1.20V                                                                |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                   |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 400-LFBGA                                                            |

| Supplier Device Package | 400-LFBGA (17x17)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc7116vm800 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | Pin As   | signments4                                        | Figure 8.  | TDM Receive Signals                          | 28 |

|-----|----------|---------------------------------------------------|------------|----------------------------------------------|----|

|     | 1.1      | MAP-BGA Ball Layout Diagrams                      | Figure 9.  | TDM Transmit Signals                         | 29 |

|     |          | Signal List By Ball Location6                     | Figure 10. | Ethernet Receive Signal Timing               | 29 |

| 2   |          | cal Characteristics                               | Figure 11. |                                              |    |

|     | 2.1      | Maximum Ratings                                   | Figure 12. | Asynchronous Input Signal Timing             | 30 |

|     | 2.2      | Recommended Operating Conditions18                | Figure 13. |                                              |    |

|     |          | Thermal Characteristics                           | Figure 14. | Read Timing Diagram, Single Data Strobe      | 33 |

|     | 2.4      | DC Electrical Characteristics19                   |            | Read Timing Diagram, Double Data Strobe      |    |

|     | 2.5      | AC Timings                                        | Figure 16. | Write Timing Diagram, Single Data Strobe     | 34 |

| 3   |          | are Design Considerations41                       |            | Write Timing Diagram, Double Data Strobe     |    |

|     | 3.1      | Thermal Design Considerations                     | Figure 18. | Host DMA Read Timing Diagram, HPCR[OAD] = 0  | 35 |

|     | 3.2 F    | Power Supply Design Considerations42              | Figure 19. | Host DMA Write Timing Diagram, HPCR[OAD] = 0 | 35 |

|     |          | Estimated Power Usage Calculations49              |            | I2C Timing Diagram                           |    |

|     |          | Reset and Boot                                    | Figure 21. | UART Input Timing                            | 37 |

|     | 3.5      | DDR Memory System Guidelines                      |            | UART Output Timing                           |    |

| 4   |          | ng Information57                                  |            | EE Pin Timing                                |    |

| 5   | Packag   | ge Information58                                  |            | EVNT Pin Timing                              |    |

| 6   |          | ct Documentation                                  | Figure 25. |                                              |    |

| 7   | Revision | on History                                        | Figure 26. | Test Clock Input Timing Diagram              | 39 |

|     |          |                                                   | -          | Boundary Scan (JTAG) Timing Diagram          |    |

| LI  | St Of F  | igures                                            |            | Test Access Port Timing Diagram              |    |

| Fig | jure 1.  | MSC7116 Block Diagram                             |            | TRST Timing Diagram                          |    |

| Fig | jure 2.  | MSC7116 Molded Array Process-Ball Grid Array      | Figure 30. | Voltage Sequencing Case 1                    | 43 |

|     |          | (MAP-BGA), Top View 4                             |            | Voltage Sequencing Case 2                    |    |

| Fig | jure 3.  | MSC7116 Molded Array Process-Ball Grid Array      | Figure 32. | Voltage Sequencing Case 3                    | 45 |

|     |          | (MAP-BGA), Bottom View 5                          |            | Voltage Sequencing Case 4                    |    |

| Fig | jure 4.  | Timing Diagram for a Reset Configuration Write 25 | -          | Voltage Sequencing Case 5                    |    |

| Fig | jure 5.  | DDR DRAM Input Timing Diagram 26                  |            | PLL Power Supply Filter Circuits             |    |

| Fig | jure 6.  | DDR DRAM Output Timing Diagram 27                 |            | SSTL Termination Techniques                  |    |

| Fig | jure 7.  | DDR DRAM AC Test Load                             |            | SSTL Power Value                             |    |

## 1.2 Signal List By Ball Location

**Table 1** lists the signals sorted by ball number and configuration.

Table 1. MSC7116 Signals by Ball Designator

| Signal Names |                     |                          |                      |                |          |            |  |  |

|--------------|---------------------|--------------------------|----------------------|----------------|----------|------------|--|--|

| Number       | Software Controlled |                          |                      |                | Hardware | Controlled |  |  |

|              | End of Reset        | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled    | Primary  | Alternate  |  |  |

| A1           |                     |                          | G                    | ND             |          |            |  |  |

| A2           |                     |                          | G                    | ND             |          |            |  |  |

| A3           |                     |                          | DC                   | QM1            |          |            |  |  |

| A4           |                     |                          | DC                   | QS2            |          |            |  |  |

| A5           |                     |                          | C                    | CK             |          |            |  |  |

| A6           |                     |                          | C                    | CK             |          |            |  |  |

| A7           |                     | GPIC7                    |                      | GPOC7          | HI       | D15        |  |  |

| A8           |                     | GPIC4                    |                      | GPOC4          | HI       | D12        |  |  |

| A9           |                     | GPIC2                    |                      | GPOC2          | HI       | D10        |  |  |

| A10          |                     | rese                     | erved                |                | Н        | ID7        |  |  |

| A11          |                     | rese                     | erved                |                | Н        | ID6        |  |  |

| A12          |                     | rese                     | erved                |                | Н        | ID4        |  |  |

| A13          |                     | rese                     | erved                |                | Н        | ID1        |  |  |

| A14          |                     | rese                     | erved                |                | Н        | ID0        |  |  |

| A15          |                     |                          | G                    | ND             |          |            |  |  |

| A16          | ВМ3                 | GP                       | ID8                  | GPOD8          | rese     | erved      |  |  |

| A17          |                     | l                        | N                    | IC             |          |            |  |  |

| A18          |                     |                          | N                    | IC             |          |            |  |  |

| A19          |                     |                          | N                    | IC             |          |            |  |  |

| A20          |                     |                          | N                    | IC             |          |            |  |  |

| B1           |                     |                          | V <sub>E</sub>       | DDM            |          |            |  |  |

| B2           |                     |                          |                      | IC             |          |            |  |  |

| В3           |                     |                          | C                    | <del>S</del> 0 |          |            |  |  |

| B4           |                     |                          | DC                   | QM2            |          |            |  |  |

| B5           |                     |                          | DC                   | QS3            |          |            |  |  |

| B6           |                     |                          | DC                   | QS0            |          |            |  |  |

| B7           | CKE                 |                          |                      |                |          |            |  |  |

| B8           |                     |                          | $\overline{v}$       | VE             |          |            |  |  |

| B9           |                     | GPIC6                    |                      | GPOC6          | HI       | D14        |  |  |

| B10          |                     | GPIC3                    |                      | GPOC3          | HI       | D11        |  |  |

| B11          |                     | GPIC0                    |                      | GPOC0          | Н        | ID8        |  |  |

| B12          |                     | rese                     | erved                | '              | Н        | ID5        |  |  |

| B13          |                     | rese                     | erved                |                | H        | ID2        |  |  |

Table 1. MSC7116 Signals by Ball Designator (continued)

| Signal Names |              |                          |                      |             |          |            |  |  |

|--------------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|

| Number       |              | Sc                       | oftware Controlle    | ed          | Hardware | Controlled |  |  |

|              | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |

| D10          |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |

| D11          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D12          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D13          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D14          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D15          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D16          |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| D17          |              |                          | V <sub>E</sub>       | DDC         |          |            |  |  |

| D18          |              |                          | N                    | IC          |          |            |  |  |

| D19          |              |                          | N                    | IC          |          |            |  |  |

| D20          |              |                          | N                    | IC          |          |            |  |  |

| E1           |              |                          | G                    | ND          |          |            |  |  |

| E2           |              |                          | D                    | 26          |          |            |  |  |

| E3           |              |                          | D                    | 31          |          |            |  |  |

| E4           |              |                          | V <sub>C</sub>       | DDM         |          |            |  |  |

| E5           |              |                          |                      | DDM         |          |            |  |  |

| E6           |              |                          |                      | DDC         |          |            |  |  |

| E7           |              |                          |                      | DDC         |          |            |  |  |

| E8           |              |                          |                      | DDC         |          |            |  |  |

| E9           |              |                          |                      | DDC         |          |            |  |  |

| E10          |              |                          |                      | DDM         |          |            |  |  |

| E11          |              |                          |                      | DIO         |          |            |  |  |

| E12          |              |                          |                      | DIO         |          |            |  |  |

| E13          |              |                          |                      | DIO         |          |            |  |  |

| E14          |              |                          |                      | DIO         |          |            |  |  |

| E15          |              |                          |                      | DIO         |          |            |  |  |

| E16          |              |                          |                      | DDC         |          |            |  |  |

| E17          |              |                          |                      | DDC         |          |            |  |  |

| E18          |              |                          |                      | IC          |          |            |  |  |

| E19          |              |                          | N                    | IC          |          |            |  |  |

| E20          |              |                          | N                    | IC          |          |            |  |  |

| F1           |              |                          | V                    | DDM         |          |            |  |  |

| F2           |              |                          |                      | 15          |          |            |  |  |

| F3           |              |                          | D                    | 29          |          |            |  |  |

| F4           |              |                          | V <sub>C</sub>       | DDC         |          |            |  |  |

| F5           |              |                          |                      | DDC         |          |            |  |  |

### Table 1. MSC7116 Signals by Ball Designator (continued)

|        | Signal Names |                          |                      |             |          |            |  |  |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|

| Number |              | S                        | oftware Controlle    | ed          | Hardware | Controlled |  |  |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |

| N10    |              |                          | G                    | ND          |          | ·          |  |  |  |

| N11    |              |                          | G                    | ND          |          |            |  |  |  |

| N12    |              |                          | G                    | ND          |          |            |  |  |  |

| N13    |              |                          | G                    | ND          |          |            |  |  |  |

| N14    |              |                          | G                    | ND          |          |            |  |  |  |

| N15    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |

| N16    |              |                          | V <sub>E</sub>       | DC          |          |            |  |  |  |

| N17    |              |                          | V <sub>E</sub>       | DDC         |          |            |  |  |  |

| N18    |              |                          |                      | KIN         |          |            |  |  |  |

| N19    | GPI          | A15                      | ĪRQ14                | GPOA15      | S        | CL         |  |  |  |

| N20    |              |                          | V <sub>S</sub>       | SPLL        |          |            |  |  |  |

| P1     |              |                          |                      | 7           |          |            |  |  |  |

| P2     |              |                          | D                    | 17          |          |            |  |  |  |

| P3     |              |                          | D                    | 16          |          |            |  |  |  |

| P4     |              |                          | V <sub>C</sub>       | DM          |          |            |  |  |  |

| P5     |              |                          |                      | DM          |          |            |  |  |  |

| P6     |              |                          |                      | DM          |          |            |  |  |  |

| P7     |              |                          |                      | ND          |          |            |  |  |  |

| P8     |              |                          | G                    | ND          |          |            |  |  |  |

| P9     |              |                          | G                    | ND          |          |            |  |  |  |

| P10    |              |                          | G                    | ND          |          |            |  |  |  |

| P11    |              |                          | G                    | ND          |          |            |  |  |  |

| P12    |              |                          | G                    | ND          |          |            |  |  |  |

| P13    |              |                          | G                    | ND          |          |            |  |  |  |

| P14    |              |                          | G                    | ND          |          |            |  |  |  |

| P15    |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |  |

| P16    |              |                          |                      | DIO         |          |            |  |  |  |

| P17    |              |                          |                      | DDC         |          |            |  |  |  |

| P18    |              |                          |                      | ESET        |          |            |  |  |  |

| P19    |              |                          | TP                   | SEL         |          |            |  |  |  |

| P20    |              |                          | V <sub>DI</sub>      | PLL         |          |            |  |  |  |

| R1     |              |                          |                      | ND          |          |            |  |  |  |

| R2     |              |                          | D                    | 19          |          |            |  |  |  |

| R3     |              |                          | D                    | 18          |          |            |  |  |  |

| R4     |              |                          | V <sub>E</sub>       | DM          |          |            |  |  |  |

| R5     |              |                          |                      | DM          |          |            |  |  |  |

Table 1. MSC7116 Signals by Ball Designator (continued)

|        |              |                          | Signa                | l Names     |          |            |  |

|--------|--------------|--------------------------|----------------------|-------------|----------|------------|--|

| Number |              | S                        | oftware Control      | ed          | Hardware | Controlled |  |

|        | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |

| V18    | GPI          | A24                      | IRQ24                | GPOA24      | TX_      | _EN        |  |

| V19    |              | rese                     | rved                 |             | CF       | RS         |  |

| V20    |              |                          | -                    | TDI         |          |            |  |

| W1     |              |                          | C                    | SND         |          |            |  |

| W2     |              |                          | V                    | ,<br>DDM    |          |            |  |

| W3     |              |                          | ,                    | A12         |          |            |  |

| W4     |              |                          |                      | A8          |          |            |  |

| W5     |              |                          |                      | A7          |          |            |  |

| W6     |              |                          |                      | A6          |          |            |  |

| W7     |              |                          |                      | A3          |          |            |  |

| W8     |              |                          |                      | NC          |          |            |  |

| W9     | GPI          | A17                      | ĪRQ13                | GPOA17      | EVNT1    | CLKO       |  |

| W10    | ВМО          | GPI                      | C14                  | GPOC14      | EVI      | NT2        |  |

| W11    | GPI          | A10                      | ĪRQ5                 | GPOA10      | TORFS    |            |  |

| W12    | GP           | IA7                      | ĪRQ7                 | GPOA7       | TOTFS    |            |  |

| W13    | GP           | IA3                      | ĪRQ8                 | GPOA3       | T1RD     |            |  |

| W14    | GP           | rIA1                     | ĪRQ10                | GPOA1       | T1TFS    |            |  |

| W15    |              | GPID4                    |                      | GPOD4       | TXD2     | reserved   |  |

| W16    | GPI          | A27                      | ĪRQ18                | GPOA27      | RXD3     | reserved   |  |

| W17    | GPI          | A19                      | ĪRQ19                | GPOA19      | TX       | D1         |  |

| W18    | GPI          | A23                      | ĪRQ23                | GPOA23      | TXCLK or | r REFCLK   |  |

| W19    | GPI          | A26                      | ĪRQ26                | GPOA26      | RX_      | _ER        |  |

| W20    | H8BIT        |                          | reserved             |             | MI       | OC .       |  |

| Y1     |              |                          | V                    | DDM         |          |            |  |

| Y2     |              |                          |                      | GND         |          |            |  |

| Y3     |              |                          |                      | A9          |          |            |  |

| Y4     |              |                          |                      | A1          |          |            |  |

| Y5     |              |                          |                      | A0          |          |            |  |

| Y6     |              |                          |                      | A4          |          |            |  |

| Y7     |              |                          | E                    | BA1         |          |            |  |

| Y8     | rese         | rved                     | NMI                  |             | reserved |            |  |

| Y9     | BM1          | GPI                      | C15                  | GPOC15      | EVI      | NT3        |  |

| Y10    | GPI          | A11                      | ĪRQ4                 | GPOA11      | TOF      | RCK        |  |

| Y11    |              | GPIA9                    |                      | GPOA9       | T0       | RD         |  |

| Y12    |              | GPIA6                    |                      | GPOA6       | T0       | TD         |  |

| Y13    | GP           | IA5                      | ĪRQ0                 | GPOA5       | T1F      | RCK        |  |

#### rical Characteristics

#### Table 5. DC Electrical Characteristics (continued)

| Characteristic                                                            | Symbol          | Min  | Typical | Max | Unit |

|---------------------------------------------------------------------------|-----------------|------|---------|-----|------|

| Tri-state (high impedance off state) leakage current, $V_{IN} = V_{DDIO}$ | I <sub>OZ</sub> | -1.0 | 0.09    | 1   | μA   |

| Signal low input current, V <sub>IL</sub> = 0.4 V                         | ΙL              | -1.0 | 0.09    | 1   | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V                        | I <sub>H</sub>  | -1.0 | 0.09    | 1   | μA   |

| Output high voltage, I <sub>OH</sub> = -2 mA, except open drain pins      | V <sub>OH</sub> | 2.0  | 3.0     | _   | V    |

| Output low voltage, I <sub>OL</sub> = 5 mA                                | V <sub>OL</sub> | _    | 0       | 0.4 | V    |

| Typical power at 266 MHz <sup>5</sup>                                     | Р               | _    | 293.0   | _   | mW   |

Notes: 1. The value of V<sub>DDM</sub> at the MSC7116 device must remain within 50 mV of V<sub>DDM</sub> at the DRAM device at all times.

- V<sub>REF</sub> must be equal to 50% of V<sub>DDM</sub> and track V<sub>DDM</sub> variations as measured at the receiver. Peak-to-peak noise must not exceed ±2% of the DC value.

- V<sub>TT</sub> is not applied directly to the MSC7116 device. It is the level measured at the far end signal termination. It should be equal

to V<sub>REF</sub>. This rail should track variations in the DC level of V<sub>REF</sub>.

- Output leakage for the memory interface is measured with all outputs disabled, 0 V ≤ V<sub>OUT</sub> ≤ V<sub>DDM</sub>.

- 5. The core power values were measured.using a standard EFR pattern at typical conditions (25°C, 300 MHz, 1.2 V core).

#### **Table 6** lists the DDR DRAM capacitance.

#### **Table 6. DDR DRAM Capacitance**

| Parameter/Condition                     | Symbol          | Max | Unit |

|-----------------------------------------|-----------------|-----|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub> | 30  | pF   |

| Delta input/output capacitance: DQ, DQS |                 | 30  | pF   |

Note: These values were measured under the following conditions:

- $V_{DDM} = 2.5 V \pm 0.125 V$

- f = 1 MHz

- T<sub>A</sub> = 25°C

- $V_{OUT} = V_{DDM}/2$

- V<sub>OUT</sub> (peak to peak) = 0.2 V

#### 2.5.2 Configuring Clock Frequencies

This section describes important requirements for configuring clock frequencies in the MSC7116 device when using the PLL block. To configure the device clocking, you must program four fields in the Clock Control Register (CLKCTL):

- *PLLDVF field*. Specifies the PLL division factor (PLLDVF + 1) to divide the input clock frequency F<sub>CLKIN</sub>. The output of the divider block is the input to the multiplier block.

- *PLLMLTF field.* Specifies the PLL multiplication factor (PLLMLTF + 1). The output from the multiplier block is the loop frequency F<sub>LOOP</sub>.

- RNG field. Selects the available PLL frequency range for F<sub>VCO</sub>, either F<sub>LOOP</sub> when the RNG bit is set (1) or F<sub>LOOP</sub>/2 when the RNG bit is cleared (0).

- CKSEL field. Selects  $F_{CLKIN}$ ,  $F_{VCO}$ , or  $F_{VCO}/2$  as the source for the core clock.

There are restrictions on the frequency range permitted at the beginning of the multiplication portion of the PLL that affect the allowable values for the PLLDVF and PLLMLTF fields. The following sections define these restrictions and provide guidelines to configure the device clocking when using the PLL. Refer to the Clock and Power Management chapter in the *MSC711x Reference Manual* for details on the clock programming model.

#### 2.5.2.1 PLL Multiplier Restrictions

There are two restrictions for correct usage of the PLL block:

- The input frequency to the PLL multiplier block (that is, the output of the divider) must be in the range 10–25 MHz.

- The output frequency of the PLL multiplier must be in the range 266–532 MHz.

When programming the PLL for a desired output frequency using the PLLDVF, PLLMLTF, and RNG fields, you must meet these constraints.

#### 2.5.2.2 Input Division Factors and Corresponding CLKIN Frequency Range

The value of the PLLDVF field determines the allowable CLKIN frequency range, as shown in **Table 9**.

Table 9. CLKIN Frequency Ranges by Divide Factor Value

| PLLDVF<br>Field Value | Input Divide<br>Factor | CLKIN Frequency Range | Comments             |

|-----------------------|------------------------|-----------------------|----------------------|

| 0x00                  | 1                      | 10 to 25 MHz          | Input Division by 1  |

| 0x01                  | 2                      | 20 to 50 MHz          | Input Division by 2  |

| 0x02                  | 3                      | 30 to 75 MHz          | Input Division by 3  |

| 0x03                  | 4                      | 40 to 100 MHz         | Input Division by 4  |

| 0x04                  | 5                      | 50 to 100 MHz         | Input Division by 5  |

| 0x05                  | 6                      | 60 to 100 MHz         | Input Division by 6  |

| 0x06                  | 7                      | 70 to 100 MHz         | Input Division by 7  |

| 0x07                  | 8                      | 80 to 100 MHz         | Input Division by 8  |

| 0x08                  | 9                      | 90 to 100 MHz         | Input Division by 9  |

| 0x09                  | 10                     | 100 MHz               | Input Division by 10 |

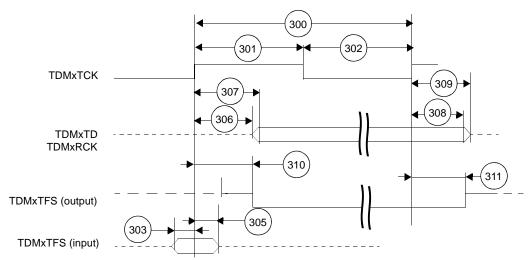

Figure 9. TDM Transmit Signals

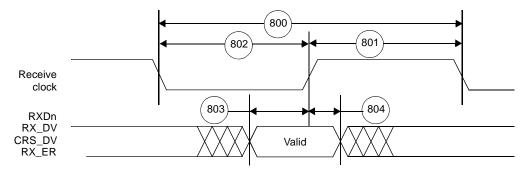

### 2.5.6 Ethernet Timing

### 2.5.6.1 Receive Signal Timing

**Table 21. Receive Signal Timing**

| No. | Characteristics                                                                                       | Min           | Max          | Unit          |

|-----|-------------------------------------------------------------------------------------------------------|---------------|--------------|---------------|

| 800 | Receive clock period:  • MII: RXCLK (max frequency = 25 MHz)  • RMII: REFCLK (max frequency = 50 MHz) | 40<br>20      | _            | ns<br>ns      |

| 801 | Receive clock pulse width high—as a percent of clock period  • MII: RXCLK  • RMII: REFCLK             | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 802 | Receive clock pulse width low—as a percent of clock period:  • MII: RXCLK  • RMII: REFCLK             | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 803 | RXDn, RX_DV, CRS_DV, RX_ER to receive clock rising edge setup time                                    | 4             | _            | ns            |

| 804 | Receive clock rising edge to RXDn, RX_DV, CRS_DV, RX_ER hold time                                     | 2             | _            | ns            |

Figure 10. Ethernet Receive Signal Timing

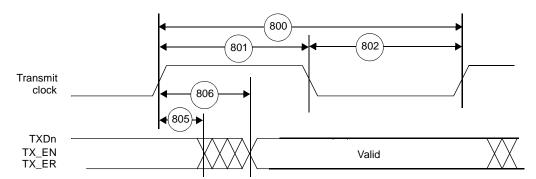

### 2.5.6.2 Transmit Signal Timing

#### **Table 22. Transmit Signal Timing**

| No. | Characteristics                                                                            | Min           | Max          | Unit          |

|-----|--------------------------------------------------------------------------------------------|---------------|--------------|---------------|

| 800 | Transmit clock period:  • MII: TXCLK  • RMII: REFCLK                                       | 40<br>20      | _            | ns<br>ns      |

| 801 | Transmit clock pulse width high—as a percent of clock period  • MII: RXCLK  • RMII: REFCLK | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 802 | Transmit clock pulse width low—as a percent of clock period:  • MII: RXCLK  • RMII: REFCLK | 35<br>14<br>7 | 65<br>—<br>— | %<br>ns<br>ns |

| 805 | Transmit clock to TXDn, TX_EN, TX_ER invalid                                               | 4             | _            | ns            |

| 806 | Transmit clock to TXDn, TX_EN, TX_ER valid                                                 | _             | 14           | ns            |

Figure 11. Ethernet Receive Signal Timing

### 2.5.6.3 Asynchronous Input Signal Timing

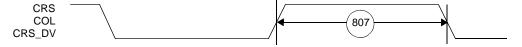

**Table 23. Asynchronous Input Signal Timing**

| No. | Characteristics                                                                                                      | Min      | Max | Unit     |

|-----|----------------------------------------------------------------------------------------------------------------------|----------|-----|----------|

| 807 | MII: CRS and COL minimum pulse width (1.5 × TXCLK period)     RMII: CRS_DV minimum pulse width (1.5 x REFCLK period) | 60<br>30 | _   | ns<br>ns |

Figure 12. Asynchronous Input Signal Timing

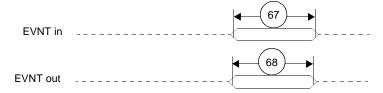

### 2.5.11 Event Timing

**Table 29. EVNT Signal Timing**

| Number                |                                                                                          | Characteristics | Туре                      | Min                  |  |

|-----------------------|------------------------------------------------------------------------------------------|-----------------|---------------------------|----------------------|--|

| 67                    |                                                                                          | EVNT as input   | Asynchronous              | 1.5 × APBCLK periods |  |

| 68                    |                                                                                          | EVNT as output  | Synchronous to core clock | 1 APBCLK period      |  |

| Notes: 1.<br>2.<br>3. | 2. Direction of the EVNT signal is configured through the GPIO and Event port registers. |                 |                           |                      |  |

Figure 24 shows the signal behavior of the EVNT pins.

Figure 24. EVNT Pin Timing

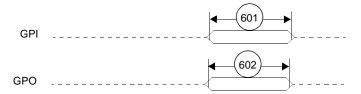

#### 2.5.12 GPIO Timing

Table 30. GPIO Signal Timing 1,2,3

| Number | Characteristics                  | Туре                      | Min                             |

|--------|----------------------------------|---------------------------|---------------------------------|

| 601    | GPI <sup>4.5</sup>               | Asynchronous              | 1.5 × APBCLK periods            |

| 602    | GPO <sup>5</sup>                 | Synchronous to core clock | 1 APBCLK period                 |

| 603    | Port A edge-sensitive interrupt  | Asynchronous              | 1.5 × APBCLK periods            |

| 604    | Port A level-sensitive interrupt | Asynchronous              | 3 × APBCLK periods <sup>6</sup> |

Notes: 1. Refer to Table 27 for a definition of the APBCLK period.

- 2. Direction of the GPIO signal is configured through the GPIO port registers.

- 3. Refer to **Section 1.5** for details on GPIO pin functionality.

- 4. GPI data is synchronized to the APBCLK internally and the minimum listed is the capability of the hardware to capture data into a register when the GPADR is read. The specification is not tested due to the asynchronous nature of the input and dependence on the state of the DSP core. It is guaranteed by design.

- 5. The output signals cannot toggle faster than 75 MHz.

- Level-sensitive interrupts should be held low until the system determines (via the service routine) that the interrupt is acknowledged.

Figure 25 shows the signal behavior of the GPI/GPO pins.

Figure 25. GPI/GPO Pin Timing

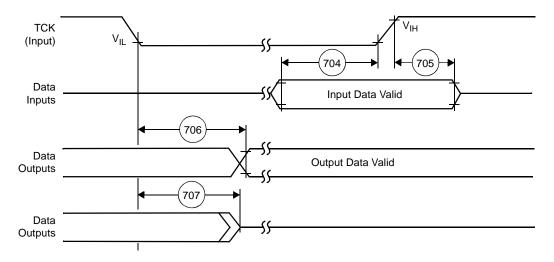

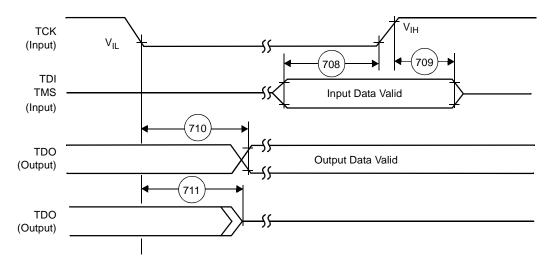

Figure 27. Boundary Scan (JTAG) Timing Diagram

Figure 28. Test Access Port Timing Diagram

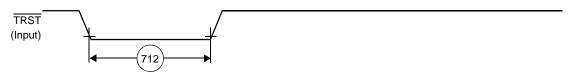

Figure 29. TRST Timing Diagram

## 3 Hardware Design Considerations

This section described various areas to consider when incorporating the MSC7116 device into a system design.

### 3.1 Thermal Design Considerations

An estimation of the chip-junction temperature, T<sub>I</sub>, in °C can be obtained from the following:

$$T_{J} = T_{A} + (R_{\mathbf{Q}JA} \times P_{D})$$

Eqn. 1

where

$T_A$  = ambient temperature near the package (°C)

$R_{AIA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D = P_{INT} + P_{I/O} = power dissipation in the package (W)$

$P_{INT} = I_{DD} \times V_{DD} = internal power dissipation (W)$

$P_{I/O}$  = power dissipated from device on output pins (W)

The power dissipation values for the MSC7116 are listed in **Table 4**. The ambient temperature for the device is the air temperature in the immediate vicinity that would cool the device. The junction-to-ambient thermal resistances are JEDEC standard values that provide a quick and easy estimation of thermal performance. There are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. The value that more closely approximates a specific application depends on the power dissipated by other components on the printed circuit board (PCB). The value obtained using a single layer board is appropriate for tightly packed PCB configurations. The value obtained using a board with internal planes is more appropriate for boards with low power dissipation (less than 0.02 W/cm<sup>2</sup> with natural convection) and well separated components. Based on an estimation of junction temperature using this technique, determine whether a more detailed thermal analysis is required. Standard thermal management techniques can be used to maintain the device thermal junction temperature below its maximum. If T<sub>J</sub> appears to be too high, either lower the ambient temperature or the power dissipation of the chip.

You can verify the junction temperature by measuring the case temperature using a small diameter thermocouple (40 gauge is recommended) or an infrared temperature sensor on a spot on the device case. Use the following equation to determine T<sub>I</sub>:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Eqn. 2

where

$T_T$  = thermocouple (or infrared) temperature on top of the package (°C)

$\Psi_{IT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

### 3.2 Power Supply Design Considerations

This section outlines the MSC7116 power considerations: power supply, power sequencing, power planes, decoupling, power supply filtering, and power consumption. It also presents a recommended power supply design and options for low-power consumption. For information on AC/DC electrical specifications and thermal characteristics, refer to **Section 2**.

#### 3.2.1 Power Supply

The MSC7116 requires four input voltages, as shown in **Table 32**.

Table 32. MSC7116 Voltages

| Voltage   | Symbol            | Value  |

|-----------|-------------------|--------|

| Core      | V <sub>DDC</sub>  | 1.2 V  |

| Memory    | $V_{DDM}$         | 2.5 V  |

| Reference | V <sub>REF</sub>  | 1.25 V |

| I/O       | V <sub>DDIO</sub> | 3.3 V  |

You should supply the MSC7116 core voltage via a variable switching supply or regulator to allow for compatibility with possible core voltage changes on future silicon revisions. The core voltage is supplied with 1.2 V (+5% and -10%) across  $V_{DDC}$  and GND and the I/O section is supplied with 3.3 V (±10%) across  $V_{DDIO}$  and GND. The memory and reference voltages supply the DDR memory controller block. The memory voltage is supplied with 2.5 V across  $V_{DDM}$  and GND. The reference voltage is supplied across  $V_{REF}$  and GND and must be between  $0.49 \times V_{DDM}$  and  $0.51 \times V_{DDM}$ . Refer to the JEDEC standard JESD8 (Stub Series Terminated Logic for 2.5 Volts (STTL\_2)) for memory voltage supply requirements.

#### 3.2.2 Power Sequencing

One consequence of multiple power supplies is that the voltage rails ramp up at different rates when power is initially applied. The rates depend on the power supply, the type of load on each power supply, and the way different voltages are derived. It is extremely important to observe the power up and power down sequences at the board level to avoid latch-up, forward biasing of ESD devices, and excessive currents, which all lead to severe device damage.

**Note:** There are five possible power-up/power-down sequence cases. The first four cases listed in the following sections are recommended for new designs. The fifth case is not recommended for new designs and must be carefully evaluated for current spike risks based on actual information for the specific application.

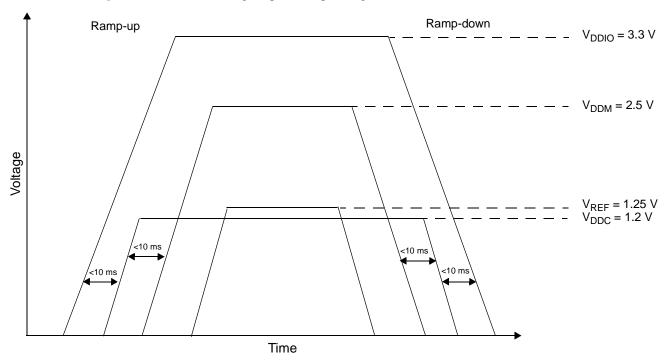

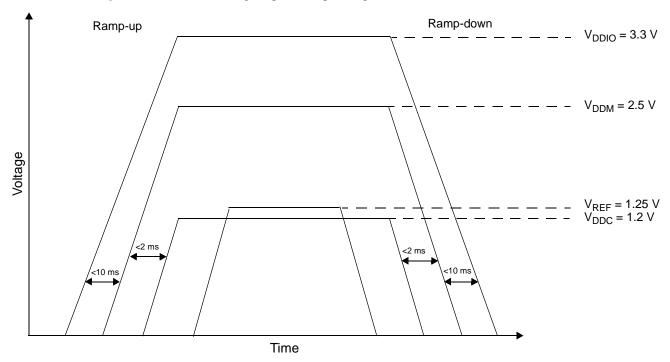

#### 3.2.2.1 Case 1

The power-up sequence is as follows:

- 1. Turn on the V<sub>DDIO</sub> (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn on the  $V_{DDM}$  (2.5 V) supply third.

- 4. Turn on the  $V_{REF}$  (1.25 V) supply fourth (last).

The power-down sequence is as follows:

- 1. Turn off the  $V_{REF}$  (1.25 V) supply first.

- 2. Turn off the  $V_{DDM}$  (2.5 V) supply second.

- 3. Turn off the  $V_{DDC}$  (1.2 V) supply third.

- 4. Turn of the V<sub>DDIO</sub> (3.3 V) supply fourth (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down of V<sub>DDIO</sub> and V<sub>DDC</sub> is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 10 ms for power-up and power-down.

- Refer to **Figure 30** for relative timing for power sequencing case 1.

Figure 30. Voltage Sequencing Case 1

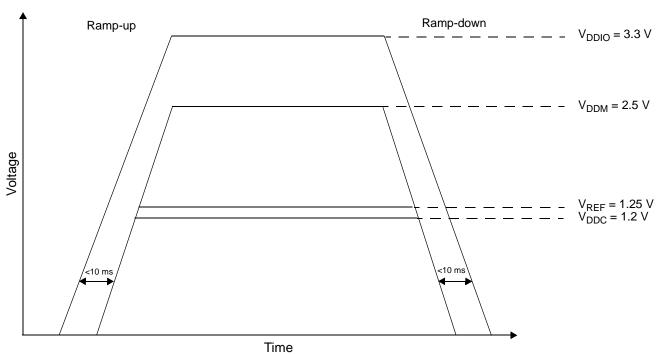

#### 3.2.2.4 Case 4

The power-up sequence is as follows:

- 1. Turn on the V<sub>DDIO</sub> (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V),  $V_{DDM}$  (2.5 V), and  $V_{REF}$  (1.25 V) supplies simultaneously (second).

**Note:** Make sure that the time interval between the ramp-up of  $V_{DDIO}$  and  $V_{DDC}$  is less than 10 ms.

The power-down sequence is as follows:

- 1. Turn off the  $V_{DDC}$  (1.2 V),  $V_{REF}$  (1.25 V), and  $V_{DDM}$  (2.5 V) supplies simultaneously (first).

- 2. Turn of the  $V_{DDIO}$  (3.3 V) supply last.

Use the following guidelines:

- Make sure that the time interval between the ramp-up or ramp-down time for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 10 ms for power-up and power-down.

- Refer to **Figure 33** for relative timing for Case 4.

Figure 33. Voltage Sequencing Case 4

MSC7116 Data Sheet, Rev. 13

### 3.2.2.5 Case 5 (not recommended for new designs)

The power-up sequence is as follows:

- 1. Turn on the V<sub>DDIO</sub> (3.3 V) supply first.

- 2. Turn on the  $V_{DDM}$  (2.5 V) supply second.

- 3. Turn on the  $V_{DDC}$  (1.2 V) supply third.

- 4. Turn on the  $V_{REF}$  (1.25 V) supply fourth (last).

**Note:** Make sure that the time interval between the ramp-up of  $V_{DDIO}$  and  $V_{DDM}$  is less than 10 ms.

The power-down sequence is as follows:

- 1. Turn off the  $V_{REF}$  (1.25 V) supply first.

- 2. Turn off the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn off the  $V_{DDM}$  (2.5 V) supply third.

- 4. Turn of the  $V_{DDIO}$  (3.3 V) supply fourth (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down of V<sub>DDIO</sub> and V<sub>DDM</sub> is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 2 ms for power-up and power-down.

- Refer to **Figure 34** for relative timing for power sequencing case 5.

Figure 34. Voltage Sequencing Case 5

Note: Cases 1, 2, 3, and 4 are recommended for system design. Designs that use Case 5 may have large current spikes on the V<sub>DDM</sub> supply at startup and is not recommended for most designs. If a design uses case 5, it must accommodate the potential current spikes. Verify risks related to current spikes using actual information for the specific application.

#### 3.2.3 Power Planes

Each power supply pin ( $V_{DDC}$ ,  $V_{DDM}$ , and  $V_{DDO}$ ) should have a low-impedance path to the board power supply. Each GND pin should be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on the device. The MSC7116  $V_{DDC}$  power supply pins should be bypassed to ground using decoupling capacitors. The capacitor leads and associated printed circuit traces connecting to device power pins and GND should be kept to less than half an inch per capacitor lead. A minimum four-layer board that employs two inner layers as power and GND planes is recommended. See **Section 3.5** for DDR Controller power guidelines.

#### 3.2.4 Decoupling

Both the I/O voltage and core voltage should be decoupled for switching noise. For I/O decoupling, use standard capacitor values of  $0.01~\mu F$  for every two to three voltage pins. For core voltage decoupling, use two levels of decoupling. The first level should consist of a  $0.01~\mu F$  high frequency capacitor with low effective series resistance (ESR) and effective series inductance (ESL) for every two to three voltage pins. The second decoupling level should consist of two bulk/tantalum decoupling capacitors, one  $10~\mu F$  and one  $47~\mu F$ , (with low ESR and ESL) mounted as closely as possible to the MSC7116 voltage pins. Additionally, the maximum drop between the power supply and the DSP device should be 15~mV at 1~A.

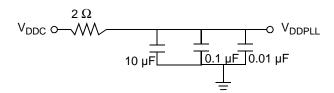

#### 3.2.5 PLL Power Supply Filtering

The MSC7116  $V_{DDPLL}$  power signal provides power to the clock generation PLL. To ensure stability of the internal clock, the power supplied to this pin should be filtered with capacitors that have low and high frequency filtering characteristics.  $V_{DDPLL}$  can be connected to  $V_{DDC}$  through a 2  $\Omega$  resistor.  $V_{SSPLL}$  can be tied directly to the GND plane. A circuit similar to the one shown in **Figure 35** is recommended. The PLL loop filter should be placed as closely as possible to the  $V_{DDPLL}$  pin (which are located on the outside edge of the silicon package) to minimize noise coupled from nearby circuits. The 0.01  $\mu$ F capacitor should be closest to  $V_{DDPLL}$ , followed by the 0.1  $\mu$ F capacitor, the 10  $\mu$ F capacitor, and finally the 2- $\Omega$  resistor to  $V_{DDC}$ . These traces should be kept short.

Figure 35. PLL Power Supply Filter Circuits

### 3.2.6 Power Consumption

You can reduce power consumption in your design by controlling the power consumption of the following regions of the device:

- Extended core. Use the SC1400 Stop and Wait modes by issuing a stop or wait instruction.

- Clock synthesis module. Disable the PLL, timer, watchdog, or DDR clocks or disable the CLKO pin.

- AHB subsystem. Freeze or shut down the AHB subsystem using the GPSCTL[XBR HRQ] bit.

- Peripheral subsystem. Halt the individual on-device peripherals such as the DDR memory controller, Ethernet MAC, HDI16, TDM, UART, I<sup>2</sup>C, and timer modules.

For details, see the "Clocks and Power Management" chapter of the MSC711x Reference Manual.

When booting from a power-on reset, the HDI16 is additionally configurable as follows:

- 8- or 16-bit mode as specified by the H8BIT pin.

- Data strobe as specified by the HDSP and HDDS pins.

These pins are sampled only on the deassertion of power-on reset. During a boot from a hard reset, the configuration of these pins is unaffected.

**Note:** When the HDI16 is used for booting or other purposes, bit 0 is the least significant bit and not the most significant bit as for other DSP products.

#### 3.4.3.2 I<sup>2</sup>C Boot

When the MSC7116 device is configured to boot from the  $I^2C$  port, the boot program configures the GPIO pins for  $I^2C$  operation. Then the MSC7116 device initiates accesses to the  $I^2C$  module, downloading data to the MSC7116 device. The  $I^2C$  interface is configured as follows:

- PLL is disabled and bypassed so that the I<sup>2</sup>C module is clocked with the IPBus clock.

- I<sup>2</sup>C interface operates in master mode and polling is used.

- EPROM operates in slave mode.

- Clock divider is set to 128.

- Address of slave during boot is 0xA0.

The IPBus clock is internally divided to generate the bit clock, as follows:

- CLKIN must be a maximum of 100 MHz

- PLL is bypassed.

- IPBus clock = CLKIN/2 is a maximum of 50 MHz.

- I<sup>2</sup>C bit clock must be less than or equal to:

- IPBus clock/I<sup>2</sup>C clock divider

- 50 MHz (max)/128

- 390.6 KHz

This satisfies the maximum clock rate requirement of 400 kbps for the  $I^2C$  interface. For details on the boot procedure, see the "Boot Program" chapter of the MSC711x Reference Manual.

#### 3.4.3.3 SPI Boot

When the MSC7116 device is configured to boot from the SPI port, the boot program configures the GPIO pins for SPI operation. Then the MSC7116 device initiates accesses to the SPI module, downloading data to the MSC7116 device. When the SPI routines run in the boot ROM, the MSC7116 is always configured as the SPI master. Booting through the SPI is supported for serial EEPROM devices and serial Flash devices. When a READ\_ID instruction is issued to the serial memory device and the device returns a value of 0x00 or 0xFF, the routines for accessing a serial EEPROM are used, at a maximum frequency of 4 Mbps. Otherwise, the routines for accessing a serial Flash are used, and they can run at faster speeds. Booting is performed through one of two sets of pins:

- Main set: BM[2–3], HA3, and HCS2, which allow use of the PLL.

- Alternate set: UTXD, URXD, SDA, and SCL, which cannot be used with the PLL.

In either configuration, an error during SPI boot is flagged on the EVNT3 pin. For details on the boot procedure, see the "Boot Program" chapter of the *MSC711x Reference Manual*.

### 3.5 DDR Memory System Guidelines

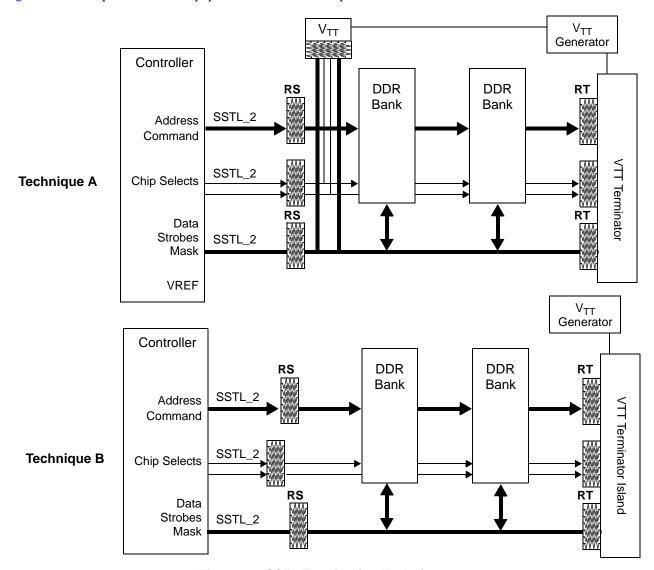

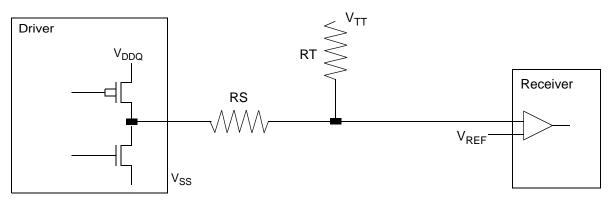

MSC7116 devices contain a memory controller that provides a glueless interface to external double data rate (DDR) SDRAM memory modules with Class 2 Series Stub Termination Logic 2.5 V (SSTL\_2). There are two termination techniques, as shown in Figure 36. Technique B is the most popular termination technique.

Figure 36. SSTL Termination Techniques

Figure 37 illustrates the power wattage for the resistors. Typical values for the resistors are as follows:

- $RS = 22 \Omega$

- $RT = 24 \Omega$

Figure 37. SSTL Power Value

#### 3.5.1 V<sub>REF</sub> and V<sub>TT</sub> Design Constraints

$V_{TT}$  and  $V_{REF}$  are isolated power supplies at the same voltage, with  $V_{TT}$  as a high current power source. This section outlines the voltage supply design needs and goals:

- Minimize the noise on both rails.

- V<sub>TT</sub> must track variation in the V<sub>REF</sub> DC offsets. Although they are isolated supplies, one possible solution is to use a single IC to generate both signals.

- Both references should have minimal drift over temperature and source supply.

- It is important to minimize the noise from coupling onto V<sub>REF</sub> as follows:

- Isolate V<sub>REF</sub> and shield it with a ground trace.

- Use 15–20 mm track.

- Use 20–30 mm clearance between other traces for isolating.

- Use the outer layer route when possible.

- Use distributed decoupling to localize transient currents and return path and decouple with an inductance less than 3 nH.

- Max source/sink transient currents of up to 1.8 A for a 32-bit data bus.

- Use a wide island trace on the outer layer:

- Place the island at the end of the bus.

- Decouple both ends of the bus.

- Use distributed decoupling across the island.

- Place SSTL termination resistors inside the V<sub>TT</sub> island and ensure a good, solid connection.

- Place the V<sub>TT</sub> regulator as closely as possible to the termination island.

- Reduce inductance and return path.

- Tie current sense pin at the midpoint of the island.

### 3.5.2 Decoupling

The DDR decoupling considerations are as follows:

- DDR memory requires significantly more burst current than previous SDRAMs.

- In the worst case, up to 64 drivers may be switching states.

- Pay special attention and decouple discrete ICs per manufacturer guidelines.

- Leverage V<sub>TT</sub> island topology to minimize the number of capacitors required to supply the burst current needs of the termination rail.

- See the Micron DesignLine publication entitled *Decoupling Capacitor Calculation for a DDR Memory Channel* (http://download.micron.com/pdf/pubs/designline/3Q00dl1-4.pdf).