Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | e200z0h                                                      |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 40MHz                                                        |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                     |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 79                                                           |

| Program Memory Size        | 384KB (384K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64K x 8                                                      |

| RAM Size                   | 36K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | A/D 30x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5603pef1mll4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 8 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering as many as 5 transfers on the transmit and receive side

- Queueing operation possible through use of the eDMA

- General purpose I/O functionality on pins when not used for SPI

### 1.5.25 Pulse width modulator (FlexPWM)

The pulse width modulator module (PWM) contains four PWM submodules, each capable of controlling a single half-bridge power stage. There are also four fault channels.

This PWM is capable of controlling most motor types: AC induction motors (ACIM), permanent magnet AC motors (PMAC), both brushless (BLDC) and brush DC motors (BDC), switched (SRM) and variable reluctance motors (VRM), and stepper motors.

The FlexPWM block implements the following features:

- 16-bit resolution for center, edge-aligned, and asymmetrical PWMs

- Maximum operating clock frequency of 120 MHz

- PWM outputs can operate as complementary pairs or independent channels

- Can accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Write protection for critical registers

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

- Individual software-control for each PWM output

- All outputs can be programmed to change simultaneously via a "Force Out" event

- PWMX pin can optionally output a third PWM signal from each submodule

- · Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual-edge capture functionality

- eDMA support with automatic reload

- 2 fault inputs

- Capture capability for PWMA, PWMB, and PWMX channels not supported

### 1.5.26 eTimer

The MPC5604P includes two eTimer modules. Each module provides six 16-bit general purpose up/down timer/counter units with the following features:

- Maximum operating clock frequency of 120 MHz

- Individual channel capability

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0–100% pulse measurement

- Rotation direction flag (Quad decoder mode)

- Maximum count rate

- External event counting: max. count rate = peripheral clock/2

- Internal clock counting: max. count rate = peripheral clock

- Counters are:

- Cascadable

- Preloadable

- Programmable count modulo

- Quadrature decode capabilities

- Counters can share available input pins

- Count once or repeatedly

- Pins available as GPIO when timer functionality not in use

## 1.5.27 Analog-to-digital converter (ADC) module

The ADC module provides the following features:

Analog part:

- 2 on-chip AD converters

- 10-bit AD resolution

- 1 sample and hold unit per ADC

- Conversion time, including sampling time, less than 1 μs (at full precision)

- Typical sampling time is 150 ns min. (at full precision)

- Differential non-linearity error (DNL) ±1 LSB

- Integral non-linearity error (INL)  $\pm 1.5$  LSB

- TUE <3 LSB

- Single-ended input signal up to 5.0 V

- The ADC and its reference can be supplied with a voltage independent from V<sub>DDIO</sub>

- The ADC supply can be equal or higher than V<sub>DDIO</sub>

- The ADC supply and the ADC reference are not independent from each other (they are internally bonded to the same pad)

- Sample times of 2 (default), 8, 64, or 128 ADC clock cycles

#### Digital part:

- $2 \times 13$  input channels including 4 channels shared between the 2 converters

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range) before results are stored in the appropriate ADC result location,

- 2 modes of operation: Normal mode or CTU control mode

- Normal mode features

- Register-based interface with the CPU: control register, status register, 1 result register per channel

#### MPC5604P Microcontroller Data Sheet, Rev. 8

|             | Pad                             |                                      |                                                          |                                                 |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|----------------------------------------------------------|-------------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                                                | Peripheral <sup>3</sup>                         | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| C[2]        | PCR[34]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[34]<br>—<br>—<br>AN[3]                              | SIUL<br>—<br>—<br><br>ADC_0                     | Input only                    | _       |                   | 30      | 45      |

| C[3]        | PCR[35]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[35]<br>CS1<br>ETC[4]<br>TXD<br>EIRQ[21]             | SIUL<br>DSPI_0<br>eTimer_1<br>LIN_1<br>SIUL     | I/O<br>O<br>I/O<br>O<br>I     | Slow    | Medium            | 10      | 16      |

| C[4]        | PCR[36]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[36]<br>CS0<br>X[1]<br>DEBUG[4]<br>EIRQ[22]          | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | /O<br> /O<br> /O<br> -<br>    | Slow    | Medium            | 5       | 11      |

| C[5]        | PCR[37]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[37]<br>SCK<br>—<br>DEBUG[5]<br>FAULT[3]<br>EIRQ[23] | SIUL<br>DSPI_0<br><br>SSCM<br>FlexPWM_0<br>SIUL | /O<br> /O<br> -<br> <br> <br> | Slow    | Medium            | 7       | 13      |

| C[6]        | PCR[38]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[38]<br>SOUT<br>B[1]<br>DEBUG[6]<br>EIRQ[24]         | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | I/O<br>I/O<br>O<br>I          | Slow    | Medium            | 98      | 142     |

| C[7]        | PCR[39]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[39]<br>—<br>A[1]<br>DEBUG[7]<br>SIN                 | SIUL<br><br>FlexPWM_0<br>SSCM<br>DSPI_0         | /O<br> -<br> -<br>            | Slow    | Medium            | 9       | 15      |

| C[8]        | PCR[40]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[40]<br>CS1<br>—<br>CS6<br>FAULT[2]                  | SIUL<br>DSPI_1<br><br>DSPI_0<br>FlexPWM_0       | I/O<br>O<br>O<br>I            | Slow    | Medium            | 91      | 130     |

| C[9]        | PCR[41]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[41]<br>CS3<br>—<br>X[3]<br>FAULT[2]                 | SIUL<br>DSPI_2<br>                              | I/O<br>O<br>I/O<br>I          | Slow    | Medium            | 84      | 123     |

| C[10]       | PCR[42]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[42]<br>CS2<br>—<br>A[3]<br>FAULT[1]                 | SIUL<br>DSPI_2<br><br>FlexPWM_0<br>FlexPWM_0    | I/O<br>O<br><br>O<br>I        | Slow    | Medium            | 78      | 111     |

Table 5. Pin muxing (continued)

|             | Pad                             |                                      |                                   |                            |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|-----------------------------------|----------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                         | Peripheral <sup>3</sup>    | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| F[9]        | PCR[89]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[89]<br>MSEO0<br>—<br>—       | SIUL<br>NEXUS_0<br>—<br>—  | I/O<br>O<br>—                 | Slow    | Fast              | _       | 23      |

| F[10]       | PCR[90]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[90]<br>EVTO<br>—<br>—        | SIUL<br>NEXUS_0<br>—       | 1/0<br>0<br>—                 | Slow    | Fast              | _       | 24      |

| F[11]       | PCR[91]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[91]<br>—<br>—<br>—<br>EVTI   | SIUL<br>—<br>—<br>NEXUS_0  | I/O<br>—<br>—<br>—<br>—       | Slow    | Medium            | _       | 25      |

| F[12]       | PCR[92]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[92]<br>ETC[3]<br>—           | SIUL<br>eTimer_1<br>—      | I/O<br>I/O<br>—               | Slow    | Medium            | —       | 106     |

| F[13]       | PCR[93]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[92]<br>ETC[4]<br>—           | SIUL<br>eTimer_1<br>—      | I/O<br>I/O<br>—               | Slow    | Medium            | _       | 112     |

| F[14]       | PCR[94]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[94]<br>TXD<br>—<br>—         | SIUL<br>LIN_1<br>—         | I/O<br>O<br>—                 | Slow    | Medium            | _       | 115     |

| F[15]       | PCR[95]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[95]<br>—<br>—<br>—<br>RXD    | SIUL<br>—<br>—<br>LIN_1    | I/O<br>—<br>—<br>—<br>—       | Slow    | Medium            | _       | 113     |

|             |                                 |                                      |                                   | Port G (12-bit)            |                               |         |                   |         |         |

| G[0]        | PCR[96]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[96]<br>F[0]<br>—<br>EIRQ[30] | SIUL<br>FCU_0<br>—<br>SIUL | I/O<br>O<br>—<br>I            | Slow    | Medium            |         | 38      |

| G[1]        | PCR[97]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[97]<br>F[1]<br><br>EIRQ[31]  | SIUL<br>FCU_0<br>—<br>SIUL | I/O<br>O<br>—<br>I            | Slow    | Medium            |         | 141     |

| G[2]        | PCR[98]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[98]<br>X[2]<br>—             | SIUL<br>FlexPWM_0<br>      | I/O<br>I/O<br>—               | Slow    | Medium            |         | 102     |

Table 5. Pin muxing (continued)

# 3 Electrical characteristics

# 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

### CAUTION

All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 6 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 6. Parameter classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

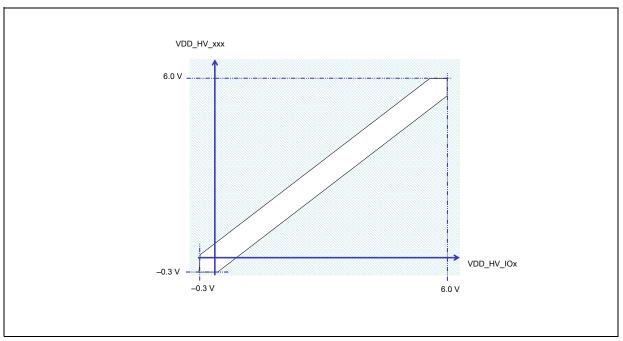

Figure 4. Power supplies constraints (–0.3 V  $\leq$  V\_{DD\_HV\_IOx}  $\leq$  6.0 V)

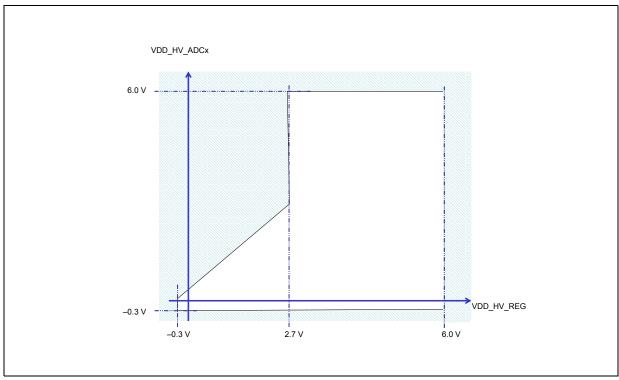

The MPC5604P supply architecture allows of having ADC supply managed independently from standard  $V_{DD_HV}$  supply. Figure 5 shows the constraints of the ADC power supply.

Figure 5. Independent ADC supply (–0.3 V  $\leq$  V\_{DD\_HV\_REG}  $\leq$  6.0 V)

# **3.4** Recommended operating conditions

| Symbol                                 |    | Devenueter                                           | Conditions                            | Value                        |                              |      |  |

|----------------------------------------|----|------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|--|

|                                        |    | Parameter                                            | Conditions                            | Min                          | Max <sup>1</sup>             | Unit |  |

| V <sub>SS</sub>                        | SR | Device ground                                        | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_HV_IOx</sub> <sup>2</sup>    | SR | 5.0 V input/output supply voltage                    | _                                     | 4.5                          | 5.5                          | V    |  |

| V <sub>SS_HV_IOx</sub>                 | SR | Input/output ground voltage                          | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_HV_FL</sub>                  | SR | 5.0 V code and data flash                            | —                                     | 4.5                          | 5.5                          | V    |  |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |  |

| V <sub>SS_HV_FL</sub>                  | SR | Code and data flash ground                           | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier                   | —                                     | 4.5                          | 5.5                          | V    |  |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |  |

| V <sub>SS_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier reference voltage | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_HV_REG</sub>                 | SR | R 5.0 V voltage regulator supply                     | —                                     | 4.5                          | 5.5                          | V    |  |

|                                        |    | voltage                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |  |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup>   | SR | 5.0 V ADC_0 supply and high                          | —                                     | 4.5                          | 5.5                          | V    |  |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | _                            |      |  |

| V <sub>SS_HV_ADC0</sub>                | SR | ADC_0 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |  |

| V <sub>DD_HV_ADC1</sub> <sup>3</sup>   | SR | 5.0 V ADC_1 supply and high                          | —                                     | 4.5                          | 5.5                          | V    |  |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | _                            |      |  |

| V <sub>SS_HV_ADC1</sub>                | SR | ADC_1 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |  |

| DD_LV_REGCOR <sup>4,5</sup>            | CC | Internal supply voltage                              | —                                     | -                            | —                            | V    |  |

| V <sub>SS_LV_REGCOR</sub> <sup>4</sup> |    | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |  |

| V <sub>DD_LV_CORx</sub> <sup>4,5</sup> | СС | Internal supply voltage                              | —                                     | _                            | —                            | V    |  |

| $V_{SS_{LV}_{CORx}}^4$                 | SR | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |  |

| T <sub>A</sub>                         | SR | Ambient temperature under bias                       | -                                     | -40                          | 125                          | °C   |  |

Table 8. Recommended operating conditions (5.0 V)

<sup>1</sup> Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_IOy</sub> - V<sub>DD\_HV\_IOx</sub> | < 100 mV.</p>

$^{3}$  The difference between ADC voltage supplies must be less than 100 mV,  $|V_{DD_{-HV}ADC1} - V_{DD_{-HV}ADC0}| < 100 mV$ .

3.5 Thermal characteristics

### 3.5.1 Package thermal characteristics

#### Table 10. Thermal characteristics for 144-pin LQFP

| Symbol             | Parameter                                              | Conditions            | Typical value | Unit |

|--------------------|--------------------------------------------------------|-----------------------|---------------|------|

| $R_{	hetaJA}$      | Thermal resistance junction-to-ambient,                | Single layer board—1s | 54.2          | °C/W |

|                    | natural convection <sup>1</sup>                        | Four layer board—2s2p | 44.4          | °C/W |

| $R_{\theta JB}$    | Thermal resistance junction-to-board <sup>2</sup>      | Four layer board—2s2p | 29.9          | °C/W |

| $R_{\theta JCtop}$ | Thermal resistance junction-to-case (top) <sup>3</sup> | Single layer board—1s | 9.3           | °C/W |

| $\Psi_{JB}$        | Junction-to-board, natural convection <sup>4</sup>     | Operating conditions  | 30.2          | °C/W |

| Ψ <sub>JC</sub>    | Junction-to-case, natural convection <sup>5</sup>      | Operating conditions  | 0.8           | °C/W |

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

- <sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

| Symbol              | Parameter                                              | Conditions            | Typical value | Unit |

|---------------------|--------------------------------------------------------|-----------------------|---------------|------|

| $R_{	hetaJA}$       | Thermal resistance junction-to-ambient,                | Single layer board—1s | 47.3          | °C/W |

|                     | natural convection <sup>1</sup>                        | Four layer board—2s2p | 35.3          | °C/W |

| $R_{\theta JB}$     | Thermal resistance junction-to-board <sup>2</sup>      | Four layer board—2s2p | 19.1          | °C/W |

| R <sub>0JCtop</sub> | Thermal resistance junction-to-case (top) <sup>3</sup> | Single layer board—1s | 9.7           | °C/W |

| $\Psi_{JB}$         | Junction-to-board, natural convection <sup>4</sup>     | Operating conditions  | 19.1          | °C/W |

| ΨJC                 | Junction-to-case, natural convection <sup>5</sup>      | Operating conditions  | 0.8           | °C/W |

Table 11. Thermal characteristics for 100-pin LQFP

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Part  | Manufacturer | Approved derivatives <sup>1</sup> |  |  |

|-------|--------------|-----------------------------------|--|--|

| BCP68 | ON Semi      | BCP68                             |  |  |

|       | NXP          | BCP68-25                          |  |  |

|       | Infineon     | BCP68-25                          |  |  |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25        |  |  |

| BC868 | NXP          | BC868                             |  |  |

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;        |  |  |

|       | NXP          | BC817-16;BC817-25                 |  |  |

| BCP56 | ST           | BCP56-16                          |  |  |

|       | Infineon     | BCP56-10;BCP56-16                 |  |  |

|       | ON Semi      | BCP56-10                          |  |  |

|       | NXP          | BCP56-10;BCP56-16                 |  |  |

#### Table 14. Approved NPN ballast components (configuration with resistor on base)

<sup>1</sup> For automotive applications please check with the appropriate transistor vendor for automotive grade certification

| Symbol                    |    | с | Parameter                                                                | Conditions                                                                                          |      | Value |      | Unit |

|---------------------------|----|---|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-------|------|------|

| Cymson                    |    | Ū |                                                                          | Contractions                                                                                        | Min  | Тур   | Max  | onne |

| V <sub>DD_LV_REGCOR</sub> | CC |   | Output voltage under maximum<br>load run supply current<br>configuration | Post-trimming                                                                                       | 1.15 | _     | 1.32 | V    |

| R <sub>B</sub>            | SR |   | External resistance on bipolar junction transistor (BJT) base            | —                                                                                                   | 18   |       | 22   | kΩ   |

| C <sub>DEC1</sub>         | SR |   | External decoupling/stability ceramic capacitor                          | BJT from Table 14. 3<br>capacitances (i.e. X7R or X8R<br>capacitors) with nominal value<br>of 10 µF | 19.5 | 30    |      | μF   |

|                           |    |   |                                                                          | BJT BC817, one capacitance of 22 $\mu$ F                                                            | 14.3 | 22    |      | μF   |

| Ded      | 144       | LQFP        | 100 LQFP  |             |  |  |

|----------|-----------|-------------|-----------|-------------|--|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[72]  | 1%        | 1%          | _         | _           |  |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[73]  | 1%        | 1%          | _         | _           |  |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[74]  | 1%        | 1%          | _         | _           |  |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[75]  | 1%        | 1%          | _         |             |  |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[76]  | 1%        | 1%          | _         | _           |  |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |  |

| PAD[107] | 20%       | 17%         | _         |             |  |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |  |

| PAD[106] | 18%       | 16%         | _         |             |  |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |  |

| PAD[105] | 16%       | 14%         | _         | _           |  |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |  |

| PAD[104] | 14%       | 13%         | _         |             |  |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |  |

| PAD[103] | 12%       | 11%         | —         |             |  |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |  |

| PAD[101] | 11%       | 9%          | _         | _           |  |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |  |

| TCK      | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |  |

| PAD[102] | 11%       | 10%         | _         | —           |  |  |

### Table 24. I/O weight (continued)

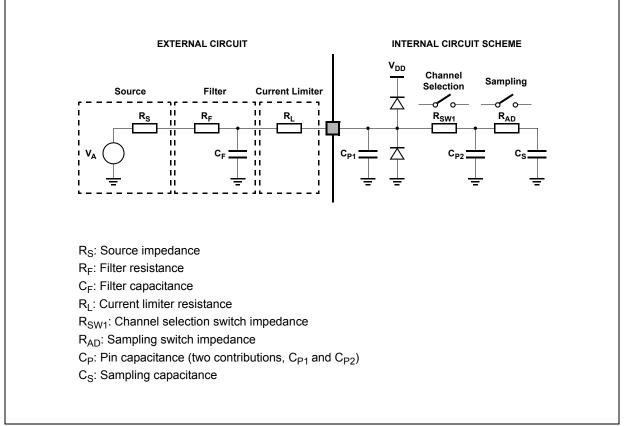

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{P2}$  being substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc \times (C_S+C_{P2}))$ ), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Equation 4 generates a constraint for external network design, in particular on resistive path.

Figure 15. Input equivalent circuit

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_{F_2}$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in Figure 15): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch closed).

| No. | Symbol C           |    | C Parameter |                             |     | Unit |     |      |

|-----|--------------------|----|-------------|-----------------------------|-----|------|-----|------|

| NO. | Symbo              | 01 | C           | Falameter                   | Min | Тур  | Мах | Unit |

| 6   | t <sub>NTDIS</sub> | СС | D           | TDI data setup time         | 6   | _    | _   | ns   |

|     | t <sub>NTMSS</sub> | CC | D           | TMS data setup time         | 6   |      | _   | ns   |

| 7   | t <sub>NTDIH</sub> | CC | D           | TDI data hold time          | 10  | _    | _   | ns   |

|     | t <sub>NTMSH</sub> | CC | D           | TMS data hold time          | 10  | _    | _   | ns   |

| 8   | t <sub>TDOV</sub>  | СС | D           | TCK low to TDO data valid   | —   | _    | 35  | ns   |

| 9   | t <sub>TDOI</sub>  | CC | D           | TCK low to TDO data invalid | 6   | _    | _   | ns   |

Table 38. Nexus debug port timing<sup>1</sup> (continued)

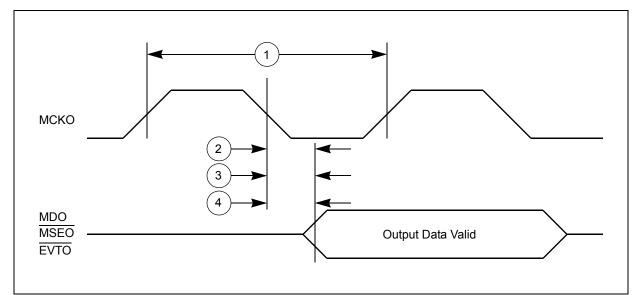

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

<sup>2</sup> MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

<sup>3</sup> Lower frequency is required to be fully compliant to standard.

Figure 24. Nexus output timing

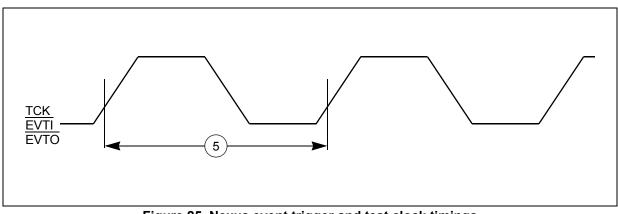

Figure 25. Nexus event trigger and test clock timings

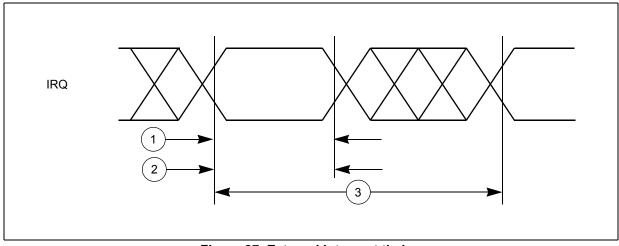

<sup>3</sup> N = ISR time to clear the flag

Figure 27. External interrupt timing

# 3.17.5 DSPI timing

| Table | 40. | DSPI | timing <sup>1</sup> |

|-------|-----|------|---------------------|

|       |     |      |                     |

| No. | o. Symbol (       |     | с | Parameter                  | Parameter Conditions                          | Va                     | Unit                   |      |

|-----|-------------------|-----|---|----------------------------|-----------------------------------------------|------------------------|------------------------|------|

| NO. | Synn              | 101 | C | Falameter                  | Conditions                                    | Min                    | Max                    | Unit |

| 1   | t <sub>SCK</sub>  | CC  | D | DSPI cycle time            | Master (MTFE = 0)                             | 60                     | —                      | ns   |

|     |                   |     |   |                            | Slave (MTFE = 0)                              | 60                     | —                      |      |

| 2   | t <sub>CSC</sub>  | CC  | D | CS to SCK delay            | _                                             | 16                     | —                      | ns   |

| 3   | t <sub>ASC</sub>  | CC  | D | After SCK delay            | —                                             | 26                     | —                      | ns   |

| 4   | t <sub>SDC</sub>  | CC  | D | SCK duty cycle             | _                                             | 0.4 * t <sub>SCK</sub> | 0.6 * t <sub>SCK</sub> | ns   |

| 5   | t <sub>A</sub>    | CC  | D | Slave access time          | SS active to SOUT valid                       | —                      | 30                     | ns   |

| 6   | t <sub>DIS</sub>  | СС  | D | Slave SOUT disable time    | SS inactive to SOUT high impedance or invalid | —                      | 16                     | ns   |

| 7   | t <sub>PCSC</sub> | CC  | D | PCSx to PCSS time —        |                                               | 13                     | —                      | ns   |

| 8   | t <sub>PASC</sub> | CC  | D | PCSS to PCSx time          | SS to PCSx time —                             |                        | —                      | ns   |

| 9   | t <sub>SUI</sub>  | CC  | D | Data setup time for inputs | Master (MTFE = 0)                             | 35                     | —                      | ns   |

|     |                   |     |   |                            | Slave                                         | 4                      | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 0)                   | 35                     | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 1)                   | 35                     | —                      | 1    |

| 10  | t <sub>HI</sub>   | CC  | D | Data hold time for inputs  | Master (MTFE = 0)                             | -5                     | —                      | ns   |

|     |                   |     |   |                            | Slave                                         | 4                      | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 0)                   | 11                     | —                      |      |

|     |                   |     |   |                            | Master (MTFE = 1, CPHA = 1)                   | -5                     | —                      | 1    |

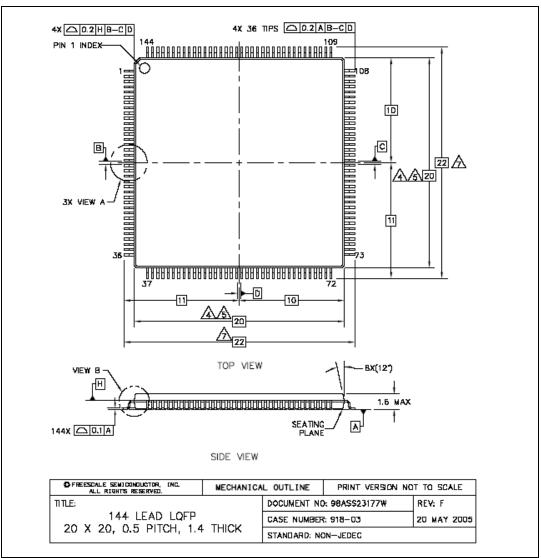

# 4 Package characteristics

# 4.1 Package mechanical data

## 4.1.1 144 LQFP mechanical outline drawing

Figure 37. 144 LQFP package mechanical drawing (part 1)

|                                                                                                                                                                                                                                                        | freescale<br>semiconductor |                     | DOCUMENT NO: 98ASS23308W |            |   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|--------------------------|------------|---|

| semiconductor                                                                                                                                                                                                                                          |                            |                     | PAGE:                    | 983        |   |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRCTLY FROM THE DOCUMENT CONTROL. REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE               | THIS DRAWING        | REV:                     | Н          |   |

| NOTES:                                                                                                                                                                                                                                                 |                            |                     |                          |            |   |

| 1. ALL DIMENSIONS ARE IN MILL                                                                                                                                                                                                                          | IMETERS.                   |                     |                          |            |   |

| 2. INTERPRET DIMENSIONS AND                                                                                                                                                                                                                            | TOLERANCES PER             | ASME Y14.5M-19      | 994.                     |            |   |

| 3 DATUMS B, C AND D TO BE                                                                                                                                                                                                                              | DETERMINED AT I            | DATUM PLANE H.      |                          |            |   |

| 4. THE TOP PACKAGE BODY SIZ<br>BY A MAXIMUM OF 0.1 MM.                                                                                                                                                                                                 | E MAY BE SMALL             | ER THAN THE BO      | ТТОМ РА                  | CKAGE SIZE |   |

| 5. DIMENSIONS DO NOT INCLUDE<br>PROTRUSION IS 0.25 mm PE<br>SIZE DIMENSIONS INCLUDING                                                                                                                                                                  | ER SIDE. THE DIMI          |                     |                          |            |   |

| 6. DIMENSION DOES NOT INCLUE<br>CAUSE THE LEAD WIDTH TO<br>AND AN ADJACENT LEAD SH                                                                                                                                                                     | EXCEED 0.35. MII           | NIMUM SPACE BET     |                          |            |   |

| 7. dimensions are determined                                                                                                                                                                                                                           | AT THE SEATING             | G PLANE, DATUM      | Α.                       |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            |                     |                          |            |   |

|                                                                                                                                                                                                                                                        |                            | I                   |                          |            |   |

| 100 LEAD LQF                                                                                                                                                                                                                                           | P                          | CASE NUMBER: 983-02 |                          |            |   |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                    |                            | STANDARD: NON-      |                          |            |   |

|                                                                                                                                                                                                                                                        |                            | PACKAGE CODE:       | 8264                     | SHEET:     | 3 |

### Figure 41. 100 LQFP package mechanical drawing (part 3)

MPC5604P Microcontroller Data Sheet, Rev. 8

|                  | Dimensions |        |        |                     |        |        |  |

|------------------|------------|--------|--------|---------------------|--------|--------|--|

| Symbol           | mm         |        |        | inches <sup>1</sup> |        |        |  |

|                  | Min        | Тур    | Max    | Min                 | Тур    | Max    |  |

| А                |            | _      | 1.600  | _                   |        | 0.0630 |  |

| A1               | 0.050      | _      | 0.150  | 0.0020              | —      | 0.0059 |  |

| A2               | 1.350      | 1.400  | 1.450  | 0.0531              | 0.0551 | 0.0571 |  |

| b                | 0.170      | 0.220  | 0.270  | 0.0067              | 0.0087 | 0.0106 |  |

| С                | 0.090      | _      | 0.200  | 0.0035              | —      | 0.0079 |  |

| D                | 15.800     | 16.000 | 16.200 | 0.6220              | 0.6299 | 0.6378 |  |

| D1               | 13.800     | 14.000 | 14.200 | 0.5433              | 0.5512 | 0.5591 |  |

| D3               | —          | 12.000 | _      | —                   | 0.4724 | —      |  |

| Е                | 15.800     | 16.000 | 16.200 | 0.6220              | 0.6299 | 0.6378 |  |

| E1               | 13.800     | 14.000 | 14.200 | 0.5433              | 0.5512 | 0.5591 |  |

| E3               | —          | 12.000 | _      | —                   | 0.4724 | —      |  |

| е                | —          | 0.500  | _      | —                   | 0.0197 | —      |  |

| L                | 0.450      | 0.600  | 0.750  | 0.0177              | 0.0236 | 0.0295 |  |

| L1               | —          | 1.000  | -      | —                   | 0.0394 | —      |  |

| k                | 0.0°       | 3.5°   | 7.0°   | 0.0°                | 3.5°   | 7.0°   |  |

| ccc <sup>2</sup> | 0.08       |        |        |                     | 0.0031 |        |  |

Table 41.

<sup>1</sup> Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

<sup>2</sup> Tolerance

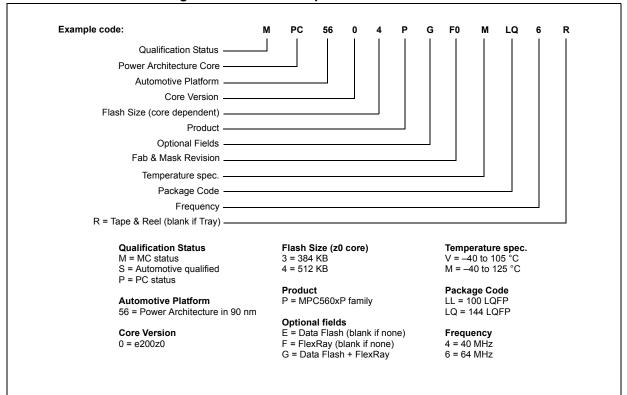

# 5 Ordering information

Figure 42. Commercial product code structure

| Revision | Date        | Substantive changes                                                                                                                                                          |  |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rev. 4   | 24-Jun-2009 | Through all document:                                                                                                                                                        |  |

|          |             | <ul> <li>Replaced all "RESET_B" occurrences with "RESET" through all document.</li> </ul>                                                                                    |  |

|          |             | <ul> <li>AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing, and<br/>DSPI Timing sections inserted again.</li> </ul>                                  |  |

|          |             | <ul> <li>Electrical parameters updated.</li> </ul>                                                                                                                           |  |

|          |             | - Electrical parameters upuateu.                                                                                                                                             |  |

|          |             | Table 2                                                                                                                                                                      |  |

|          |             | – Added row for Data Flash.                                                                                                                                                  |  |

|          |             | Table 3                                                                                                                                                                      |  |

|          |             | <ul> <li>Added a footnote regarding the decoupling capacitors.</li> </ul>                                                                                                    |  |

|          |             | Table 5                                                                                                                                                                      |  |

|          |             | – Removed the "other function" column.                                                                                                                                       |  |

|          |             | <ul> <li>Rearranged the contents.</li> </ul>                                                                                                                                 |  |

|          |             | Table 15                                                                                                                                                                     |  |

|          |             | <ul> <li>Updated definition of Condition column.</li> </ul>                                                                                                                  |  |

|          |             | Table 20                                                                                                                                                                     |  |

|          |             | <ul> <li>merged in an unique Table the power consumption data related to "Maximum<br/>mode" and "Airbag mode".</li> </ul>                                                    |  |

|          |             | Table 22                                                                                                                                                                     |  |

|          |             | <ul> <li>merged in an unique Table the power consumption data related to "Maximum<br/>mode" and "Airbag mode".</li> </ul>                                                    |  |

|          |             | Table 30                                                                                                                                                                     |  |

|          |             | – Updated the parameter definition of $\Delta$ RCMVAR.                                                                                                                       |  |

|          |             | – Removed the condition definition of $\Delta$ RCMVAR.                                                                                                                       |  |

|          |             | Table 30                                                                                                                                                                     |  |

|          |             | <ul> <li>Added t<sub>ADC_C</sub> and TUE rows.</li> </ul>                                                                                                                    |  |

|          |             | Table 31                                                                                                                                                                     |  |

|          |             | <ul> <li>Added t<sub>ADC C</sub> and TUE rows.</li> </ul>                                                                                                                    |  |

|          |             | – Removed R <sub>sw2.</sub>                                                                                                                                                  |  |

|          |             | Table 34                                                                                                                                                                     |  |

|          |             | – Added.                                                                                                                                                                     |  |

|          |             | Table 29                                                                                                                                                                     |  |

|          |             | <ul> <li>Updated and added footnotes.</li> </ul>                                                                                                                             |  |

|          |             | Section 3.17.1, "RESET pin characteristics                                                                                                                                   |  |

|          |             | <ul> <li>Replaces whole section.</li> </ul>                                                                                                                                  |  |

|          |             | Table 38                                                                                                                                                                     |  |

|          |             | <ul> <li>Renamed the "Flash (KB)" heading column in "Code Flash / Data Flash (EE) (KB)"</li> <li>Replaced the value of RAM from 32 to 36KB in the last four rows.</li> </ul> |  |

| Table 42. F | Revision | history | (continued) |

|-------------|----------|---------|-------------|

|-------------|----------|---------|-------------|

| Revision | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 7   |      | <ul> <li>Formatting and editorial changes throughout</li> <li>Removed all content referencing Junction Temperature Sensor</li> <li>Section 1, "Introduction: changed title (was: Overview); reorganized contents</li> <li>MPC5604P device comparison:</li> <li>ADC feature: changed "16 channels" to "15-channel"; added footnote to to indicate that four channels are shared between the two ADCs</li> <li>removed MPC5602P column</li> <li>indicated that data flash memory is an optional feature</li> <li>changed "dual channel" to "selectable single or dual channel support" in FlexRay footnote</li> <li>updated "eTimer" feature</li> <li>updated footnote relative to "Digital power supply" feature</li> <li>Updated MPC5604P block diagram</li> <li>Added APC5604P series block summary</li> <li>Added Section 1.5, "Feature details</li> <li>Section 2.1, "Package pinouts: removed alternate functions from pinout diagrams</li> <li>Supply pins: updated dable</li> <li>Pin muxing: added rows "B[4]" and "B[5]</li> <li>Section 3.3, "Absolute maximum ratings: added voltage specifications to titles of Figure 4 and Figure 5; in Table 7, changed row "V<sub>SS-HV</sub> / Digital Ground" to "V<sub>SS</sub> / Device Ground"; updated symbols</li> <li>Section 3.4, "Recommended operating conditions: added voltage specifications to titles of Figure 7</li> </ul> |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |      | Updated Section 3.6, "Electromagnetic interference (EMI) characteristics<br>Section 3.8.1, "Voltage regulator electrical characteristics: amended titles of Table 15 and<br>Table 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics (configuration with resistor on base):<br>updated symbol and values for V <sub>DD_LV_REGCOR</sub><br>Low voltage monitor electrical characteristics: Updated V <sub>MLVDDOK_H</sub> max value—was<br>1.15 V; is 1.145 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | Section 3.10, "DC electrical characteristics: reorganized contents<br>Updated Section 3.10.1, "NVUSRO register (includes adding<br>"NVUSRO[OSCILLATOR_MARGIN] field description" table<br>Supply current (5.0 V, NVUSRO[PAD3V5V] = 0): updated symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Revision           | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>Rev. 8 |      | <ul> <li>Section 1.5.4, "Flash memory: Changed "Data flash memory: 32-bit ECC" to "Data flash memory: 64-bit ECC"</li> <li>Figure 42 (Commercial product code structure), replaced "C = 60 MHz, 5 V" and "D = 60 MHz, 3.3 V" with respectively "C = 40 MHz, 5 V" and "D = 40 MHz, 3.3 V"</li> <li>Table 7 (Absolute maximum ratings), updated TV<sub>DD</sub> parameter, the minimum value to 3.0 V/s and the maximum value to 0.5 V/µs</li> <li>Table 5 (Pin muxing), changed the description in the column "I/O direction" from "I/O" to "O" for the following port pins: A[10] with function B[0]</li> <li>A[11] with function A[2]</li> <li>A[12] with function A[2]</li> <li>A[13] with function B[2]</li> <li>C[7] with function A[1]</li> <li>C[10] with function A[1]</li> <li>D[0] with function B[1]</li> <li>D[10] with function A[1]</li> <li>D[11] with function B[0]</li> <li>D[13] with function B[1]</li> <li>D[14] with function B[1]</li> <li>Updated Section 3.8.1, "Voltage regulator electrical characteristics</li> </ul> |

|                    |      | Added Table 25 (I/O consumption)<br>Section 3.10, DC electrical characteristics:<br>deleted references to "oscillator margin"<br>deleted subsection "NVUSRO[OSCILLATOR_MARGIN] field description"<br>Table <u>19 (DC</u> electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)), added IPU row<br>for RESET pin<br>Table <u>21 (DC</u> electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)), added IPU row<br>for RESET pin<br>Table <u>31 (ADC conversion characteristics</u> ), added V <sub>INAN</sub> entry<br>Removed "Order codes" table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 42. Revision history (continued)