# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 68                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 40K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pef0mll6 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5603P/4P series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 1.3 Device comparison

Table 1 provides a summary of different members of the MPC5604P family and their features to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                              | MPC5603P          | MPC5604P         |

|------------------------------------------------------|-------------------|------------------|

| Code flash memory (with ECC)                         | 384 KB            | 512 KB           |

| Data flash memory / EE option (with ECC)             | 64 KB (optic      | onal feature)    |

| SRAM (with ECC)                                      | 36 KB             | 40 KB            |

| Processor core                                       | 32-bit e          | 200z0h           |

| Instruction set                                      | VLE (variable le  | ength encoding)  |

| CPU performance                                      | 0–64              | MHz              |

| FMPLL (frequency-modulated phase-locked loop) module | 2                 | 2                |

| INTC (interrupt controller) channels                 | 14                | 17               |

| PIT (periodic interrupt timer)                       | 1 (includes fou   | r 32-bit timers) |

| eDMA (enhanced direct memory access) channels        | 1                 | 6                |

| FlexRay <sup>1</sup>                                 | Optiona           | I feature        |

| FlexCAN (controller area network)                    | 2 <sup>2</sup>    | 2,3              |

| Safety port                                          | Yes (via second F | FlexCAN module)  |

| FCU (fault collection unit)                          | Ye                | es               |

| CTU (cross triggering unit)                          | Ye                | es               |

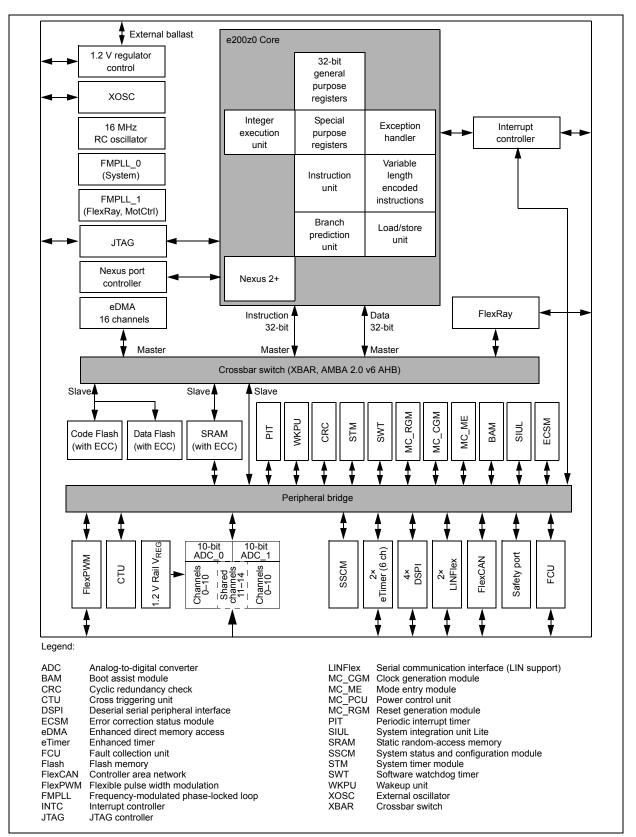

Figure 1. MPC5604P block diagram

- 32 message buffers of up to 8-bytes data length

- · Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- · Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a six-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

# 1.5.21 Safety port (FlexCAN)

The MPC5604P MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate as fast as 7.5 Mbit/s at 60 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8 bytes data length

- Can be used as a second independent CAN module

# 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

# 2 Package pinouts and signal descriptions

# 2.1 Package pinouts

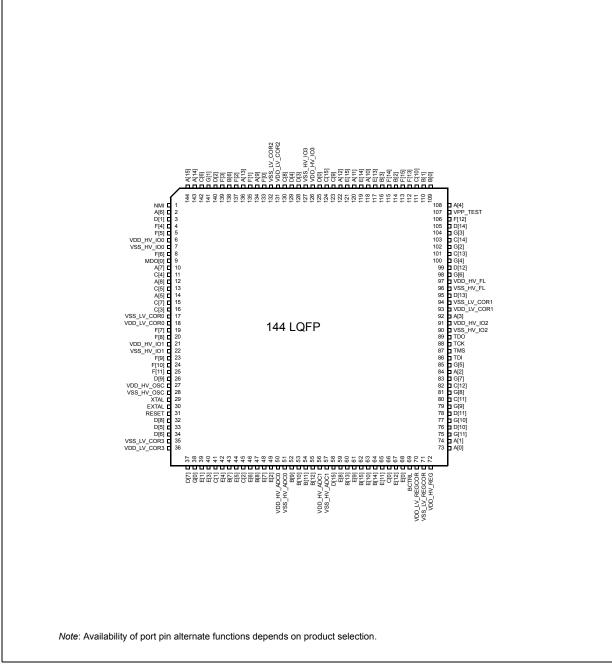

The LQFP pinouts are shown in the following figures.

Figure 2. 144-pin LQFP pinout (top view)

MPC5604P Microcontroller Data Sheet, Rev. 8

Table 5. Pin muxing

|                   | Pad                          |                                             |                                                            |                                                                |                                    | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------------|------------------------------|---------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|---------|-------------------|---------|---------|

| Port<br>pin       | configuration register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                                  | Peripheral <sup>3</sup>                                        | I/O<br>direction <sup>4</sup>      | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

|                   |                              |                                             |                                                            | Port A (16-bit)                                                |                                    |         |                   |         |         |

| A[0]              | PCR[0]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[0]<br>ETC[0]<br>SCK<br>F[0]<br>EIRQ[0]                | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | 1/0<br>1/0<br>0<br>1               | Slow    | Medium            | 51      | 73      |

| A[1]              | PCR[1]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[1]<br>ETC[1]<br>SOUT<br>F[1]<br>EIRQ[1]               | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | /O<br> /O<br>0<br>                 | Slow    | Medium            | 52      | 74      |

| A[2] <sup>6</sup> | PCR[2]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[2]<br>ETC[2]<br>—<br>A[3]<br>SIN<br>ABS[0]<br>EIRQ[2] | SIUL<br>eTimer_0<br>—<br>FlexPWM_0<br>DSPI_2<br>MC_RGM<br>SIUL | /O<br> /O<br> -<br> <br> <br> <br> | Slow    | Medium            | 57      | 84      |

| A[3] <sup>6</sup> | PCR[3]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[3]<br>ETC[3]<br>CS0<br>B[3]<br>ABS[2]<br>EIRQ[3]      | SIUL<br>eTimer_0<br>DSPI_2<br>FlexPWM_0<br>MC_RGM<br>SIUL      | /O<br> /O<br> /O<br>0<br> <br>     | Slow    | Medium            | 64      | 92      |

| A[4] <sup>6</sup> | PCR[4]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[4]<br>ETC[0]<br>CS1<br>ETC[4]<br>FAB<br>EIRQ[4]       | SIUL<br>eTimer_1<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL       | /O<br> /O<br>0<br> /O<br> <br>     | Slow    | Medium            | 75      | 108     |

| A[5]              | PCR[5]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[5]<br>CS0<br>ETC[5]<br>CS7<br>EIRQ[5]                 | SIUL<br>DSPI_1<br>eTimer_1<br>DSPI_0<br>SIUL                   | /O<br> /O<br> /O<br>0<br>          | Slow    | Medium            | 8       | 14      |

| A[6]              | PCR[6]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[6]<br>SCK<br>—<br>—<br>EIRQ[6]                        | SIUL<br>DSPI_1<br>—<br>SIUL                                    | /O<br> /O<br><br>                  | Slow    | Medium            | 2       | 2       |

| A[7]              | PCR[7]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[7]<br>SOUT<br>—<br>EIRQ[7]                            | SIUL<br>DSPI_1<br>—<br>SIUL                                    | /O<br>O<br>—<br>I                  | Slow    | Medium            | 4       | 10      |

|             | Pad                             |                                             |                                                   |                                             |                               | Pad s   | peed <sup>5</sup> | Pin               | No.     |

|-------------|---------------------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------|-------------------------------|---------|-------------------|-------------------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                         | Peripheral <sup>3</sup>                     | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | uid-ool         1 | 144-pin |

| B[10]       | PCR[26]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[26]<br>—<br>—<br>—<br>AN[12]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    | _       | _                 |                   | 53      |

| B[11]       | PCR[27]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[27]<br>—<br>—<br>—<br>AN[13]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    | _       | _                 | 37                | 54      |

| B[12]       | PCR[28]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[28]<br><br><br>AN[14]                        | SIUL<br>—<br>—<br><br>ADC_0 / ADC_1         | Input only                    | _       | _                 | 38                | 55      |

| B[13]       | PCR[29]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[29]<br>—<br>—<br>—<br>AN[0]<br>RXD           | SIUL<br>—<br>—<br>ADC_1<br>LIN_1            | Input only                    | _       | _                 | 42                | 60      |

| B[14]       | PCR[30]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[30]<br>—<br>—<br>AN[1]<br>ETC[4]<br>EIRQ[19] | SIUL<br>—<br>—<br>ADC_1<br>eTimer_0<br>SIUL | Input only                    |         | _                 | 44                | 64      |

| B[15]       | PCR[31]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[31]<br>—<br>—<br>—<br>AN[2]<br>EIRQ[20]      | SIUL<br>—<br>—<br>ADC_1<br>SIUL             | Input only                    | _       | _                 | 43                | 62      |

|             |                                 |                                             |                                                   | Port C (16-bit)                             |                               |         |                   | •                 |         |

| C[0]        | PCR[32]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[32]<br>—<br>—<br>—<br>AN[3]                  | SIUL<br>—<br>—<br>—<br>ADC_1                | Input only                    | _       |                   | 45                | 66      |

| C[1]        | PCR[33]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[33]<br>—<br>—<br>—<br>AN[2]                  | SIUL<br>—<br>—<br>—<br>ADC_0                | Input only                    | _       |                   | 28                | 41      |

Table 5. Pin muxing (continued)

|             | Pad                             |                                      |                                                          |                                                 |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|----------------------------------------------------------|-------------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                                                | Peripheral <sup>3</sup>                         | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| C[2]        | PCR[34]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[34]<br>—<br>—<br>AN[3]                              | SIUL<br>—<br>—<br><br>ADC_0                     | Input only                    | _       |                   | 30      | 45      |

| C[3]        | PCR[35]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[35]<br>CS1<br>ETC[4]<br>TXD<br>EIRQ[21]             | SIUL<br>DSPI_0<br>eTimer_1<br>LIN_1<br>SIUL     | I/O<br>O<br>I/O<br>O<br>I     | Slow    | Medium            | 10      | 16      |

| C[4]        | PCR[36]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[36]<br>CS0<br>X[1]<br>DEBUG[4]<br>EIRQ[22]          | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | /O<br> /O<br> /O<br> -<br>    | Slow    | Medium            | 5       | 11      |

| C[5]        | PCR[37]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[37]<br>SCK<br>—<br>DEBUG[5]<br>FAULT[3]<br>EIRQ[23] | SIUL<br>DSPI_0<br><br>SSCM<br>FlexPWM_0<br>SIUL | /O<br> /O<br> -<br> <br> <br> | Slow    | Medium            | 7       | 13      |

| C[6]        | PCR[38]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[38]<br>SOUT<br>B[1]<br>DEBUG[6]<br>EIRQ[24]         | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | I/O<br>I/O<br>O<br>I          | Slow    | Medium            | 98      | 142     |

| C[7]        | PCR[39]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[39]<br>—<br>A[1]<br>DEBUG[7]<br>SIN                 | SIUL<br><br>FlexPWM_0<br>SSCM<br>DSPI_0         | /O<br> -<br> -<br>            | Slow    | Medium            | 9       | 15      |

| C[8]        | PCR[40]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[40]<br>CS1<br>—<br>CS6<br>FAULT[2]                  | SIUL<br>DSPI_1<br><br>DSPI_0<br>FlexPWM_0       | I/O<br>O<br>O<br>I            | Slow    | Medium            | 91      | 130     |

| C[9]        | PCR[41]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[41]<br>CS3<br>—<br>X[3]<br>FAULT[2]                 | SIUL<br>DSPI_2<br>                              | I/O<br>O<br>I/O<br>I          | Slow    | Medium            | 84      | 123     |

| C[10]       | PCR[42]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[42]<br>CS2<br>—<br>A[3]<br>FAULT[1]                 | SIUL<br>DSPI_2<br><br>FlexPWM_0<br>FlexPWM_0    | I/O<br>O<br><br>O<br>I        | Slow    | Medium            | 78      | 111     |

Table 5. Pin muxing (continued)

| Symbol              |    | Parameter                                                             | Conditions                        | Va                                                            | lue                              | Unit |

|---------------------|----|-----------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------|----------------------------------|------|

| Symbol              |    | Falance                                                               | Conditions                        | Min                                                           | Max <sup>2</sup>                 | Onic |

| V <sub>INANO</sub>  | SR | ADC0 and shared ADC0/1 analog                                         | V <sub>DD_HV_REG</sub> ><br>2.7 V | V <sub>SS_HV_ADV0</sub> -<br>0.3                              | V <sub>DD_HV_ADV0</sub> +<br>0.3 | V    |

| * INANU             |    | input voltage <sup>6</sup>                                            | V <sub>DD_HV_REG</sub> <<br>2.7 V | MinMax2VSS_HV_ADV0 -VDD_HV_ADV0 +0.30.3VSS_HV_ADV0VDD_HV_ADV0 | V                                |      |

| V <sub>INAN1</sub>  | SR | ADC1 analog input voltage <sup>7</sup>                                | V <sub>DD_HV_REG</sub> ><br>2.7 V | V <sub>SS_HV_ADV1</sub> -<br>0.3                              |                                  | V    |

| * INAN1             |    |                                                                       | V <sub>DD_HV_REG</sub> <<br>2.7 V | V <sub>SS_HV_ADV1</sub>                                       | V <sub>DD_HV_ADV1</sub>          | V    |

| I <sub>INJPAD</sub> | SR | Injected input current on any pin<br>during overload condition        |                                   | -10                                                           | 10                               | mA   |

| I <sub>INJSUM</sub> | SR | Absolute sum of all injected input currents during overload condition |                                   | -50                                                           | 50                               | mA   |

| I <sub>VDD_LV</sub> | SR | Low voltage static current sink through $V_{DD_LV}$                   | —                                 |                                                               | 155                              | mA   |

| T <sub>STG</sub>    | SR | Storage temperature                                                   | —                                 | -55                                                           | 150                              | °C   |

| TJ                  | SR | Junction temperature under bias                                       | —                                 | -40                                                           | 150                              | °C   |

## Table 7. Absolute maximum ratings<sup>1</sup> (continued)

<sup>1</sup> Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

<sup>2</sup> Absolute maximum voltages are currently maximum burn-in voltages. Absolute maximum specifications for device stress have not yet been determined.

- <sup>3</sup> The difference between each couple of voltage supplies must be less than 300 mV,

- $|V_{DD_{HV}_{IOY}} V_{DD_{HV}_{IOY}}| < 300 \text{ mV.}$ <sup>4</sup> The difference between ADC voltage supplies must be less than 100 mV,  $|V_{DD_{HV}_{ADC1}} V_{DD_{HV}_{ADC0}}| < 100 \text{ mV.}$

- <sup>5</sup> Guaranteed by device validation

- $^{6}$  Not allowed to refer this voltage to V\_DD\_HV\_ADV1, V\_SS\_HV\_ADV1

- $^7\,$  Not allowed to refer this voltage to V\_DD\_HV\_ADV0, V\_SS\_HV\_ADV0

Figure 4 shows the constraints of the different power supplies.

# **3.4** Recommended operating conditions

| Cumb al                                |    | Devenueter                                           | Conditions                            | Va                           | lue                          | 11   |

|----------------------------------------|----|------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| Symbol                                 |    | Parameter                                            | Conditions                            | Min                          | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                        | SR | Device ground                                        | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup>    | SR | 5.0 V input/output supply voltage                    | _                                     | 4.5                          | 5.5                          | V    |

| V <sub>SS_HV_IOx</sub>                 | SR | Input/output ground voltage                          | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_FL</sub>                  | SR | 5.0 V code and data flash                            | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_FL</sub>                  | SR | Code and data flash ground                           | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier                   | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier reference voltage | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_REG</sub>                 | SR | 5.0 V voltage regulator supply                       | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | voltage                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup>   | SR | 5.0 V ADC_0 supply and high                          | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | _                            |      |

| V <sub>SS_HV_ADC0</sub>                | SR | ADC_0 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_ADC1</sub> <sup>3</sup>   | SR | 5.0 V ADC_1 supply and high                          | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | _                            |      |

| V <sub>SS_HV_ADC1</sub>                | SR | ADC_1 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |

| DD_LV_REGCOR <sup>4,5</sup>            | СС | Internal supply voltage                              | —                                     | -                            | —                            | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>4</sup> |    | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>4,5</sup> | СС | Internal supply voltage                              | —                                     | _                            | —                            | V    |

| $V_{SS_LV_CORx}^4$                     | SR | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |

| T <sub>A</sub>                         | SR | Ambient temperature under bias                       | -                                     | -40                          | 125                          | °C   |

Table 8. Recommended operating conditions (5.0 V)

<sup>1</sup> Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_IOy</sub> - V<sub>DD\_HV\_IOx</sub> | < 100 mV.</p>

$^{3}$  The difference between ADC voltage supplies must be less than 100 mV,  $|V_{DD_{-HV}ADC1} - V_{DD_{-HV}ADC0}| < 100 mV$ .

<sup>5</sup> Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

## 3.5.2 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from Equation 1:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D}) \qquad \qquad Eqn. 1$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in Equation 2 as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \qquad \qquad Eqn. 2$$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction to case thermal resistance (°C/W)

$R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using Equation 3:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D}) \qquad \qquad Eqn. 3$$

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

References:

# 3.8 Power management electrical characteristics

# 3.8.1 Voltage regulator electrical characteristics

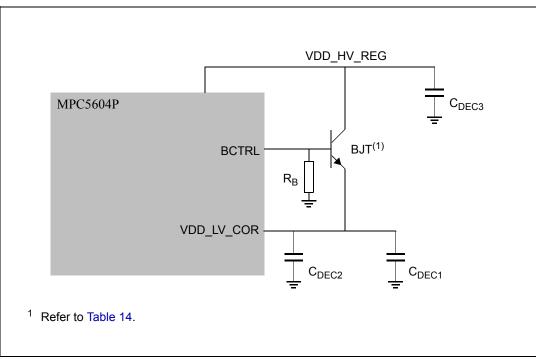

The internal voltage regulator requires an external NPN ballast to be connected as shown in Figure 8. Table 14 contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the  $V_{DD_HV_REG}$  BCTRL and  $V_{DD_LV_CORx}$  pins to less than  $L_{Reg}$ , see Table 15.

## NOTE

The voltage regulator output cannot be used to drive external circuits. Output pins are used only for decoupling capacitances.

$V_{DD\_LV\_COR}$  must be generated using internal regulator and external NPN transistor. It is not possible to provide  $V_{DD\_LV\_COR}$  through external regulator.

For the MPC5604P microcontroller, capacitors, with total values not below  $C_{DEC1}$ , should be placed between  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  close to external ballast transistor emitter. 4 capacitors, with total values not below  $C_{DEC2}$ , should be placed close to microcontroller nins between each  $V_{DD\_LV\_CORx}$  (op\_supply pairs and the

be placed close to microcontroller pins between each  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  supply pairs and the  $V_{DD\_LV\_REGCOR}/V_{SS\_LV\_REGCOR}$  pair . Additionally, capacitors with total values not below  $C_{DEC3}$ , should be placed between the  $V_{DD\_HV\_REG}/V_{SS\_HV\_REG}$  pins close to ballast collector. Capacitors values have to take into account capacitor accuracy, aging and variation versus temperature.

All reported information are valid for voltage and temperature ranges described in recommended operating condition, Table 8 and Table 9.

Figure 8. Configuration with resistor on base

| Part  | Manufacturer | Approved derivatives <sup>1</sup> |  |  |

|-------|--------------|-----------------------------------|--|--|

| BCP68 | ON Semi      | BCP68                             |  |  |

|       | NXP          | BCP68-25                          |  |  |

|       | Infineon     | BCP68-25                          |  |  |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25        |  |  |

| BC868 | NXP          | BC868                             |  |  |

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;        |  |  |

|       | NXP          | BC817-16;BC817-25                 |  |  |

| BCP56 | ST           | BCP56-16                          |  |  |

|       | Infineon     | BCP56-10;BCP56-16                 |  |  |

|       | ON Semi      | BCP56-10                          |  |  |

|       | NXP          | BCP56-10;BCP56-16                 |  |  |

Table 14. Approved NPN ballast components (configuration with resistor on base)

<sup>1</sup> For automotive applications please check with the appropriate transistor vendor for automotive grade certification

| Symbol                    |    | с | Parameter                                                                | Conditions                                                                                          |      | Unit |      |      |

|---------------------------|----|---|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|

| Cymool                    |    | Ū |                                                                          | Contractions                                                                                        | Min  | Тур  | Max  | onit |

| V <sub>DD_LV_REGCOR</sub> | CC |   | Output voltage under maximum<br>load run supply current<br>configuration | Post-trimming                                                                                       | 1.15 | _    | 1.32 | V    |

| R <sub>B</sub>            | SR |   | External resistance on bipolar junction transistor (BJT) base            | —                                                                                                   | 18   |      | 22   | kΩ   |

| C <sub>DEC1</sub>         | SR |   | External decoupling/stability ceramic capacitor                          | BJT from Table 14. 3<br>capacitances (i.e. X7R or X8R<br>capacitors) with nominal value<br>of 10 µF | 19.5 | 30   |      | μF   |

|                           |    |   |                                                                          | BJT BC817, one capacitance of 22 $\mu$ F                                                            | 14.3 | 22   |      | μF   |

<sup>2</sup> "SR" parameter values must not exceed the absolute maximum ratings shown in Table 7.

| Symbol                  | С |             | Parameter                                   | Conditions                                                    |                            | Va     | Unit  |    |  |

|-------------------------|---|-------------|---------------------------------------------|---------------------------------------------------------------|----------------------------|--------|-------|----|--|

| Cymbol                  |   |             | i ulullotoi                                 |                                                               |                            | 1 1 1  |       |    |  |

| I <sub>DD_LV_CORx</sub> | Т |             | RUN—Maximum mode <sup>1</sup>               | V <sub>DD_LV_CORx</sub>                                       | 40 MHz                     | 62     | 77    | mA |  |

|                         |   |             | externally forced at 1.3 V                  | externally forced at 1.3 V                                    | externally forced at 1.3 V | 64 MHz | 71    | 89 |  |

|                         |   |             | RUN—Typical mode <sup>2</sup>               |                                                               | 40 MHz                     | 45     | 56    |    |  |

|                         |   |             |                                             |                                                               | 64 MHz                     | 53     | 66    |    |  |

|                         | Ρ |             | RUN—Maximum mode <sup>3</sup>               | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | 64 MHz                     | 60     | 75    |    |  |

|                         |   | ent         | HALT mode <sup>4</sup>                      | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | —                          | 1.5    | 10    |    |  |

|                         |   | oly current | STOP mode <sup>5</sup>                      | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | —                          | 1      | 10    |    |  |

| I <sub>DD_FLASH</sub>   | Т | Supply o    | Flash during read on single mode            | V <sub>DD_HV_FL</sub> at 3.3 V                                |                            | 8      | 10    |    |  |

|                         |   |             | Flash during erase operation on single mode | V <sub>DD_HV_FL</sub> at 3.3 V                                | —                          | 10     | 12    |    |  |

| I <sub>DD_ADC</sub>     | Т |             | ADC—Maximum mode <sup>1</sup>               | V <sub>DD_HV_ADC0</sub> at 3.3 V                              | ADC_1                      | 2.5    | 4     |    |  |

|                         |   |             |                                             | V <sub>DD_HV_ADC1</sub> at 3.3 V<br>f <sub>ADC</sub> = 16 MHz | ADC_0                      | 2      | 4     |    |  |

|                         |   |             | ADC—Typical mode <sup>2</sup>               |                                                               | ADC_1                      | 0.8    | 1     |    |  |

|                         |   |             |                                             |                                                               | ADC_0                      | 0.005  | 0.006 |    |  |

| I <sub>DD_OSC</sub>     | Т | •           | Oscillator                                  | V <sub>DD_OSC</sub> at 3.3 V                                  | 8 MHz                      | 2.4    | 3     |    |  |

Table 22. Supply current (3.3 V, NVUSRO[PAD3V5V] = 1)

<sup>1</sup> Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

<sup>2</sup> Typical mode: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

<sup>3</sup> Code fetched from RAM, PLL\_0: 64 MHz system clock (x4 multiplier with 16 MHz XTAL), PLL\_1 is ON at PHI\_div2 = 120 MHz and PHI\_div3 = 80 MHz, auxiliary clock sources set that all peripherals receive maximum frequency, all peripherals enabled.

<sup>4</sup> Halt mode configurations: code fetched from RAM, code and data flash memories in low power mode, OSC/PLL 0/PLL 1 are OFF, core clock frozen, all peripherals are disabled.

<sup>5</sup> STOP "P" mode Device Under Test (DUT) configuration: code fetched from RAM, code and data flash memories OFF, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

# 3.10.4 Input DC electrical characteristics definition

Figure 13 shows the DC electrical characteristics behavior as function of time.

| Ded      | 144       | LQFP        | 100 LQFP  |             |  |

|----------|-----------|-------------|-----------|-------------|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[72]  | 1%        | 1%          | _         |             |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[73]  | 1%        | 1%          | _         | _           |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[74]  | 1%        | 1%          | _         | _           |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[75]  | 1%        | 1%          | _         | _           |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[76]  | 1%        | 1%          | _         | _           |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |

| PAD[107] | 20%       | 17%         | _         |             |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |

| PAD[106] | 18%       | 16%         | _         |             |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |

| PAD[105] | 16%       | 14%         | _         | _           |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |

| PAD[104] | 14%       | 13%         | _         |             |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |

| PAD[103] | 12%       | 11%         | —         |             |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |

| PAD[101] | 11%       | 9%          | _         |             |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |

| TCK      | 1%        | 1%          | 1%        | 1%          |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |

| PAD[102] | 11%       | 10%         | _         | —           |  |

## Table 24. I/O weight (continued)

| Symbol           |        | с | Parameter                         |   | Value |      |  |

|------------------|--------|---|-----------------------------------|---|-------|------|--|

|                  |        | U |                                   |   | Мах   | Unit |  |

| f <sub>OSC</sub> | S<br>R | _ | Oscillator frequency              | 4 | 40    | MHz  |  |

| 9 <sub>m</sub>   | _      | Ρ | Transconductance                  |   | 20    | mA/V |  |

| V <sub>OSC</sub> | —      | Т | Oscillation amplitude on XTAL pin | 1 | _     | V    |  |

| toscsu           | -      | Т | Start-up time <sup>1,2</sup>      | 8 | _     | ms   |  |

<sup>1</sup> The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

<sup>2</sup> Value captured when amplitude reaches 90% of XTAL

| Symbol            |    | Parameter                |      | Value |      |      |  |

|-------------------|----|--------------------------|------|-------|------|------|--|

|                   |    |                          |      | Тур   | Мах  | Unit |  |

| f <sub>OSC</sub>  | SR | Oscillator frequency     | 4    | —     | 40   | MHz  |  |

| f <sub>CLK</sub>  | SR | Frequency in bypass      | _    | _     | 64   | MHz  |  |

| t <sub>rCLK</sub> | SR | Rise/fall time in bypass | _    | —     | 1    | ns   |  |

| t <sub>DC</sub>   | SR | Duty cycle               | 47.5 | 50    | 52.5 | %    |  |

### Table 28. Input clock characteristics

# 3.12 FMPLL electrical characteristics

### Table 29. FMPLL electrical characteristics

| Symbol                                           | с | Parameter                                                | Conditions <sup>1</sup>                          | Va  | Unit                 |      |

|--------------------------------------------------|---|----------------------------------------------------------|--------------------------------------------------|-----|----------------------|------|

| Symbol                                           | Č | raiametei                                                | Conditions                                       | Min | Max                  | Onit |

| f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | D | PLL reference frequency range <sup>2</sup>               | Crystal reference                                | 4   | 40                   | MHz  |

| f <sub>PLLIN</sub>                               | D | Phase detector input frequency range (after pre-divider) | frequency range (after —                         |     | 16                   | MHz  |

| f <sub>FMPLLOUT</sub>                            | D | Clock frequency range in normal mode                     | —                                                | 16  | 120                  | MHz  |

| f <sub>FREE</sub>                                | Ρ | Free-running frequency                                   | Measured using clock<br>division — typically /16 | 20  | 150                  | MHz  |

| t <sub>CYC</sub>                                 | D | System clock period                                      | —                                                | —   | 1 / f <sub>SYS</sub> | ns   |

| f <sub>LORL</sub>                                | D | Loss of reference frequency window <sup>3</sup>          | Lower limit                                      | 1.6 | 3.7                  | MHz  |

| f <sub>LORH</sub>                                |   |                                                          | Upper limit                                      | 24  | 56                   |      |

| f <sub>SCM</sub>                                 | D | Self-clocked mode frequency <sup>4,5</sup>               | _                                                | 20  | 150                  | MHz  |

| Symbol              | с | Parameter                                  | meter                                         | Conditions <sup>1</sup>                                                                    | Value |                    | Unit                  |  |

|---------------------|---|--------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------|-------|--------------------|-----------------------|--|

| Cymbol              | ľ |                                            |                                               | Conditions                                                                                 | Min   | Max                |                       |  |

| C <sub>JITTER</sub> | Т | CLKOUT period<br>jitter <sup>6,7,8,9</sup> | Short-term jitter <sup>10</sup>               | f <sub>SYS</sub> maximum                                                                   | -4    | 4                  | % f <sub>CLKOUT</sub> |  |

|                     |   | Jitter                                     | Long-term jitter (avg.<br>over 2 ms interval) | f <sub>PLLIN</sub> = 16 MHz<br>(resonator), f <sub>PLLCLK</sub> at<br>64 MHz, 4,000 cycles | _     | 10                 | ns                    |  |

| t <sub>ipii</sub>   | D | PLL lock time <sup>11, 12</sup>            |                                               | —                                                                                          | _     | 200                | μs                    |  |

| t <sub>dc</sub>     | D | Duty cycle of reference                    | ce                                            | —                                                                                          | 40    | 60                 | %                     |  |

| f <sub>LCK</sub>    | D | Frequency LOCK ran                         | ge                                            | —                                                                                          | -6    | 6                  | % f <sub>SYS</sub>    |  |

| f <sub>UL</sub>     | D | Frequency un-LOCK                          | range                                         | —                                                                                          | -18   | 18                 | % f <sub>SYS</sub>    |  |

| f <sub>CS</sub>     | D | Modulation depth                           |                                               | Center spread                                                                              | ±0.25 | ±4.0 <sup>13</sup> | % f <sub>SYS</sub>    |  |

| f <sub>DS</sub>     |   |                                            |                                               | Down spread                                                                                | -0.5  | -8.0               |                       |  |

| f <sub>MOD</sub>    | D | Modulation frequency                       | ,14                                           | —                                                                                          |       | 70                 | kHz                   |  |

Table 29. FMPLL electrical characteristics (continued)

<sup>1</sup> V<sub>DD LV CORx</sub> = 1.2 V ±10%; V<sub>SS</sub> = 0 V; T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Considering operation with PLL not bypassed

<sup>3</sup> "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self-clocked mode.

<sup>4</sup> Self-clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

<sup>5</sup> f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

<sup>6</sup> This value is determined by the crystal manufacturer and board design.

<sup>7</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

<sup>8</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>9</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

<sup>10</sup> Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

<sup>11</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

<sup>12</sup> This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

$^{13}$  This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

<sup>14</sup> Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

| Symbol           | С | Parameter                                                                    | Conditions <sup>1</sup> | Max value | Unit |

|------------------|---|------------------------------------------------------------------------------|-------------------------|-----------|------|

| f <sub>max</sub> |   | Maximum working frequency at given number of wait states in worst conditions | 2 wait states           | 66        | MHz  |

|                  |   |                                                                              | 0 wait states           | 18        |      |

### Table 34. Flash memory read access timing

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

#### AC specifications 3.16

#### 3.16.1 **Pad AC specifications**

| Table 35. | Output p | in transition | times |

|-----------|----------|---------------|-------|

|-----------|----------|---------------|-------|

| Symb                          |    | с | Parameter                                      |                           | onditions <sup>1</sup>                                                                                                           |     | Value | )   | Unit |  |  |  |  |                         |  |   |  |    |  |

|-------------------------------|----|---|------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|--|--|--|--|-------------------------|--|---|--|----|--|

| Synn                          | 01 | C | Falameter                                      |                           | onations                                                                                                                         | Min | Тур   | Max | Unit |  |  |  |  |                         |  |   |  |    |  |

| t <sub>tr</sub>               | CC | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                                                                                      | —   | —     | 50  | ns   |  |  |  |  |                         |  |   |  |    |  |

|                               |    | Т | SLOW configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0                                                                                                                      | —   | —     | 100 |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                                                  | —   | —     | 125 |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 25 pF    | $V_{DD} = 3.3 V \pm 10\%$ ,                                                                                                      | —   | —     | 40  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | Т |                                                | C <sub>L</sub> = 50 pF    | PAD3V5V = 1                                                                                                                      | —   | —     | 50  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                                                  | _   | —     | 75  |      |  |  |  |  |                         |  |   |  |    |  |

| t <sub>tr</sub>               | СС | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0<br>SIUL.PCRx.SRC = 1<br>$V_{DD} = 3.3 V \pm 10\%,$<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | —   | —     | 10  | ns   |  |  |  |  |                         |  |   |  |    |  |

|                               |    | Т | (                                              | C <sub>L</sub> = 50 pF    |                                                                                                                                  | —   | —     | 20  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                                                  | _   | —     | 40  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 25 pF    |                                                                                                                                  | —   | —     | 12  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | Т |                                                | C <sub>L</sub> = 50 pF    |                                                                                                                                  | —   | —     | 25  |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                                                  | —   | —     | 40  |      |  |  |  |  |                         |  |   |  |    |  |

| t <sub>tr</sub>               | СС | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                                                                                      | —   | —     | 4   | ns   |  |  |  |  |                         |  |   |  |    |  |

|                               |    |   | FAST configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1                                                                                                 | —   | —     | 6   |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    |   |                                                |                           |                                                                                                                                  |     |       |     |      |  |  |  |  | C <sub>L</sub> = 100 pF |  | _ |  | 12 |  |

|                               |    |   |                                                | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                                                                                    | —   | —     | 4   |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    |   |                                                | C <sub>L</sub> = 50 pF    | SIUL.PCRx.SRC = 1                                                                                                                | —   | —     | 7   |      |  |  |  |  |                         |  |   |  |    |  |

|                               |    |   |                                                | C <sub>L</sub> = 100 pF   |                                                                                                                                  | —   | —     | 12  |      |  |  |  |  |                         |  |   |  |    |  |

| t <sub>SYM</sub> <sup>3</sup> | СС | Т | Symmetric transition time, same drive          | V <sub>DD</sub> = 5.0 V : | ± 10%, PAD3V5V = 0                                                                                                               | —   | —     | 4   | ns   |  |  |  |  |                         |  |   |  |    |  |

|                               |    |   | strength between N and P transistor            | V <sub>DD</sub> = 3.3 V : | ± 10%, PAD3V5V = 1                                                                                                               | —   | —     | 5   |      |  |  |  |  |                         |  |   |  |    |  |

<sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified <sup>2</sup> C<sub>L</sub> includes device and package capacitances (C<sub>PKG</sub> < 5 pF).

<sup>3</sup> Transition timing of both positive and negative slopes will differ maximum 50%

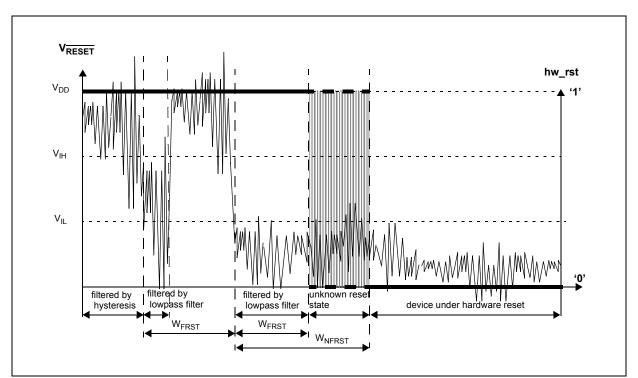

Figure 20. Noise filtering on reset signal

| Symb             | al     | с | Parameter                                  | Conditions <sup>1</sup>                                                                          |                     | Value |                      | Unit |

|------------------|--------|---|--------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|-------|----------------------|------|

| C y line         | Gymbol |   |                                            | Conditions                                                                                       | Min                 | Тур   | Мах                  | onne |

| V <sub>IH</sub>  | SR     | Ρ | Input High Level CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.65V <sub>DD</sub> | _     | V <sub>DD</sub> +0.4 | V    |

| V <sub>IL</sub>  | SR     | Ρ | Input low Level CMOS<br>(Schmitt Trigger)  | _                                                                                                | -0.4                | _     | 0.35V <sub>DD</sub>  | V    |

| V <sub>HYS</sub> | СС     | С | Input hysteresis CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.1V <sub>DD</sub>  | _     | _                    | V    |

| V <sub>OL</sub>  | СС     | Ρ | Output low level                           | Push Pull, I <sub>OL</sub> = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                   | _     | 0.1V <sub>DD</sub>   | V    |

|                  |        |   |                                            | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>            | _                   | _     | 0.1V <sub>DD</sub>   |      |

|                  |        |   |                                            | Push Pull, I <sub>OL</sub> = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | —                   | _     | 0.5                  |      |

Table 36. RESET electrical characteristics

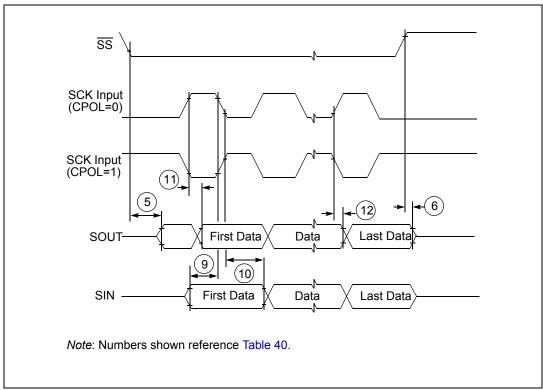

Figure 35. DSPI modified transfer format timing – Slave, CPHA = 1

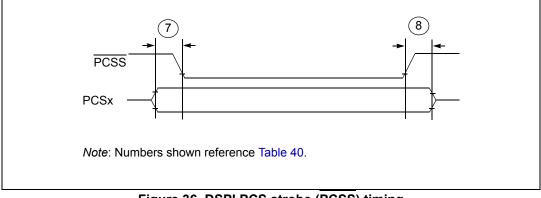

Figure 36. DSPI PCS strobe (PCSS) timing

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2008–2012 Freescale, Inc.

Document Number: MPC5604P Rev. 8 07/2012