Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 108                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 40K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pef0mlq6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse width modulator (FlexPWM)               | Contains four PWM submodules, each of which is capable of controlling a single half-bridge power stage and two fault input channels                                                                                              |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR <sup>1</sup> and operating system tasks                                                                                                                               |

| System watchdog timer (SWT)                   | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, 1 of which can cause non-maskable interrupt requests or wakeup events                                                                          |

### Table 2. MPC5604P series block summary (continued)

AUTOSAR: AUTomotive Open System ARchitecture (see http://www.autosar.org)

# 1.5 Feature details

1

### 1.5.1 High performance e200z0 core processor

The e200z0 Power Architecture core provides the following features:

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16-bit and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit

- 1 cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- · Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non-maskable interrupt support

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

# 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the MPC5604P:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module can run on an independent clock source

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

# 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The PLL has the following major features:

• Input clock frequency: 4–40 MHz

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the PLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

## 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

## 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- $\pm 5\%$  variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

### 1.5.12 Periodic interrupt timer (PIT)

The PIT module implements these features:

- 4 general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

## 1.5.13 System timer module (STM)

The STM module implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

## 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- 32 message buffers of up to 8-bytes data length

- · Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- · Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a six-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

## 1.5.21 Safety port (FlexCAN)

The MPC5604P MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate as fast as 7.5 Mbit/s at 60 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8 bytes data length

- Can be used as a second independent CAN module

## 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

- Input capture trigger

- Output compare

- Double buffer (to capture rising edge and falling edge)

- Separate prescaler for each counter

- Selectable clock source

- 0–100% pulse measurement

- Rotation direction flag (Quad decoder mode)

- Maximum count rate

- External event counting: max. count rate = peripheral clock/2

- Internal clock counting: max. count rate = peripheral clock

- Counters are:

- Cascadable

- Preloadable

- Programmable count modulo

- Quadrature decode capabilities

- Counters can share available input pins

- Count once or repeatedly

- Pins available as GPIO when timer functionality not in use

# 1.5.27 Analog-to-digital converter (ADC) module

The ADC module provides the following features:

Analog part:

- 2 on-chip AD converters

- 10-bit AD resolution

- 1 sample and hold unit per ADC

- Conversion time, including sampling time, less than 1 μs (at full precision)

- Typical sampling time is 150 ns min. (at full precision)

- Differential non-linearity error (DNL) ±1 LSB

- Integral non-linearity error (INL)  $\pm 1.5$  LSB

- TUE <3 LSB

- Single-ended input signal up to 5.0 V

- The ADC and its reference can be supplied with a voltage independent from V<sub>DDIO</sub>

- The ADC supply can be equal or higher than V<sub>DDIO</sub>

- The ADC supply and the ADC reference are not independent from each other (they are internally bonded to the same pad)

- Sample times of 2 (default), 8, 64, or 128 ADC clock cycles

### Digital part:

- $2 \times 13$  input channels including 4 channels shared between the 2 converters

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range) before results are stored in the appropriate ADC result location,

- 2 modes of operation: Normal mode or CTU control mode

- Normal mode features

- Register-based interface with the CPU: control register, status register, 1 result register per channel

- ADC state machine managing 3 request flows: regular command, hardware injected command, software injected command

- Selectable priority between software and hardware injected commands

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range)

- DMA compatible interface

- CTU control mode features

- Triggered mode only

- 4 independent result queues ( $2 \times 16$  entries,  $2 \times 4$  entries)

- Result alignment circuitry (left justified; right justified)

- 32-bit read mode allows to have channel ID on one of the 16-bit part

- DMA compatible interfaces

### 1.5.28 Cross triggering unit (CTU)

The cross triggering unit allows automatic generation of ADC conversion requests on user selected conditions without CPU load during the PWM period and with minimized CPU load for dynamic configuration.

It implements the following features:

- Double buffered trigger generation unit with as many as eight independent triggers generated from external triggers

- Trigger generation unit configurable in sequential mode or in triggered mode

- Each Trigger can be appropriately delayed to compensate the delay of external low pass filter

- Double buffered global trigger unit allowing eTimer synchronization and/or ADC command generation

- Double buffered ADC command list pointers to minimize ADC-trigger unit update

- Double buffered ADC conversion command list with as many as 24 ADC commands

- Each trigger has the capability to generate consecutive commands

- ADC conversion command allows to control ADC channel from each ADC, single or synchronous sampling, independent result queue selection

### 1.5.29 Nexus development interface (NDI)

The NDI (Nexus Development Interface) block provides real-time development support capabilities for the MPC5604P Power Architecture based MCU in compliance with the IEEE-ISTO 5001-2003 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility. The NDI block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal busses to provide development support as per the IEEE-ISTO 5001-2003 Class 2+ standard. The development support provided includes access to the MCU's internal memory map and access to the processor's internal registers during run time.

The Nexus Interface provides the following features:

- Configured via the IEEE 1149.1

- All Nexus port pins operate at V<sub>DDIO</sub> (no dedicated power supply)

- Nexus 2+ features supported

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or keep executing and allow overwrite of information

|             | Pad                             |                                             |                                                   |                                             |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                         | Peripheral <sup>3</sup>                     | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| B[10]       | PCR[26]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[26]<br>—<br>—<br>—<br>AN[12]                 | SIUL<br>—<br>—<br>                          | Input only                    | _       | _                 | 36      | 53      |

| B[11]       | PCR[27]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[27]<br>—<br>—<br>—<br>AN[13]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    |         | _                 | 37      | 54      |

| B[12]       | PCR[28]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[28]<br><br><br>AN[14]                        | SIUL<br>—<br>—<br><br>ADC_0 / ADC_1         | Input only                    | _       | _                 | 38      | 55      |

| B[13]       | PCR[29]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[29]<br>—<br>—<br>—<br>AN[0]<br>RXD           | SIUL<br>—<br>—<br>ADC_1<br>LIN_1            | Input only                    | _       | _                 | 42      | 60      |

| B[14]       | PCR[30]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[30]<br>—<br>—<br>AN[1]<br>ETC[4]<br>EIRQ[19] | SIUL<br>—<br>—<br>ADC_1<br>eTimer_0<br>SIUL | Input only                    |         | _                 | 44      | 64      |

| B[15]       | PCR[31]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[31]<br>—<br>—<br>—<br>AN[2]<br>EIRQ[20]      | SIUL<br>—<br>—<br>ADC_1<br>SIUL             | Input only                    | _       | _                 | 43      | 62      |

|             |                                 |                                             |                                                   | Port C (16-bit)                             |                               |         |                   | •       |         |

| C[0]        | PCR[32]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[32]<br>—<br>—<br>—<br>AN[3]                  | SIUL<br>—<br>—<br>—<br>ADC_1                | Input only                    | _       |                   | 45      | 66      |

| C[1]        | PCR[33]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[33]<br>—<br>—<br>—<br>AN[2]                  | SIUL<br>—<br>—<br>—<br>ADC_0                | Input only                    | _       |                   | 28      | 41      |

Table 5. Pin muxing (continued)

|             | Pad                          |                                      |                                   |                              |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|------------------------------|--------------------------------------|-----------------------------------|------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                         | Peripheral <sup>3</sup>      | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| E[6]        | PCR[70]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[70]<br><br><br>AN[9]         | SIUL<br>—<br>—<br>—<br>ADC_0 | Input only                    | _       |                   | _       | 46      |

| E[7]        | PCR[71]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[71]<br>—<br>—<br>AN[10]      | SIUL<br>—<br>—<br><br>ADC_0  | Input only                    | _       | _                 | _       | 48      |

| E[8]        | PCR[72]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[72]<br>—<br>—<br>AN[6]       | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only                    |         | _                 |         | 59      |

| E[9]        | PCR[73]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[73]<br>—<br>—<br>AN[7]       | SIUL<br>—<br>—<br><br>ADC_1  | Input only                    | _       |                   | _       | 61      |

| E[10]       | PCR[74]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[74]<br><br><br>AN[8]         | SIUL<br>—<br>—<br>ADC_1      | Input only                    | _       |                   | _       | 63      |

| E[11]       | PCR[75]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[75]<br>—<br>—<br>—<br>AN[9]  | SIUL<br>—<br>—<br>—<br>ADC_1 | Input only                    | _       | _                 | _       | 65      |

| E[12]       | PCR[76]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[76]<br>—<br>—<br>AN[10]      | SIUL<br>—<br>—<br>ADC_1      | Input only                    | _       | _                 | _       | 67      |

| E[13]       | PCR[77]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[77]<br>SCK<br>—<br>EIRQ[25]  | SIUL<br>DSPI_3<br>—<br>SIUL  | /O<br> /O<br><br>             | Slow    | Medium            | -       | 117     |

| E[14]       | PCR[78]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[78]<br>SOUT<br>—<br>EIRQ[26] | SIUL<br>DSPI_3<br>—<br>SIUL  | /O<br>O<br>—<br>I             | Slow    | Medium            |         | 119     |

Table 5. Pin muxing (continued)

# **3.4** Recommended operating conditions

| Cumb al                                |    | Devenueter                                           | Conditions                            | Va                           | lue                          | 11   |

|----------------------------------------|----|------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| Symbol                                 |    | Parameter                                            | Conditions                            | Min                          | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                        | SR | Device ground                                        | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup>    | SR | 5.0 V input/output supply voltage                    | _                                     | 4.5                          | 5.5                          | V    |

| V <sub>SS_HV_IOx</sub>                 | SR | Input/output ground voltage                          | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_FL</sub>                  | SR | 5.0 V code and data flash                            | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_FL</sub>                  | SR | Code and data flash ground                           | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier                   | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_OSC</sub>                 | SR | 5.0 V crystal oscillator amplifier reference voltage | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_REG</sub>                 | SR | 5.0 V voltage regulator supply                       | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | voltage                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup>   | SR | R 5.0 V ADC_0 supply and high                        | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | $V_{DD_{HV_{REG}}} - 0.1$    | _                            |      |

| V <sub>SS_HV_ADC0</sub>                | SR | ADC_0 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_ADC1</sub> <sup>3</sup>   | SR | 5.0 V ADC_1 supply and high                          | —                                     | 4.5                          | 5.5                          | V    |

|                                        |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | _                            |      |

| V <sub>SS_HV_ADC1</sub>                | SR | ADC_1 ground and low reference voltage               | _                                     | 0                            | 0                            | V    |

| DD_LV_REGCOR <sup>4,5</sup>            | СС | Internal supply voltage                              | —                                     | -                            | —                            | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>4</sup> |    | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>4,5</sup> | СС | Internal supply voltage                              | —                                     | _                            | —                            | V    |

| $V_{SS_{LV}_{CORx}}^4$                 | SR | Internal reference voltage                           | —                                     | 0                            | 0                            | V    |

| T <sub>A</sub>                         | SR | Ambient temperature under bias                       | -                                     | -40                          | 125                          | °C   |

Table 8. Recommended operating conditions (5.0 V)

<sup>1</sup> Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_IOy</sub> - V<sub>DD\_HV\_IOx</sub> | < 100 mV.</p>

$^{3}$  The difference between ADC voltage supplies must be less than 100 mV,  $|V_{DD_{-HV}ADC1} - V_{DD_{-HV}ADC0}| < 100 mV$ .

| Symbol                    | Symbol |   | Parameter                                                                | Conditions                                           |      |     | Unit |      |

|---------------------------|--------|---|--------------------------------------------------------------------------|------------------------------------------------------|------|-----|------|------|

| Gymbol                    |        | С |                                                                          | Conditions                                           | Min  | Тур | Max  | Onic |

| V <sub>DD_LV_REGCOR</sub> | CC     | Ρ | Output voltage under maximum<br>load run supply current<br>configuration | Post-trimming                                        | 1.15 | _   | 1.32 | V    |

| C <sub>DEC1</sub>         | SR     | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances                                       | 40   | 56  |      | μF   |

| R <sub>REG</sub>          | SR     | _ | Resulting ESR of all four C <sub>DEC1</sub>                              | Absolute maximum value<br>between 100 kHz and 10 MHz |      | _   | 45   | mΩ   |

| C <sub>DEC2</sub>         | SR     | _ | External decoupling/stability ceramic capacitor                          | 4 capacitances of 100 nF each                        | 400  |     | _    | nF   |

| C <sub>DEC3</sub>         | SR     |   | External decoupling/stability<br>ceramic capacitor on<br>VDD_HV_REG      | _                                                    | 40   | _   | _    | μF   |

| L <sub>Reg</sub>          | SR     |   | Resulting ESL of $V_{DD_HV_REG}$ , BCTRL and $V_{DD_LV_CORx}$ pins       | —                                                    |      |     | 15   | nH   |

Table 16. Voltage regulator electrical characteristics (configuration without resistor on base)

### 3.8.2 Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the  $V_{DD}$  and the  $V_{DD \ LV}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- LVDHV5 monitors  $V_{DD}$  when application uses device in the 5.0V  $\pm$  10% range

- LVDLVCOR monitors low voltage digital power domain

### Table 17. Low voltage monitor electrical characteristics

| Symbol                   | с | Parameter                                     | Conditions <sup>1</sup> | Va  | Unit |      |

|--------------------------|---|-----------------------------------------------|-------------------------|-----|------|------|

| Symbol                   | U | Falameter                                     | Conditions              | Min | Max  | onit |

| V <sub>PORH</sub>        | Т | Power-on reset threshold                      | —                       | 1.5 | 2.7  | V    |

| V <sub>PORUP</sub>       | Р | Supply for functional POR module              | T <sub>A</sub> = 25 °C  | 1.0 | —    | V    |

| V <sub>REGLVDMOK_H</sub> | Р | Regulator low voltage detector high threshold | —                       | _   | 2.95 | V    |

| V <sub>REGLVDMOK_L</sub> | Р | Regulator low voltage detector low threshold  | —                       | 2.6 | —    | V    |

| V <sub>FLLVDMOK_H</sub>  | Р | Flash low voltage detector high threshold     | —                       | _   | 2.95 | V    |

| V <sub>FLLVDMOK_L</sub>  | Р | Flash low voltage detector low threshold      | —                       | 2.6 | —    | V    |

| V <sub>IOLVDMOK_H</sub>  | Р | I/O low voltage detector high threshold       | —                       | _   | 2.95 | V    |

| V <sub>IOLVDMOK_L</sub>  | Р | I/O low voltage detector low threshold        | —                       | 2.6 |      | V    |

| Symbol                   | с | Parameter                                  | Conditions <sup>1</sup> | Va   | Unit  |   |  |

|--------------------------|---|--------------------------------------------|-------------------------|------|-------|---|--|

| Symbol                   |   | Falameter                                  | Conditions              | Min  | Max   |   |  |

| V <sub>IOLVDM5OK_H</sub> | Р | I/O 5V low voltage detector high threshold |                         |      | 4.4   | V |  |

| V <sub>IOLVDM50K_L</sub> | Р | I/O 5V low voltage detector low threshold  | —                       | 3.8  | —     | V |  |

| V <sub>MLVDDOK_H</sub>   | Р | Digital supply low voltage detector high   | —                       |      | 1.145 | V |  |

| V <sub>MLVDDOK_L</sub>   | Р | Digital supply low voltage detector low    | —                       | 1.08 |       | V |  |

Table 17. Low voltage monitor electrical characteristics (continued)

$\frac{1}{1}$  V<sub>DD</sub> = 3.3V ± 10% / 5.0V ± 10%, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified

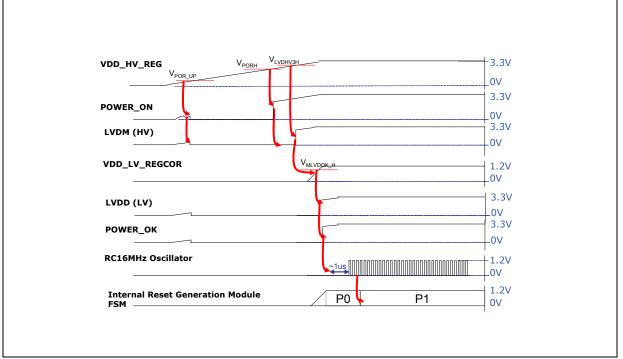

# 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the MPC5604P implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct start-up of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain). LVDs are gated low when POWER\_ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash memory and RC16 oscillator needed during power-up phase and reset phase. When POWER\_OK is low the associated module are set into a safe state.

Figure 10. Power-up typical sequence

| Symbol              | C | C Parameter                                | Conditions <sup>1</sup>                       | Va                                                                                         | lue   | Unit               |                       |

|---------------------|---|--------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------|-------|--------------------|-----------------------|

| Cymbol              | ľ |                                            |                                               | Conditions                                                                                 | Min   |                    |                       |

| C <sub>JITTER</sub> | Т | CLKOUT period<br>jitter <sup>6,7,8,9</sup> | Short-term jitter <sup>10</sup>               | f <sub>SYS</sub> maximum                                                                   | -4    | 4                  | % f <sub>CLKOUT</sub> |

|                     |   | Jitter                                     | Long-term jitter (avg.<br>over 2 ms interval) | f <sub>PLLIN</sub> = 16 MHz<br>(resonator), f <sub>PLLCLK</sub> at<br>64 MHz, 4,000 cycles | _     | 10                 | ns                    |

| t <sub>ipii</sub>   | D | PLL lock time <sup>11, 12</sup>            | ·                                             | —                                                                                          | _     | 200                | μs                    |

| t <sub>dc</sub>     | D | Duty cycle of reference                    | ce                                            | —                                                                                          | 40    | 60                 | %                     |

| f <sub>LCK</sub>    | D | Frequency LOCK ran                         | ge                                            | —                                                                                          | -6    | 6                  | % f <sub>SYS</sub>    |

| f <sub>UL</sub>     | D | Frequency un-LOCK                          | range                                         | —                                                                                          | -18   | 18                 | % f <sub>SYS</sub>    |

| f <sub>CS</sub>     | D | Modulation depth                           |                                               | Center spread                                                                              | ±0.25 | ±4.0 <sup>13</sup> | % f <sub>SYS</sub>    |

| f <sub>DS</sub>     |   |                                            |                                               | Down spread                                                                                | -0.5  | -8.0               |                       |

| f <sub>MOD</sub>    | D | Modulation frequency                       | ,14                                           | —                                                                                          |       | 70                 | kHz                   |

Table 29. FMPLL electrical characteristics (continued)

<sup>1</sup> V<sub>DD LV CORx</sub> = 1.2 V ±10%; V<sub>SS</sub> = 0 V; T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Considering operation with PLL not bypassed

<sup>3</sup> "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self-clocked mode.

<sup>4</sup> Self-clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

<sup>5</sup> f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

<sup>6</sup> This value is determined by the crystal manufacturer and board design.

<sup>7</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

<sup>8</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>9</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

<sup>10</sup> Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

<sup>11</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

<sup>12</sup> This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

$^{13}$  This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

<sup>14</sup> Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

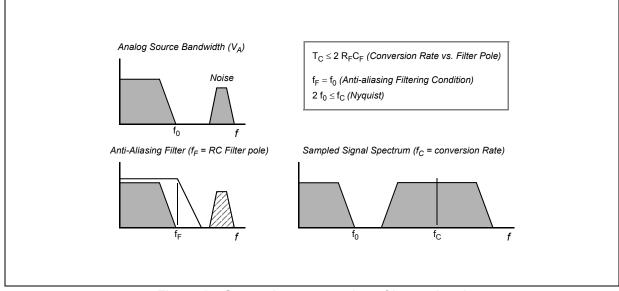

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_L$  sizing is obtained:

#### Eqn. 9

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

Eqn. 10

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing.

Figure 17. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 11 between the ideal and real sampled voltage on  $C_S$ :

| Symbol           | С | Parameter                                    | Conditions <sup>1</sup> | Max value | Unit |

|------------------|---|----------------------------------------------|-------------------------|-----------|------|

| f <sub>max</sub> |   | Maximum working frequency at given number of | 2 wait states           | 66        | MHz  |

|                  |   | wait states in worst conditions              | 0 wait states           | 18        |      |

### Table 34. Flash memory read access timing

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

#### AC specifications 3.16

#### 3.16.1 **Pad AC specifications**

| Table 35. | Output p | in transition | times |

|-----------|----------|---------------|-------|

|-----------|----------|---------------|-------|

| Symb                          |     | с | Parameter                                      |                           | onditions <sup>1</sup>                                                                                 |     | Value | )   | Unit |

|-------------------------------|-----|---|------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Synn                          | 101 | C | Falameter                                      |                           | onations                                                                                               | Min | Тур   | Max | Unit |

| t <sub>tr</sub>               | CC  | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                                                            | —   | —     | 50  | ns   |

|                               |     | Т | SLOW configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0                                                                                            | —   | —     | 100 |      |

|                               |     | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | —   | —     | 125 |      |

|                               |     | D |                                                | C <sub>L</sub> = 25 pF    | $V_{DD} = 3.3 V \pm 10\%$ ,                                                                            | —   | —     | 40  |      |

|                               |     | Т |                                                | C <sub>L</sub> = 50 pF    | PAD3V5V = 1                                                                                            | —   | —     | 50  |      |

|                               |     | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | _   | —     | 75  |      |

| t <sub>tr</sub>               | СС  | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                                                            | —   | —     | 10  | ns   |

|                               |     | Т | MEDIUM configuration                           | C <sub>L</sub> = 50 pF    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1<br>V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | _   | —     | 20  |      |

|                               |     | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | —   | —     | 40  |      |

|                               |     | D |                                                | C <sub>L</sub> = 25 pF    |                                                                                                        | —   | —     | 12  |      |

|                               |     | Т |                                                | C <sub>L</sub> = 50 pF    |                                                                                                        | —   | —     | 25  |      |

|                               |     | D |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | _   | —     | 40  |      |

| t <sub>tr</sub>               | СС  | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                                                            | —   | —     | 4   | ns   |

|                               |     |   | FAST configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1                                                                       | _   | —     | 6   |      |

|                               |     |   |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | _   |       | 12  |      |

|                               |     |   |                                                | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                                                          | —   | —     | 4   |      |

|                               |     |   |                                                | C <sub>L</sub> = 50 pF    | SIUL.PCRx.SRC = 1                                                                                      | —   | —     | 7   |      |

|                               |     |   |                                                | C <sub>L</sub> = 100 pF   |                                                                                                        | —   | —     | 12  |      |

| t <sub>SYM</sub> <sup>3</sup> | СС  | Т | Symmetric transition time, same drive          | V <sub>DD</sub> = 5.0 V : | ± 10%, PAD3V5V = 0                                                                                     | —   | —     | 4   | ns   |

|                               |     |   | strength between N and P transistor            | V <sub>DD</sub> = 3.3 V : | ± 10%, PAD3V5V = 1                                                                                     | —   | —     | 5   |      |

<sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified <sup>2</sup> C<sub>L</sub> includes device and package capacitances (C<sub>PKG</sub> < 5 pF).

<sup>3</sup> Transition timing of both positive and negative slopes will differ maximum 50%

| Symbol             |    | ~ |                                                                                                            | Conditions <sup>1</sup>                                               |     |     |     |      |

|--------------------|----|---|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

|                    |    | С | Parameter                                                                                                  | Conditions                                                            | Min | Тур | Max | Unit |

| t <sub>tr</sub>    | СС | D | Output transition time output pin <sup>3</sup>                                                             | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | —   | -   | 10  | ns   |

|                    |    |   | MEDIUM configuration                                                                                       | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0  | _   | _   | 20  |      |

|                    |    |   |                                                                                                            | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | _   | —   | 40  |      |

|                    |    |   |                                                                                                            | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _   | —   | 12  |      |

|                    |    |   |                                                                                                            | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1  | _   | —   | 25  |      |

|                    |    |   |                                                                                                            | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | _   | —   | 40  |      |

| W <sub>FRST</sub>  | SR | Ρ | RESET input filtered pulse                                                                                 | _                                                                     | _   | -   | 40  | ns   |

| W <sub>NFRST</sub> | SR | Ρ | RESET input not filtered pulse                                                                             | _                                                                     | 500 | —   | _   | ns   |

| t <sub>POR</sub>   | CC | D | Maximum delay before<br>internal reset is released<br>after all V <sub>DD_HV</sub> reach<br>nominal supply | Monotonic $V_{DD_HV}$ supply ramp                                     | —   | _   | 1   | ms   |

| I <sub>WPU</sub>   | СС | Ρ | Weak pull-up current                                                                                       | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                            | 10  | —   | 150 | μA   |

|                    |    |   | absolute value                                                                                             | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                            | 10  | —   | 150 |      |

|                    |    |   |                                                                                                            | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>4</sup>               | 10  |     | 250 |      |

Table 36. RESET electrical characteristics (continued)

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = –40 °C to T\_A  $_{MAX}$ , unless otherwise specified

<sup>2</sup> This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of device reference manual).

$^3~$  CL includes device and package capacitance (CPKG < 5 pF).

<sup>4</sup> The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

## 3.17.2 IEEE 1149.1 interface timing

| No.  | Symbo                             | 1  | с | Parameter                                              | Conditions | Value |     | Unit |

|------|-----------------------------------|----|---|--------------------------------------------------------|------------|-------|-----|------|

| 110. | No. Cymbol                        |    | Ŭ | i uluncter                                             | Conditions | Min   | Мах |      |

| 1    | t <sub>JCYC</sub>                 | CC | D | TCK cycle time                                         | —          | 100   |     | ns   |

| 2    | t <sub>JDC</sub>                  | CC | D | TCK clock pulse width (measured at $V_{DD_HV_IOx}/2$ ) | —          | 40    | 60  | ns   |

| 3    | t <sub>TCKRISE</sub>              | CC | D | TCK rise and fall times (40% – 70%)                    | —          | _     | 3   | ns   |

| 4    | $t_{\text{TMSS},}t_{\text{TDIS}}$ | CC | D | TMS, TDI data setup time                               | —          | 5     | —   | ns   |

Table 37. JTAG pin AC electrical characteristics

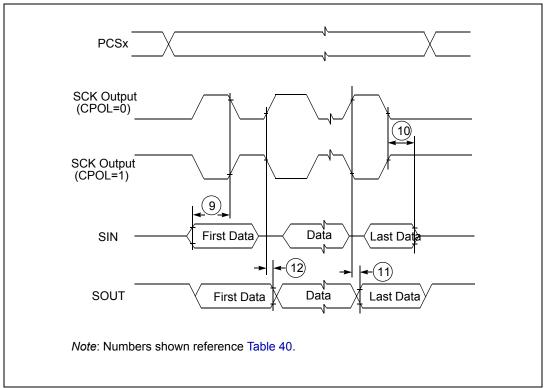

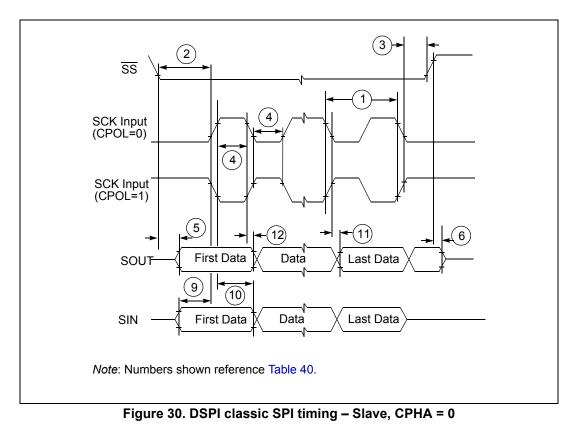

Figure 29. DSPI classic SPI timing – Master, CPHA = 1

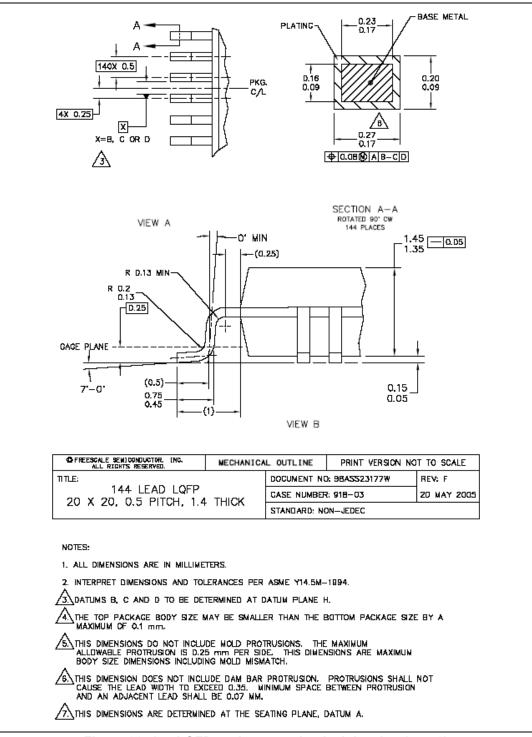

Figure 38. 144 LQFP package mechanical drawing (part 2)

|                                                                                                                                                                                                                                                        | MECHANICAL OUTLINES | DOCUMENT NO: 98ASS23308W |       |        |   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|-------|--------|---|--|--|--|--|

| <b>Treescale</b><br>semiconductor                                                                                                                                                                                                                      | DICTIONARY          |                          | PAGE: | 983    | 5 |  |  |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRCTLY FROM THE DOCUMENT CONTROL. REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE        | THIS DRAWING             | REV:  | Н      |   |  |  |  |  |

| NOTES:                                                                                                                                                                                                                                                 |                     |                          |       |        |   |  |  |  |  |

| 1. ALL DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                  |                     |                          |       |        |   |  |  |  |  |

| 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.                                                                                                                                                                                           |                     |                          |       |        |   |  |  |  |  |

| 3. datums b, c and d to be determined at datum plane H.                                                                                                                                                                                                |                     |                          |       |        |   |  |  |  |  |

| $\overline{\cancel{4.}}$ The top package body size may be smaller than the bottom package size by a maximum of 0.1 mm.                                                                                                                                 |                     |                          |       |        |   |  |  |  |  |

| 5. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSIONS. THE MAXIMUM ALLOWABLE<br>PROTRUSION IS 0.25 mm PER SIDE. THE DIMENSIONS ARE MAXIMUM BODY<br>SIZE DIMENSIONS INCLUDING MOLD MISMATCH.                                                                    |                     |                          |       |        |   |  |  |  |  |

| 6. DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION. PROTRUSIONS SHALL NOT<br>CAUSE THE LEAD WIDTH TO EXCEED 0.35. MINIMUM SPACE BETWEEN PROTRUSION<br>AND AN ADJACENT LEAD SHALL BE 0.07 MM.                                                             |                     |                          |       |        |   |  |  |  |  |

| 7. DIMENSIONS ARE DETERMINED AT THE SEATING PLANE, DATUM A.                                                                                                                                                                                            |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     |                          |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     | I                        |       |        |   |  |  |  |  |

| 100 LEAD LQF                                                                                                                                                                                                                                           | P                   | CASE NUMBER: 9           |       |        |   |  |  |  |  |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                    |                     | STANDARD: NON-           |       |        |   |  |  |  |  |

|                                                                                                                                                                                                                                                        |                     | PACKAGE CODE:            | 8264  | SHEET: | 3 |  |  |  |  |

### Figure 41. 100 LQFP package mechanical drawing (part 3)

| Revision | Date        | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 5   | 06-Oct-2009 | <ul> <li>Removed B[4] and B[5] rows from "Pin muxing" table and inserted them on "System pins" table.</li> <li>Updated package pinout.</li> <li>Rewrote entirely section "Power Up/dpwn Sequencing" section.</li> <li>Renamend "V<sub>DD_LV_PLL</sub>" and "V<sub>SS_LV_PLL</sub>" supply pins with respectively "V<sub>DD_LV_COR3</sub>" and "V<sub>SS_LV_COR3</sub>".</li> <li>Added explicative figures on "Electrical characteristics" section.</li> <li>Updated "Thermal characteristics" for 100-pin.</li> <li>Proposed two different configuration of "voltage regulator Inserted Power Up/Down sequence.</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added "I/O pad current specification" section.</li> <li>Renamed the "Airbag mode" with "Typical mode"and updated the values on "supply current" tables.</li> </ul>                                                                                                          |

| Rev. 6   | 12-Feb-2010 | Inserted label of Y-axis in the "Independent ADC supply" figure.<br>"Recommended Operating Conditions" tables:<br>Updated the T <sub>A</sub> value<br>Moved the T <sub>J</sub> row to "Absolute Maximum Ratings" table.<br>Rewrite note 1 and 3<br>Inverted Min a Typ value of C <sub>DEC2</sub> on "Voltage Regulator Electrical Characteristics" table.<br>Removed an useless duplicate of "Voltage Regulator Electrical Characteristics" table.<br>Inserted the name of C <sub>S</sub> into "Input Equivalent Circuit" figure.<br>Removed leakage lvpp from datasheet.<br>Updated "Supply Current" tables.<br>Added note on "Output pin transition times" table.<br>Updated "Temperature Sensor Electrical Characteristics" table.<br>Updated "16 MHz RC Oscillator Electrical Characteristics" table.<br>Removed the note about the condition from "Flash read access timing" table.<br>Removed the notes that assert the values need to be confirmed before validation. |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2008–2012 Freescale, Inc.

Document Number: MPC5604P Rev. 8 07/2012