# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 68                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 40K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 30x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pef1mll6r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

For high priority interrupt requests, the time from the assertion of the interrupt request from the peripheral to when the processor is executing the interrupt service routine (ISR) has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

- 2 external high priority interrupts directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

# 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the MPC5604P:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module can run on an independent clock source

- On-chip oscillator with automatic level control

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

# 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The PLL has the following major features:

• Input clock frequency: 4–40 MHz

- 32 message buffers of up to 8-bytes data length

- · Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- · Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a six-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

# 1.5.21 Safety port (FlexCAN)

The MPC5604P MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate as fast as 7.5 Mbit/s at 60 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8 bytes data length

- Can be used as a second independent CAN module

# 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

Table 5. Pin muxing

|                   | Pad                          |                                             |                                                            |                                                                |                                    | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------------|------------------------------|---------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|---------|-------------------|---------|---------|

| Port<br>pin       | configuration register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                                  | Peripheral <sup>3</sup>                                        | I/O<br>direction <sup>4</sup>      | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

|                   |                              |                                             |                                                            | Port A (16-bit)                                                |                                    |         |                   | •       |         |

| A[0]              | PCR[0]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[0]<br>ETC[0]<br>SCK<br>F[0]<br>EIRQ[0]                | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | 1/0<br>1/0<br>0<br>1               | Slow    | Medium            | 51      | 73      |

| A[1]              | PCR[1]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[1]<br>ETC[1]<br>SOUT<br>F[1]<br>EIRQ[1]               | SIUL<br>eTimer_0<br>DSPI_2<br>FCU_0<br>SIUL                    | /O<br> /O<br>0<br>                 | Slow    | Medium            | 52      | 74      |

| A[2] <sup>6</sup> | PCR[2]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[2]<br>ETC[2]<br>—<br>A[3]<br>SIN<br>ABS[0]<br>EIRQ[2] | SIUL<br>eTimer_0<br>—<br>FlexPWM_0<br>DSPI_2<br>MC_RGM<br>SIUL | /O<br> /O<br> -<br> <br> <br> <br> | Slow    | Medium            | 57      | 84      |

| A[3] <sup>6</sup> | PCR[3]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[3]<br>ETC[3]<br>CS0<br>B[3]<br>ABS[2]<br>EIRQ[3]      | SIUL<br>eTimer_0<br>DSPI_2<br>FlexPWM_0<br>MC_RGM<br>SIUL      | /O<br> /O<br> /O<br>0<br> <br>     | Slow    | Medium            | 64      | 92      |

| A[4] <sup>6</sup> | PCR[4]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[4]<br>ETC[0]<br>CS1<br>ETC[4]<br>FAB<br>EIRQ[4]       | SIUL<br>eTimer_1<br>DSPI_2<br>eTimer_0<br>MC_RGM<br>SIUL       | /O<br> /O<br>0<br> /O<br> <br>     | Slow    | Medium            | 75      | 108     |

| A[5]              | PCR[5]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[5]<br>CS0<br>ETC[5]<br>CS7<br>EIRQ[5]                 | SIUL<br>DSPI_1<br>eTimer_1<br>DSPI_0<br>SIUL                   | /O<br> /O<br> /O<br>0<br>          | Slow    | Medium            | 8       | 14      |

| A[6]              | PCR[6]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[6]<br>SCK<br>—<br>—<br>EIRQ[6]                        | SIUL<br>DSPI_1<br>—<br>SIUL                                    | /O<br> /O<br><br>                  | Slow    | Medium            | 2       | 2       |

| A[7]              | PCR[7]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[7]<br>SOUT<br>—<br>EIRQ[7]                            | SIUL<br>DSPI_1<br>—<br>SIUL                                    | /O<br>O<br>—<br>I                  | Slow    | Medium            | 4       | 10      |

|             | Pad                             |                                             |                                                   |                                             |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                         | Peripheral <sup>3</sup>                     | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| B[10]       | PCR[26]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[26]<br>—<br>—<br>—<br>AN[12]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    | _       | _                 | 36      | 53      |

| B[11]       | PCR[27]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[27]<br>—<br>—<br>—<br>AN[13]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    |         | _                 | 37      | 54      |

| B[12]       | PCR[28]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[28]<br><br><br>AN[14]                        | SIUL<br>—<br>—<br><br>ADC_0 / ADC_1         | Input only                    | _       | _                 | 38      | 55      |

| B[13]       | PCR[29]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[29]<br>—<br>—<br>—<br>AN[0]<br>RXD           | SIUL<br>—<br>—<br>ADC_1<br>LIN_1            | Input only                    | _       | _                 | 42      | 60      |

| B[14]       | PCR[30]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[30]<br>—<br>—<br>AN[1]<br>ETC[4]<br>EIRQ[19] | SIUL<br>—<br>—<br>ADC_1<br>eTimer_0<br>SIUL | Input only                    |         | _                 | 44      | 64      |

| B[15]       | PCR[31]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[31]<br>—<br>—<br>—<br>AN[2]<br>EIRQ[20]      | SIUL<br>—<br>—<br>ADC_1<br>SIUL             | Input only                    | _       | _                 | 43      | 62      |

|             |                                 |                                             |                                                   | Port C (16-bit)                             |                               |         |                   | •       |         |

| C[0]        | PCR[32]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[32]<br>—<br>—<br>—<br>AN[3]                  | SIUL<br>—<br>—<br>—<br>ADC_1                | Input only                    | _       |                   | 45      | 66      |

| C[1]        | PCR[33]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[33]<br>—<br>—<br>—<br>AN[2]                  | SIUL<br>—<br>—<br>—<br>ADC_0                | Input only                    | _       |                   | 28      | 41      |

Table 5. Pin muxing (continued)

|             | Pad                             |                                      |                                                              |                                                                  |                                | Pad s   | speed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|--------------------------------|---------|--------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                                                    | Peripheral <sup>3</sup>                                          | I/O<br>direction <sup>4</sup>  | SRC = 0 | SRC = 1            | 100-pin | 144-pin |

| C[11]       | PCR[43]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[43]<br>ETC[4]<br>CS2<br>CS0                             | SIUL<br>eTimer_0<br>DSPI_2<br>DSPI_3                             | I/O<br>I/O<br>O<br>I/O         | Slow    | Medium             | 55      | 80      |

| C[12]       | PCR[44]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[44]<br>ETC[5]<br>CS3<br>CS1                             | SIUL<br>eTimer_0<br>DSPI_2<br>DSPI_3                             | I/O<br>I/O<br>O                | Slow    | Medium             | 56      | 82      |

| C[13]       | PCR[45]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[45]<br>ETC[1]<br>—<br>EXT_IN<br>EXT_IN                  | SIUL<br>eTimer_1<br>—<br>CTU_0<br>FlexPWM_0                      | /O<br> /O<br><br> <br>         | Slow    | Medium             | 71      | 101     |

| C[14]       | PCR[46]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[46]<br>ETC[2]<br>EXT_TGR<br>—                           | SIUL<br>eTimer_1<br>CTU_0<br>—                                   | I/O<br>I/O<br>O<br>—           | Slow    | Medium             | 72      | 103     |

| C[15]       | PCR[47]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[47]<br>CA_TR_EN<br>ETC[0]<br>A[1]<br>EXT_IN<br>EXT_SYNC | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0<br>CTU_0<br>FlexPWM_0 | I/O<br>O<br>I/O<br>O<br>I<br>I | Slow    | Symmetric          | 85      | 124     |

|             |                                 |                                      |                                                              | Port D (16-bit)                                                  | 1                              |         | 1                  |         |         |

| D[0]        | PCR[48]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[48]<br>CA_TX<br>ETC[1]<br>B[1]                          | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0                       | I/O<br>O<br>I/O<br>O           | Slow    | Symmetric          | 86      | 125     |

| D[1]        | PCR[49]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[49]<br>—<br>ETC[2]<br>EXT_TRG<br>CA_RX                  | SIUL<br>—<br>eTimer_1<br>CTU_0<br>FlexRay_0                      | ₩<br>10 10 -                   | Slow    | Medium             | 3       | 3       |

| D[2]        | PCR[50]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[50]<br>—<br>ETC[3]<br>X[3]<br>CB_RX                     | SIUL<br>—<br>eTimer_1<br>FlexPWM_0<br>FlexRay_0                  | /O<br><br> /O<br> /O<br>       | Slow    | Medium             | 97      | 140     |

| D[3]        | PCR[51]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[51]<br>CB_TX<br>ETC[4]<br>A[3]                          | SIUL<br>FlexRay_0<br>eTimer_1<br>FlexPWM_0                       | I/O<br>O<br>I/O<br>O           | Slow    | Symmetric          | 89      | 128     |

Table 5. Pin muxing (continued)

|             | Pad                             |                                      |                                      |                                  |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|--------------------------------------|----------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                            | Peripheral <sup>3</sup>          | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| G[3]        | PCR[99]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[99]<br>A[2]<br>—<br>—           | SIUL<br>FlexPWM_0<br>—           | I/O<br>O<br>—                 | Slow    | Medium            | _       | 104     |

| G[4]        | PCR[100]                        | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[100]<br>B[2]<br>—<br>—          | SIUL<br>FlexPWM_0<br>            | I/O<br>O<br>—                 | Slow    | Medium            |         | 100     |

| G[5]        | PCR[101]                        | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[101]<br>X[3]<br>—<br>—          | SIUL<br>FlexPWM_0<br>—           | I/O<br>I/O<br>—               | Slow    | Medium            | —       | 85      |

| G[6]        | PCR[102]                        | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[102]<br>A[3]<br>—<br>—          | SIUL<br>FlexPWM_0<br>            | I/O<br>O<br>—                 | Slow    | Medium            |         | 98      |

| G[7]        | PCR[103]                        | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[103]<br>B[3]<br>—<br>—          | SIUL<br>FlexPWM_0<br>—           | I/O<br>O<br>—                 | Slow    | Medium            | —       | 83      |

| G[8]        | PCR[104]                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[104]<br>—<br>—<br>—<br>FAULT[0] | SIUL<br>—<br>—<br>FlexPWM_0      | /O<br><br>                    | Slow    | Medium            |         | 81      |

| G[9]        | PCR[105]                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[105]<br>—<br>—<br>FAULT[1]      | SIUL<br>—<br>—<br>FlexPWM_0      | I/O<br>—<br>—<br>—<br>—       | Slow    | Medium            |         | 79      |

| G[10]       | PCR[106]                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[106]<br>—<br>—<br>FAULT[2]      | SIUL<br>—<br>—<br><br>FlexPWM_0  | /O<br><br>                    | Slow    | Medium            | _       | 77      |

| G[11]       | PCR[107]                        | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[107]<br>—<br>—<br>FAULT[3]      | SIUL<br>—<br>—<br>—<br>FlexPWM_0 | I/O<br>—<br>—<br>—<br>—       | Slow    | Medium            |         | 75      |

Table 5. Pin muxing (continued)

<sup>1</sup> ALT0 is the primary (default) function for each port after reset.

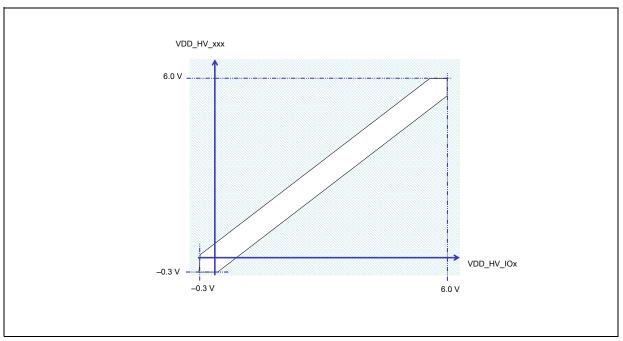

Figure 4. Power supplies constraints (–0.3 V  $\leq$  V\_{DD\_HV\_IOx}  $\leq$  6.0 V)

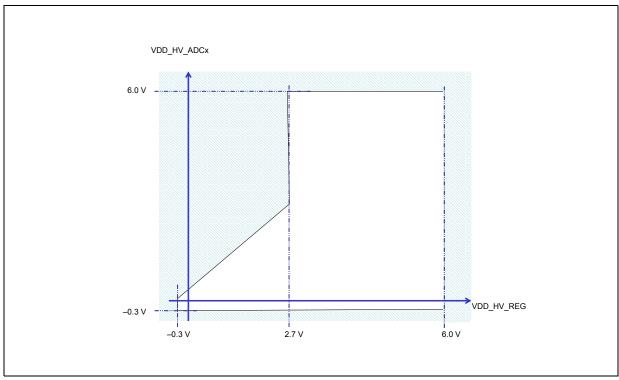

The MPC5604P supply architecture allows of having ADC supply managed independently from standard  $V_{DD_HV}$  supply. Figure 5 shows the constraints of the ADC power supply.

Figure 5. Independent ADC supply (–0.3 V  $\leq$  V\_{DD\_HV\_REG}  $\leq$  6.0 V)

- <sup>4</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

- $^5~$  The low voltage supplies (V\_{DD\\_LV\\_xxx}) are not all independent.

- $V_{DD\_LV\_COR1}$  and  $V_{DD\_LV\_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly,  $V_{SS\_LV\_COR1}$  and  $V_{SS\_LV\_COR2}$  are internally shorted.

- $V_{DD_LV_REGCOR}$  and  $V_{DD_LV_REGCORx}$  are physically shorted internally, as are  $V_{SS_LV_REGCOR}$  and  $V_{SS_LV_CORx}$ .

| Cumhal                               |    | Devenueter                                           | Conditions                            | Val                          | ue                           | 11   |

|--------------------------------------|----|------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| Symbol                               |    | Parameter                                            | Conditions                            | Min                          | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                      | SR | Device ground                                        |                                       | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup>  | SR | 3.3 V input/output supply voltage                    | _                                     | 3.0                          | 3.6                          | V    |

| V <sub>SS_HV_IOx</sub>               | SR | Input/output ground voltage                          | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_FL</sub>                | SR | 3.3 V code and data flash                            | _                                     | 3.0                          | 3.6                          | V    |

|                                      |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_FL</sub>                | SR | Code and data flash ground                           | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_OSC</sub>               | SR | 3.3 V crystal oscillator amplifier                   | _                                     | 3.0                          | 3.6                          | V    |

|                                      |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_OSC</sub>               | SR | 3.3 V crystal oscillator amplifier reference voltage | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_REG</sub>               | SR | 3.3 V voltage regulator supply                       | —                                     | 3.0                          | 3.6                          | V    |

|                                      |    | voltage                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup> | SR | 3.3 V ADC_0 supply and high                          | _                                     | 3.0                          | 5.5                          | V    |

|                                      |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | 5.5                          |      |

| V <sub>SS_HV_ADC0</sub>              | SR | ADC_0 ground and low<br>reference voltage            | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_ADC1</sub> <sup>3</sup> | SR | 3.3 V ADC_1 supply and high                          | —                                     | 3.0                          | 5.5                          | V    |

|                                      |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | 5.5                          |      |

| V <sub>SS_HV_ADC1</sub>              |    | ADC_1 ground and low reference voltage               | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> 4,5        | CC | Internal supply voltage                              | —                                     | _                            | _                            | V    |

Table 9. Recommended operating conditions (3.3 V)

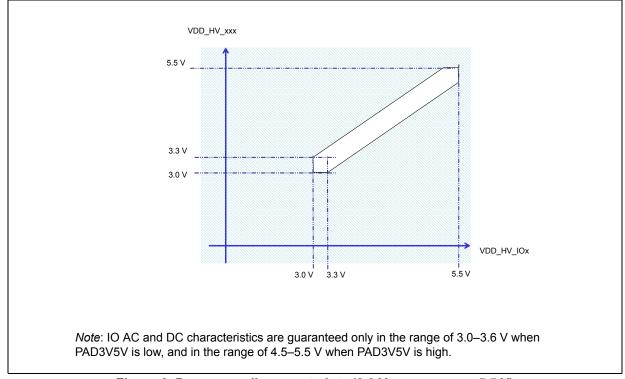

Figure 6 shows the constraints of the different power supplies.

Figure 6. Power supplies constraints (3.0 V  $\leq$  V<sub>DD\_HV\_IOx</sub>  $\leq$  5.5 V)

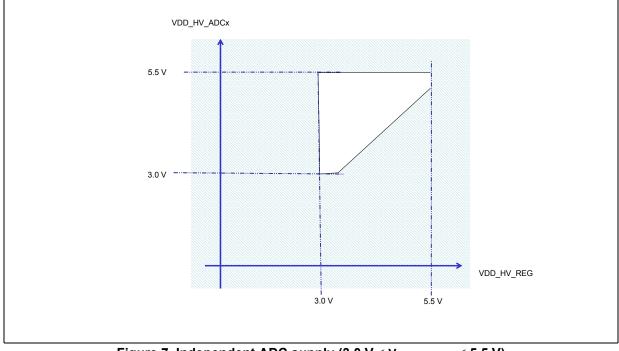

The MPC5604P supply architecture allows the ADC supply to be managed independently from the standard  $V_{DD_HV}$  supply. Figure 7 shows the constraints of the ADC power supply.

Figure 7. Independent ADC supply (3.0 V  $\leq$  V\_{DD\_HV\_REG}  $\leq$  5.5 V)

| Symbol          | с | Parameter                                          | Conditions                        | Va   | lue | Unit |

|-----------------|---|----------------------------------------------------|-----------------------------------|------|-----|------|

| Symbol          | C | Falameter                                          | Conditions                        | Min  | Max | Unit |

| I <sub>PD</sub> | Ρ | Equivalent pull-down current                       | $V_{IN} = V_{IL}$                 | 10   | _   | μA   |

|                 |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | _    | 130 |      |

| IIL             | Ρ | Input leakage current (all<br>bidirectional ports) | T <sub>A</sub> = -40 to 125 °C    | -1   | 1   | μA   |

| IIL             | Ρ | Input leakage current (all ADC input-only ports)   | T <sub>A</sub> = -40 to 125 °C    | -0.5 | 0.5 | μA   |

| C <sub>IN</sub> | D | Input capacitance                                  | —                                 | _    | 10  | pF   |

|                 | D | RESET, equivalent pull-up current                  | V <sub>IN</sub> = V <sub>IL</sub> | –130 | _   | μA   |

| I <sub>PU</sub> |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | _    | -10 | μΛ   |

Table 19. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0) (continued)

<sup>1</sup> "SR" parameter values must not exceed the absolute maximum ratings shown in Table 7.

Table 20. Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol                  | с |                | Parameter                                      | Conditions                                                    |        | Va    | lue   | Unit |

|-------------------------|---|----------------|------------------------------------------------|---------------------------------------------------------------|--------|-------|-------|------|

| Gymbol                  | Ŭ | i didileter    |                                                | Conditions                                                    |        | Тур   | Max   |      |

| I <sub>DD_LV_CORx</sub> | Т |                | RUN—Maximum mode <sup>1</sup>                  | V <sub>DD_LV_CORx</sub>                                       | 40 MHz | 62    | 77    | mA   |

|                         |   |                |                                                | externally forced at 1.3 V                                    | 64 MHz | 71    | 88    | 1    |

|                         |   |                | RUN—Typical mode <sup>2</sup>                  |                                                               | 40 MHz | 45    | 56    | 1    |

|                         |   |                |                                                |                                                               | 64 MHz | 52    | 65    | 1    |

|                         | Ρ |                | RUN—Maximum mode <sup>3</sup>                  | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | 64 MHz | 60    | 75    |      |

|                         |   | ent            | HALT mode <sup>4</sup>                         | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1.5   | 10    |      |

|                         |   | Supply current | STOP mode <sup>5</sup>                         | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1     | 10    |      |

| I <sub>DD_FLASH</sub>   | Т | ddng           | Flash during read                              | V <sub>DD_HV_FL</sub> at 5.0 V                                | —      | 10    | 12    |      |

|                         |   | 0,             | Flash during erase operation on 1 flash module | V <sub>DD_HV_FL</sub> at 5.0 V                                | _      | 15    | 19    |      |

| I <sub>DD_ADC</sub>     | Т |                | ADC—Maximum mode <sup>1</sup>                  | V <sub>DD_HV_ADC0</sub> at 5.0 V                              | ADC_1  | 3.5   | 5     | -    |

|                         |   |                |                                                | V <sub>DD_HV_ADC1</sub> at 5.0 V<br>f <sub>ADC</sub> = 16 MHz | ADC_0  | 3     | 4     | 1    |

|                         |   |                | ADC—Typical mode <sup>2</sup>                  |                                                               | ADC_1  | 0.8   | 1     | 1    |

|                         |   |                |                                                |                                                               | ADC_0  | 0.005 | 0.006 | 1    |

| I <sub>DD_OSC</sub>     | Т |                | Oscillator                                     | V <sub>DD_OSC</sub> at 5.0 V                                  | 8 MHz  | 2.6   | 3.2   | 1    |

<sup>1</sup> Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

<sup>2</sup> Typical mode configurations: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

| Ded     | 144       | LQFP        | 100 LQFP  |             |  |  |

|---------|-----------|-------------|-----------|-------------|--|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |  |

| PAD[13] | 10%       | 9%          | 12%       | 11%         |  |  |

| PAD[82] | 10%       | 9%          | —         | _           |  |  |

| PAD[22] | 10%       | 9%          | 13%       | 12%         |  |  |

| PAD[83] | 10%       | 9%          | —         | _           |  |  |

| PAD[50] | 10%       | 9%          | 14%       | 12%         |  |  |

| PAD[97] | 10%       | 9%          | —         | _           |  |  |

| PAD[38] | 10%       | 9%          | 14%       | 13%         |  |  |

| PAD[14] | 9%        | 8%          | 14%       | 13%         |  |  |

| PAD[15] | 9%        | 8%          | 15%       | 13%         |  |  |

#### Table 24. I/O weight (continued)

#### Table 25. I/O consumption

| Symbol                             |    | с | Parameter                          | Condi                          | tions <sup>1</sup>                            |     | Value |     | Unit |

|------------------------------------|----|---|------------------------------------|--------------------------------|-----------------------------------------------|-----|-------|-----|------|

| Gymbol                             |    | Ŭ | i arameter                         | Condi                          |                                               | Min | Тур   | Max | onn  |

| I <sub>SWTSLW</sub> ,2             | СС | D | for SLOW                           | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _     | 20  | mA   |

|                                    |    |   | configuration                      |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _     | 16  |      |

| I <sub>SWTMED</sub> <sup>(2)</sup> | СС | D | for MEDIUM                         | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _     | 29  | mA   |

|                                    |    |   | configuration                      | F                              | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   |       | 17  |      |

| I <sub>SWTFST</sub> <sup>(2)</sup> | СС | D | Dynamic I/O current<br>for FAST    | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _     | 110 | mA   |

|                                    |    |   | configuration                      |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _     | 50  |      |

| I <sub>RMSSLW</sub>                | СС | D |                                    | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 5.0 V \pm 10\%$                     | _   | _     | 2.3 | mA   |

|                                    |    |   | I/O current for SLOW configuration | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 0                                   | _   | _     | 3.2 |      |

|                                    |    |   |                                    | C <sub>L</sub> = 100 pF, 2 MHz | 1                                             |     | _     | 6.6 |      |

|                                    |    |   |                                    | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     | _     | 1.6 |      |

|                                    |    |   |                                    | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 1                                   | —   | —     | 2.3 |      |

|                                    |    |   |                                    | C <sub>L</sub> = 100 pF, 2 MHz | ]                                             | _   | _     | 4.7 |      |

| Symb             | <b>a</b> l | N C Parameter |                                   | Va | Unit |      |

|------------------|------------|---------------|-----------------------------------|----|------|------|

| Synib            | 01         | U             | raiameter                         |    | Мах  | onn  |

| f <sub>OSC</sub> | S<br>R     | _             | Oscillator frequency              | 4  | 40   | MHz  |

| 9 <sub>m</sub>   | _          | Ρ             | Transconductance                  | 4  | 20   | mA/V |

| V <sub>OSC</sub> | —          | Т             | Oscillation amplitude on XTAL pin | 1  | _    | V    |

| toscsu           | -          | Т             | Start-up time <sup>1,2</sup>      | 8  | _    | ms   |

<sup>1</sup> The start-up time is dependent upon crystal characteristics, board leakage, etc., high ESR and excessive capacitive loads can cause long start-up time.

<sup>2</sup> Value captured when amplitude reaches 90% of XTAL

| Symbol            |    | Parameter                   |      | Value |      |        |  |

|-------------------|----|-----------------------------|------|-------|------|--------|--|

|                   |    |                             |      | Тур   | Мах  | - Unit |  |

| f <sub>OSC</sub>  | SR | Oscillator frequency 4 – 40 |      |       |      |        |  |

| f <sub>CLK</sub>  | SR | Frequency in bypass         | _    | _     | 64   | MHz    |  |

| t <sub>rCLK</sub> | SR | Rise/fall time in bypass    | _    | —     | 1    | ns     |  |

| t <sub>DC</sub>   | SR | Duty cycle                  | 47.5 | 50    | 52.5 | %      |  |

#### Table 28. Input clock characteristics

# 3.12 FMPLL electrical characteristics

#### Table 29. FMPLL electrical characteristics

| Symbol                                           | с | Parameter                                                | Conditions <sup>1</sup>                          | Va  | Unit                 |      |

|--------------------------------------------------|---|----------------------------------------------------------|--------------------------------------------------|-----|----------------------|------|

| Symbol                                           | Č | raiametei                                                | Conditions                                       | Min | Max                  | Onit |

| f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | D | PLL reference frequency range <sup>2</sup>               | Crystal reference                                | 4   | 40                   | MHz  |

| f <sub>PLLIN</sub>                               | D | Phase detector input frequency range (after pre-divider) |                                                  | 4   | 16                   | MHz  |

| f <sub>FMPLLOUT</sub>                            | D | Clock frequency range in normal mode                     | —                                                | 16  | 120                  | MHz  |

| f <sub>FREE</sub>                                | Ρ | Free-running frequency                                   | Measured using clock<br>division — typically /16 | 20  | 150                  | MHz  |

| t <sub>CYC</sub>                                 | D | System clock period                                      | —                                                | —   | 1 / f <sub>SYS</sub> | ns   |

| f <sub>LORL</sub>                                | D | Loss of reference frequency window <sup>3</sup>          | Lower limit                                      | 1.6 | 3.7                  | MHz  |

| f <sub>LORH</sub>                                |   |                                                          | Upper limit                                      | 24  | 56                   |      |

| f <sub>SCM</sub>                                 | D | D Self-clocked mode frequency <sup>4,5</sup>             |                                                  | 20  | 150                  | MHz  |

Figure 23. JTAG boundary scan timing

# 3.17.3 Nexus timing

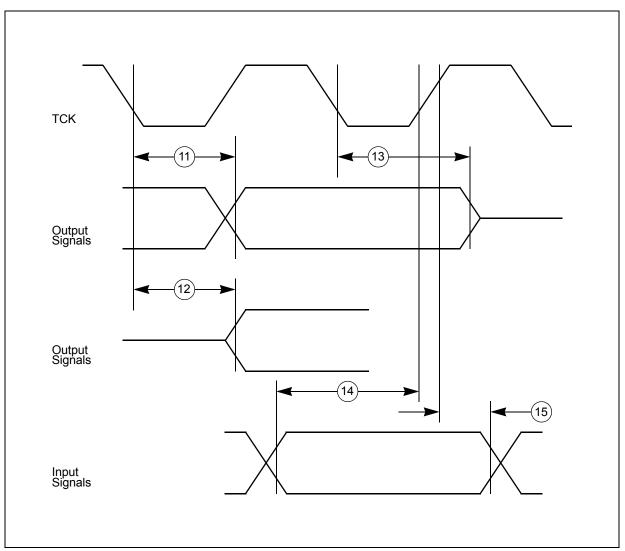

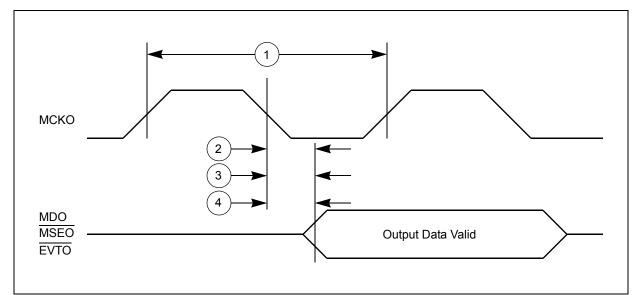

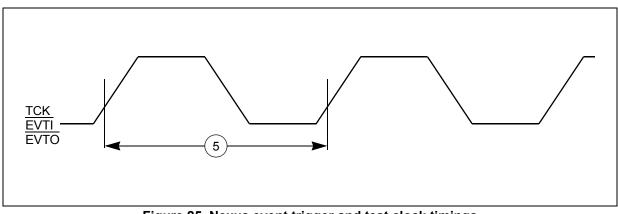

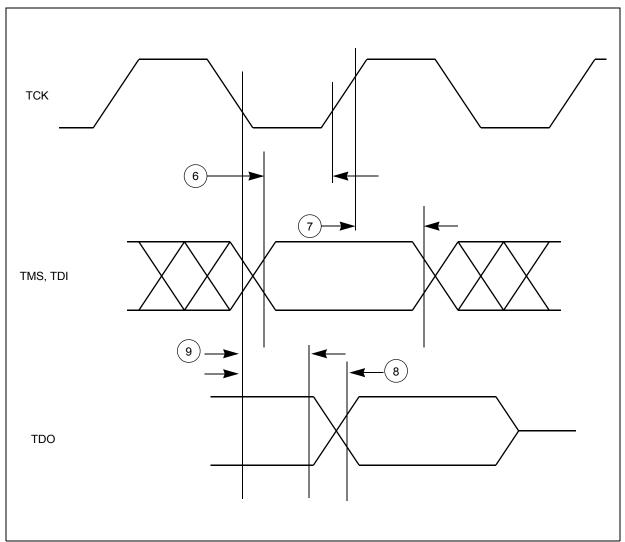

| Table 38. Nexu | s debug | port | timing <sup>1</sup> |

|----------------|---------|------|---------------------|

|----------------|---------|------|---------------------|

| No. | Symbol             |    | nbol C Parameter |                                          | Unit            |     |     |      |

|-----|--------------------|----|------------------|------------------------------------------|-----------------|-----|-----|------|

|     |                    | 51 | C                | r ai ainetei                             | Min             | Тур | Мах | onit |

| 1   | t <sub>MCYC</sub>  | CC | D                | MCKO cycle time                          | 32              |     |     | ns   |

| 2   | t <sub>MDOV</sub>  | CC | D                | MCKO low to MDO data valid <sup>2</sup>  | _               | _   | 6   | ns   |

| 3   | t <sub>MSEOV</sub> | CC | D                | MCKO low to MSEO data valid <sup>2</sup> | _               | _   | 6   | ns   |

| 4   | t <sub>EVTOV</sub> | CC | D                | MCKO low to EVTO data valid <sup>2</sup> | —               | _   | 6   | ns   |

| 5   | t <sub>TCYC</sub>  | CC | D                | TCK cycle time                           | 64 <sup>3</sup> | _   | —   | ns   |

| No. | Symbol             |    | с | Parameter                   |     | Unit |     |      |

|-----|--------------------|----|---|-----------------------------|-----|------|-----|------|

| NO. |                    |    |   | Falameter                   | Min | Тур  | Мах | onit |

| 6   | t <sub>NTDIS</sub> | СС | D | TDI data setup time         | 6   | —    | _   | ns   |

|     | t <sub>NTMSS</sub> | CC | D | TMS data setup time         | 6   | _    | _   | ns   |

| 7   | t <sub>NTDIH</sub> | CC | D | TDI data hold time          | 10  | —    | _   | ns   |

|     | t <sub>NTMSH</sub> | CC | D | TMS data hold time          | 10  | —    | _   | ns   |

| 8   | t <sub>TDOV</sub>  | СС | D | TCK low to TDO data valid   | —   | _    | 35  | ns   |

| 9   | t <sub>TDOI</sub>  | CC | D | TCK low to TDO data invalid | 6   | _    | _   | ns   |

Table 38. Nexus debug port timing<sup>1</sup> (continued)

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

<sup>2</sup> MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

<sup>3</sup> Lower frequency is required to be fully compliant to standard.

Figure 24. Nexus output timing

Figure 25. Nexus event trigger and test clock timings

Figure 26. Nexus TDI, TMS, TDO timing

# 3.17.4 External interrupt timing (IRQ pin)

### Table 39. External interrupt timing<sup>1</sup>

| No | No. Symbol        |    | с | Parameter                          | Conditions | Value              |     | Unit             |

|----|-------------------|----|---|------------------------------------|------------|--------------------|-----|------------------|

|    |                   |    | Ŭ |                                    | Conditions | Min                | Мах | Onic             |

| 1  | t <sub>IPWL</sub> | CC | D | IRQ pulse width low                | —          | 4                  | _   | t <sub>CYC</sub> |

| 2  | t <sub>IPWH</sub> | СС | D | IRQ pulse width high               | —          | 4                  | _   | t <sub>CYC</sub> |

| 3  | t <sub>ICYC</sub> | CC | D | IRQ edge to edge time <sup>2</sup> | —          | 4 + N <sup>3</sup> | _   | t <sub>CYC</sub> |

<sup>1</sup> IRQ timing specified at f<sub>SYS</sub> = 64 MHz and V<sub>DD\_HV\_IOx</sub> = 3.0 V to 5.5 V, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>, and C<sub>L</sub> = 200 pF with SRC = 0b00.

$^{2}$  Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

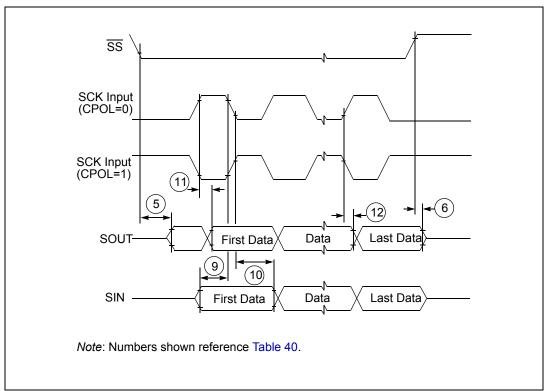

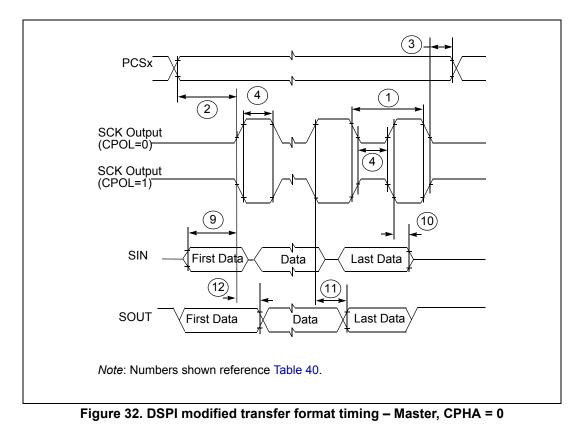

Figure 31. DSPI classic SPI timing – Slave, CPHA = 1

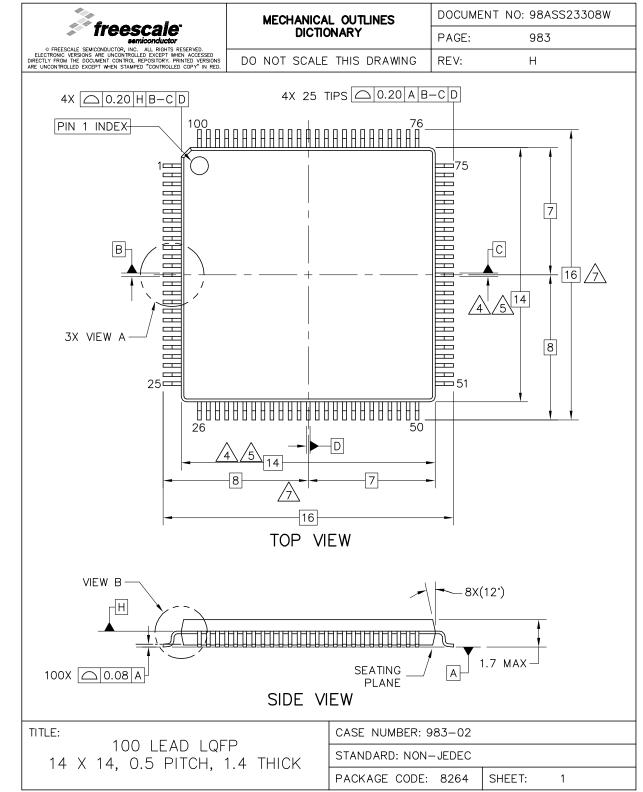

## 4.1.2 100 LQFP mechanical outline drawing

Figure 39. 100 LQFP package mechanical drawing (part 1)

# Appendix A Abbreviations

Table A-1 lists abbreviations used in this document.

#### Table A-1. Abbreviations

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| CMOS         | Complementary metal-oxide-semiconductor |

| СРНА         | Clock phase                             |

| CPOL         | Clock polarity                          |

| CS           | Peripheral chip select                  |

| DUT          | Device under test                       |

| ECC          | Error code correction                   |

| EVTO         | Event out                               |

| GPIO         | General purpose input/output            |

| MC           | Modulus counter                         |

| МСКО         | Message clock out                       |

| MCU          | Microcontroller unit                    |

| MDO          | Message data out                        |

| MSEO         | Message start/end out                   |

| MTFE         | Modified timing format enable           |

| NPN          | Negative-positive-negative              |

| NVUSRO       | Non-volatile user options register      |

| PTF          | Post trimming frequency                 |

| PWM          | Pulse width modulation                  |

| RBW          | Resolution bandwidth                    |

| SCK          | Serial communications clock             |

| SOUT         | Serial data out                         |

| TCK          | Test clock input                        |

| TDI          | Test data input                         |

| TDO          | Test data output                        |

| TMS          | Test mode select                        |

| Revision           | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>Rev. 8 |      | <ul> <li>Section 1.5.4, "Flash memory: Changed "Data flash memory: 32-bit ECC" to "Data flash memory: 64-bit ECC"</li> <li>Figure 42 (Commercial product code structure), replaced "C = 60 MHz, 5 V" and "D = 60 MHz, 3.3 V" with respectively "C = 40 MHz, 5 V" and "D = 40 MHz, 3.3 V"</li> <li>Table 7 (Absolute maximum ratings), updated TV<sub>DD</sub> parameter, the minimum value to 3.0 V/s and the maximum value to 0.5 V/µs</li> <li>Table 5 (Pin muxing), changed the description in the column "I/O direction" from "I/O" to "O" for the following port pins: A[10] with function B[0]</li> <li>A[11] with function A[2]</li> <li>A[12] with function A[2]</li> <li>A[13] with function B[2]</li> <li>C[7] with function A[1]</li> <li>C[10] with function A[1]</li> <li>D[0] with function B[1]</li> <li>D[10] with function A[1]</li> <li>D[11] with function B[0]</li> <li>D[13] with function B[1]</li> <li>D[14] with function B[1]</li> <li>Updated Section 3.8.1, "Voltage regulator electrical characteristics</li> </ul> |

|                    |      | Added Table 25 (I/O consumption)<br>Section 3.10, DC electrical characteristics:<br>deleted references to "oscillator margin"<br>deleted subsection "NVUSRO[OSCILLATOR_MARGIN] field description"<br>Table <u>19 (DC</u> electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)), added IPU row<br>for RESET pin<br>Table <u>21 (DC</u> electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)), added IPU row<br>for RESET pin<br>Table <u>31 (ADC conversion characteristics</u> ), added V <sub>INAN</sub> entry<br>Removed "Order codes" table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 42. Revision history (continued)

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2008–2012 Freescale, Inc.

Document Number: MPC5604P Rev. 8 07/2012