Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status     Active       Core Processor     e200z0h       Core Size     32-Bit Single-Core |  |

|---------------------------------------------------------------------------------------------------|--|

|                                                                                                   |  |

| Core Size 32-Bit Single-Core                                                                      |  |

|                                                                                                   |  |

| Speed 64MHz                                                                                       |  |

| Connectivity CANbus, FlexRay, LINbus, SPI, UART/USART                                             |  |

| Peripherals DMA, POR, PWM, WDT                                                                    |  |

| Number of I/O 108                                                                                 |  |

| Program Memory Size 512KB (512K x 8)                                                              |  |

| Program Memory Type FLASH                                                                         |  |

| EEPROM Size64K x 8                                                                                |  |

| RAM Size 40K x 8                                                                                  |  |

| Voltage - Supply (Vcc/Vdd) 3V ~ 5.5V                                                              |  |

| Data Converters A/D 30x10b                                                                        |  |

| Oscillator Type Internal                                                                          |  |

| Operating Temperature -40°C ~ 125°C (TA)                                                          |  |

| Mounting Type Surface Mount                                                                       |  |

| Package / Case 144-LQFP                                                                           |  |

| Supplier Device Package144-LQFP (20x20)                                                           |  |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pef1mlq6              |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

## 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5603P/4P series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 1.3 Device comparison

Table 1 provides a summary of different members of the MPC5604P family and their features to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                              | MPC5603P                        | MPC5604P        |  |

|------------------------------------------------------|---------------------------------|-----------------|--|

| Code flash memory (with ECC)                         | 384 KB                          | 512 KB          |  |

| Data flash memory / EE option (with ECC)             | 64 KB (optic                    | onal feature)   |  |

| SRAM (with ECC)                                      | 36 KB                           | 40 KB           |  |

| Processor core                                       | 32-bit e                        | 200z0h          |  |

| Instruction set                                      | VLE (variable le                | ength encoding) |  |

| CPU performance                                      | 0–64                            | MHz             |  |

| FMPLL (frequency-modulated phase-locked loop) module | 2                               |                 |  |

| INTC (interrupt controller) channels                 | 147                             |                 |  |

| PIT (periodic interrupt timer)                       | 1 (includes four 32-bit timers) |                 |  |

| eDMA (enhanced direct memory access) channels        | 16                              |                 |  |

| FlexRay <sup>1</sup>                                 | Optional feature                |                 |  |

| FlexCAN (controller area network)                    | 2 <sup>2,3</sup>                |                 |  |

| Safety port                                          | Yes (via second FlexCAN module) |                 |  |

| FCU (fault collection unit)                          | Yes                             |                 |  |

| CTU (cross triggering unit)                          | Yes                             |                 |  |

| Block                                          | Function                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)              | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                       | Block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                          |

| Clock generation module<br>(MC_CGM)            | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Controller area network (FlexCAN)              | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Cross triggering unit (CTU)                    | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                         | Supports simultaneous connections between two master ports and three slave ports; supports a 32-bit address bus width and a 32-bit data bus width                                                                                                                                                                 |

| Cyclic redundancy check (CRC)                  | CRC checksum generator                                                                                                                                                                                                                                                                                            |

| Deserial serial peripheral interface<br>(DSPI) | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)           | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels                                                                                                                                                                                            |

| Enhanced timer (eTimer)                        | Provides enhanced programmable up/down modulo counting                                                                                                                                                                                                                                                            |

| Error correction status module<br>(ECSM)       | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| External oscillator (XOSC)                     | Provides an output clock used as input reference for FMPLL_0 or as reference clock for specific modules depending on system needs                                                                                                                                                                                 |

| Fault collection unit (FCU)                    | Provides functional safety to the device                                                                                                                                                                                                                                                                          |

| Flash memory                                   | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| Frequency-modulated phase-locked loop (FMPLL)  | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Interrupt controller (INTC)                    | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                             | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with minimum load on CPU                                                                                                                                                                                                  |

| Mode entry module (MC_ME)                      | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Periodic interrupt timer (PIT)                 | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                         |

| Peripheral bridge (PBRIDGE)                    | Interface between the system bus and on-chip peripherals                                                                                                                                                                                                                                                          |

| Power control unit (MC_PCU)                    | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

## 1.5.23 Serial communication interface module (LINFlex)

The LINFlex (local interconnect network flexible) on the MPC5604P features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and as much as 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors (sync field, delimiter, ID parity, bit framing, checksum, and time-out)

- Classic or extended checksum calculation

- Configurable Break duration as long as 36-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit or 9-bit words)

- Error detection and flagging

- Parity, Noise and Framing errors

- Interrupt-driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

## 1.5.24 Deserial serial peripheral interface (DSPI)

The deserial serial peripheral interface (DSPI) module provides a synchronous serial interface for communication between the MPC5604P MCU and external devices.

The DSPI modules provide these features:

- Full duplex, synchronous transfers

- Master or slave operation

- Programmable master bit rates

- Programmable clock polarity and phase

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- Up to 20 chip select lines available

- 8 on DSPI\_0

- 4 each on DSPI\_1, DSPI\_2 and DSPI\_3

- ADC state machine managing 3 request flows: regular command, hardware injected command, software injected command

- Selectable priority between software and hardware injected commands

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range)

- DMA compatible interface

- CTU control mode features

- Triggered mode only

- 4 independent result queues ( $2 \times 16$  entries,  $2 \times 4$  entries)

- Result alignment circuitry (left justified; right justified)

- 32-bit read mode allows to have channel ID on one of the 16-bit part

- DMA compatible interfaces

## 1.5.28 Cross triggering unit (CTU)

The cross triggering unit allows automatic generation of ADC conversion requests on user selected conditions without CPU load during the PWM period and with minimized CPU load for dynamic configuration.

It implements the following features:

- Double buffered trigger generation unit with as many as eight independent triggers generated from external triggers

- Trigger generation unit configurable in sequential mode or in triggered mode

- Each Trigger can be appropriately delayed to compensate the delay of external low pass filter

- Double buffered global trigger unit allowing eTimer synchronization and/or ADC command generation

- Double buffered ADC command list pointers to minimize ADC-trigger unit update

- Double buffered ADC conversion command list with as many as 24 ADC commands

- Each trigger has the capability to generate consecutive commands

- ADC conversion command allows to control ADC channel from each ADC, single or synchronous sampling, independent result queue selection

## 1.5.29 Nexus development interface (NDI)

The NDI (Nexus Development Interface) block provides real-time development support capabilities for the MPC5604P Power Architecture based MCU in compliance with the IEEE-ISTO 5001-2003 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility. The NDI block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal busses to provide development support as per the IEEE-ISTO 5001-2003 Class 2+ standard. The development support provided includes access to the MCU's internal memory map and access to the processor's internal registers during run time.

The Nexus Interface provides the following features:

- Configured via the IEEE 1149.1

- All Nexus port pins operate at V<sub>DDIO</sub> (no dedicated power supply)

- Nexus 2+ features supported

- Static debug

- Watchpoint messaging

- Ownership trace messaging

- Program trace messaging

- Real time read/write of any internally memory mapped resources through JTAG pins

- Overrun control, which selects whether to stall before Nexus overruns or keep executing and allow overwrite of information

|             | Pad                          |                                             |                                                           |                                                          |                                   | Pad s   | peed <sup>5</sup> | Pin No. |         |

|-------------|------------------------------|---------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|-----------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                                 | Peripheral <sup>3</sup>                                  | I/O<br>direction <sup>4</sup>     | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| A[8]        | PCR[8]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[8]<br>—<br>—<br>SIN<br>EIRQ[8]                       | SIUL<br>—<br>—<br>DSPI_1<br>SIUL                         | V<br>                             | Slow    | Medium            | 6       | 12      |

| A[9]        | PCR[9]                       | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[9]<br>CS1<br>—<br>B[3]<br>FAULT[0]                   | SIUL<br>DSPI_2<br>                                       | I/O<br>O<br>O<br>I                | Slow    | Medium            | 94      | 134     |

| A[10]       | PCR[10]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[10]<br>CS0<br>B[0]<br>X[2]<br>EIRQ[9]                | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL         | I/O<br>I/O<br>O<br>I/O<br>I       | Slow    | Medium            | 81      | 118     |

| A[11]       | PCR[11]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[11]<br>SCK<br>A[0]<br>A[2]<br>EIRQ[10]               | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL         | I/O<br>I/O<br>O<br>I              | Slow    | Medium            | 82      | 120     |

| A[12]       | PCR[12]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[12]<br>SOUT<br>A[2]<br>B[2]<br>EIRQ[11]              | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL         | I/O<br>O<br>O<br>I                | Slow    | Medium            | 83      | 122     |

| A[13]       | PCR[13]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[13]<br>—<br>B[2]<br>—<br>SIN<br>FAULT[0]<br>EIRQ[12] | SIUL<br><br>FlexPWM_0<br><br>DSPI_2<br>FlexPWM_0<br>SIUL | I/O<br>—<br>O<br>—<br>I<br>I<br>I | Slow    | Medium            | 95      | 136     |

| A[14]       | PCR[14]                      | ALT0<br>ALT1<br>ALT2<br>ALT3                | GPIO[14]<br>TXD<br>ETC[4]<br>—<br>EIRQ[13]                | SIUL<br>Safety Port_0<br>eTimer_1<br>—<br>SIUL           | /O<br>O<br> /O<br>                | Slow    | Medium            | 99      | 143     |

| A[15]       | PCR[15]                      | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[15]<br><br>ETC[5]<br><br>RXD<br>EIRQ[14]             | SIUL<br>—<br>eTimer_1<br>—<br>Safety Port_0<br>SIUL      | I/O<br>—<br>I/O<br>—<br>I         | Slow    | Medium            | 100     | 144     |

Table 5. Pin muxing (continued)

|             | Pad                             |                                             |                                                   |                                             |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|---------------------------------------------|---------------------------------------------------|---------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup>        | Functions                                         | Peripheral <sup>3</sup>                     | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| B[10]       | PCR[26]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[26]<br>—<br>—<br>—<br>AN[12]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    | _       | _                 | 36      | 53      |

| B[11]       | PCR[27]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[27]<br>—<br>—<br>—<br>AN[13]                 | SIUL<br>—<br>—<br>ADC_0 / ADC_1             | Input only                    | _       | _                 | 37      | 54      |

| B[12]       | PCR[28]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[28]<br><br><br>AN[14]                        | SIUL<br>—<br>—<br><br>ADC_0 / ADC_1         | Input only                    | _       | _                 | 38      | 55      |

| B[13]       | PCR[29]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[29]<br>—<br>—<br>—<br>AN[0]<br>RXD           | SIUL<br>—<br>—<br>ADC_1<br>LIN_1            | Input only                    | _       | _                 | 42      | 60      |

| B[14]       | PCR[30]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[30]<br>—<br>—<br>AN[1]<br>ETC[4]<br>EIRQ[19] | SIUL<br>—<br>—<br>ADC_1<br>eTimer_0<br>SIUL | Input only                    |         | _                 | 44      | 64      |

| B[15]       | PCR[31]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[31]<br>—<br>—<br>—<br>AN[2]<br>EIRQ[20]      | SIUL<br>—<br>—<br>ADC_1<br>SIUL             | Input only                    | _       | _                 | 43      | 62      |

|             | Port C (16-bit)                 |                                             |                                                   |                                             |                               |         |                   |         |         |

| C[0]        | PCR[32]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[32]<br>—<br>—<br>—<br>AN[3]                  | SIUL<br>—<br>—<br>—<br>ADC_1                | Input only                    | _       |                   | 45      | 66      |

| C[1]        | PCR[33]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[33]<br>—<br>—<br>—<br>AN[2]                  | SIUL<br>—<br>—<br>—<br>ADC_0                | Input only                    | _       |                   | 28      | 41      |

Table 5. Pin muxing (continued)

|             | Pad                             | Pad                                  |                                                      |                                          |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|------------------------------------------------------|------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                                            | Peripheral <sup>3</sup>                  | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| E[15]       | PCR[79]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[79]<br>—<br>—<br>—<br>SIN<br>EIRQ[27]           | SIUL<br>—<br>—<br>DSPI_3<br>SIUL         | VO<br>                        | Slow    | Medium            |         | 121     |

|             | L                               | 1                                    |                                                      | Port F (16-bit)                          |                               |         | 1                 |         | •       |

| F[0]        | PCR[80]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[80]<br>DBG0<br>CS3<br>—                         | SIUL<br>FlexRay_0<br>DSPI_3<br>—<br>SIUL | I/O<br>O<br>—                 | Slow    | Medium            | _       | 133     |

| F[1]        | PCR[81]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | EIRQ[28]<br>GPIO[81]<br>DBG1<br>CS2<br>—<br>EIRQ[29] | SIUL<br>FlexRay_0<br>DSPI_3<br><br>SIUL  | I/O<br>O<br>O<br>I            | Slow    | Medium            |         | 135     |

| F[2]        | PCR[82]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[82]<br>DBG2<br>CS1<br>—                         | SIUL<br>FlexRay_0<br>DSPI_3<br>—         | I/O<br>O<br>—                 | Slow    | Medium            | -       | 137     |

| F[3]        | PCR[83]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[83]<br>DBG3<br>CS0<br>—                         | SIUL<br>FlexRay_0<br>DSPI_3<br>—         | I/O<br>O<br>I/O<br>—          | Slow    | Medium            | -       | 139     |

| F[4]        | PCR[84]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[84]<br>MDO[3]<br>—                              | SIUL<br>NEXUS_0<br>—                     | 1/O<br>O<br>—                 | Slow    | Fast              | _       | 4       |

| F[5]        | PCR[85]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[85]<br>MDO[2]<br>—                              | SIUL<br>NEXUS_0<br>—                     | I/O<br>O<br>—                 | Slow    | Fast              | _       | 5       |

| F[6]        | PCR[86]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[86]<br>MDO[1]<br>—                              | SIUL<br>NEXUS_0<br>—                     | I/O<br>O<br>—                 | Slow    | Fast              | _       | 8       |

| F[7]        | PCR[87]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[87]<br>MCKO<br>—<br>—                           | SIUL<br>NEXUS_0<br>—                     | I/O<br>O<br>—                 | Slow    | Fast              | —       | 19      |

| F[8]        | PCR[88]                         | ALT0<br>ALT1<br>ALT2<br>ALT3         | GPIO[88]<br>MSEO1<br>—<br>—                          | SIUL<br>NEXUS_0<br>—                     | I/O<br>O<br>—                 | Slow    | Fast              | _       | 20      |

Table 5. Pin muxing (continued)

- <sup>2</sup> Alternate functions are chosen by setting the values of the PCR[PA] bitfields inside the SIU module. PCR[PA] = 00 → ALT0; PCR[PA] = 01 → ALT1; PCR[PA] = 10 → ALT2; PCR[PA] = 11 → ALT3. This is intended to select the output functions; to use one of the input-only functions, the PCR[IBE] bit must be written to '1', regardless of the values selected in the PCR[PA] bitfields. For this reason, the value corresponding to an input only function is reported as "—".

- <sup>3</sup> Module included on the MCU.

- <sup>4</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMI[PADSEL*x*] bitfields inside the SIUL module.

- <sup>5</sup> Programmable via the SRC (Slew Rate Control) bits in the respective Pad Configuration Register.

- <sup>6</sup> Weak pull down during reset.

# 3 Electrical characteristics

# 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

## CAUTION

All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 6 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 6. Parameter classifications

## NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

3.5 Thermal characteristics

## 3.5.1 Package thermal characteristics

#### Table 10. Thermal characteristics for 144-pin LQFP

| Symbol             | Parameter                                              | Conditions            | Typical value | Unit |

|--------------------|--------------------------------------------------------|-----------------------|---------------|------|

| $R_{	hetaJA}$      | Thermal resistance junction-to-ambient,                | Single layer board—1s | 54.2          | °C/W |

|                    | natural convection <sup>1</sup>                        | Four layer board—2s2p | 44.4          | °C/W |

| $R_{\theta JB}$    | Thermal resistance junction-to-board <sup>2</sup>      | Four layer board—2s2p | 29.9          | °C/W |

| $R_{\theta JCtop}$ | Thermal resistance junction-to-case (top) <sup>3</sup> | Single layer board—1s | 9.3           | °C/W |

| $\Psi_{JB}$        | Junction-to-board, natural convection <sup>4</sup>     | Operating conditions  | 30.2          | °C/W |

| ΨJC                | Junction-to-case, natural convection <sup>5</sup>      | Operating conditions  | 0.8           | °C/W |

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

- <sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

| Symbol              | Parameter                                              | Conditions            | Typical value | Unit |

|---------------------|--------------------------------------------------------|-----------------------|---------------|------|

| $R_{	hetaJA}$       | Thermal resistance junction-to-ambient,                | Single layer board—1s | 47.3          | °C/W |

|                     | natural convection <sup>1</sup>                        | Four layer board—2s2p | 35.3          | °C/W |

| $R_{\theta JB}$     | Thermal resistance junction-to-board <sup>2</sup>      | Four layer board—2s2p | 19.1          | °C/W |

| R <sub>0JCtop</sub> | Thermal resistance junction-to-case (top) <sup>3</sup> | Single layer board—1s | 9.7           | °C/W |

| $\Psi_{JB}$         | Junction-to-board, natural convection <sup>4</sup>     | Operating conditions  | 19.1          | °C/W |

| ΨJC                 | Junction-to-case, natural convection <sup>5</sup>      | Operating conditions  | 0.8           | °C/W |

Table 11. Thermal characteristics for 100-pin LQFP

<sup>1</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

| Part  | Manufacturer | Approved derivatives <sup>1</sup> |

|-------|--------------|-----------------------------------|

| BCP68 | ON Semi      | BCP68                             |

|       | NXP          | BCP68-25                          |

|       | Infineon     | BCP68-25                          |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25        |

| BC868 | NXP          | BC868                             |

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;        |

|       | NXP          | BC817-16;BC817-25                 |

| BCP56 | ST           | BCP56-16                          |

|       | Infineon     | BCP56-10;BCP56-16                 |

|       | ON Semi      | BCP56-10                          |

|       | NXP          | BCP56-10;BCP56-16                 |

### Table 14. Approved NPN ballast components (configuration with resistor on base)

<sup>1</sup> For automotive applications please check with the appropriate transistor vendor for automotive grade certification

| Symbol                    |                                                                                                                                         | с | Parameter                                                     | Conditions                                                                                          |      | Value |    | Unit |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-------|----|------|

| Cymson                    |                                                                                                                                         | Ū |                                                               | Contractions                                                                                        | Тур  | Max   |    |      |

| V <sub>DD_LV_REGCOR</sub> | V <sub>DD_LV_REGCOR</sub> CC         P         Output voltage under maximum load run supply current configuration         Post-trimming |   | 1.15                                                          | _                                                                                                   | 1.32 | V     |    |      |

| R <sub>B</sub>            | SR                                                                                                                                      |   | External resistance on bipolar junction transistor (BJT) base | —                                                                                                   | 18   |       | 22 | kΩ   |

| C <sub>DEC1</sub>         | SR                                                                                                                                      | _ | External decoupling/stability ceramic capacitor               | BJT from Table 14. 3<br>capacitances (i.e. X7R or X8R<br>capacitors) with nominal value<br>of 10 μF | 19.5 | 30    |    | μF   |

|                           |                                                                                                                                         |   |                                                               | BJT BC817, one capacitance of 22 $\mu$ F                                                            | 14.3 | 22    |    | μF   |

- <sup>3</sup> Code fetched from RAM, PLL\_0: 64 MHz system clock (x4 multiplier with 16 MHz XTAL), PLL\_1 is ON at PHI\_div2 = 120 MHz and PHI\_div3 = 80 MHz, auxiliary clock sources set that all peripherals receive maximum frequency, all peripherals enabled.

- <sup>4</sup> Halt mode configurations: code fetched from RAM, code and data flash memories in low power mode, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

- <sup>5</sup> STOP "P" mode Device Under Test (DUT) configuration: code fetched from RAM, code and data flash memories OFF, OSC/PLL\_0/PLL\_1 are OFF, core clock frozen, all peripherals are disabled.

# 3.10.3 DC electrical characteristics (3.3 V)

Table 21 gives the DC electrical characteristics at 3.3 V (3.0 V < V<sub>DD\_HV\_IOx</sub> < 3.6 V, NVUSRO[PAD3V5V] = 1); see Figure 13.

| Symbol C            |   | Parameter                                                     | Conditions                        | Value                       |                             |    |

|---------------------|---|---------------------------------------------------------------|-----------------------------------|-----------------------------|-----------------------------|----|

| Symbol              | C | Min                                                           |                                   | Max                         | Unit                        |    |

| V <sub>IL</sub>     | D | Low level input voltage                                       | —                                 | -0.1 <sup>2</sup>           | —                           | V  |

|                     | Ρ |                                                               |                                   | _                           | 0.35 V <sub>DD_HV_IOx</sub> | V  |

| V <sub>IH</sub>     | Ρ | High level input voltage                                      | —                                 | 0.65 V <sub>DD_HV_IOx</sub> | —                           | V  |

|                     | D |                                                               |                                   | _                           | $V_{DD_HV_IOx} + 0.1^2$     | V  |

| V <sub>HYS</sub>    | Т | Schmitt trigger hysteresis                                    | _                                 | 0.1 V <sub>DD_HV_IOx</sub>  | _                           | V  |

| V <sub>OL_S</sub>   | Ρ | Slow, low level output voltage                                | I <sub>OL</sub> = 1.5 mA          | —                           | 0.5                         | V  |

| V <sub>OH_S</sub>   | Ρ | Slow, high level output voltage                               | I <sub>OH</sub> = –1.5 mA         | $V_{DD_HV_IOx} - 0.8$       | _                           | V  |

| V <sub>OL_M</sub>   | Ρ | Medium, low level output voltage                              | I <sub>OL</sub> = 2 mA            | —                           | 0.5                         | V  |

| V <sub>OH_M</sub>   | Ρ | Medium, high level output voltage                             | I <sub>OH</sub> = –2 mA           | $V_{DD_HV_IOx} - 0.8$       | _                           | V  |

| V <sub>OL_F</sub>   | Ρ | Fast, low level output voltage                                | I <sub>OL</sub> = 1.5 mA          | —                           | 0.5                         | V  |

| V <sub>OH_F</sub>   | Ρ | Fast, high level output voltage                               | I <sub>OH</sub> = –1.5 mA         | $V_{DD_HV_IOx} - 0.8$       | —                           | V  |

| V <sub>OL_SYM</sub> | Ρ | Symmetric, low level output voltage                           | I <sub>OL</sub> = 1.5 mA          | —                           | 0.5                         | V  |

| V <sub>OH_SYM</sub> | Ρ | Symmetric, high level output voltage                          | I <sub>OH</sub> = –1.5 mA         | $V_{DD_HV_IOx} - 0.8$       | _                           | V  |

| I <sub>PU</sub>     | Ρ | Equivalent pull-up current                                    | $V_{IN} = V_{IL}$                 | –130                        | —                           | μA |

|                     |   |                                                               | V <sub>IN</sub> = V <sub>IH</sub> | —                           | -10                         |    |

| I <sub>PD</sub>     | Ρ | Equivalent pull-down current                                  | $V_{IN} = V_{IL}$                 | 10                          | _                           | μA |

|                     |   |                                                               | V <sub>IN</sub> = V <sub>IH</sub> | _                           | 130                         |    |

| IIL                 | Ρ | P Input leakage current (all $T_A = -40$ bidirectional ports) |                                   | _                           | 1                           | μA |

| ۱ <sub>۱۲</sub>     | Ρ | Input leakage current (all ADC input-only ports)              | T <sub>A</sub> = -40 to 125 °C    |                             | 0.5                         | μA |

| C <sub>IN</sub>     | D | Input capacitance                                             | _                                 | —                           | 10                          | pF |

|                     | П | RESET, equivalent pull-up current                             | V <sub>IN</sub> = V <sub>IL</sub> | –130                        | —                           | μA |

| I <sub>PU</sub>     | U |                                                               | V <sub>IN</sub> = V <sub>IH</sub> | —                           | -10                         | μΛ |

Table 21. DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)<sup>1</sup>

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

| Ded     | 144       | LQFP        | 100 LQFP  |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[86] | 9%        | 6%          | _         | _           |  |

| MODO[0] | 12%       | 8%          | _         |             |  |

| PAD[7]  | 4%        | 4%          | 11%       | 10%         |  |

| PAD[36] | 5%        | 4%          | 11%       | 9%          |  |

| PAD[8]  | 5%        | 4%          | 10%       | 9%          |  |

| PAD[37] | 5%        | 4%          | 10%       | 9%          |  |

| PAD[5]  | 5%        | 4%          | 9%        | 8%          |  |

| PAD[39] | 5%        | 4%          | 9%        | 8%          |  |

| PAD[35] | 5%        | 4%          | 8%        | 7%          |  |

| PAD[87] | 12%       | 9%          | —         | —           |  |

| PAD[88] | 9%        | 6%          | _         | _           |  |

| PAD[89] | 10%       | 7%          | _         |             |  |

| PAD[90] | 15%       | 11%         | _         | _           |  |

| PAD[91] | 6%        | 5%          | _         | _           |  |

| PAD[57] | 8%        | 7%          | 8%        | 7%          |  |

| PAD[56] | 13%       | 11%         | 13%       | 11%         |  |

| PAD[53] | 14%       | 12%         | 14%       | 12%         |  |

| PAD[54] | 15%       | 13%         | 15%       | 13%         |  |

| PAD[55] | 25%       | 22%         | 25%       | 22%         |  |

| PAD[96] | 27%       | 24%         | _         | _           |  |

| PAD[65] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[67] | 1%        | 1%          | _         | _           |  |

| PAD[33] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[68] | 1%        | 1%          | _         | _           |  |

| PAD[23] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[69] | 1%        | 1%          | _         |             |  |

| PAD[34] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[70] | 1%        | 1%          | _         | _           |  |

| PAD[24] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[71] | 1%        | 1%          | —         | _           |  |

| PAD[66] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[25] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[26] | 1%        | 1%          | 1%        | 1%          |  |

### Table 24. I/O weight (continued)

| Ded     | 144       | LQFP        | 100 LQFP  |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[13] | 10%       | 9%          | 12%       | 11%         |  |

| PAD[82] | 10%       | 9%          | —         |             |  |

| PAD[22] | 10%       | 9%          | 13%       | 12%         |  |

| PAD[83] | 10%       | 9%          | —         | _           |  |

| PAD[50] | 10%       | 9%          | 14%       | 12%         |  |

| PAD[97] | 10%       | 9%          | —         | _           |  |

| PAD[38] | 10%       | 9%          | 14%       | 13%         |  |

| PAD[14] | 9%        | 8%          | 14%       | 13%         |  |

| PAD[15] | 9%        | 8%          | 15%       | 13%         |  |

## Table 24. I/O weight (continued)

## Table 25. I/O consumption

| Symbol                             | Symbol                                  |   | Parameter                       | Condi                          | Conditions <sup>1</sup>                       |     |                                               |                                | Unit        |    |       |     |

|------------------------------------|-----------------------------------------|---|---------------------------------|--------------------------------|-----------------------------------------------|-----|-----------------------------------------------|--------------------------------|-------------|----|-------|-----|

| Gymbol                             |                                         |   | i arameter                      | Condi                          | Min                                           | Тур | Max                                           |                                |             |    |       |     |

| I <sub>SWTSLW</sub> ,2             | СС                                      | D | for SLOW                        | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _   | _                                             | 20                             | mA          |    |       |     |

|                                    |                                         |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   | _                                             | 16                             |             |    |       |     |

| I <sub>SWTMED</sub> <sup>(2)</sup> | I <sub>SWTMED</sub> <sup>(2)</sup> CC D |   | CC D                            |                                | for MEDIUM                                    |     | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |                                | _           | 29 | mA    |     |

|                                    |                                         |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |                                               | 17                             |             |    |       |     |

| I <sub>SWTFST</sub> <sup>(2)</sup> | СС                                      | D | Dynamic I/O current<br>for FAST | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |     | _                                             | 110                            | mA          |    |       |     |

|                                    |                                         |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     | _                                             | 50                             |             |    |       |     |

| I <sub>RMSSLW</sub>                | СС                                      | D |                                 | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 5.0 V \pm 10\%$                     | _   | _                                             | 2.3                            | mA          |    |       |     |

|                                    |                                         |   |                                 |                                |                                               |     | I/O current for SLOW configuration            | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 0 | _  | — 3.2 |     |

|                                    |                                         |   |                                 |                                |                                               |     |                                               | C <sub>L</sub> = 100 pF, 2 MHz |             |    | _     | 6.6 |

|                                    |                                         |   |                                 | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   |     | _                                             | 1.6                            |             |    |       |     |

|                                    |                                         |   |                                 | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 1                                   | —   | —                                             | 2.3                            |             |    |       |     |

|                                    |                                         |   |                                 | C <sub>L</sub> = 100 pF, 2 MHz | ]                                             | _   | _                                             | 4.7                            |             |    |       |     |

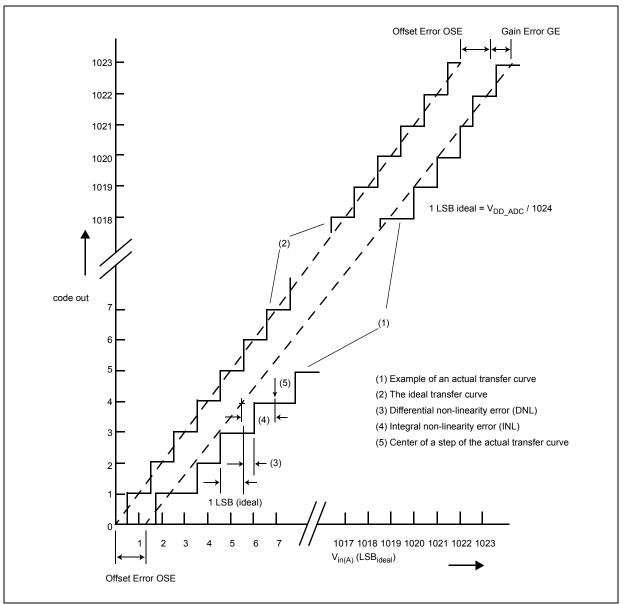

Figure 14. ADC characteristics and error definitions

# 3.14.1 Input impedance and ADC accuracy

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; further, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the source impedance value of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

Eqn. 11

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

**Eqn. 12**

$$C_F > 2048 \bullet C_S$$

## **3.14.2 ADC** conversion characteristics

| Symbol                        |    | с | Parameter                                                                                                             | Conditions <sup>1</sup>                                |                                      |     | Unit                                 |      |

|-------------------------------|----|---|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------|-----|--------------------------------------|------|

| Symbo                         |    | C |                                                                                                                       |                                                        | Min                                  | Тур | Мах                                  | Unit |

| VINANO                        | SR |   | ADC0 and shared ADC0/1<br>analog input voltage <sup>2, 3</sup>                                                        | _                                                      | V <sub>SS_HV_ADV</sub><br>0<br>- 0.3 |     | V <sub>DD_HV_ADV</sub><br>0<br>+ 0.3 | V    |

| V <sub>INAN1</sub>            | SR |   | ADC1 analog input voltage <sup>2, 4</sup>                                                                             | _                                                      | V <sub>SS_HV_ADV</sub><br>1<br>- 0.3 |     | V <sub>DD_HV_ADV</sub><br>1<br>+ 0.3 | v    |

| f <sub>CK</sub>               | SR |   | ADC clock frequency (depends<br>on ADC configuration)<br>(The duty cycle depends on<br>AD_clk <sup>5</sup> frequency) | _                                                      | 36                                   | _   | 60                                   | MHz  |

| f <sub>s</sub>                | SR |   | Sampling frequency                                                                                                    | —                                                      | —                                    | _   | 1.53                                 | MHz  |

| t <sub>ADC_S</sub>            | -  | D | Sample time <sup>7</sup>                                                                                              | f <sub>ADC</sub> = 20 MHz,<br>INPSAMP = 3              | 125                                  | _   | _                                    | ns   |

|                               |    |   |                                                                                                                       | f <sub>ADC</sub> = 9 MHz,<br>INPSAMP = 255             | _                                    |     | 28.2                                 | μs   |

| t <sub>ADC_C</sub>            |    | Ρ | Conversion time <sup>8</sup>                                                                                          | f <sub>ADC</sub> = 20 MHz <sup>9</sup> ,<br>INPCMP = 1 | 0.650                                |     | _                                    | μs   |

| t <sub>ADC_PU</sub>           | SR |   | ADC power-up delay (time<br>needed for ADC to settle<br>exiting from software power<br>down; PWDN bit = 0)            | _                                                      | _                                    | —   | 1.5                                  | μs   |

| C <sub>S</sub> <sup>10</sup>  | —  | D | ADC input sampling<br>capacitance                                                                                     | _                                                      | —                                    |     | 2.5                                  | pF   |

| C <sub>P1</sub> <sup>10</sup> | —  | D | ADC input pin capacitance 1                                                                                           | _                                                      | —                                    | _   | 3                                    | pF   |

| C <sub>P2</sub> <sup>10</sup> | _  | D | ADC input pin capacitance 2                                                                                           | _                                                      | _                                    | _   | 1                                    | pF   |

### Table 31. ADC conversion characteristics

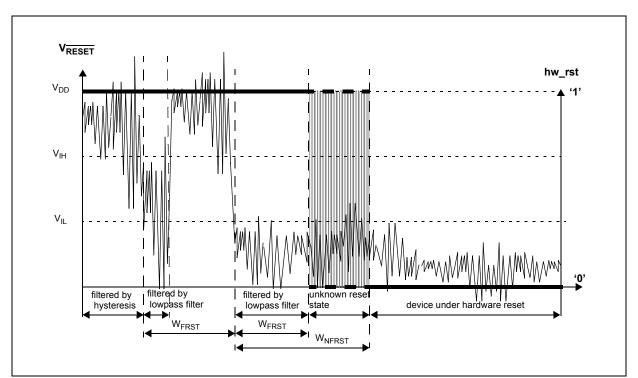

Figure 20. Noise filtering on reset signal

| Symb             | Symbol C |   | Parameter                                  | Conditions <sup>1</sup>                                                                          |                     | Value |                      | Unit |

|------------------|----------|---|--------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|-------|----------------------|------|

| Cynns            |          | Ŭ |                                            |                                                                                                  | Min                 | Тур   | Мах                  | onne |

| V <sub>IH</sub>  | SR       | Ρ | Input High Level CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.65V <sub>DD</sub> | _     | V <sub>DD</sub> +0.4 | V    |

| V <sub>IL</sub>  | SR       | Ρ | Input low Level CMOS<br>(Schmitt Trigger)  | _                                                                                                | -0.4                | _     | 0.35V <sub>DD</sub>  | V    |

| V <sub>HYS</sub> | СС       | С | Input hysteresis CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.1V <sub>DD</sub>  | _     | _                    | V    |

| V <sub>OL</sub>  | СС       | Ρ | Output low level                           | Push Pull, I <sub>OL</sub> = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                   | _     | 0.1V <sub>DD</sub>   | V    |

|                  |          |   |                                            | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>            | _                   | _     | 0.1V <sub>DD</sub>   |      |

|                  |          |   |                                            | Push Pull, I <sub>OL</sub> = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | —                   | _     | 0.5                  |      |

Table 36. RESET electrical characteristics

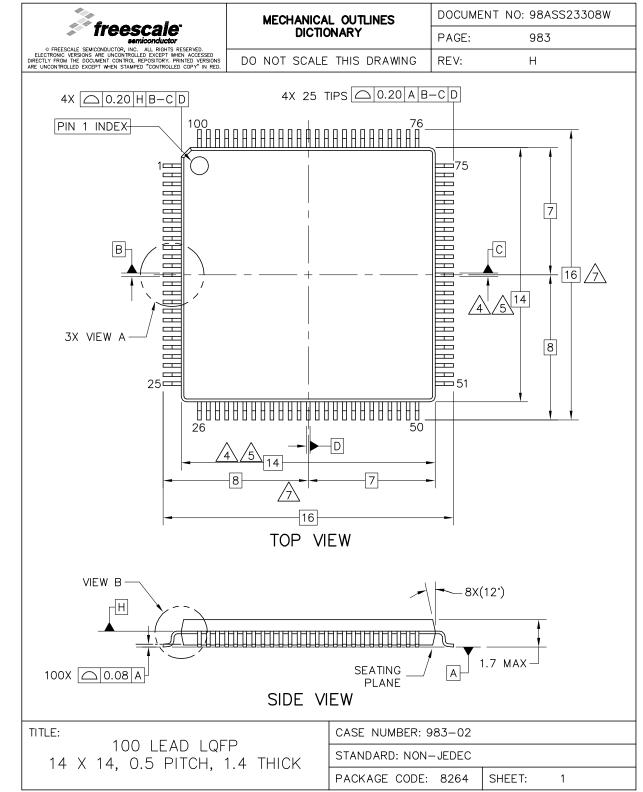

## 4.1.2 100 LQFP mechanical outline drawing

Figure 39. 100 LQFP package mechanical drawing (part 1)

MPC5604P Microcontroller Data Sheet, Rev. 8

# Appendix A Abbreviations

Table A-1 lists abbreviations used in this document.

#### Table A-1. Abbreviations

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| CMOS         | Complementary metal-oxide-semiconductor |

| СРНА         | Clock phase                             |

| CPOL         | Clock polarity                          |

| CS           | Peripheral chip select                  |

| DUT          | Device under test                       |

| ECC          | Error code correction                   |

| EVTO         | Event out                               |

| GPIO         | General purpose input/output            |

| MC           | Modulus counter                         |

| МСКО         | Message clock out                       |

| MCU          | Microcontroller unit                    |

| MDO          | Message data out                        |

| MSEO         | Message start/end out                   |

| MTFE         | Modified timing format enable           |

| NPN          | Negative-positive-negative              |

| NVUSRO       | Non-volatile user options register      |

| PTF          | Post trimming frequency                 |

| PWM          | Pulse width modulation                  |

| RBW          | Resolution bandwidth                    |

| SCK          | Serial communications clock             |

| SOUT         | Serial data out                         |

| TCK          | Test clock input                        |

| TDI          | Test data input                         |

| TDO          | Test data output                        |

| TMS          | Test mode select                        |

| Table 42. F | Revision | history | (continued) |

|-------------|----------|---------|-------------|

|-------------|----------|---------|-------------|

| Revision | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 7   |      | <ul> <li>Formatting and editorial changes throughout</li> <li>Removed all content referencing Junction Temperature Sensor</li> <li>Section 1, "Introduction: changed title (was: Overview); reorganized contents</li> <li>MPC5604P device comparison:</li> <li>ADC feature: changed "16 channels" to "15-channel"; added footnote to to indicate that four channels are shared between the two ADCs</li> <li>removed MPC5602P column</li> <li>indicated that data flash memory is an optional feature</li> <li>changed "dual channel" to "selectable single or dual channel support" in FlexRay footnote</li> <li>updated "eTimer" feature</li> <li>updated footnote relative to "Digital power supply" feature</li> <li>Updated MPC5604P block diagram</li> <li>Added APC5604P series block summary</li> <li>Added Section 1.5, "Feature details</li> <li>Section 2.1, "Package pinouts: removed alternate functions from pinout diagrams</li> <li>Supply pins: updated dable</li> <li>Pin muxing: added rows "B[4]" and "B[5]</li> <li>Section 3.3, "Absolute maximum ratings: added voltage specifications to titles of Figure 4 and Figure 5; in Table 7, changed row "V<sub>SS-HV</sub> / Digital Ground" to "V<sub>SS</sub> / Device Ground"; updated symbols</li> <li>Section 3.4, "Recommended operating conditions: added voltage specifications to titles of Figure 7</li> </ul> |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |      | Updated Section 3.6, "Electromagnetic interference (EMI) characteristics<br>Section 3.8.1, "Voltage regulator electrical characteristics: amended titles of Table 15 and<br>Table 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics (configuration with resistor on base):<br>updated symbol and values for V <sub>DD_LV_REGCOR</sub><br>Low voltage monitor electrical characteristics: Updated V <sub>MLVDDOK_H</sub> max value—was<br>1.15 V; is 1.145 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | Section 3.10, "DC electrical characteristics: reorganized contents<br>Updated Section 3.10.1, "NVUSRO register (includes adding<br>"NVUSRO[OSCILLATOR_MARGIN] field description" table<br>Supply current (5.0 V, NVUSRO[PAD3V5V] = 0): updated symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |