# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 68                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 40K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pqf1mll6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 | Feature                       | MPC5603P                                            | MPC5604P               |  |  |  |

|-----------------|-------------------------------|-----------------------------------------------------|------------------------|--|--|--|

| eTimer          |                               | 2 (16-bit, 6 channels)                              |                        |  |  |  |

| FlexPWM (puls   | se-width modulation) channels | 8 (capturing on >                                   | K-channels)            |  |  |  |

| ADC (analog-to  | o-digital converter)          | 2 (10-bit, 15-c                                     | channel <sup>4</sup> ) |  |  |  |

| LINFlex         |                               | 2                                                   |                        |  |  |  |

| DSPI (deserial  | serial peripheral interface)  | 4                                                   |                        |  |  |  |

| CRC (cyclic red | dundancy check) unit          | Yes                                                 |                        |  |  |  |

| JTAG controlle  | r                             | Yes                                                 |                        |  |  |  |

| Nexus port con  | troller (NPC)                 | Yes (Level 2+)                                      |                        |  |  |  |

| Supply          | Digital power supply          | 3.3 V or 5 V single supply with external transistor |                        |  |  |  |

|                 | Analog power supply           | 3.3 V or 5 V                                        |                        |  |  |  |

|                 | Internal RC oscillator        | 16 MHz                                              |                        |  |  |  |

|                 | External crystal oscillator   | 4–40 MHz                                            |                        |  |  |  |

| Packages        |                               | 100 LQ<br>144 LQ                                    |                        |  |  |  |

| Temperature     | Standard ambient temperature  | –40 to 12                                           | 5 °C                   |  |  |  |

### Table 1. MPC5604P device comparison (continued)

<sup>1</sup> 32 message buffers, selectable single or dual channel support

<sup>2</sup> Each FlexCAN module has 32 message buffers.

<sup>3</sup> One FlexCAN module can act as a Safety Port with a bit rate as high as 7.5 Mbit/s.

<sup>4</sup> Four channels shared between the two ADCs

## 1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5604P MCU.

array controller. It supports a 32-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit wide prefetch buffers. Prefetch buffer hits allow no-wait responses. Normal flash memory array accesses are registered and are forwarded to the system bus on the following cycle, incurring two wait-states.

The flash memory module provides the following features:

- As much as 576 KB flash memory

- 8 blocks (32 KB + 2×16 KB + 32 KB + 32 KB + 3×128 KB) code flash

- 4 blocks (16 KB + 16 KB + 16 KB + 16 KB) data flash

- Full Read While Write (RWW) capability between code and data flash

- Four 128-bit wide prefetch buffers to provide single cycle in-line accesses (prefetch buffers can be configured to prefetch code or data or both)

- Typical flash memory access time: 0 wait states for buffer hits, 2 wait states for page buffer miss at 64 MHz

- Hardware managed flash memory writes handled by 32-bit RISC Krypton engine

- · Hardware and software configurable read and write access protections on a per-master basis

- Configurable access timing allowing use in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (up to 31 additional cycles) allowing use for emulation of other memory types.

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page sizes

- Code flash memory: 128 bits (4 words)

- Data flash memory: 32 bits (1 word)

- ECC with single-bit correction, double-bit detection for data integrity

- Code flash memory: 64-bit ECC

- Data flash memory: 64-bit ECC

- Embedded hardware program and erase algorithm

- Erase suspend, program suspend and erase-suspended program

- Censorship protection scheme to prevent flash memory content visibility

- Hardware support for EEPROM emulation

## 1.5.5 Static random access memory (SRAM)

The MPC5604P SRAM module provides up to 40 KB of general-purpose memory.

ECC handling is done on a 32-bit boundary and is completely software compatible with MPC55xx family devices with an e200z6 core and 64-bit wide ECC.

The SRAM module provides the following features:

- · Supports read/write accesses mapped to the SRAM from any master

- Up to 40 KB general purpose SRAM

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

- Typical SRAM access time: 0 wait-state for reads and 32-bit writes; 1 wait state for 8- and 16-bit writes if back to back with a read to same memory block

## 1.5.6 Interrupt controller (INTC)

The interrupt controller (INTC) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems. The INTC handles 147 selectable-priority interrupt sources.

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the PLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

## 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

## 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- $\pm 5\%$  variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

### 1.5.12 Periodic interrupt timer (PIT)

The PIT module implements these features:

- 4 general purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel can be used as trigger for a DMA request

## 1.5.13 System timer module (STM)

The STM module implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

## 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- Watchpoint triggering, watchpoint triggers program tracing

- Auxiliary Output Port

- 4 MDO (Message Data Out) pins

- MCKO (Message Clock Out) pin

- 2 MSEO (Message Start/End Out) pins

- EVTO (Event Out) pin

- Auxiliary Input Port

- EVTI (Event In) pin

## 1.5.30 Cyclic redundancy check (CRC)

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC module features:

- Support for CRC-16-CCITT (*x*25 protocol):

- $x^{16} + x^{12} + x^5 + 1$

- Support for CRC-32 (Ethernet protocol):  $- x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

### 1.5.31 IEEE 1149.1 JTAG controller

The JTAG controller (JTAGC) block provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode. All data input to and output from the JTAGC block is communicated in serial format. The JTAGC block is compliant with the IEEE standard.

The JTAG controller provides the following features:

- IEEE Test Access Port (TAP) interface with 4 pins (TDI, TMS, TCK, TDO)

- Selectable modes of operation include JTAGC/debug or normal system operation.

- A 5-bit instruction register that supports the following IEEE 1149.1-2001 defined instructions:

BYPASS, IDCODE, EXTEST, SAMPLE, SAMPLE/PRELOAD

- A 5-bit instruction register that supports the additional following public instructions:

- ACCESS\_AUX\_TAP\_NPC, ACCESS\_AUX\_TAP\_ONCE

- 3 test data registers: a bypass register, a boundary scan register, and a device identification register.

- A TAP controller state machine that controls the operation of the data registers, instruction register and associated circuitry.

## 1.5.32 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN (negative-positive-negative) transistor

- Regulates external 3.3 V /5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

|             | Pad                             |                                      |                                                          |                                                 |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|----------------------------------------------------------|-------------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                                                | Peripheral <sup>3</sup>                         | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| C[2]        | PCR[34]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[34]<br>—<br>—<br>AN[3]                              | SIUL<br>—<br>—<br><br>ADC_0                     | Input only                    | _       |                   | 30      | 45      |

| C[3]        | PCR[35]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[35]<br>CS1<br>ETC[4]<br>TXD<br>EIRQ[21]             | SIUL<br>DSPI_0<br>eTimer_1<br>LIN_1<br>SIUL     | I/O<br>O<br>I/O<br>O<br>I     | Slow    | Medium            | 10      | 16      |

| C[4]        | PCR[36]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[36]<br>CS0<br>X[1]<br>DEBUG[4]<br>EIRQ[22]          | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | /O<br> /O<br> /O<br> -<br>    | Slow    | Medium            | 5       | 11      |

| C[5]        | PCR[37]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[37]<br>SCK<br>—<br>DEBUG[5]<br>FAULT[3]<br>EIRQ[23] | SIUL<br>DSPI_0<br><br>SSCM<br>FlexPWM_0<br>SIUL | /O<br> /O<br> -<br> <br> <br> | Slow    | Medium            | 7       | 13      |

| C[6]        | PCR[38]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[38]<br>SOUT<br>B[1]<br>DEBUG[6]<br>EIRQ[24]         | SIUL<br>DSPI_0<br>FlexPWM_0<br>SSCM<br>SIUL     | I/O<br>I/O<br>O<br>I          | Slow    | Medium            | 98      | 142     |

| C[7]        | PCR[39]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[39]<br>—<br>A[1]<br>DEBUG[7]<br>SIN                 | SIUL<br><br>FlexPWM_0<br>SSCM<br>DSPI_0         | /O<br> -<br> -<br>            | Slow    | Medium            | 9       | 15      |

| C[8]        | PCR[40]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[40]<br>CS1<br>—<br>CS6<br>FAULT[2]                  | SIUL<br>DSPI_1<br><br>DSPI_0<br>FlexPWM_0       | I/O<br>O<br>O<br>I            | Slow    | Medium            | 91      | 130     |

| C[9]        | PCR[41]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[41]<br>CS3<br>—<br>X[3]<br>FAULT[2]                 | SIUL<br>DSPI_2<br>                              | I/O<br>O<br>I/O<br>I          | Slow    | Medium            | 84      | 123     |

| C[10]       | PCR[42]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[42]<br>CS2<br>—<br>A[3]<br>FAULT[1]                 | SIUL<br>DSPI_2<br><br>FlexPWM_0<br>FlexPWM_0    | I/O<br>O<br><br>O<br>I        | Slow    | Medium            | 78      | 111     |

Table 5. Pin muxing (continued)

## 3 Electrical characteristics

## 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

### CAUTION

All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 6 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### Table 6. Parameter classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

- <sup>4</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

- $^5~$  The low voltage supplies (V\_{DD\\_LV\\_xxx}) are not all independent.

- $V_{DD\_LV\_COR1}$  and  $V_{DD\_LV\_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly,  $V_{SS\_LV\_COR1}$  and  $V_{SS\_LV\_COR2}$  are internally shorted.

- $V_{DD_LV_REGCOR}$  and  $V_{DD_LV_REGCORx}$  are physically shorted internally, as are  $V_{SS_LV_REGCOR}$  and  $V_{SS_LV_CORx}$ .

| Cump hal                             |    | Devenueter                                           | Conditions                            | Val                          | ue                           | 11   |

|--------------------------------------|----|------------------------------------------------------|---------------------------------------|------------------------------|------------------------------|------|

| Symbol                               |    | Parameter                                            | Conditions                            | Min                          | Max <sup>1</sup>             | Unit |

| V <sub>SS</sub>                      | SR | Device ground                                        |                                       | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>2</sup>  | SR | 3.3 V input/output supply voltage                    | _                                     | 3.0                          | 3.6                          | V    |

| V <sub>SS_HV_IOx</sub>               | SR | Input/output ground voltage                          | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_FL</sub>                | SR | 3.3 V code and data flash                            | _                                     | 3.0                          | 3.6                          | V    |

|                                      |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_FL</sub>                | SR | Code and data flash ground                           | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_OSC</sub>               | SR | 3.3 V crystal oscillator amplifier                   | _                                     | 3.0                          | 3.6                          | V    |

|                                      |    | supply voltage                                       | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>SS_HV_OSC</sub>               | SR | 3.3 V crystal oscillator amplifier reference voltage | _                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_REG</sub>               | SR | 3.3 V voltage regulator supply                       | —                                     | 3.0                          | 3.6                          | V    |

|                                      |    | voltage                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | $V_{DD_HV_IOx} - 0.1$        | V <sub>DD_HV_IOx</sub> + 0.1 |      |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup> | SR | 3.3 V ADC_0 supply and high                          | _                                     | 3.0                          | 5.5                          | V    |

|                                      |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | 5.5                          |      |

| V <sub>SS_HV_ADC0</sub>              | SR | ADC_0 ground and low<br>reference voltage            | —                                     | 0                            | 0                            | V    |

| V <sub>DD_HV_ADC1</sub> <sup>3</sup> | SR | 3.3 V ADC_1 supply and high                          | —                                     | 3.0                          | 5.5                          | V    |

|                                      |    | reference voltage                                    | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> – 0.1 | 5.5                          |      |

| V <sub>SS_HV_ADC1</sub>              |    | ADC_1 ground and low reference voltage               | —                                     | 0                            | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> 4,5        | CC | Internal supply voltage                              | —                                     | _                            | _                            | V    |

Table 9. Recommended operating conditions (3.3 V)

| Symbol                                 |    | Parameter                         | Conditions | Value |                  |      |  |

|----------------------------------------|----|-----------------------------------|------------|-------|------------------|------|--|

| Symbol                                 |    | Falameter                         | Conditions | Min   | Max <sup>1</sup> | Unit |  |

| V <sub>SS_LV_REGCOR</sub> <sup>4</sup> | SR | Internal reference voltage        | —          | 0     | 0                | V    |  |

| V <sub>DD_LV_CORx</sub> 4,5            | СС | Internal supply voltage           | _          | —     | _                | V    |  |

| V <sub>SS_LV_CORx</sub> <sup>4</sup>   | SR | Internal reference voltage        | —          | 0     | 0                | V    |  |

| T <sub>A</sub>                         | SR | Ambient temperature under<br>bias | _          | -40   | 125              | °C   |  |

Table 9. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_IOy</sub> - V<sub>DD\_HV\_IOx</sub> | < 100 mV.</p>

<sup>3</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_ADC1</sub> - V<sub>DD\_HV\_ADC0</sub>| < 100 mV. As long as that condition is met, ADC\_0 and ADC\_1 can be operated at 5 V with the rest of the device operating at 3.3 V.</p>

<sup>4</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

$^5~$  The low voltage supplies (V\_DD\_LV\_xxx) are not all independent.

$V_{DD\_LV\_COR1}$  and  $V_{DD\_LV\_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly,  $V_{SS\_LV\_COR1}$  and  $V_{SS\_LV\_COR2}$  are internally shorted.

$V_{DD\_LV\_REGCOR} \text{ and } V_{DD\_LV\_REGCORx} \text{ are physically shorted internally, as are } V_{SS\_LV\_REGCOR} \text{ and } V_{SS\_LV\_CORx}.$

| Symbol          | с | Parameter                                          | Conditions                        | Va   | lue | Unit |

|-----------------|---|----------------------------------------------------|-----------------------------------|------|-----|------|

|                 | C | Parameter                                          | Conditions                        | Min  | Max | Unit |

| I <sub>PD</sub> | Ρ | Equivalent pull-down current                       | $V_{IN} = V_{IL}$                 | 10   | _   | μA   |

|                 |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | _    | 130 |      |

| IIL             | Ρ | Input leakage current (all<br>bidirectional ports) | T <sub>A</sub> = -40 to 125 °C    | -1   | 1   | μA   |

| IIL             | Ρ | Input leakage current (all ADC input-only ports)   | T <sub>A</sub> = -40 to 125 °C    | -0.5 | 0.5 | μA   |

| C <sub>IN</sub> | D | Input capacitance                                  | —                                 | _    | 10  | pF   |

|                 | D | RESET, equivalent pull-up current                  | V <sub>IN</sub> = V <sub>IL</sub> | –130 | _   | μA   |

| I <sub>PU</sub> |   |                                                    | V <sub>IN</sub> = V <sub>IH</sub> | _    | -10 | μΛ   |

Table 19. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0) (continued)

<sup>1</sup> "SR" parameter values must not exceed the absolute maximum ratings shown in Table 7.

Table 20. Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol                  | с |                | Parameter                                      | Conditions                                                    |        | Va    | lue   | Unit |

|-------------------------|---|----------------|------------------------------------------------|---------------------------------------------------------------|--------|-------|-------|------|

| Gymbol                  | Ŭ |                | i arameter                                     | Conditions                                                    |        | Тур   | Max   |      |

| I <sub>DD_LV_CORx</sub> | Т |                | RUN—Maximum mode <sup>1</sup>                  | V <sub>DD_LV_CORx</sub>                                       | 40 MHz | 62    | 77    | mA   |

|                         |   |                |                                                | externally forced at 1.3 V                                    | 64 MHz | 71    | 88    | 1    |

|                         |   |                | RUN—Typical mode <sup>2</sup>                  |                                                               | 40 MHz | 45    | 56    | 1    |

|                         |   |                |                                                |                                                               | 64 MHz | 52    | 65    | 1    |

|                         | Ρ |                | RUN—Maximum mode <sup>3</sup>                  | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | 64 MHz | 60    | 75    |      |

|                         |   | ent            | HALT mode <sup>4</sup>                         | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1.5   | 10    |      |

|                         |   | Supply current | STOP mode <sup>5</sup>                         | V <sub>DD_LV_CORx</sub><br>externally forced at 1.3 V         | _      | 1     | 10    |      |

| I <sub>DD_FLASH</sub>   | Т | ddng           | Flash during read                              | V <sub>DD_HV_FL</sub> at 5.0 V                                | —      | 10    | 12    |      |

|                         |   | 0,             | Flash during erase operation on 1 flash module | V <sub>DD_HV_FL</sub> at 5.0 V                                | _      | 15    | 19    |      |

| I <sub>DD_ADC</sub>     | Т |                | ADC—Maximum mode <sup>1</sup>                  | V <sub>DD_HV_ADC0</sub> at 5.0 V                              | ADC_1  | 3.5   | 5     | -    |

|                         |   |                |                                                | V <sub>DD_HV_ADC1</sub> at 5.0 V<br>f <sub>ADC</sub> = 16 MHz | ADC_0  | 3     | 4     | 1    |

|                         |   |                | ADC—Typical mode <sup>2</sup>                  |                                                               | ADC_1  | 0.8   | 1     | 1    |

|                         |   |                |                                                |                                                               | ADC_0  | 0.005 | 0.006 | 1    |

| I <sub>DD_OSC</sub>     | Т |                | Oscillator                                     | V <sub>DD_OSC</sub> at 5.0 V                                  | 8 MHz  | 2.6   | 3.2   | 1    |

<sup>1</sup> Maximum mode: FlexPWM, ADCs, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, 1st and 2nd PLL enabled. I/O supply current excluded.

<sup>2</sup> Typical mode configurations: DSPI, LINFlex, FlexCAN, 15 output pins, 1st PLL only. I/O supply current excluded.

| Ded      | 144       | LQFP        | 100 LQFP  |             |  |  |

|----------|-----------|-------------|-----------|-------------|--|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[72]  | 1%        | 1%          | _         | _           |  |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[73]  | 1%        | 1%          | _         | _           |  |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[74]  | 1%        | 1%          | _         | _           |  |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[75]  | 1%        | 1%          | _         |             |  |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[76]  | 1%        | 1%          | _         | _           |  |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |  |

| PAD[107] | 20%       | 17%         | _         |             |  |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |  |

| PAD[106] | 18%       | 16%         | _         |             |  |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |  |

| PAD[105] | 16%       | 14%         | _         | _           |  |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |  |

| PAD[104] | 14%       | 13%         | _         |             |  |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |  |

| PAD[103] | 12%       | 11%         | —         |             |  |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |  |

| PAD[101] | 11%       | 9%          | _         | _           |  |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |  |

| TCK      | 1%        | 1%          | 1%        | 1%          |  |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |  |

| PAD[102] | 11%       | 10%         | _         | —           |  |  |

### Table 24. I/O weight (continued)

| Symbol           | С | Parameter                                    | Conditions <sup>1</sup> | Max value | Unit |

|------------------|---|----------------------------------------------|-------------------------|-----------|------|

| f <sub>max</sub> | С | Maximum working frequency at given number of | 2 wait states           | 66        | MHz  |

|                  |   | wait states in worst conditions              | 0 wait states           | 18        |      |

### Table 34. Flash memory read access timing

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

### AC specifications 3.16

#### 3.16.1 **Pad AC specifications**

| Table 35. Outpu | t pin | transition | times |

|-----------------|-------|------------|-------|

|-----------------|-------|------------|-------|

| Symb                          |    | с | Parameter                                      |                           | onditions <sup>1</sup>                                             |     | Value | )   | Unit |

|-------------------------------|----|---|------------------------------------------------|---------------------------|--------------------------------------------------------------------|-----|-------|-----|------|

| Synn                          | 01 | C | Falameter                                      | Conditions                |                                                                    | Min | Тур   | Max | Unit |

| t <sub>tr</sub>               | CC | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                        | —   | —     | 50  | ns   |

|                               |    | Т | SLOW configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0                                                        | —   | —     | 100 |      |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                    | —   | —     | 125 |      |

|                               |    | D |                                                | C <sub>L</sub> = 25 pF    | $V_{DD} = 3.3 V \pm 10\%$ ,                                        | —   | —     | 40  |      |

|                               |    | Т |                                                | C <sub>L</sub> = 50 pF    | PAD3V5V = 1                                                        | —   | —     | 50  |      |

|                               |    | D | -                                              | C <sub>L</sub> = 100 pF   |                                                                    | _   | —     | 75  |      |

| t <sub>tr</sub>               | СС | D | MEDIUM configuration                           | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                        | —   | —     | 10  | ns   |

|                               |    | Т |                                                | C <sub>L</sub> = 50 pF    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1                                   | _   | —     | 20  |      |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | —   | —     | 40  |      |

|                               |    | D |                                                | C <sub>L</sub> = 25 pF    |                                                                    | —   | —     | 12  |      |

|                               |    | Т |                                                | C <sub>L</sub> = 50 pF    |                                                                    | —   | —     | 25  |      |

|                               |    | D |                                                | C <sub>L</sub> = 100 pF   |                                                                    | _   | —     | 40  |      |

| t <sub>tr</sub>               | СС | D | Output transition time output pin <sup>2</sup> | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,                                        | —   | —     | 4   | ns   |

|                               |    |   | FAST configuration                             | C <sub>L</sub> = 50 pF    | PAD3V5V = 0<br>SIUL.PCRx.SRC = 1                                   | _   | —     | 6   |      |

|                               |    |   |                                                | C <sub>L</sub> = 100 pF   |                                                                    | _   |       | 12  |      |

|                               |    |   |                                                | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1                      | —   | —     | 4   |      |

|                               |    |   |                                                | C <sub>L</sub> = 50 pF    | SIUL.PCRx.SRC = 1                                                  | —   | —     | 7   |      |

|                               |    |   |                                                | C <sub>L</sub> = 100 pF   |                                                                    | —   | —     | 12  |      |

| t <sub>SYM</sub> <sup>3</sup> | СС | Т | Symmetric transition time, same drive          | V <sub>DD</sub> = 5.0 V : | ± 10%, PAD3V5V = 0                                                 | —   | —     | 4   | ns   |

|                               |    |   | strength between N and P transistor            | V <sub>DD</sub> = 3.3 V : | ± 10%, PAD3V5V = 1                                                 | —   | —     | 5   |      |

<sup>1</sup> V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified <sup>2</sup> C<sub>L</sub> includes device and package capacitances (C<sub>PKG</sub> < 5 pF).

<sup>3</sup> Transition timing of both positive and negative slopes will differ maximum 50%

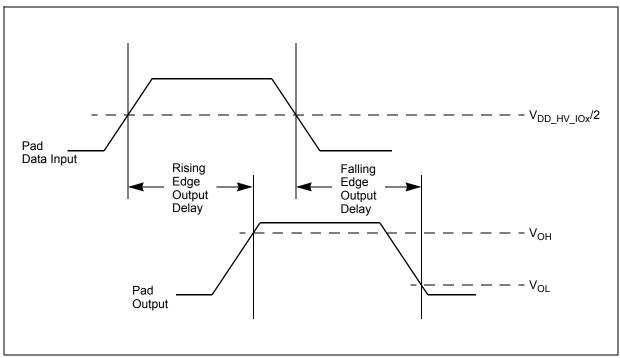

Figure 18. Pad output delay

## 3.17 AC timing characteristics

## 3.17.1 **RESET** pin characteristics

The MPC5604P implements a dedicated bidirectional  $\overline{\text{RESET}}$  pin.

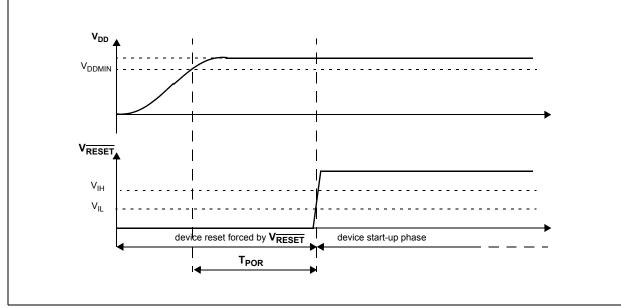

Figure 19. Start-up reset requirements

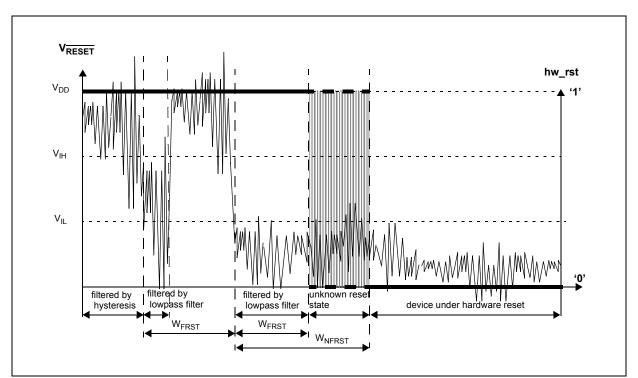

Figure 20. Noise filtering on reset signal

| Symb             | Symbol C |   | Parameter                                  | Conditions <sup>1</sup>                                                                          | Value               |     |                      | Unit |

|------------------|----------|---|--------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|-----|----------------------|------|

| C yms            |          |   |                                            | Conditions                                                                                       | Min                 | Тур | Мах                  |      |

| V <sub>IH</sub>  | SR       | Ρ | Input High Level CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.65V <sub>DD</sub> | _   | V <sub>DD</sub> +0.4 | V    |

| V <sub>IL</sub>  | SR       | Ρ | Input low Level CMOS<br>(Schmitt Trigger)  | _                                                                                                | -0.4                | _   | 0.35V <sub>DD</sub>  | V    |

| V <sub>HYS</sub> | СС       | С | Input hysteresis CMOS<br>(Schmitt Trigger) | _                                                                                                | 0.1V <sub>DD</sub>  | _   | _                    | V    |

| V <sub>OL</sub>  | СС       | Ρ | Output low level                           | Push Pull, I <sub>OL</sub> = 2mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                   | _   | 0.1V <sub>DD</sub>   | V    |

|                  |          |   |                                            | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>            | _                   | _   | 0.1V <sub>DD</sub>   |      |

|                  |          |   |                                            | Push Pull, I <sub>OL</sub> = 1mA,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | —                   | _   | 0.5                  |      |

Table 36. RESET electrical characteristics

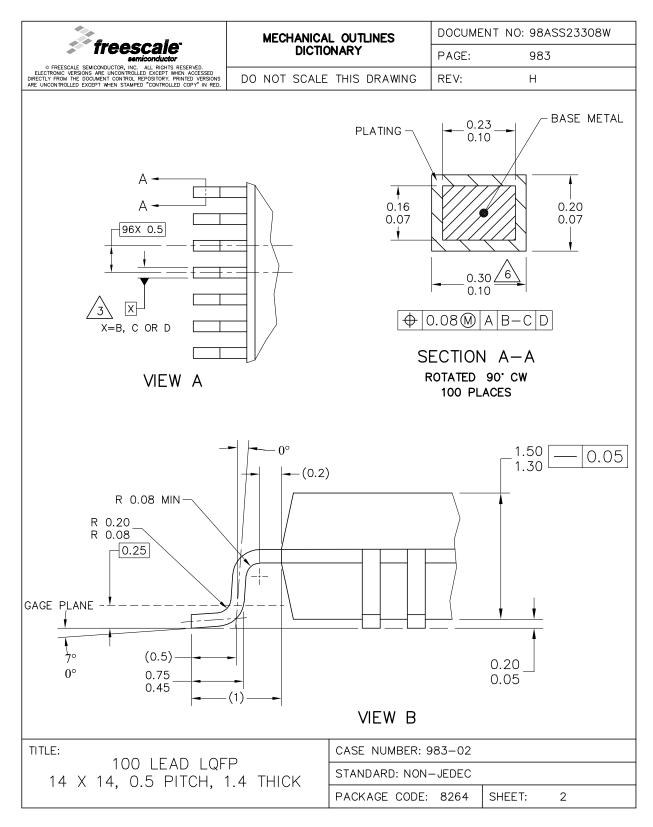

Figure 40. 100 LQFP package mechanical drawing (part 2)

MPC5604P Microcontroller Data Sheet, Rev. 8

|                  | Dimensions |        |        |                     |        |        |  |

|------------------|------------|--------|--------|---------------------|--------|--------|--|

| Symbol           | mm         |        |        | inches <sup>1</sup> |        |        |  |

|                  | Min        | Тур    | Max    | Min                 | Тур    | Max    |  |

| А                |            | _      | 1.600  | _                   |        | 0.0630 |  |

| A1               | 0.050      | _      | 0.150  | 0.0020              | —      | 0.0059 |  |

| A2               | 1.350      | 1.400  | 1.450  | 0.0531              | 0.0551 | 0.0571 |  |

| b                | 0.170      | 0.220  | 0.270  | 0.0067              | 0.0087 | 0.0106 |  |

| С                | 0.090      | _      | 0.200  | 0.0035              | —      | 0.0079 |  |

| D                | 15.800     | 16.000 | 16.200 | 0.6220              | 0.6299 | 0.6378 |  |

| D1               | 13.800     | 14.000 | 14.200 | 0.5433              | 0.5512 | 0.5591 |  |

| D3               | _          | 12.000 | _      | —                   | 0.4724 | —      |  |

| Е                | 15.800     | 16.000 | 16.200 | 0.6220              | 0.6299 | 0.6378 |  |

| E1               | 13.800     | 14.000 | 14.200 | 0.5433              | 0.5512 | 0.5591 |  |

| E3               | _          | 12.000 | _      | —                   | 0.4724 | —      |  |

| е                | —          | 0.500  | _      | —                   | 0.0197 | —      |  |

| L                | 0.450      | 0.600  | 0.750  | 0.0177              | 0.0236 | 0.0295 |  |

| L1               | —          | 1.000  | -      | —                   | 0.0394 | —      |  |

| k                | 0.0°       | 3.5°   | 7.0°   | 0.0°                | 3.5°   | 7.0°   |  |

| ccc <sup>2</sup> |            | 0.08   | 1      |                     | 0.0031 |        |  |

Table 41.

<sup>1</sup> Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

<sup>2</sup> Tolerance

## 6 Document revision history

Table 42 summarizes revisions to this document.

| Revision | Date     | Substantive changes                                                                                                                                                                                                                                                                                                               |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1   | Aug 2008 | Initial release                                                                                                                                                                                                                                                                                                                   |

| Rev. 2   | Nov 2008 | Table 5:TDO and TDI pins (Port pins B[4:5] are single function pins.                                                                                                                                                                                                                                                              |

|          |          | Table 10, Table 11:         Thermal characteristics added.                                                                                                                                                                                                                                                                        |

|          |          | Table 11, Table 12:EMI testing specifications split into separate tables for Normal mode and Airbag mode;data to be added in a later revision.                                                                                                                                                                                    |

|          |          | Table 16, Table 17, Table 19, Table 20:Supply current specifications split into separate tables for Normal mode and Airbag mode;data to be added in a later revision.                                                                                                                                                             |

|          |          | <ul> <li>Table 21:</li> <li>Values for I<sub>OL</sub> and I<sub>OH</sub> (in Conditions column) changed.</li> <li>Max values for V<sub>OH_S</sub>, V<sub>OH_M</sub>, V<sub>OH_F</sub> and V<sub>OH_SYM</sub> deleted.</li> <li>V<sub>ILR</sub> max value changed.</li> <li>I<sub>PUR</sub> min and max values changed.</li> </ul> |

|          |          | Table 27:         Sensitivity value changed.         Table 30:                                                                                                                                                                                                                                                                    |

|          |          | Most values in table changed.                                                                                                                                                                                                                                                                                                     |

| Rev. 3   | Feb 2009 | <ul> <li>Description of system requirements, controller characteristics and how controller<br/>characteristics are guaranteed updated.</li> <li>Electrical parameters updated.</li> </ul>                                                                                                                                         |

|          |          | <ul> <li>EMI characteristics are now in one table; values have been updated.</li> <li>ESD characteristics are now in one table.</li> </ul>                                                                                                                                                                                        |

|          |          | • Electrical parameters are identified as either system requirements or controller characteristics. Method used to guarantee each controller characteristic is noted in table.                                                                                                                                                    |

|          |          | AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing,<br>and DSPI Timing sections deleted                                                                                                                                                                                                                    |

### Table 42. Revision history

| Revision | Date        | Substantive changes                                                                                                                                                          |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 4   | 24-Jun-2009 | Through all document:                                                                                                                                                        |

|          |             | <ul> <li>Replaced all "RESET_B" occurrences with "RESET" through all document.</li> </ul>                                                                                    |

|          |             | <ul> <li>AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing, and<br/>DSPI Timing sections inserted again.</li> </ul>                                  |

|          |             | <ul> <li>Electrical parameters updated.</li> </ul>                                                                                                                           |

|          |             | - Electrical parameters upuateu.                                                                                                                                             |

|          |             | Table 2                                                                                                                                                                      |

|          |             | – Added row for Data Flash.                                                                                                                                                  |

|          |             | Table 3                                                                                                                                                                      |

|          |             | <ul> <li>Added a footnote regarding the decoupling capacitors.</li> </ul>                                                                                                    |

|          |             | Table 5                                                                                                                                                                      |

|          |             | – Removed the "other function" column.                                                                                                                                       |

|          |             | <ul> <li>Rearranged the contents.</li> </ul>                                                                                                                                 |

|          |             | Table 15                                                                                                                                                                     |

|          |             | <ul> <li>Updated definition of Condition column.</li> </ul>                                                                                                                  |

|          |             | Table 20                                                                                                                                                                     |

|          |             | <ul> <li>merged in an unique Table the power consumption data related to "Maximum<br/>mode" and "Airbag mode".</li> </ul>                                                    |

|          |             | Table 22                                                                                                                                                                     |

|          |             | <ul> <li>merged in an unique Table the power consumption data related to "Maximum<br/>mode" and "Airbag mode".</li> </ul>                                                    |

|          |             | Table 30                                                                                                                                                                     |

|          |             | – Updated the parameter definition of $\Delta$ RCMVAR.                                                                                                                       |

|          |             | – Removed the condition definition of $\Delta$ RCMVAR.                                                                                                                       |

|          |             | Table 30                                                                                                                                                                     |

|          |             | <ul> <li>Added t<sub>ADC_C</sub> and TUE rows.</li> </ul>                                                                                                                    |

|          |             | Table 31                                                                                                                                                                     |

|          |             | <ul> <li>Added t<sub>ADC C</sub> and TUE rows.</li> </ul>                                                                                                                    |

|          |             | – Removed R <sub>sw2.</sub>                                                                                                                                                  |

|          |             | Table 34                                                                                                                                                                     |

|          |             | – Added.                                                                                                                                                                     |

|          |             | Table 29                                                                                                                                                                     |

|          |             | <ul> <li>Updated and added footnotes.</li> </ul>                                                                                                                             |

|          |             | Section 3.17.1, "RESET pin characteristics                                                                                                                                   |

|          |             | <ul> <li>Replaces whole section.</li> </ul>                                                                                                                                  |

|          |             | Table 38                                                                                                                                                                     |

|          |             | <ul> <li>Renamed the "Flash (KB)" heading column in "Code Flash / Data Flash (EE) (KB)"</li> <li>Replaced the value of RAM from 32 to 36KB in the last four rows.</li> </ul> |

| Revision | Date        | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 5   | 06-Oct-2009 | <ul> <li>Removed B[4] and B[5] rows from "Pin muxing" table and inserted them on "System pins" table.</li> <li>Updated package pinout.</li> <li>Rewrote entirely section "Power Up/dpwn Sequencing" section.</li> <li>Renamend "V<sub>DD_LV_PLL</sub>" and "V<sub>SS_LV_PLL</sub>" supply pins with respectively "V<sub>DD_LV_COR3</sub>" and "V<sub>SS_LV_COR3</sub>".</li> <li>Added explicative figures on "Electrical characteristics" section.</li> <li>Updated "Thermal characteristics" for 100-pin.</li> <li>Proposed two different configuration of "voltage regulator Inserted Power Up/Down sequence.</li> <li>Added explicative figures on "DC Electrical characteristics".</li> <li>Added "I/O pad current specification" section.</li> <li>Renamed the "Airbag mode" with "Typical mode"and updated the values on "supply current" tables.</li> </ul>                                                                                                          |

| Rev. 6   | 12-Feb-2010 | Inserted label of Y-axis in the "Independent ADC supply" figure.<br>"Recommended Operating Conditions" tables:<br>Updated the T <sub>A</sub> value<br>Moved the T <sub>J</sub> row to "Absolute Maximum Ratings" table.<br>Rewrite note 1 and 3<br>Inverted Min a Typ value of C <sub>DEC2</sub> on "Voltage Regulator Electrical Characteristics" table.<br>Removed an useless duplicate of "Voltage Regulator Electrical Characteristics" table.<br>Inserted the name of C <sub>S</sub> into "Input Equivalent Circuit" figure.<br>Removed leakage lvpp from datasheet.<br>Updated "Supply Current" tables.<br>Added note on "Output pin transition times" table.<br>Updated "Temperature Sensor Electrical Characteristics" table.<br>Updated "16 MHz RC Oscillator Electrical Characteristics" table.<br>Removed the note about the condition from "Flash read access timing" table.<br>Removed the notes that assert the values need to be confirmed before validation. |

| Table 42. F | Revision | history | (continued) |

|-------------|----------|---------|-------------|

|-------------|----------|---------|-------------|

| Revision | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 7   |      | <ul> <li>Formatting and editorial changes throughout</li> <li>Removed all content referencing Junction Temperature Sensor</li> <li>Section 1, "Introduction: changed title (was: Overview); reorganized contents</li> <li>MPC5604P device comparison:</li> <li>ADC feature: changed "16 channels" to "15-channel"; added footnote to to indicate that four channels are shared between the two ADCs</li> <li>removed MPC5602P column</li> <li>indicated that data flash memory is an optional feature</li> <li>changed "dual channel" to "selectable single or dual channel support" in FlexRay footnote</li> <li>updated "eTimer" feature</li> <li>updated footnote relative to "Digital power supply" feature</li> <li>Updated MPC5604P block diagram</li> <li>Added APC5604P series block summary</li> <li>Added Section 1.5, "Feature details</li> <li>Section 2.1, "Package pinouts: removed alternate functions from pinout diagrams</li> <li>Supply pins: updated dable</li> <li>Pin muxing: added rows "B[4]" and "B[5]</li> <li>Section 3.3, "Absolute maximum ratings: added voltage specifications to titles of Figure 4 and Figure 5; in Table 7, changed row "V<sub>SS-HV</sub> / Digital Ground" to "V<sub>SS</sub> / Device Ground"; updated symbols</li> <li>Section 3.4, "Recommended operating conditions: added voltage specifications to titles of Figure 7</li> </ul> |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |      | Updated Section 3.6, "Electromagnetic interference (EMI) characteristics<br>Section 3.8.1, "Voltage regulator electrical characteristics: amended titles of Table 15 and<br>Table 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |      | Voltage regulator electrical characteristics (configuration without resistor on base) and<br>Voltage regulator electrical characteristics (configuration with resistor on base):<br>updated symbol and values for V <sub>DD_LV_REGCOR</sub><br>Low voltage monitor electrical characteristics: Updated V <sub>MLVDDOK_H</sub> max value—was<br>1.15 V; is 1.145 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | Section 3.10, "DC electrical characteristics: reorganized contents<br>Updated Section 3.10.1, "NVUSRO register (includes adding<br>"NVUSRO[OSCILLATOR_MARGIN] field description" table<br>Supply current (5.0 V, NVUSRO[PAD3V5V] = 0): updated symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Revision           | Date        | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 7<br>(cont'd) | 07-Apr-2011 | <ul> <li>Corrected parameter descriptions in DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1):</li> <li>V<sub>OL_F</sub>—was "Fast, high level output voltage"; is "Fast, low level output voltage"</li> <li>V<sub>OL_SYM</sub>—was "Symmetric, high level output voltage"; is "Symmetric, low level output voltage"</li> <li>Supply current (3.3 V, NVUSRO[PAD3V5V] = 1): updated symbols</li> <li>Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0): replaced instances of EXTAL with XTAL</li> <li>Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1): replaced instances of EXTAL with XTAL</li> <li>FMPLL electrical characteristics: replaced "PLLMRFM" with "FMPLL" in table title; updated conditions; removed f<sub>sys</sub> row; updated f<sub>FMPLLOUT</sub> min value</li> <li>ADC conversion characteristics: updated symbols; added row t<sub>ADC_PU</sub></li> <li>Flash memory read access timing: added footnote to "Conditions" column</li> <li>Section 3.16.1, "Pad AC specifications: added Pad output delay diagram</li> <li>In the range of figures "DSPI Classic SPI Timing — Master, CPHA = 0" to "DSPI PCS Strobe (PCSS) Timing": added note</li> <li>Removed Orderable Part Number Summary table</li> <li>Updated "Commercial product code structure" figure</li> <li>Table A-1: Added abbreviations "DUT", "NPN", and "RBW"</li> </ul> |