Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | CANbus, FlexRay, LINbus, SPI, UART/USART                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 108                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64K x 8                                                                 |

| RAM Size                   | 40K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 30x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

|                            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5604pgf1vlg6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

### 1.1 Document overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5603P/4P series of microcontroller units (MCUs). It also describes the device features and highlights important electrical and physical characteristics. For functional characteristics, refer to the device reference manual.

# 1.2 Description

This 32-bit system-on-chip (SoC) automotive microcontroller family is the latest achievement in integrated automotive application controllers. It belongs to an expanding range of automotive-focused products designed to address chassis applications—specifically, electrical hydraulic power steering (EHPS) and electric power steering (EPS)—as well as airbag applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology.

The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

### 1.3 Device comparison

Table 1 provides a summary of different members of the MPC5604P family and their features to enable a comparison among the family members and an understanding of the range of functionality offered within this family.

| Feature                                              | MPC5603P          | MPC5604P         |

|------------------------------------------------------|-------------------|------------------|

| Code flash memory (with ECC)                         | 384 KB            | 512 KB           |

| Data flash memory / EE option (with ECC)             | 64 KB (optic      | onal feature)    |

| SRAM (with ECC)                                      | 36 KB             | 40 KB            |

| Processor core                                       | 32-bit e          | 200z0h           |

| Instruction set                                      | VLE (variable le  | ength encoding)  |

| CPU performance                                      | 0–64              | MHz              |

| FMPLL (frequency-modulated phase-locked loop) module | 2                 |                  |

| INTC (interrupt controller) channels                 | 14                | 17               |

| PIT (periodic interrupt timer)                       | 1 (includes fou   | r 32-bit timers) |

| eDMA (enhanced direct memory access) channels        | 1                 | 6                |

| FlexRay <sup>1</sup>                                 | Optiona           | I feature        |

| FlexCAN (controller area network)                    | 2 <sup>2</sup>    | 2,3              |

| Safety port                                          | Yes (via second F | FlexCAN module)  |

| FCU (fault collection unit)                          | Ye                | es               |

| CTU (cross triggering unit)                          | Ye                | es               |

| Symbol   | Description                                                                                                                                                                               | Pad speed <sup>1</sup> |             | peed <sup>1</sup> | Pin     |         |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|-------------------|---------|---------|--|

| Symbol   | Description                                                                                                                                                                               | Direction              | SRC = 0     | SRC = 1           | 100-pin | 144-pin |  |

| EXTAL    | <ul> <li>Analog input of oscillator amplifier<br/>circuit, when oscillator not in bypass<br/>mode</li> <li>Analog input for clock generator when<br/>oscillator in bypass mode</li> </ul> | _                      | _           |                   | 19      | 30      |  |

| TMS      | JTAG state machine control                                                                                                                                                                | Bidirectional          | Slow        | Fast              | 59      | 87      |  |

| тск      | JTAG clock                                                                                                                                                                                | Input only             | Slow        | —                 | 60      | 88      |  |

| TDI      | Test Data In                                                                                                                                                                              | Input only             | Slow        | Medium            | 58      | 86      |  |

| TDO      | Test Data Out                                                                                                                                                                             | Output only            | Slow        | Fast              | 61      | 89      |  |

|          | Reset pin, available on                                                                                                                                                                   | 100-pin and 144-       | pin packag  | e.                |         |         |  |

| RESET    | Bidirectional reset with Schmitt trigger<br>characteristics and noise filter                                                                                                              | Bidirectional          | Medium      | _                 | 20      | 31      |  |

|          | Test pin, available on 1                                                                                                                                                                  | 00-pin and 144-p       | oin package | 9.                |         |         |  |

| VPP_TEST | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                                              | _                      | _           | _                 | 74      | 107     |  |

Table 4. System pins (continued)

<sup>1</sup> SCR values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

### 2.2.3 Pin muxing

Table 5 defines the pin list and muxing for the MPC5604P devices.

Each row of Table 5 shows all the possible ways of configuring each pin, via alternate functions. The default function assigned to each pin after reset is the ALTO function.

MPC5604P devices provide four main I/O pad types, depending on the associated functions:

- Slow pads are the most common, providing a compromise between transition time and low electromagnetic emission.

- *Medium pads* provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads provide maximum speed. They are used for improved NEXUS debugging capability.

- Symmetric pads are designed to meet FlexRay requirements.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance. For more information, see the data sheet's "Pad AC Specifications" section.

|             | Pad                             |                                      |                                     |                                           |                               | Pad s   | peed <sup>5</sup> | Pin     | No.     |

|-------------|---------------------------------|--------------------------------------|-------------------------------------|-------------------------------------------|-------------------------------|---------|-------------------|---------|---------|

| Port<br>pin | configuration<br>register (PCR) | Alternate<br>function <sup>1,2</sup> | Functions                           | Peripheral <sup>3</sup>                   | I/O<br>direction <sup>4</sup> | SRC = 0 | SRC = 1           | 100-pin | 144-pin |

| D[14]       | PCR[62]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[62]<br>B[1]<br>CS3<br>—<br>SIN | SIUL<br>FlexPWM_0<br>DSPI_3<br><br>DSPI_3 | I/O<br>O<br>O<br>I            | Slow    | Medium            | 73      | 105     |

| D[15]       | PCR[63]                         | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[63]<br>—<br>—<br>—<br>AN[4]    | SIUL<br>—<br>—<br>—<br>ADC_1              | Input only                    |         | _                 | 41      | 58      |

|             |                                 |                                      |                                     | Port E(16-bit)                            |                               |         |                   |         |         |

| E[0]        | PCR[64]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[64]<br>—<br>—<br>AN[5]         | SIUL<br>—<br>—<br>ADC_1                   | Input only                    | _       | _                 | 46      | 68      |

| E[1]        | PCR[65]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[65]<br>—<br>—<br>—<br>AN[4]    | SIUL<br>—<br>—<br>ADC_0                   | Input only                    |         | _                 | 27      | 39      |

| E[2]        | PCR[66]                         | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[66]<br>—<br>—<br>—<br>AN[5]    | SIUL<br>—<br>—<br>ADC_0                   | Input only                    | _       | _                 | 32      | 49      |

| E[3]        | PCR[67]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[67]<br>—<br>—<br>—<br>AN[6]    | SIUL<br>—<br>—<br>ADC_0                   | Input only                    | _       | _                 |         | 40      |

| E[4]        | PCR[68]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[68]<br>—<br>—<br>—<br>AN[7]    | SIUL<br>—<br>—<br>ADC_0                   | Input only                    |         | _                 | _       | 42      |

| E[5]        | PCR[69]                         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—    | GPIO[69]<br>—<br>—<br>—<br>AN[8]    | SIUL<br>—<br>—<br>—<br>ADC_0              | Input only                    |         |                   | —       | 44      |

Table 5. Pin muxing (continued)

| Symbol                                 |    | Parameter                         | Conditions | Val | ue               | Unit |

|----------------------------------------|----|-----------------------------------|------------|-----|------------------|------|

| Symbol                                 |    | Falameter                         | Conditions | Min | Max <sup>1</sup> |      |

| V <sub>SS_LV_REGCOR</sub> <sup>4</sup> | SR | Internal reference voltage        | —          | 0   | 0                | V    |

| V <sub>DD_LV_CORx</sub> 4,5            | СС | Internal supply voltage           | —          | —   | _                | V    |

| V <sub>SS_LV_CORx</sub> <sup>4</sup>   | SR | Internal reference voltage        | —          | 0   | 0                | V    |

| T <sub>A</sub>                         | SR | Ambient temperature under<br>bias | _          | -40 | 125              | °C   |

Table 9. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> Parametric figures can be out of specification when voltage drops below 4.5 V, however, guaranteeing the full functionality. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

<sup>2</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_IOy</sub> - V<sub>DD\_HV\_IOx</sub> | < 100 mV.</p>

<sup>3</sup> The difference between each couple of voltage supplies must be less than 100 mV, |V<sub>DD\_HV\_ADC1</sub> - V<sub>DD\_HV\_ADC0</sub>| < 100 mV. As long as that condition is met, ADC\_0 and ADC\_1 can be operated at 5 V with the rest of the device operating at 3.3 V.</p>

<sup>4</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

$^5~$  The low voltage supplies (V\_DD\_LV\_xxx) are not all independent.

$V_{DD\_LV\_COR1}$  and  $V_{DD\_LV\_COR2}$  are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash module. Similarly,  $V_{SS\_LV\_COR1}$  and  $V_{SS\_LV\_COR2}$  are internally shorted.

$V_{DD\_LV\_REGCOR} \text{ and } V_{DD\_LV\_REGCORx} \text{ are physically shorted internally, as are } V_{SS\_LV\_REGCOR} \text{ and } V_{SS\_LV\_CORx}.$

<sup>5</sup> Thermal characterization parameter indicating the temperature difference between the case and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

### 3.5.2 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from Equation 1:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D}) \qquad \qquad Eqn. 1$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in Equation 2 as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \qquad \qquad Eqn. 2$$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction to case thermal resistance (°C/W)

$R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using Equation 3:

$$T_{J} = T_{T} + (\Psi_{JT} \times P_{D}) \qquad \qquad Eqn. 3$$

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\Psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

References:

Semiconductor Equipment and Materials International 3081 Zanker Road San Jose, CA 95134 U.S.A. (408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

- 1. C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 3.6 Electromagnetic interference (EMI) characteristics

| Symbol    | Parameter          | Conditions                                        | Clocks                                      | Frequency       | Level<br>(Max) | Unit |

|-----------|--------------------|---------------------------------------------------|---------------------------------------------|-----------------|----------------|------|

| $V_{EME}$ | Radiated emissions | 5                                                 | f <sub>OSC</sub> 8 MHz                      | 150 kHz–150 MHz | 16             | dBµV |

|           |                    | conditions and EM testing per standard IEC61967-2 | f <sub>CPU</sub> 64 MHz<br>No PLL frequency | 150–1000 MHz    | 15             |      |

|           |                    | Supply voltage = 5 V DC                           | modulation                                  | IEC Level       | М              | —    |

|           |                    | Ambient temperature = 25 °C                       | f <sub>OSC</sub> 8 MHz                      | 150 kHz–150 MHz | 15             | dBµV |

|           |                    | Worst-case orientation                            | f <sub>CPU</sub> 64 MHz<br>1% PLL frequency | 150–1000 MHz    | 14             |      |

|           |                    |                                                   | modulation                                  | IEC Level       | М              | —    |

#### Table 12. EMI testing specifications

# 3.7 Electrostatic discharge (ESD) characteristics

Table 13. ESD ratings<sup>1,2</sup>

| Symbol                |    | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|----|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | SR | Electrostatic discharge (Human Body Model)     | —          | 2000          | V    |

| V <sub>ESD(CDM)</sub> | SR | Electrostatic discharge (Charged Device Model) | _          | 750 (corners) | V    |

|                       |    |                                                |            | 500 (other)   |      |

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

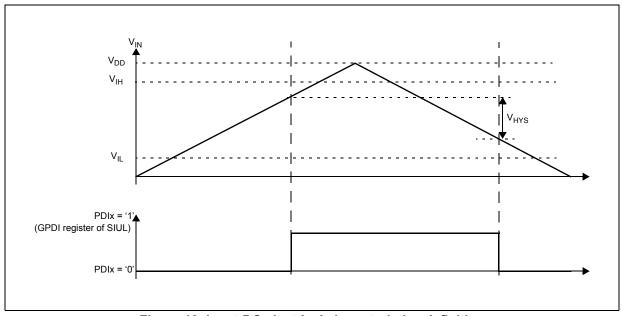

Figure 13. Input DC electrical characteristics definition

### 3.10.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 23.

| Package     |               |               | \$            | Supply segme  | nt            |                |               |

|-------------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|

| T ackage    | 1             | 2             | 3             | 4             | 5             | 6              | 7             |

| 144<br>LQFP | pin8 – pin20  | pin23 – pin38 | pin39 – pin55 | pin58 – pin68 | pin73 – pin89 | pin92 – pin125 | pin128 – pin5 |

| 100<br>LQFP | pin15 – pin26 | pin27 – pin38 | pin41 – pin46 | pin51 – pin61 | pin64 – pin86 | pin89 – pin10  | _             |

Table 24 provides the weight of concurrent switching I/Os.

In order to ensure device functionality, the sum of the weight of concurrent switching I/Os on a single segment should remain below 100%.

#### Table 24. I/O weight

| Pad     | 144       | LQFP        | 100 LQFP  |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Fau     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| NMI     | 1%        | 1%          | 1%        | 1%          |  |

| PAD[6]  | 6%        | 5%          | 14%       | 13%         |  |

| PAD[49] | 5%        | 4%          | 14%       | 12%         |  |

| PAD[84] | 14%       | 10%         | —         | —           |  |

| PAD[85] | 9%        | 7%          | —         | —           |  |

| Pad     | 144       | LQFP        | 100 LQFP  |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[86] | 9%        | 6%          | _         | _           |  |

| MODO[0] | 12%       | 8%          | _         |             |  |

| PAD[7]  | 4%        | 4%          | 11%       | 10%         |  |

| PAD[36] | 5%        | 4%          | 11%       | 9%          |  |

| PAD[8]  | 5%        | 4%          | 10%       | 9%          |  |

| PAD[37] | 5%        | 4%          | 10%       | 9%          |  |

| PAD[5]  | 5%        | 4%          | 9%        | 8%          |  |

| PAD[39] | 5%        | 4%          | 9%        | 8%          |  |

| PAD[35] | 5%        | 4%          | 8%        | 7%          |  |

| PAD[87] | 12%       | 9%          | —         | —           |  |

| PAD[88] | 9%        | 6%          | _         | —           |  |

| PAD[89] | 10%       | 7%          | _         |             |  |

| PAD[90] | 15%       | 11%         | _         |             |  |

| PAD[91] | 6%        | 5%          | _         | _           |  |

| PAD[57] | 8%        | 7%          | 8%        | 7%          |  |

| PAD[56] | 13%       | 11%         | 13%       | 11%         |  |

| PAD[53] | 14%       | 12%         | 14%       | 12%         |  |

| PAD[54] | 15%       | 13%         | 15%       | 13%         |  |

| PAD[55] | 25%       | 22%         | 25%       | 22%         |  |

| PAD[96] | 27%       | 24%         | _         | _           |  |

| PAD[65] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[67] | 1%        | 1%          | _         | _           |  |

| PAD[33] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[68] | 1%        | 1%          | _         |             |  |

| PAD[23] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[69] | 1%        | 1%          | _         |             |  |

| PAD[34] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[70] | 1%        | 1%          | _         | _           |  |

| PAD[24] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[71] | 1%        | 1%          | —         | —           |  |

| PAD[66] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[25] | 1%        | 1%          | 1%        | 1%          |  |

| PAD[26] | 1%        | 1%          | 1%        | 1%          |  |

#### Table 24. I/O weight (continued)

| Ded      | 144       | LQFP        | 100 LQFP  |             |  |

|----------|-----------|-------------|-----------|-------------|--|

| Pad      | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[27]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[28]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[63]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[72]  | 1%        | 1%          | _         |             |  |

| PAD[29]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[73]  | 1%        | 1%          | _         | _           |  |

| PAD[31]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[74]  | 1%        | 1%          | _         | _           |  |

| PAD[30]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[75]  | 1%        | 1%          | _         |             |  |

| PAD[32]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[76]  | 1%        | 1%          | _         | _           |  |

| PAD[64]  | 1%        | 1%          | 1%        | 1%          |  |

| PAD[0]   | 23%       | 20%         | 23%       | 20%         |  |

| PAD[1]   | 21%       | 18%         | 21%       | 18%         |  |

| PAD[107] | 20%       | 17%         | _         |             |  |

| PAD[58]  | 19%       | 16%         | 19%       | 16%         |  |

| PAD[106] | 18%       | 16%         | _         |             |  |

| PAD[59]  | 17%       | 15%         | 17%       | 15%         |  |

| PAD[105] | 16%       | 14%         | _         | _           |  |

| PAD[43]  | 15%       | 13%         | 15%       | 13%         |  |

| PAD[104] | 14%       | 13%         | _         |             |  |

| PAD[44]  | 13%       | 12%         | 13%       | 12%         |  |

| PAD[103] | 12%       | 11%         | —         |             |  |

| PAD[2]   | 11%       | 10%         | 11%       | 10%         |  |

| PAD[101] | 11%       | 9%          | _         |             |  |

| PAD[21]  | 10%       | 8%          | 10%       | 8%          |  |

| TMS      | 1%        | 1%          | 1%        | 1%          |  |

| TCK      | 1%        | 1%          | 1%        | 1%          |  |

| PAD[20]  | 16%       | 11%         | 16%       | 11%         |  |

| PAD[3]   | 4%        | 3%          | 4%        | 3%          |  |

| PAD[61]  | 9%        | 8%          | 9%        | 8%          |  |

| PAD[102] | 11%       | 10%         | _         | —           |  |

#### Table 24. I/O weight (continued)

| Ded     | 144 LQFP  |             | 100 LQFP  |             |  |

|---------|-----------|-------------|-----------|-------------|--|

| Pad     | Weight 5V | Weight 3.3V | Weight 5V | Weight 3.3V |  |

| PAD[13] | 10%       | 9%          | 12%       | 11%         |  |

| PAD[82] | 10%       | 9%          | —         |             |  |

| PAD[22] | 10%       | 9%          | 13%       | 12%         |  |

| PAD[83] | 10%       | 9%          | —         | _           |  |

| PAD[50] | 10%       | 9%          | 14%       | 12%         |  |

| PAD[97] | 10%       | 9%          | —         | _           |  |

| PAD[38] | 10%       | 9%          | 14%       | 13%         |  |

| PAD[14] | 9%        | 8%          | 14%       | 13%         |  |

| PAD[15] | 9%        | 8%          | 15%       | 13%         |  |

### Table 24. I/O weight (continued)

### Table 25. I/O consumption

| Symbol                             | Symbol                     |   | Parameter                       | Condi                          | tions <sup>1</sup>                            |                               | Value       |                               | Unit                        |     |   |     |   |

|------------------------------------|----------------------------|---|---------------------------------|--------------------------------|-----------------------------------------------|-------------------------------|-------------|-------------------------------|-----------------------------|-----|---|-----|---|

| Cymisol                            |                            | С | i arameter                      | Conditions                     |                                               | Min                           | Тур         | Max                           |                             |     |   |     |   |

| I <sub>SWTSLW</sub> ,2             | СС                         | D | for SLOW                        | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 | _                             | _           | 20                            | mA                          |     |   |     |   |

|                                    |                            |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                             | _           | 16                            |                             |     |   |     |   |

| I <sub>SWTMED</sub> <sup>(2)</sup> | SWTMED <sup>(2)</sup> CC E |   | for MEDIUM                      | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |                               | _           | 29                            | mA                          |     |   |     |   |

|                                    |                            |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _                             |             | 17                            |                             |     |   |     |   |

| I <sub>SWTFST</sub> <sup>(2)</sup> | СС                         | D | Dynamic I/O current<br>for FAST | C <sub>L</sub> = 25 pF         | V <sub>DD</sub> = 5.0 V ± 10%,<br>PAD3V5V = 0 |                               | _           | 110                           | mA                          |     |   |     |   |

|                                    |                            |   | configuration                   |                                | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |                               | _           | 50                            |                             |     |   |     |   |

| I <sub>RMSSLW</sub>                | СС                         | D |                                 | C <sub>L</sub> = 25 pF, 2 MHz  | $V_{DD} = 5.0 V \pm 10\%$                     | _                             | _           | 2.3                           | mA                          |     |   |     |   |

|                                    |                            |   |                                 |                                | I/O current for SLOW configuration            | C <sub>L</sub> = 25 pF, 4 MHz | PAD3V5V = 0 | _                             | _                           | 3.2 | 1 |     |   |

|                                    |                            |   |                                 | C <sub>L</sub> = 100 pF, 2 MHz |                                               |                               | _           | 6.6                           | 1                           |     |   |     |   |

|                                    |                            |   |                                 |                                |                                               |                               |             | C <sub>L</sub> = 25 pF, 2 MHz | $V_{DD} = 3.3 V \pm 10\%$ , |     | _ | 1.6 | 1 |

|                                    |                            |   |                                 | C <sub>L</sub> = 25 pF, 4 MHz  | PAD3V5V = 1                                   | —                             | —           | 2.3                           |                             |     |   |     |   |

|                                    |                            |   |                                 | C <sub>L</sub> = 100 pF, 2 MHz | ]                                             | _                             | _           | 4.7                           |                             |     |   |     |   |

### 3.13 16 MHz RC oscillator electrical characteristics

| Symbol                 | <u>د</u> | Parameter                                                                                                                                   | Conditions                                   | Value |     |     | Unit |

|------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|-----|-----|------|

| Symbol C               |          | Falanetei                                                                                                                                   | Conditions                                   | Min   | Тур | Max | Onit |

| f <sub>RC</sub>        | Ρ        | RC oscillator frequency                                                                                                                     | T <sub>A</sub> = 25 °C                       | _     | 16  | —   | MHz  |

| $\Delta_{ m RCMVAR}$   | Ρ        | Fast internal RC oscillator variation over temperature and supply with respect to $f_{RC}$ at $T_A = 25$ °C in high-frequency configuration |                                              | -5    |     | 5   | %    |

| $\Delta_{\rm RCMTRIM}$ | Т        | Post Trim Accuracy: The variation of the $PTF^1$ from the T <sub>A</sub> = 16 MHz                                                           |                                              | -1    | _   | 1   | %    |

| $\Delta_{\rm RCMSTEP}$ | Т        | Fast internal RC oscillator trimming step                                                                                                   | r trimming step $T_A = 25 \degree C - 1.6 -$ |       | %   |     |      |

Table 30. 16 MHz RC oscillator electrical characteristics

PTF = Post Trimming Frequency: The frequency of the output clock after trimming at typical supply voltage and temperature

## 3.14 Analog-to-digital converter (ADC) electrical characteristics

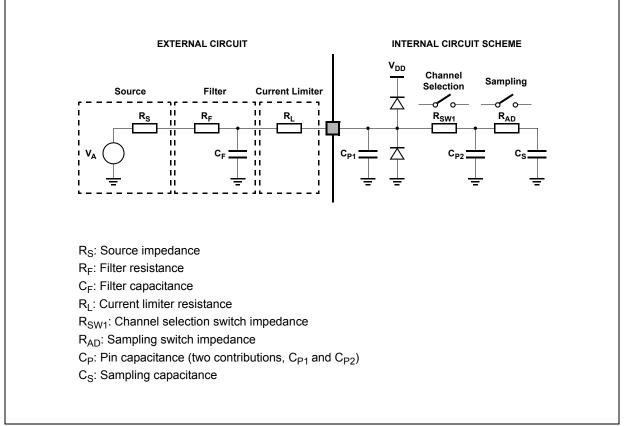

The device provides a 10-bit successive approximation register (SAR) analog-to-digital converter.

1

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  and  $C_{P2}$  being substantially two switched capacitances, with a frequency equal to the ADC conversion rate, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{P2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc \times (C_S+C_{P2}))$ ), where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{P2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Equation 4 generates a constraint for external network design, in particular on resistive path.

Figure 15. Input equivalent circuit

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_{F_2}$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in Figure 15): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch closed).

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_L$  sizing is obtained:

#### Eqn. 9

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

Eqn. 10

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

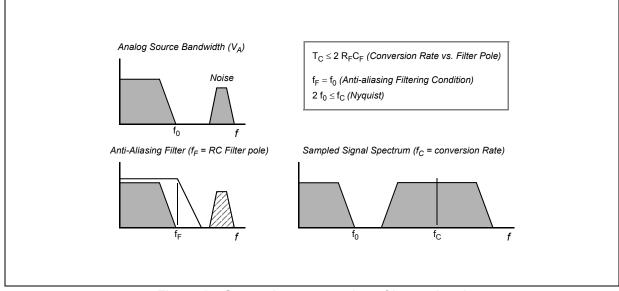

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $T_S$ ). The filter is typically designed to act as anti-aliasing.

Figure 17. Spectral representation of input signal

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive Equation 11 between the ideal and real sampled voltage on  $C_S$ :

| Symph                          | Symbol C |   | Parameter                                        | Conditions <sup>1</sup>                                                                                       |      | Value |     |        |  |

|--------------------------------|----------|---|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------|-----|--------|--|

| Symp                           |          |   | Parameter                                        | Conditions                                                                                                    | Min  | Тур   | Max | _ Unit |  |

| R <sub>SW1</sub> <sup>10</sup> | _        | D | Internal resistance of analog source             | V <sub>DD_HV_ADC</sub> =<br>5 V ± 10%                                                                         | _    | —     | 0.6 | kΩ     |  |

|                                |          |   |                                                  | V <sub>DD_HV_ADC</sub> =<br>3.3 V ± 10%                                                                       | _    | —     | 3   | kΩ     |  |

| R <sub>AD</sub> <sup>10</sup>  | —        | D | Internal resistance of analog — –                |                                                                                                               | _    | —     | 2   | kΩ     |  |

| I <sub>INJ</sub>               |          | Т | Input current injection                          | Current injection on<br>one ADC input,<br>different from the<br>converted one.<br>Remains within TUE<br>spec. | _5   |       | 5   | mA     |  |

| INL                            | СС       | Ρ | Integral non-linearity                           | No overload                                                                                                   | -1.5 |       | 1.5 | LSB    |  |

| DNL                            | СС       | Ρ | Differential non-linearity                       | No overload                                                                                                   | -1.0 |       | 1.0 | LSB    |  |

| OSE                            | СС       | Т | Offset error                                     | _                                                                                                             | _    | ±1    |     | LSB    |  |

| GE                             | СС       | Т | Gain error                                       | _                                                                                                             | _    | ±1    | _   | LSB    |  |

| TUE                            | СС       | Ρ | Total unadjusted error without current injection | thout — -2                                                                                                    |      | —     | 2.5 | LSB    |  |

| TUE                            | СС       | Т | Total unadjusted error with current injection    | 3                                                                                                             |      | _     | 3   | LSB    |  |

| Table 31. ADC | conversion | characteristics | (continued) |

|---------------|------------|-----------------|-------------|

|---------------|------------|-----------------|-------------|

<sup>1</sup> V<sub>DD</sub> = 3.3 V to 3.6 V / 4.5 V to 5.5 V, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified and analog input voltage from V<sub>SS\_HV\_ADCx</sub> to V<sub>DD\_HV\_ADCx</sub>.

<sup>2</sup> V<sub>AINx</sub> may exceed V<sub>SS\_HV\_AD</sub> and V<sub>DD\_HV\_AD</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

<sup>3</sup> Not allowed to refer this voltage to V<sub>DD\_HV\_ADV1</sub>, V<sub>SS\_HV\_ADV1</sub>

$^4$  Not allowed to refer this voltage to V\_DD\_HV\_ADV0, V\_SS\_HV\_ADV0

<sup>5</sup> AD clk clock is always half of the ADC module input clock defined via the auxiliary clock divider for the ADC.

<sup>6</sup> When configured to allow 60 MHz ADC, the minimum ADC clock speed is 9 MHz, below which precision is lost.

<sup>7</sup> During the sample time the input capacitance CS can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>ADC S</sub>. After the end of the sample time  $t_{ADC_S}$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_{ADC_S}$  depend on programming.

<sup>8</sup> This parameter includes the sample time  $t_{ADC S}$ .

<sup>9</sup> 20 MHz ADC clock. Specific prescaler is programmed on MC\_PLL\_CLK to provide 20 MHz clock to the ADC.

<sup>10</sup> See Figure 15.

# 4 Package characteristics

## 4.1 Package mechanical data

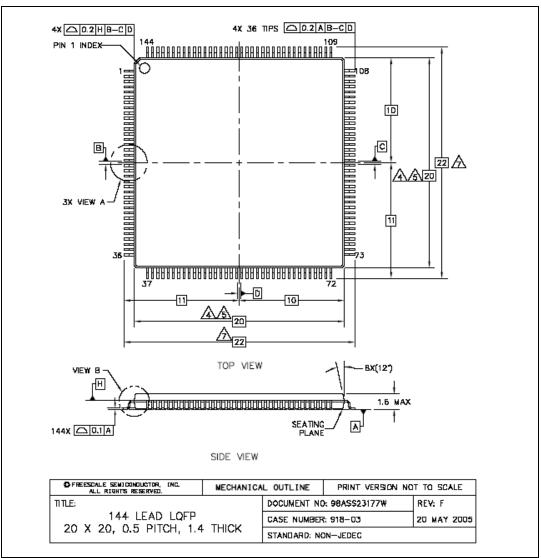

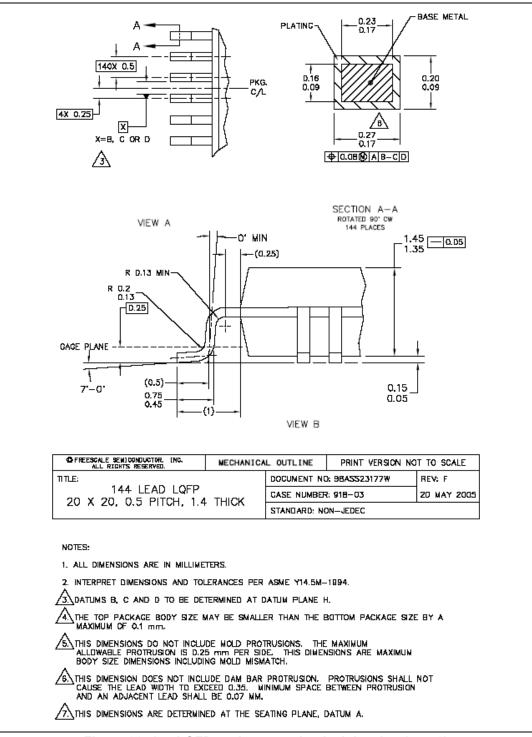

### 4.1.1 144 LQFP mechanical outline drawing

Figure 37. 144 LQFP package mechanical drawing (part 1)

Figure 38. 144 LQFP package mechanical drawing (part 2)

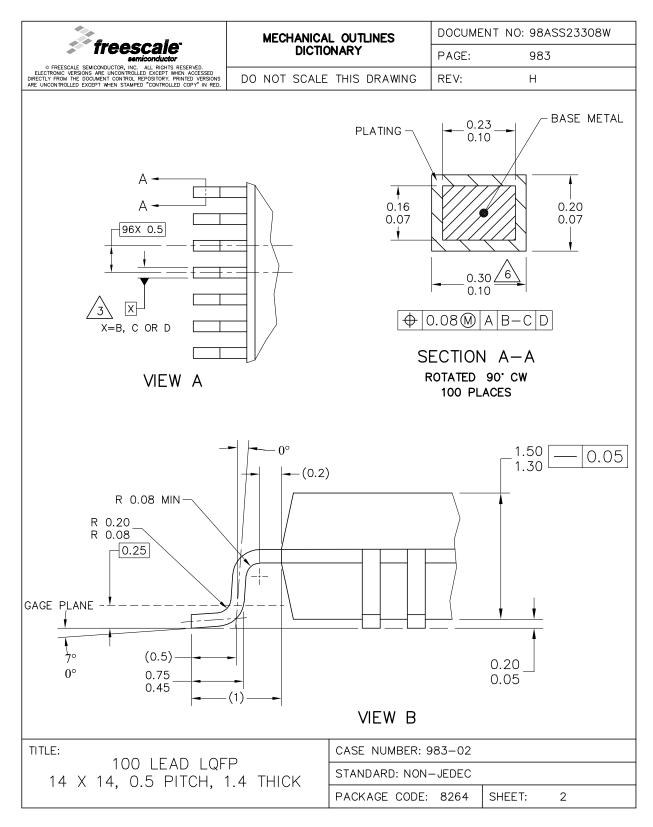

Figure 40. 100 LQFP package mechanical drawing (part 2)

MPC5604P Microcontroller Data Sheet, Rev. 8

|                                                                                                                                                                                                                                                        | MECHANICA         | MECHANICAL OUTLINES |         | DOCUMENT NO: 98ASS23308W |   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|---------|--------------------------|---|--|--|--|

| <b>Treescale</b><br>semiconductor                                                                                                                                                                                                                      | DICTIONARY        |                     | PAGE:   | 983                      |   |  |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRCTLY FROM THE DOCUMENT CONTROL. REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE      | THIS DRAWING        | REV:    | Н                        |   |  |  |  |

| NOTES:                                                                                                                                                                                                                                                 |                   |                     |         |                          |   |  |  |  |

| 1. ALL DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                  |                   |                     |         |                          |   |  |  |  |

| 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.                                                                                                                                                                                           |                   |                     |         |                          |   |  |  |  |

| 3 DATUMS B, C AND D TO BE                                                                                                                                                                                                                              | DETERMINED AT I   | DATUM PLANE H.      |         |                          |   |  |  |  |

| 4. THE TOP PACKAGE BODY SIZ<br>BY A MAXIMUM OF 0.1 MM.                                                                                                                                                                                                 | E MAY BE SMALL    | ER THAN THE BO      | ТТОМ РА | CKAGE SIZE               |   |  |  |  |

| 5. DIMENSIONS DO NOT INCLUDE<br>PROTRUSION IS 0.25 mm PE<br>SIZE DIMENSIONS INCLUDING                                                                                                                                                                  | ER SIDE. THE DIMI |                     |         |                          |   |  |  |  |

| 6. DIMENSION DOES NOT INCLUE<br>CAUSE THE LEAD WIDTH TO<br>AND AN ADJACENT LEAD SH                                                                                                                                                                     | EXCEED 0.35. MII  | NIMUM SPACE BET     |         |                          |   |  |  |  |

| 7. dimensions are determined                                                                                                                                                                                                                           | AT THE SEATING    | G PLANE, DATUM      | Α.      |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   |                     |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   | I                   |         |                          |   |  |  |  |

| 100 LEAD LQF                                                                                                                                                                                                                                           | P                 | CASE NUMBER: 9      |         |                          |   |  |  |  |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                    |                   | STANDARD: NON-JEDEC |         |                          |   |  |  |  |

|                                                                                                                                                                                                                                                        |                   | PACKAGE CODE:       | 8264    | SHEET:                   | 3 |  |  |  |

### Figure 41. 100 LQFP package mechanical drawing (part 3)

MPC5604P Microcontroller Data Sheet, Rev. 8

# 6 Document revision history

Table 42 summarizes revisions to this document.

| Revision | Date     | Substantive changes                                                                                                                                                                                                                                                                                                               |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1   | Aug 2008 | Initial release                                                                                                                                                                                                                                                                                                                   |

| Rev. 2   | Nov 2008 | Table 5:TDO and TDI pins (Port pins B[4:5] are single function pins.                                                                                                                                                                                                                                                              |

|          |          | Table 10, Table 11:         Thermal characteristics added.                                                                                                                                                                                                                                                                        |

|          |          | Table 11, Table 12:EMI testing specifications split into separate tables for Normal mode and Airbag mode;data to be added in a later revision.                                                                                                                                                                                    |

|          |          | Table 16, Table 17, Table 19, Table 20:Supply current specifications split into separate tables for Normal mode and Airbag mode;data to be added in a later revision.                                                                                                                                                             |

|          |          | <ul> <li>Table 21:</li> <li>Values for I<sub>OL</sub> and I<sub>OH</sub> (in Conditions column) changed.</li> <li>Max values for V<sub>OH_S</sub>, V<sub>OH_M</sub>, V<sub>OH_F</sub> and V<sub>OH_SYM</sub> deleted.</li> <li>V<sub>ILR</sub> max value changed.</li> <li>I<sub>PUR</sub> min and max values changed.</li> </ul> |

|          |          | Table 27:         Sensitivity value changed.         Table 30:                                                                                                                                                                                                                                                                    |

|          |          | Most values in table changed.                                                                                                                                                                                                                                                                                                     |

| Rev. 3   | Feb 2009 | <ul> <li>Description of system requirements, controller characteristics and how controller<br/>characteristics are guaranteed updated.</li> <li>Electrical parameters updated.</li> </ul>                                                                                                                                         |

|          |          | <ul> <li>EMI characteristics are now in one table; values have been updated.</li> <li>ESD characteristics are now in one table.</li> </ul>                                                                                                                                                                                        |

|          |          | • Electrical parameters are identified as either system requirements or controller characteristics. Method used to guarantee each controller characteristic is noted in table.                                                                                                                                                    |

|          |          | AC Timings: 1149.1 (JTAG) Timing, Nexus Timing, External Interrupt Timing,<br>and DSPI Timing sections deleted                                                                                                                                                                                                                    |

#### Table 42. Revision history

| Revision           | Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision<br>Rev. 8 |      | <ul> <li>Section 1.5.4, "Flash memory: Changed "Data flash memory: 32-bit ECC" to "Data flash memory: 64-bit ECC"</li> <li>Figure 42 (Commercial product code structure), replaced "C = 60 MHz, 5 V" and "D = 60 MHz, 3.3 V" with respectively "C = 40 MHz, 5 V" and "D = 40 MHz, 3.3 V"</li> <li>Table 7 (Absolute maximum ratings), updated TV<sub>DD</sub> parameter, the minimum value to 3.0 V/s and the maximum value to 0.5 V/µs</li> <li>Table 5 (Pin muxing), changed the description in the column "I/O direction" from "I/O" to "O" for the following port pins: A[10] with function B[0]</li> <li>A[11] with function A[2]</li> <li>A[12] with function A[2]</li> <li>A[13] with function B[2]</li> <li>C[7] with function A[1]</li> <li>C[10] with function A[1]</li> <li>D[0] with function B[1]</li> <li>D[10] with function A[1]</li> <li>D[11] with function B[0]</li> <li>D[13] with function B[1]</li> <li>D[14] with function B[1]</li> <li>Updated Section 3.8.1, "Voltage regulator electrical characteristics</li> </ul> |

|                    |      | Added Table 25 (I/O consumption)<br>Section 3.10, DC electrical characteristics:<br>deleted references to "oscillator margin"<br>deleted subsection "NVUSRO[OSCILLATOR_MARGIN] field description"<br>Table <u>19 (DC</u> electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)), added IPU row<br>for RESET pin<br>Table <u>21 (DC</u> electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)), added IPU row<br>for RESET pin<br>Table <u>31 (ADC conversion characteristics</u> ), added V <sub>INAN</sub> entry<br>Removed "Order codes" table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 42. Revision history (continued)