#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 852MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d4avt08adr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Introduction

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

- A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

# **1.3 Updated Signal Naming Convention**

The signal names of the i.MX 6 series of products have been standardized to better align the signal names within the family and across the documentation. Some of the benefits of these changes are as follows:

- The names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- The names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This change applies only to signal names. The original ball names have been preserved to prevent the need to change schematics, BSDL models, IBIS models, etc.

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, *IMX 6 Series Signal Name Mapping* (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

| Block<br>Mnemonic | Block Name                                  | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>96KB       | Boot ROM                                    | Internal<br>Memory               | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROMCP             | ROM Controller with Patch                   | Data Path                        | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SATA              | Serial ATA                                  | Connectivity<br>Peripherals      | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDMA              | Smart Direct Memory<br>Access               | System<br>Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast context-switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

| SJC               | System JTAG<br>Controller                   | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6Dual/6Quad SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SNVS              | Secure Non-Volatile<br>Storage              | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPDIF             | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Table 2. i.MX 6Dual/6Quad Modules List (continued)

Modules List

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| Table 2. i.MX 6Dual/6Quad Modules | List (continued) |

|-----------------------------------|------------------|

|-----------------------------------|------------------|

Modules List

| Block<br>Mnemonic | Block Name                      | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-2<br>(TZ)    | Watchdog<br>(TrustZone)         | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such a situation is<br>undesirable as it can compromise the system's security. Once the TZ<br>WDOG module is activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer times out. Upon<br>a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces<br>switching to the TZ mode. If it is still not served, the TZ WDOG asserts a<br>security violation signal to the CSU. The TZ WDOG module cannot be<br>programmed or deactivated by a normal mode Software. |

| EIM               | NOR-Flash /PSRAM<br>interface   | Connectivity<br>Peripherals | <ul> <li>The EIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTALOSC           | Crystal Oscillator<br>interface | —                           | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# 3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are defined in the i.MX 6Dual/6Quad reference manual (IMX6DQRM). Special signal consideration information is contained in the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

# 3.2 Recommended Connections for Unused Analog Interfaces

The recommended connections for unused analog interfaces can be found in the section, "Unused analog interfaces," of the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

# 4.1.10 HDMI Maximum Power Consumption

Table 13 provides HDMI PHY currents for both Active 3D Tx with LFSR15 data pattern and Power-down modes.

| Mode       | Test Conditions      | Supply   | Max Current | Unit |

|------------|----------------------|----------|-------------|------|

| Active     | Bit rate 251.75 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.1         | mA   |

|            | Bit rate 279.27 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.2         | mA   |

|            | Bit rate 742.5 Mbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 7.5         | mA   |

|            | Bit rate 1.485 Gbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 12          | mA   |

|            | Bit rate 2.275 Gbps  | HDMI_VPH | 16          | mA   |

|            |                      | HDMI_VP  | 17          | mA   |

|            | Bit rate 2.97 Gbps   | HDMI_VPH | 19          | mA   |

|            |                      | HDMI_VP  | 22          | mA   |

| Power-down | _                    | HDMI_VPH | 49          | μΑ   |

|            |                      | HDMI_VP  | 1100        | μΑ   |

| Table 13 | B. HDMI PH | Y Current Dr | ain |

|----------|------------|--------------|-----|

|----------|------------|--------------|-----|

## 4.2.3 Power Supplies Usage

- All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Group" column of Table 100, "21 x 21 mm Functional Contact Assignments," on page 149.

- When the SATA interface is not used, the SATA\_VP and SATA\_VPH supplies should be grounded. The input and output supplies for rest of the ports (SATA\_REXT, SATA\_PHY\_RX\_N, SATA\_PHY\_RX\_P, and SATA\_PHY\_TX\_N) can be left floating. It is recommended not to turn OFF the SATA\_VPH supply while the SATA\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, SATA\_VP and SATA\_VPH must remain powered.

- When the PCIE interface is not used, the PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX supplies should be grounded. The input and output supplies for rest of the ports (PCIE\_REXT, PCIE\_RX\_N, PCIE\_RX\_P, PCIE\_TX\_N, and PCIE\_TX\_P) can be left floating. It is recommended not to turn the PCIE\_VPH supply OFF while the PCIE\_VP supply is ON, as it may lead to excessive power consumption. If boundary scan test is used, PCIE\_VP, PCIE\_VPH, and PCIE\_VPTX must remain powered.

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for details on the power tree scheme recommended operation.

## NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of their input supply ripple rejection and their on die trimming. This translates into more voltage for the die producing higher operating frequencies. These regulators have three basic modes.

- Bypass. The regulation FET is switched fully on passing the external voltage, DCDC\_LOW, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

# 4.4.4 480 MHz PLL

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

### Table 17. 480 MHz PLL Electrical Parameters

## 4.4.5 MLB PLL

The MediaLB PLL is necessary in the MediaLB 6-Pin implementation to phase align the internal and external clock edges, effectively tuning out the delay of the differential clock receiver and is also responsible for generating the higher speed internal clock, when the internal-to-external clock ratio is not 1:1.

### Table 18. MLB PLL Electrical Parameters

| Parameter | Value   |

|-----------|---------|

| Lock time | <1.5 ms |

## 4.4.6 ARM PLL

### Table 19. ARM PLL Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz~1.3 GHz        |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

# 4.5 **On-Chip Oscillators**

## 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

## 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered

# 4.6 I/O DC Parameters

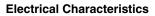

This section includes the DC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

## NOTE

The term 'OVDD' in this section refers to the associated supply rail of an input or output.

Figure 3. Circuit for Parameters Voh and Vol for I/O Cells

# 4.6.1 XTALI and RTC\_XTALI (Clock Inputs) DC Parameters

Table 21 shows the DC parameters for the clock inputs.

| Parameter                             | Symbol                | Test Conditions                                                                                                                                                           | Min                | Тур | Мах          | Unit |

|---------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------|------|

| XTALI high-level DC input voltage     | Vih                   | _                                                                                                                                                                         | 0.8 x NVCC_PLL_OUT | —   | NVCC_PLL_OUT | V    |

| XTALI low-level DC input voltage      | Vil                   | —                                                                                                                                                                         | 0                  | —   | 0.2          | V    |

| RTC_XTALI high-level DC input voltage | Vih                   |                                                                                                                                                                           | 0.8                |     | 1.1          | V    |

| RTC_XTALI low-level DC input voltage  | Vil                   |                                                                                                                                                                           | 0                  |     | 0.2          | V    |

| Input capacitance                     | C <sub>IN</sub>       | Simulated data                                                                                                                                                            | —                  | 5   | _            | pF   |

| Startup current                       |                       | Power-on startup for<br>0.15msec with a driven<br>32KHz RTC clock @<br>1.1V. This current draw<br>is present even if an<br>external clock source<br>directly drives XTALI | _                  |     | 600          | uA   |

| DC input current                      | I <sub>XTALI_DC</sub> | —                                                                                                                                                                         | —                  | —   | 2.5          | uA   |

| ID   | Parameter                            | Min <sup>1</sup>        | Max <sup>1</sup>                    | Unit |

|------|--------------------------------------|-------------------------|-------------------------------------|------|

| WE4  | Clock rise to address valid          | -0.5 × t × (k+1) - 1.25 | -0.5 × t × (k+1) + 2.25             | ns   |

| WE5  | Clock rise to address invalid        | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE6  | Clock rise to EIM_CSx_B valid        | -0.5 × t × (k+1) - 1.25 | -0.5×t×(k+1) + 2.25                 | ns   |

| WE7  | Clock rise to EIM_CSx_B invalid      | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE8  | Clock rise to EIM_WE_B valid         | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE9  | Clock rise to EIM_WE_B invalid       | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE10 | Clock rise to EIM_OE_B valid         | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE11 | Clock rise to EIM_OE_B invalid       | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE12 | Clock rise to EIM_EBx_B valid        | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE13 | Clock rise to EIM_EBx_B invalid      | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE14 | Clock rise to EIM_LBA_B valid        | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE15 | Clock rise to EIM_LBA_B invalid      | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE16 | Clock rise to output data valid      | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE17 | Clock rise to output data invalid    | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE18 | Input data setup time to clock rise  | 2.3                     | —                                   | ns   |

| WE19 | Input data hold time from clock rise | 2                       | —                                   | ns   |

| WE20 | EIM_WAIT_B setup time to clock rise  | 2                       | —                                   | ns   |

| WE21 | EIM_WAIT_B hold time from clock rise | 2                       | —                                   | ns   |

### Table 40. EIM Bus Timing Parameters (continued)

<sup>1</sup> k represents register setting BCD value. <sup>2</sup> t is clock period (1/Freq). For 104 MHz, t = 9.165 ns.

<sup>4</sup> Refer to JEDEC DDR3 SDRAM Standards for Data Setup (tDS), Hold (tDH) and Slew Rate Derating tables.

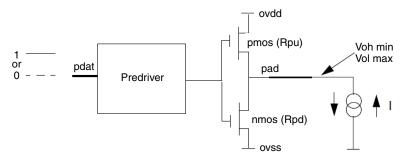

Figure 26 shows the DDR3/DDR3L read timing diagram. The timing parameters for this diagram appear in Table 44.

Figure 26. DDR3/DDR3L Read Cycle

### 4.9.4.2 LPDDR2 Parameters

### Table 44. DDR3/DDR3L Read Cycle

| ID    | Parameter <sup>1,2,3</sup>                       | Svmbol | CK = 532 MHz |     | Unit |      |

|-------|--------------------------------------------------|--------|--------------|-----|------|------|

|       |                                                  | Symbol | Min          | Max | Onic | onit |

| DDR26 | Minimum required DRAM_DATAxx valid window width. | _      | 450          | _   | ps   |      |

To receive the reported setup and hold values, the read calibration must be performed to locate the DRAM\_SDQSx\_P in the middle of DRAM\_DATAxx window.

<sup>2</sup> All measurements are in reference to Vref level.

<sup>3</sup> Measurements were completed using balanced load and a 25  $\Omega$  resistor from outputs to DRAM\_VREF.

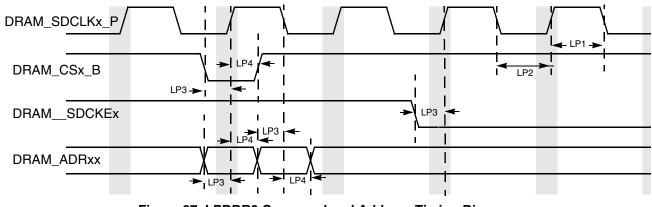

Figure 27 shows the LPDDR2 basic timing diagram. The timing parameters for this diagram appear in Table 45.

Figure 27. LPDDR2 Command and Address Timing Diagram

#### i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors, Rev. 4, 07/2015

1

**Electrical Characteristics**

| ID                                                               | ID Parameter                       |                 | Min | Max | Unit |

|------------------------------------------------------------------|------------------------------------|-----------------|-----|-----|------|

| eSDHC Input/Card Outputs SD_CMD, SD_DATAx (Reference to SDx_CLK) |                                    |                 |     |     |      |

| SD7                                                              | SD7 eSDHC Input Setup Time         |                 | 2.5 | _   | ns   |

| SD8                                                              | eSDHC Input Hold Time <sup>4</sup> | t <sub>IH</sub> | 1.5 | _   | ns   |

### Table 54. SD/eMMC4.3 Interface Timing Specification (continued)

<sup>1</sup> In low speed mode, card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

<sup>2</sup> In normal (full) speed mode for SD/SDIO card, clock frequency can be any value between 0–25 MHz. In high-speed mode, clock frequency can be any value between 0–50 MHz.

<sup>3</sup> In normal (full) speed mode for MMC card, clock frequency can be any value between 0-20 MHz. In high-speed mode, clock frequency can be any value between 0-52 MHz.

<sup>4</sup>To satisfy hold timing, the delay difference between clock input and cmd/data input must not exceed 2 ns.

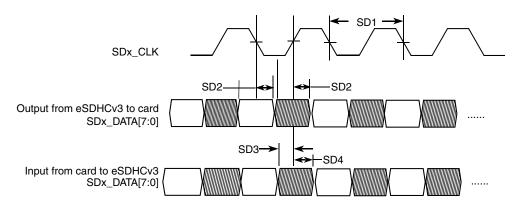

## 4.11.4.2 eMMC4.4/4.41 (Dual Data Rate) eSDHCv3 AC Timing

Figure 46 depicts the timing of eMMC4.4/4.41. Table 55 lists the eMMC4.4/4.41 timing characteristics. Be aware that only SDx\_DATAx is sampled on both edges of the clock (not applicable to SD\_CMD).

Figure 46. eMMC4.4/4.41 Timing

#### Table 55. eMMC4.4/4.41 Interface Timing Specification

| ID                                | Parameter                                                         | Symbols          | Min | Max | Unit |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------|------------------|-----|-----|------|--|--|--|--|

|                                   | Card Input Clock                                                  |                  |     |     |      |  |  |  |  |

| SD1 Clock Frequency (EMMC4.4 DDR) |                                                                   | f <sub>PP</sub>  | 0   | 52  | MHz  |  |  |  |  |

| SD1                               | Clock Frequency (SD3.0 DDR)                                       | f <sub>PP</sub>  | 0   | 50  | MHz  |  |  |  |  |

|                                   | uSDHC Output / Card Inputs SD_CMD, SD_DATAx (Reference to SD_CLK) |                  |     |     |      |  |  |  |  |

| SD2                               | SD2 uSDHC Output Delay                                            |                  | 2.5 | 7.1 | ns   |  |  |  |  |

|                                   | uSDHC Input / Card Outputs SD_CMD, SD_DATAx (Reference to SD_CLK) |                  |     |     |      |  |  |  |  |

| SD3 uSDHC Input Setup Time        |                                                                   | t <sub>ISU</sub> | 2.6 | _   | ns   |  |  |  |  |

| SD4                               | uSDHC Input Hold Time                                             | t <sub>IH</sub>  | 1.5 | _   | ns   |  |  |  |  |

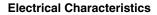

## 4.11.5.3 RGMII Signal Switching Specifications

The following timing specifications meet the requirements for RGMII interfaces for a range of transceiver devices.

| Symbol                          | Description                              |    | Max  | Unit |

|---------------------------------|------------------------------------------|----|------|------|

| T <sub>cyc</sub> <sup>2</sup>   | Clock cycle duration                     |    | 8.8  | ns   |

| T <sub>skewT</sub> <sup>3</sup> | Data to clock output skew at transmitter |    | 900  | ps   |

| T <sub>skewR</sub> <sup>3</sup> | Data to clock input skew at receiver     |    | 2.6  | ns   |

| Duty_G <sup>4</sup>             | Duty cycle for Gigabit                   |    | 55   | %    |

| Duty_T <sup>4</sup>             | Duty cycle for 10/100T                   | 40 | 60   | %    |

| Tr/Tf                           | Rise/fall time (20–80%)                  | —  | 0.75 | ns   |

### Table 62. RGMII Signal Switching Specifications<sup>1</sup>

<sup>1</sup> The timings assume the following configuration: DDR\_SEL = (11)b

DSE (drive-strength) = (111)b

$^2~$  For 10 Mbps and 100 Mbps,  $T_{cyc}$  will scale to 400 ns ±40 ns and 40 ns ±4 ns respectively.

<sup>3</sup> For all versions of RGMII prior to 2.0; This implies that PC board design will require clocks to be routed such that an additional delay of greater than 1.2 ns and less than 1.7 ns will be added to the associated clock signal. For 10/100, the max value is unspecified.

<sup>4</sup> Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domain as long as minimum duty cycle is not violated and stretching occurs for no more than three Tcyc of the lowest speed transitioned between.

Figure 53. RGMII Transmit Signal Timing Diagram Original

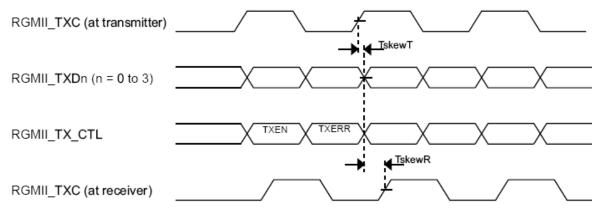

### Figure 63. TMDS Output Signals Rise and Fall Time Definition

| Symbol         | Parameter                            | Conditions                                                              | Min  | Тур | Max    | Unit |

|----------------|--------------------------------------|-------------------------------------------------------------------------|------|-----|--------|------|

|                | т                                    | MDS Drivers Specifications                                              |      |     |        |      |

| —              | Maximum serial data rate             | _                                                                       | _    | —   | 3.4    | Gbps |

| F<br>TMDSCLK   | TMDSCLK frequency                    | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz  |

| P<br>TMDSCLK   | TMDSCLK period                       | RL = 50 Ω<br>See Figure 59.                                             | 2.94 | —   | 40     | ns   |

| t<br>CDC       | TMDSCLK duty cycle                   | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 59. | 40   | 50  | 60     | %    |

| t<br>CPH       | TMDSCLK high time                    | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| t<br>CPL       | TMDSCLK low time                     | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| _              | TMDSCLK jitter <sup>1</sup>          | RL = 50 Ω                                                               | _    | —   | 0.25   | UI   |

| t<br>SK(p)     | Intra-pair (pulse) skew              | RL = 50 $\Omega$<br>See Figure 61.                                      | -    | _   | 0.15   | UI   |

| t<br>SK(pp)    | Inter-pair skew                      | RL = 50 $\Omega$<br>See Figure 62.                                      | -    | -   | 1      | UI   |

| t <sub>R</sub> | Differential output signal rise time | 20-80%<br>RL = 50 $\Omega$<br>See Figure 63.                            | 75   | —   | 0.4 UI | ps   |

### Table 64. Switching Characteristics

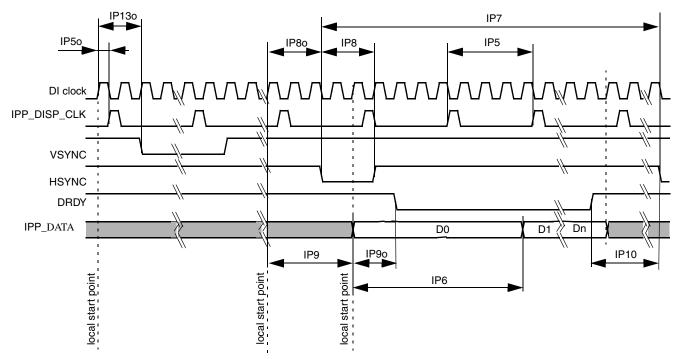

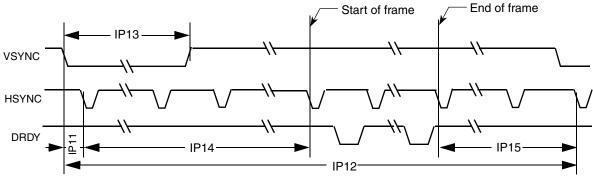

Figure 69. TFT Panels Timing Diagram—Horizontal Sync Pulse

Figure 70 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

Figure 70. TFT Panels Timing Diagram—Vertical Sync Pulse

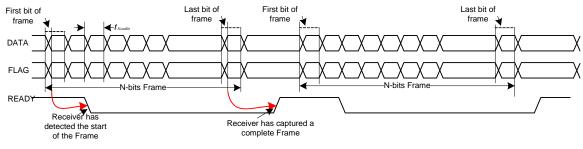

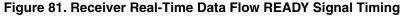

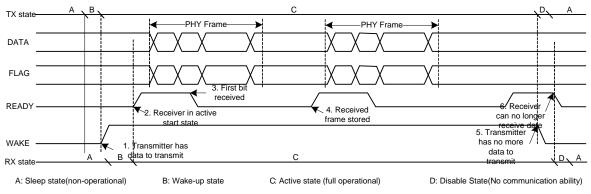

### 4.11.13.3 Receiver Real-Time Data Flow

Figure 82. Synchronized Data Flow Transmission with WAKE

## 4.11.13.5 Stream Transmission Mode Frame Transfer

## 4.11.17.1.1 SATA PHY Transmitter Characteristics

Table 81 provides specifications for SATA PHY transmitter characteristics.

| Parameters                                                               | Symbol           | Min  | Тур | Мах | Unit |

|--------------------------------------------------------------------------|------------------|------|-----|-----|------|

| Transmit common mode voltage                                             | V <sub>CTM</sub> | 0.4  | —   | 0.6 | V    |

| Transmitter pre-emphasis accuracy (measured change in de-emphasized bit) | _                | -0.5 | _   | 0.5 | dB   |

### Table 81. SATA2 PHY Transmitter Characteristics

## 4.11.17.1.2 SATA PHY Receiver Characteristics

Table 82 provides specifications for SATA PHY receiver characteristics.

| Table 82. SATA PHY Receiver | Characteristics |

|-----------------------------|-----------------|

|-----------------------------|-----------------|

| Parameters                                        | Symbol                         | Min  | Тур | Мах | Unit |

|---------------------------------------------------|--------------------------------|------|-----|-----|------|

| Minimum Rx eye height (differential peak-to-peak) | V <sub>MIN_RX_EYE_HEIGHT</sub> | 175  | _   | —   | mV   |

| Tolerance                                         | PPM                            | -400 | _   | 400 | ppm  |

## 4.11.17.2 SATA\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 191  $\Omega$  1% precision resistor on SATA\_REXT pad to ground.

Resistor calibration consists of learning which state of the internal Resistor Calibration register causes an internal, digitally trimmed calibration resistor to best match the impedance applied to the SATA\_REXT pin. The calibration register value is then supplied to all Tx and Rx termination resistors.

During the calibration process (for a few tens of microseconds), up to 0.3 mW can be dissipated in the external SATA\_REXT resistor. At other times, no power is dissipated by the SATA\_REXT resistor.

## 4.11.18 SCAN JTAG Controller (SJC) Timing Parameters

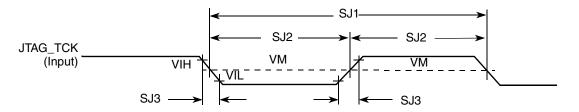

Figure 90 depicts the SJC test clock input timing. Figure 91 depicts the SJC boundary scan timing. Figure 92 depicts the SJC test access port. Figure 93 depicts the JTAG\_TRST\_B timing. Signal parameters are listed in Table 83.

Figure 90. Test Clock Input Timing Diagram

## 4.11.21.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

### 4.11.21.2.1 UART Transmitter

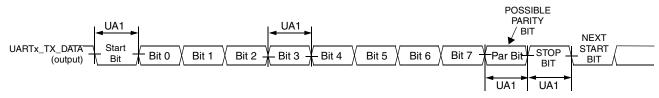

Figure 100 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 91 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 100. UART RS-232 Serial Mode Transmit Timing Diagram

### Table 91. RS-232 Serial Mode Transmit Timing Parameters

| ID  | Parameter         | Symbol            | Min                                 | Мах                                             | Unit |

|-----|-------------------|-------------------|-------------------------------------|-------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | $1/F_{baud_rate}^1 - T_{ref_clk}^2$ | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | _    |

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref\_clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

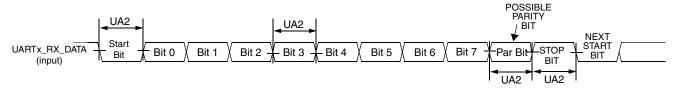

### 4.11.21.2.2 UART Receiver

Figure 101 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 92 lists serial mode receive timing characteristics.

Figure 101. UART RS-232 Serial Mode Receive Timing Diagram

Table 92.

RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Max                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> −<br>1/(16 × F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 × F <sub>baud_rate</sub> ) | _    |

The UART receiver can tolerate  $1/(16 \times F_{baud\_rate})$  tolerance in each bit. But accumulation tolerance in one frame must not exceed  $3/(16 \times F_{baud\_rate})$ .

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

#### Package Information and Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                              | Remark                                                                                                                      |  |  |

|------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| VDDHIGH_CAP      | H10, J10                                         | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)    |  |  |

| VDDHIGH_IN       | H9, J9                                           | Primary supply for the 2.5 V regulator                                                                                      |  |  |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                | Secondary supply for the VPU and<br>GPU (internal regulator output—<br>requires capacitor if internal regulator<br>is used) |  |  |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                | Secondary supply for the SoC and PU<br>(internal regulator output—requires<br>capacitor if internal regulator is used)      |  |  |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16 | Primary supply for the SoC and PU regulators                                                                                |  |  |

| VDDUSB_CAP       | F9                                               | Secondary supply for the 3 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)      |  |  |

| ZQPAD            | AE17                                             | —                                                                                                                           |  |  |

### Table 99. 21 x 21 mm Supplies Contact Assignment (continued)

Table 100 displays an alpha-sorted list of the signal assignments including power rails. The table also includes out of reset pad state.

|            | Ball | Power Group  | Ball Type | Out of Reset Condition <sup>1</sup> |                                   |              |                    |

|------------|------|--------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|

| Ball Name  |      |              |           | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |

| BOOT_MODE0 | C12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE0                    | Input        | PD (100K)          |

| BOOT_MODE1 | F12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE1                    | Input        | PD (100K)          |

| CLK1_N     | C7   | VDD_HIGH_CAP | —         | —                                   | CLK1_N                            | —            | —                  |

| CLK1_P     | D7   | VDD_HIGH_CAP | —         | —                                   | CLK1_P                            | —            | —                  |

| CLK2_N     | C5   | VDD_HIGH_CAP | —         | —                                   | CLK2_N                            | —            | —                  |

| CLK2_P     | D5   | VDD_HIGH_CAP | —         | —                                   | CLK2_P                            | —            | —                  |

| CSI_CLK0M  | F4   | NVCC_MIPI    | —         | —                                   | CSI_CLK_N                         | —            | —                  |

| CSI_CLK0P  | F3   | NVCC_MIPI    | —         | —                                   | CSI_CLK_P                         | —            | —                  |

| CSI_D0M    | E4   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_N                       | —            | —                  |

| CSI_D0P    | E3   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_P                       | —            | —                  |

| CSI_D1M    | D1   | NVCC_MIPI    | —         | —                                   | CSI_DATA1_N                       | —            | —                  |

| CSI_D1P    | D2   | NVCC_MIPI    | —         | —                                   | CSI_DATA1_P                       | —            | —                  |

| CSI_D2M    | E1   | NVCC_MIPI    | —         | —                                   | CSI_DATA2_N                       | —            | —                  |

| CSI_D2P    | E2   | NVCC_MIPI    | —         | —                                   | CSI_DATA2_P                       | —            | —                  |

| CSI_D3M    | F2   | NVCC_MIPI    | —         | —                                   | CSI_DATA3_N                       | —            | —                  |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM, Cortex, TrustZone, and NEON are registered trademarksof ARM Limited (or its subsidiaries) in the EU and/or elsewhere.

© 2012-2015 Freescale Semiconductor, Inc. All rights reserved.

Document Number: IMX6DQAEC Rev. 4 07/2015