# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d6avt10acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

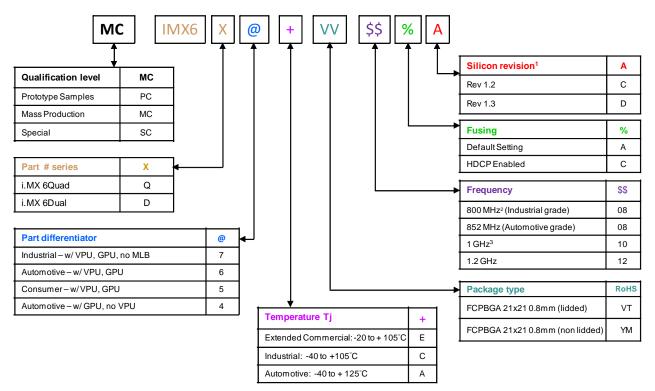

Figure 1 describes the part number nomenclature to identify the characteristics of the specific part number you have (for example, cores, frequency, temperature grade, fuse options, silicon revision). Figure 1 applies to the i.MX 6Dual/6Quad.

The two characteristics that identify which data sheet a specific part applies to are the part number series field and the temperature grade (junction) field:

- The i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors data sheet (IMX6DQAEC) covers parts listed with "A (Automotive temp)"

- The i.MX 6Dual/6Quad Applications Processors for Consumer Products data sheet (IMX6DQCEC) covers parts listed with "D (Commercial temp)" or "E (Extended Commercial temp)"

- The i.MX 6Dual/6Quad Applications Processors for Industrial Products data sheet (IMX6DQIEC) covers parts listed with "C (Industrial temp)"

Ensure that you have the right data sheet for your specific part by checking the temperature grade (junction) field and matching it to the right data sheet. If you have questions, see freescale.com/imx6series or contact your Freescale representative.

1. See the freescale.com\imx6series Web page for latest information on the available silicon revision.

2. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz.

3. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

Figure 1. Part Number Nomenclature—i.MX 6Quad and i.MX 6Dual

\_\_\_\_\_

| Block<br>Mnemonic                                              | Block Name                                    | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPU2Dv2                                                        | Graphics Processing<br>Unit-2D, ver. 2        | Multimedia<br>Peripherals        | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GPU2Dv4                                                        | Graphics Processing<br>Unit, ver. 4           | Multimedia<br>Peripherals        | The GPU2Dv4 provides hardware acceleration for 3D graphics algorithm<br>with sufficient processor power to run desktop quality interactive graphic<br>applications on displays up to HD1080 resolution. The GPU3D provide<br>OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| GPUVGv2                                                        | Vector Graphics<br>Processing Unit,<br>ver. 2 | Multimedia<br>Peripherals        | OpenVG graphics accelerator provides OpenVG 1.1 support as well as<br>other accelerations, including Real-time hardware curve tesselation of<br>lines, quadratic and cubic Bezier curves, 16x Line Anti-aliasing, and<br>various Vector Drawing functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HDMI Tx                                                        | HDMI Tx interface                             | Multimedia<br>Peripherals        | The HDMI module provides HDMI standard interface port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HSI                                                            | MIPI HSI interface                            | Connectivity<br>Peripherals      | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3 | I <sup>2</sup> C Interface                    | Connectivity<br>Peripherals      | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| IOMUXC                                                         | IOMUX Control                                 | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| IPUv3H-1<br>IPUv3H-2                                           | Image Processing<br>Unit, ver. 3H             | Multimedia<br>Peripherals        | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation.</li> <li>The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces:</li> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/DSI transmitter</li> <li>MIPI/CSI-2 receiver</li> <li>The processing includes:</li> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> |  |  |  |

| KPP                                                            | Key Pad Port                                  | Connectivity<br>Peripherals      | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Block<br>Mnemonic | Block Name                                  | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM<br>96KB       | Boot ROM                                    | Internal<br>Memory               | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ROMCP             | ROM Controller with Patch                   | Data Path                        | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SATA              | Serial ATA                                  | Connectivity<br>Peripherals      | The SATA controller and PHY is a complete mixed-signal IP solution designed to implement SATA II, 3.0 Gbps HDD connectivity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDMA              | Smart Direct Memory<br>Access               | System<br>Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast context-switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

| SJC               | System JTAG<br>Controller                   | System<br>Control<br>Peripherals | The SJC provides JTAG interface, which complies with JTAG TAP standards, to internal logic. The i.MX 6Dual/6Quad processors use JTAG port for production, testing, and system debugging. In addition, the SJC provides BSR (Boundary Scan Register) standard support, which complies with IEEE1149.1 and IEEE1149.6 standards. The JTAG port must be accessible during platform initial laboratory bring-up, for manufacturing tests and troubleshooting, as well as for software debugging by authorized entities. The i.MX 6Dual/6Quad SJC incorporates three security modes for protecting against unauthorized accesses. Modes are selected through eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SNVS              | Secure Non-Volatile<br>Storage              | Security                         | Secure Non-Volatile Storage, including Secure Real Time Clock, Security State Machine, Master Key Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPDIF             | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. It supports Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# Table 2. i.MX 6Dual/6Quad Modules List (continued)

Modules List

| Block<br>Mnemonic                              | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|------------------------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                    | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the processor to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |  |  |  |

| TEMPMON                                        | Temperature Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP module for detecting high temperature conditions. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die. Temperature distribution may not be uniformly distributed; therefore, the read out value may not be the reflection of the temperature value for the entire die.                                                                                                                                                                                                                 |  |  |  |

| TZASC                                          | Trust-Zone Address<br>Space Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                               | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 5 MHz</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                                                                                                                             |  |  |  |

| USBOH3A                                        | USB 2.0 High Speed<br>OTG and 3x HS<br>Hosts | Connectivity<br>Peripherals      | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> <li>Two identical high-speed Host modules connected to HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Table 2. i.MX 6Dual/6Quad Modules | List (continued) |

|-----------------------------------|------------------|

|-----------------------------------|------------------|

Modules List

| Block<br>Mnemonic | Block Name                      | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-2<br>(TZ)    | Watchdog<br>(TrustZone)         | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such a situation is<br>undesirable as it can compromise the system's security. Once the TZ<br>WDOG module is activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer times out. Upon<br>a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces<br>switching to the TZ mode. If it is still not served, the TZ WDOG asserts a<br>security violation signal to the CSU. The TZ WDOG module cannot be<br>programmed or deactivated by a normal mode Software. |

| EIM               | NOR-Flash /PSRAM<br>interface   | Connectivity<br>Peripherals | <ul> <li>The EIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTALOSC           | Crystal Oscillator<br>interface | —                           | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# 3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are defined in the i.MX 6Dual/6Quad reference manual (IMX6DQRM). Special signal consideration information is contained in the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

# 3.2 Recommended Connections for Unused Analog Interfaces

The recommended connections for unused analog interfaces can be found in the section, "Unused analog interfaces," of the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

| Denne Ormerka                            | O a maliti a ma                                                                                          | Maximum                                                                       | Unit                                 |    |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|----|--|

| Power Supply                             | Conditions                                                                                               | Power Virus                                                                   | ver Virus CoreMark                   |    |  |

| i.MX 6Quad:<br>VDD_ARM_IN + VDD_ARM23_IN | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 3920                                                                          | 2500                                 | mA |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 3630                                                                          | 2260                                 | mA |  |

| i.MX 6Dual: VDD_ARM_IN                   | <ul> <li>ARM frequency = 996 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2350                                                                          | 1500                                 | mA |  |

|                                          | <ul> <li>ARM frequency = 852 MHz</li> <li>ARM LDOs set to 1.3V</li> <li>T<sub>j</sub> = 125°C</li> </ul> | 2110                                                                          | 1360                                 | mA |  |

| i.MX 6Dual: or i.MX 6Quad:<br>VDD_SOC_IN | • Running 3DMark<br>• GPU frequency = 600 MHz<br>• SOC LDO set to $1.3V$<br>• $T_j = 125^{\circ}C$       | Running 3DMark     2500       GPU frequency = 600 MHz     500 LDO set to 1.3V |                                      | mA |  |

| VDD_HIGH_IN                              | -                                                                                                        | — 125 <sup>1</sup>                                                            |                                      | mA |  |

| VDD_SNVS_IN                              | 1VS_IN —                                                                                                 |                                                                               | 275 <sup>2</sup>                     |    |  |

| USB_OTG_VBUS/<br>USB_H1_VBUS (LDO 3P0)   | -                                                                                                        | 25 <sup>3</sup>                                                               |                                      | mA |  |

|                                          | Primary Interface (IO) Supplie                                                                           | es                                                                            |                                      |    |  |

| NVCC_DRAM                                | —                                                                                                        | (see no                                                                       | te <sup>4</sup> )                    |    |  |

| NVCC_ENET                                | N=10                                                                                                     | Use maximum IO equation <sup>5</sup>                                          |                                      |    |  |

| NVCC_LCD                                 | N=29                                                                                                     | Use maximum I                                                                 | Use maximum IO equation <sup>5</sup> |    |  |

| NVCC_GPIO                                | N=24                                                                                                     | 24 Use maximum IO equation <sup>5</sup>                                       |                                      |    |  |

| NVCC_CSI                                 | N=20                                                                                                     | Use maximum I                                                                 | Use maximum IO equation <sup>5</sup> |    |  |

| NVCC_EIM0                                | N=19                                                                                                     | Use maximum IO equation <sup>5</sup>                                          |                                      |    |  |

| NVCC_EIM1                                | N=14                                                                                                     | Use maximum I                                                                 | C equation <sup>5</sup>              |    |  |

| NVCC_EIM2                                | N=20                                                                                                     | Use maximum IO equation <sup>5</sup>                                          |                                      |    |  |

| NVCC_JTAG                                | N=6                                                                                                      | Use maximum IO equation <sup>5</sup>                                          |                                      |    |  |

| NVCC_RGMII                               | N=6                                                                                                      | Use maximum I                                                                 | D equation <sup>5</sup>              |    |  |

| NVCC_SD1                                 | N=6                                                                                                      | Use maximum I                                                                 | Use maximum IO equation <sup>5</sup> |    |  |

| NVCC_SD2                                 | N=6                                                                                                      | Use maximum I                                                                 | D equation <sup>5</sup>              |    |  |

| NVCC_SD3                                 | N=11                                                                                                     | Use maximum I                                                                 | D equation <sup>5</sup>              |    |  |

| NVCC_NANDF                               | N=26                                                                                                     | Use maximum I                                                                 |                                      |    |  |

| NVCC_MIPI                                | —                                                                                                        | 25.5                                                                          |                                      | mA |  |

# Table 8. Maximum Supply Currents

| Mode                                                | Test Conditions    | Supply   | Typical Current | Unit |

|-----------------------------------------------------|--------------------|----------|-----------------|------|

| P1: Transmitter idle, Rx powered                    | Single Transceiver | SATA_VP  | 0.67            | mA   |

| down, LOS disabled                                  |                    | SATA_VPH | 0.23            |      |

|                                                     | Clock Module       | SATA_VP  | 6.9             |      |

|                                                     |                    | SATA_VPH | 6.2             |      |

| P2: Powered-down state, only<br>LOS and POR enabled | Single Transceiver | SATA_VP  | 0.53            | mA   |

|                                                     |                    | SATA_VPH | 0.11            |      |

|                                                     | Clock Module       | SATA_VP  | 0.036           |      |

|                                                     |                    | SATA_VPH | 0.12            |      |

| PDDQ mode <sup>3</sup>                              | Single Transceiver | SATA_VP  | 0.13            | mA   |

|                                                     |                    | SATA_VPH | 0.012           |      |

|                                                     | Clock Module       | SATA_VP  | 0.008           | 1    |

|                                                     |                    | SATA_VPH | 0.004           | 1    |

# Table 11. SATA PHY Current Drain (continued)

<sup>1</sup> Programmed for 1.0 V peak-to-peak Tx level.

<sup>2</sup> Programmed for 0.9 V peak-to-peak Tx level with no boost or attenuation.

<sup>3</sup> LOW power non-functional.

| Table 30. DDR I/O DDR3/DDR3L Mode AC Parameters <sup>1</sup> (c | continued) |

|-----------------------------------------------------------------|------------|

|-----------------------------------------------------------------|------------|

| Parameter                                                        | Symbol           | Test Condition                 | Min | Тур | Max | Unit |

|------------------------------------------------------------------|------------------|--------------------------------|-----|-----|-----|------|

| Single output slew rate, measured between<br>Vol(ac) and Voh(ac) | tsr              | Driver impedance = $34 \Omega$ | 2.5 | _   | 5   | V/ns |

| Skew between pad rise/fall asymmetry + skew caused by SSN        | t <sub>SKD</sub> | clk = 533 MHz                  | _   | -   | 0.1 | ns   |

<sup>1</sup> Note that the JEDEC JESD79\_3C specification supersedes any specification in this document.

<sup>2</sup> Vid(ac) specifies the input differential voltage IVtr-Vcpl required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac) – Vil(ac).

<sup>3</sup> The typical value of Vix(ac) is expected to be about 0.5 × OVDD. and Vix(ac) is expected to track variation of OVDD. Vix(ac) indicates the voltage at which differential input signal must cross.

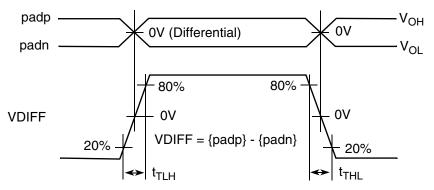

# 4.7.3 LVDS I/O AC Parameters

The differential output transition time waveform is shown in Figure 6.

Figure 6. Differential LVDS Driver Transition Time Waveform

Table 31 shows the AC parameters for LVDS I/O.

Table 31. I/O AC Parameters of LVDS Pad

| Parameter                                | Symbol           | Test Condition                 | Min | Тур | Мах  | Unit |

|------------------------------------------|------------------|--------------------------------|-----|-----|------|------|

| Differential pulse skew <sup>1</sup>     | t <sub>SKD</sub> |                                | _   |     | 0.25 |      |

| Transition Low to High Time <sup>2</sup> | t <sub>TLH</sub> | Rload = 100 Ω,<br>Cload = 2 pF | _   |     | 0.5  | ns   |

| Transition High to Low Time <sup>2</sup> | t <sub>THL</sub> |                                | _   |     | 0.5  |      |

| Operating Frequency                      | f                | —                              | _   | 600 | 800  | MHz  |

| Offset voltage imbalance                 | Vos              | _                              | _   |     | 150  | mV   |

<sup>1</sup> t<sub>SKD</sub> = I t<sub>PHLD</sub> – t<sub>PLHD</sub> I, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

<sup>2</sup> Measurement levels are 20–80% from output voltage.

# 4.7.4 MLB 6-Pin I/O AC Parameters

The differential output transition time waveform is shown in Figure 7.

| ID   | Parameter                            | Min <sup>1</sup>        | Max <sup>1</sup>                    | Unit |

|------|--------------------------------------|-------------------------|-------------------------------------|------|

| WE4  | Clock rise to address valid          | -0.5 × t × (k+1) - 1.25 | -0.5 × t × (k+1) + 2.25             | ns   |

| WE5  | Clock rise to address invalid        | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE6  | Clock rise to EIM_CSx_B valid        | -0.5 × t × (k+1) - 1.25 | -0.5×t×(k+1) + 2.25                 | ns   |

| WE7  | Clock rise to EIM_CSx_B invalid      | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE8  | Clock rise to EIM_WE_B valid         | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE9  | Clock rise to EIM_WE_B invalid       | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE10 | Clock rise to EIM_OE_B valid         | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE11 | Clock rise to EIM_OE_B invalid       | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE12 | Clock rise to EIM_EBx_B valid        | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE13 | Clock rise to EIM_EBx_B invalid      | 0.5 × t × (k+1) - 1.25  | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE14 | Clock rise to EIM_LBA_B valid        | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE15 | Clock rise to EIM_LBA_B invalid      | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE16 | Clock rise to output data valid      | -0.5 × t × (k+1) - 1.25 | $-0.5 \times t \times (k+1) + 2.25$ | ns   |

| WE17 | Clock rise to output data invalid    | 0.5×t×(k+1) - 1.25      | $0.5 \times t \times (k+1) + 2.25$  | ns   |

| WE18 | Input data setup time to clock rise  | 2.3                     | —                                   | ns   |

| WE19 | Input data hold time from clock rise | 2                       | —                                   | ns   |

| WE20 | EIM_WAIT_B setup time to clock rise  | 2                       | —                                   | ns   |

| WE21 | EIM_WAIT_B hold time from clock rise | 2                       | —                                   | ns   |

# Table 40. EIM Bus Timing Parameters (continued)

<sup>1</sup> k represents register setting BCD value.

<sup>2</sup> t is clock period (1/Freq). For 104 MHz, t = 9.165 ns.

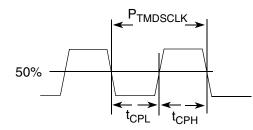

Figure 59. TMDS Clock Signal Definitions

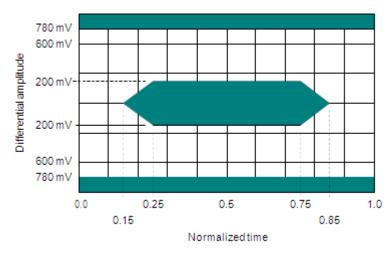

Figure 60. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

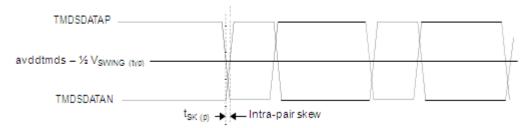

Figure 61. Intra-Pair Skew Definition

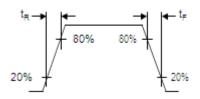

## Figure 63. TMDS Output Signals Rise and Fall Time Definition

| Symbol         | Parameter                            | Conditions                                                              | Min  | Тур | Max    | Unit |

|----------------|--------------------------------------|-------------------------------------------------------------------------|------|-----|--------|------|

|                | T                                    | MDS Drivers Specifications                                              |      |     |        |      |

|                | Maximum serial data rate             | —                                                                       | —    | —   | 3.4    | Gbps |

| F<br>TMDSCLK   | TMDSCLK frequency                    | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz  |

| P<br>TMDSCLK   | TMDSCLK period                       | RL = 50 $\Omega$<br>See Figure 59.                                      | 2.94 | _   | 40     | ns   |

| t<br>CDC       | TMDSCLK duty cycle                   | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 59. | 40   | 50  | 60     | %    |

| t<br>CPH       | TMDSCLK high time                    | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| t<br>CPL       | TMDSCLK low time                     | RL = 50 Ω<br>See Figure 59.                                             | 4    | 5   | 6      | UI   |

| _              | TMDSCLK jitter <sup>1</sup>          | RL = 50 Ω                                                               | _    | —   | 0.25   | UI   |

| t<br>SK(p)     | Intra-pair (pulse) skew              | RL = 50 $\Omega$<br>See Figure 61.                                      | -    | _   | 0.15   | UI   |

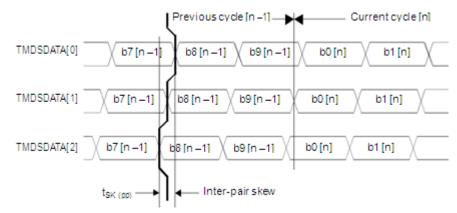

| t<br>SK(pp)    | Inter-pair skew                      | RL = 50 Ω<br>See Figure 62.                                             | -    | —   | 1      | UI   |

| t <sub>R</sub> | Differential output signal rise time | 20–80%<br>RL = 50 $\Omega$<br>See Figure 63.                            | 75   | —   | 0.4 UI | ps   |

#### Table 64. Switching Characteristics

# 4.11.10.3 Electrical Characteristics

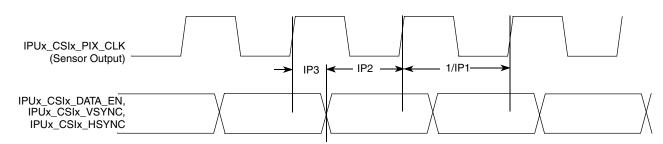

Figure 67 depicts the sensor interface timing. IPU2\_CSIx\_PIX\_CLK signal described here is not generated by the IPU. Table 67 lists the sensor interface timing characteristics.

Figure 67. Sensor Interface Timing Diagram

## Table 67. Sensor Interface Timing Characteristics

| ID  | Parameter                             | Symbol | Min  | Мах | Unit |

|-----|---------------------------------------|--------|------|-----|------|

| IP1 | Sensor output (pixel) clock frequency | Fpck   | 0.01 | 180 | MHz  |

| IP2 | Data and control setup time           | Tsu    | 2    | _   | ns   |

| IP3 | Data and control holdup time          | Thd    | 1    | _   | ns   |

# 4.11.10.4 IPU Display Interface Signal Mapping

The IPU supports a number of display output video formats. Table 68 defines the mapping of the Display Interface Pins used during various supported video interface formats.

| i.MX 6Dual/6Quad        |                             |               |               | LCD           |                             |                 |                 |                        |

|-------------------------|-----------------------------|---------------|---------------|---------------|-----------------------------|-----------------|-----------------|------------------------|

|                         | RGB,                        | R             | GB/TV         | Signal A      | Allocation                  | (Examp          | ole)            | Comment <sup>1,2</sup> |

| Port Name<br>(x = 0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb | 20-bit<br>YCrCb |                        |

| IPUx_DISPx_DAT00        | DAT[0]                      | B[0]          | B[0]          | B[0]          | Y/C[0]                      | C[0]            | C[0]            | _                      |

| IPUx_DISPx_DAT01        | DAT[1]                      | B[1]          | B[1]          | B[1]          | Y/C[1]                      | C[1]            | C[1]            | _                      |

| IPUx_DISPx_DAT02        | DAT[2]                      | B[2]          | B[2]          | B[2]          | Y/C[2]                      | C[2]            | C[2]            | —                      |

| IPUx_DISPx_DAT03        | DAT[3]                      | B[3]          | B[3]          | B[3]          | Y/C[3]                      | C[3]            | C[3]            | _                      |

| IPUx_DISPx_DAT04        | DAT[4]                      | B[4]          | B[4]          | B[4]          | Y/C[4]                      | C[4]            | C[4]            | _                      |

| IPUx_DISPx_DAT05        | DAT[5]                      | G[0]          | B[5]          | B[5]          | Y/C[5]                      | C[5]            | C[5]            | _                      |

| IPUx_DISPx_DAT06        | DAT[6]                      | G[1]          | G[0]          | B[6]          | Y/C[6]                      | C[6]            | C[6]            | _                      |

## Table 68. Video Signal Cross-Reference

| i.MX 6Dual/6Quad        |                                         |               |               | LCD           |                             |                                  |                                  |                                  |

|-------------------------|-----------------------------------------|---------------|---------------|---------------|-----------------------------|----------------------------------|----------------------------------|----------------------------------|

|                         | RGB, RGB/TV Signal Allocation (Example) |               |               |               | ocation (Example)           |                                  | Comment <sup>1,2</sup>           |                                  |

| Port Name<br>(x = 0, 1) | Signal<br>Name<br>(General)             | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb                  | 20-bit<br>YCrCb                  |                                  |

| IPUx_DISPx_DAT07        | DAT[7]                                  | G[2]          | G[1]          | B[7]          | Y/C[7]                      | C[7]                             | C[7]                             | _                                |

| IPUx_DISPx_DAT08        | DAT[8]                                  | G[3]          | G[2]          | G[0]          | —                           | Y[0]                             | C[8]                             | _                                |

| IPUx_DISPx_DAT09        | DAT[9]                                  | G[4]          | G[3]          | G[1]          |                             | Y[1]                             | C[9]                             | _                                |

| IPUx_DISPx_DAT10        | DAT[10]                                 | G[5]          | G[4]          | G[2]          | _                           | Y[2]                             | Y[0]                             | _                                |

| IPUx_DISPx_DAT11        | DAT[11]                                 | R[0]          | G[5]          | G[3]          |                             | Y[3]                             | Y[1]                             | _                                |

| IPUx_DISPx_DAT12        | DAT[12]                                 | R[1]          | R[0]          | G[4]          |                             | Y[4]                             | Y[2]                             | —                                |

| IPUx_DISPx_DAT13        | DAT[13]                                 | R[2]          | R[1]          | G[5]          |                             | Y[5]                             | Y[3]                             |                                  |

| IPUx_DISPx_DAT14        | DAT[14]                                 | R[3]          | R[2]          | G[6]          |                             | Y[6]                             | Y[4]                             | _                                |

| IPUx_DISPx_DAT15        | DAT[15]                                 | R[4]          | R[3]          | G[7]          |                             | Y[7]                             | Y[5]                             | _                                |

| IPUx_DISPx_DAT16        | DAT[16]                                 | —             | R[4]          | R[0]          |                             | _                                | Y[6]                             | _                                |

| IPUx_DISPx_DAT17        | DAT[17]                                 | —             | R[5]          | R[1]          |                             | _                                | Y[7]                             | _                                |

| IPUx_DISPx_DAT18        | DAT[18]                                 |               |               | R[2]          |                             |                                  | Y[8]                             | _                                |

| IPUx_DISPx_DAT19        | DAT[19]                                 | —             | —             | R[3]          |                             | _                                | Y[9]                             | _                                |

| IPUx_DISPx_DAT20        | DAT[20]                                 |               |               | R[4]          |                             |                                  |                                  | _                                |

| IPUx_DISPx_DAT21        | DAT[21]                                 | —             | —             | R[5]          |                             |                                  |                                  | _                                |

| IPUx_DISPx_DAT22        | DAT[22]                                 | —             | —             | R[6]          |                             | _                                | —                                | _                                |

| IPUx_DISPx_DAT23        | DAT[23]                                 | —             | —             | R[7]          |                             | _                                | —                                | _                                |

| IPUx_DIx_DISP_CLK       |                                         | PixCLK        |               |               |                             |                                  | _                                |                                  |

| IPUx_DIx_PIN01          |                                         |               |               |               |                             | May be required for anti-tearing |                                  |                                  |

| IPUx_DIx_PIN02          |                                         | HSYNC         |               |               |                             |                                  | _                                |                                  |

| IPUx_DIx_PIN03          |                                         | VSYNC         |               |               |                             |                                  | VSYNC out                        |                                  |

| IPUx_DIx_PIN04          |                                         |               |               |               |                             |                                  | Additional frame/row synchronous |                                  |

| IPUx_DIx_PIN05          |                                         |               |               |               |                             |                                  |                                  | signals with programmable timing |

| IPUx_DIx_PIN06          | 1                                       |               |               |               |                             |                                  |                                  | 1                                |

| IPUx_DIx_PIN07          |                                         |               |               | _             |                             |                                  |                                  | 1                                |

| IPUx_DIx_PIN08          |                                         |               |               | _             |                             |                                  |                                  | 1                                |

# Table 68. Video Signal Cross-Reference (continued)

| Parameter                                                                               | Symbol  | Timing Para | Unit                |    |

|-----------------------------------------------------------------------------------------|---------|-------------|---------------------|----|

| Falanielei                                                                              | Symbol  | Min         | Max                 |    |

| SPDIF_IN Skew: asynchronous inputs, no specs apply                                      | _       | —           | 0.7                 | ns |

| SPDIF_OUT output (Load = 50pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         |             | 1.5<br>24.2<br>31.3 | ns |

| SPDIF_OUT output (Load = 30pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         |             | 1.5<br>13.6<br>18.0 | ns |

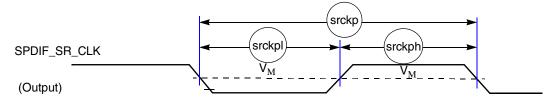

| Modulating Rx clock (SPDIF_SR_CLK) period                                               | srckp   | 40.0        |                     | ns |

| SPDIF_SR_CLK high period                                                                | srckph  | 16.0        |                     | ns |

| SPDIF_SR_CLK low period                                                                 | srckpl  | 16.0        |                     | ns |

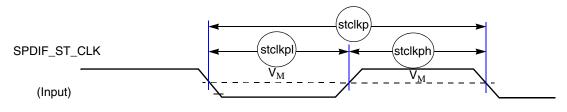

| Modulating Tx clock (SPDIF_ST_CLK) period                                               | stclkp  | 40.0        | —                   | ns |

| SPDIF_ST_CLK high period                                                                | stclkph | 16.0        | _                   | ns |

| SPDIF_ST_CLK low period                                                                 | stclkpl | 16.0        | —                   | ns |

# Table 84. SPDIF Timing Parameters

# Figure 94. SPDIF\_SR\_CLK Timing Diagram

Figure 95. SPDIF\_ST\_CLK Timing Diagram

| ID   | Parameter                                      | Min  | Max  | Unit |  |  |  |  |

|------|------------------------------------------------|------|------|------|--|--|--|--|

|      | External Clock Operation                       |      |      |      |  |  |  |  |

| SS22 | AUDx_TXC/AUDx_RXC clock period                 | 81.4 | —    | ns   |  |  |  |  |

| SS23 | AUDx_TXC/AUDx_RXC clock high period            | 36   | —    | ns   |  |  |  |  |

| SS24 | AUDx_TXC/AUDx_RXC clock rise time              | _    | 6.0  | ns   |  |  |  |  |

| SS25 | AUDx_TXC/AUDx_RXC clock low period             | 36   | —    | ns   |  |  |  |  |

| SS26 | AUDx_TXC/AUDx_RXC clock fall time              |      | 6.0  | ns   |  |  |  |  |

| SS28 | AUDx_RXC high to AUDx_TXFS (bl) high           | -10  | 15.0 | ns   |  |  |  |  |

| SS30 | AUDx_RXC high to AUDx_TXFS (bl) low            | 10   | —    | ns   |  |  |  |  |

| SS32 | AUDx_RXC high to AUDx_TXFS (wl) high           | -10  | 15.0 | ns   |  |  |  |  |

| SS34 | AUDx_RXC high to AUDx_TXFS (wl) low            | 10   | —    | ns   |  |  |  |  |

| SS35 | AUDx_TXC/AUDx_RXC External AUDx_TXFS rise time |      | 6.0  | ns   |  |  |  |  |

| SS36 | AUDx_TXC/AUDx_RXC External AUDx_TXFS fall time | —    | 6.0  | ns   |  |  |  |  |

| SS40 | AUDx_RXD setup time before AUDx_RXC low        | 10   | —    | ns   |  |  |  |  |

| SS41 | AUDx_RXD hold time after AUDx_RXC low          | 2    | —    | ns   |  |  |  |  |

#### Table 89. SSI Receiver Timing with External Clock

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- AUDx\_TXC and AUDx\_RXC refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

# 6.2.2 21 x 21 mm Ground, Power, Sense, and Reference Contact Assignments

Table 99 shows the device connection list for ground, power, sense, and reference contact signals.

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Remark                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| CSI_REXT         | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                           |

| DRAM_VREF        | AC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                           |

| DSI_REXT         | G4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                           |

| FA_ANA           | A5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                           |

| GND              | <ul> <li>A13, A25, A4, A8, AA10, AA13, AA16, AA19, AA22, AD4, D3,</li> <li>F8, J15, L10, M15, P15, T15, U8, W17, AA7, AD7, D6, G10,</li> <li>J18, L12, M18, P18, T17, V19, W18, AB24, AE1, D8, G19, J2,</li> <li>L15, M8, P8, T19, V8, W19, AB3, AE25, E5, G3, J8, L18, N10,</li> <li>R12, T8, W10, W3, AD10, B4, E6, H12, K10, L2, N15, R15,</li> <li>U11, W11, W7, AD13, C1, E7, H15, K12, L5, N18, R17, U12,</li> <li>W12, W8, AD16, C10, F5, H18, K15, L8, N8, R8, U15, W13,</li> <li>W9, AD19, C4, F6, H8, K18, M10, P10, T11, U17, W15, Y24,</li> <li>AD22, C6, F7, J12, K8, M12, P12, T12, U19, W16, Y5</li> </ul> |                                                                                                                                             |

| GPANAIO          | C8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                           |

| HDMI_DDCCEC      | K2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog ground reference for the Hot<br>Plug detect signal                                                                                   |

| HDMI_REF         | J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                           |