# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d6avt10ad                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Introduction

- Displays—Total five interfaces available. Total raw pixel rate of all interfaces is up to 450 Mpixels/sec, 24 bpp. Up to four interfaces may be active in parallel.

- One Parallel 24-bit display port, up to 225 Mpixels/sec (for example, WUXGA at 60 Hz or dual HD1080 and WXGA at 60 Hz)

- LVDS serial ports—One port up to 165 Mpixels/sec or two ports up to 85 MP/sec (for example, WUXGA at 60 Hz) each

- HDMI 1.4 port

- MIPI/DSI, two lanes at 1 Gbps

- Camera sensors:

- Parallel Camera port (up to 20 bit and up to 240 MHz peak)

- MIPI CSI-2 serial camera port, supporting up to 1000 Mbps/lane in 1/2/3-lane mode and up to 800 Mbps/lane in 4-lane mode. The CSI-2 Receiver core can manage one clock lane and up to four data lanes. Each i.MX 6Dual/6Quad processor has four lanes.

- Expansion cards:

- Four MMC/SD/SDIO card ports all supporting:

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One High Speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB PHY

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed PHY

- Two HS hosts with integrated HS-IC USB (High Speed Inter-Chip USB) PHY

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260kHz in I2S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while others four supports 4-wire. This is due to the SoC IOMUX limitation, since all UART IPs are identical.

- Five eCSPI (Enhanced CSPI)

- Three I2C, supporting 400 kbps

#### Introduction

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (150 Mbps) with the option of DTCP cipher accelerator

The i.MX 6Dual/6Quad processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use Software State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Dual/6Quad processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Dual/6Quad processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H (2 IPUs)

- GPU3Dv4—3D Graphics Processing Unit (OpenGL ES 2.0) version 4

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- GPUVG—OpenVG 1.1 Graphics Processing Unit

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing 16 KB secure RAM and True and Pseudo Random Number Generator (NIST certified)

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Dual/6Quad errata document (IMX6DQCE).

# 3 Modules List

The i.MX 6Dual/6Quad processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block<br>Mnemonic | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 512x8 Fuse<br>Box | Electrical Fuse Array                                                               | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels,<br>Security Keys, and many other system parameters.<br>The i.MX 6Dual/6Quad processors consist of 512x8-bit fuse box<br>accessible through OCOTP_CTRL interface.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| APBH-DMA          | NAND Flash and<br>BCH ECC DMA<br>Controller                                         | System<br>Control<br>Peripherals        | DMA controller used for GPMI2 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ARM               | ARM Platform                                                                        | ARM                                     | The ARM Cortex-A9 platform consists of 4x (four) Cortex-A9 cores<br>version r2p10 and associated sub-blocks, including Level 2 Cache<br>Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller),<br>private timers, Watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                                                          |  |  |  |

| ASRC              | Asynchronous<br>Sample Rate<br>Converter                                            | Multimedia<br>Peripherals               | The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversion of up to 10 channels of about -120dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs.                                                                                                                                               |  |  |  |

| AUDMUX            | Digital Audio Mux                                                                   | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example,<br>SSI1, SSI2, and SSI3) and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical functionality and<br>programming models. A desired connectivity is achieved by configuring<br>two or more AUDMUX ports.                                                                                                                                                                                    |  |  |  |

| BCH40             | Binary-BCH ECC<br>Processor                                                         | System<br>Control<br>Peripherals        | The BCH40 module provides up to 40-bit ECC encryption/decryption for NAND Flash controller (GPMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CAAM              | Cryptographic<br>Accelerator and<br>Assurance Module                                | Security                                | CAAM is a cryptographic accelerator and assurance module. CAAM<br>implements several encryption and hashing functions, a run-time integrity<br>checker, and a Pseudo Random Number Generator (PRNG). The pseudo<br>random number generator is certified by Cryptographic Algorithm<br>Validation Program (CAVP) of National Institute of Standards and<br>Technology (NIST). Its DRBG validation number is 94 and its SHS<br>validation number is 1455.<br>CAAM also implements a Secure Memory mechanism. In i.MX<br>6Dual/6Quad processors, the security memory provided is 16 KB. |  |  |  |

| CCM<br>GPC<br>SRC | Clock Control<br>Module, General<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Table 2. | i.MX | 6Dual/6Quad | <b>Modules List</b> |

|----------|------|-------------|---------------------|

|----------|------|-------------|---------------------|

\_\_\_\_\_

| Block<br>Mnemonic                         | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------------------------------------------|--------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CSI                                       | MIPI CSI-2 Interface                 | Multimedia<br>Peripherals        | The CSI IP provides MIPI CSI-2 standard camera interface port. The CSI-2 interface supports up to 1 Gbps for up to 3 data lanes and up to Mbps for 4 data lanes.                                                                                                                                                                                                                                                |  |  |  |

| CSU                                       | Central Security Unit                | Security                         | The Central Security Unit (CSU) is responsible for setting comprehensive security policy within the i.MX 6Dual/6Quad platform. The Security Control Registers (SCR) of the CSU are set during boot time by the HAB and are locked to prevent further writing.                                                                                                                                                   |  |  |  |

| CTI-0<br>CTI-1<br>CTI-2<br>CTI-3<br>CTI-4 | Cross Trigger<br>Interfaces          | Debug / Trace                    | Cross Trigger Interfaces allows cross-triggering based on inputs from masters attached to CTIs. The CTI module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                      |  |  |  |

| СТМ                                       | Cross Trigger Matrix                 | Debug / Trace                    | Cross Trigger Matrix IP is used to route triggering events between CTIs.<br>The CTM module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                                          |  |  |  |

| DAP                                       | Debug Access Port                    | System<br>Control<br>Peripherals | <ul> <li>The DAP provides real-time access for the debugger without halting the core to:</li> <li>System memory and peripheral registers</li> <li>All debug configuration registers</li> <li>The DAP also provides debugger access to JTAG scan chains. The DAP module is internal to the Cortex-A9 Core Platform.</li> </ul>                                                                                   |  |  |  |

| DCIC-0<br>DCIC-1                          | Display Content<br>Integrity Checker | Automotive IP                    | The DCIC provides integrity check on portion(s) of the display. Each i.MX 6Dual/6Quad processor has two such modules, one for each IPU.                                                                                                                                                                                                                                                                         |  |  |  |

| DSI                                       | MIPI DSI interface                   | Multimedia<br>Peripherals        | The MIPI DSI IP provides DSI standard display port interface. The DSI interface support 80 Mbps to 1 Gbps speed per data lane.                                                                                                                                                                                                                                                                                  |  |  |  |

| DTCP                                      | DTCP                                 | MM                               | Provides encryption function according to Digital Transmission Content<br>Protection standard for traffic over MLB150.                                                                                                                                                                                                                                                                                          |  |  |  |

| eCSPI1-5                                  | Configurable SPI                     | Connectivity<br>Peripherals      | Full-duplex enhanced Synchronous Serial Interface. It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.                                                                                                                                                                                                                                                         |  |  |  |

| ENET                                      | Ethernet Controller                  | Connectivity<br>Peripherals      | The Ethernet Media Access Controller (MAC) is designed to support 10/100/1000 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The i.MX 6Dual/6Quad processors also consist of hardware assist for IEEE 1588 standard. For details, see the ENET chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM). |  |  |  |

|                                           |                                      |                                  | to 470 Mbps (total for Tx and Rx) due to internal bus throughput<br>limitations. The actual measured performance in optimized environment<br>is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX<br>6Dual/6Quad errata document (IMX6DQCE).                                                                                                                                                   |  |  |  |

| Table 2. i.MX 6Dual/6Quad Modules List ( | continued) |

|------------------------------------------|------------|

|------------------------------------------|------------|

\_\_\_\_\_

| Block<br>Mnemonic                                              | Block Name                                    | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPU2Dv2                                                        | Graphics Processing<br>Unit-2D, ver. 2        | Multimedia<br>Peripherals        | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GPU2Dv4                                                        | Graphics Processing<br>Unit, ver. 4           | Multimedia<br>Peripherals        | The GPU2Dv4 provides hardware acceleration for 3D graphics algorithm<br>with sufficient processor power to run desktop quality interactive graph<br>applications on displays up to HD1080 resolution. The GPU3D provide<br>OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| GPUVGv2                                                        | Vector Graphics<br>Processing Unit,<br>ver. 2 | Multimedia<br>Peripherals        | OpenVG graphics accelerator provides OpenVG 1.1 support as well as<br>other accelerations, including Real-time hardware curve tesselation of<br>lines, quadratic and cubic Bezier curves, 16x Line Anti-aliasing, and<br>various Vector Drawing functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HDMI Tx                                                        | HDMI Tx interface                             | Multimedia<br>Peripherals        | The HDMI module provides HDMI standard interface port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| HSI                                                            | MIPI HSI interface                            | Connectivity<br>Peripherals      | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3 | I <sup>2</sup> C Interface                    | Connectivity<br>Peripherals      | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| IOMUXC                                                         | IOMUX Control                                 | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| IPUv3H-1<br>IPUv3H-2                                           | Image Processing<br>Unit, ver. 3H             | Multimedia<br>Peripherals        | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation.</li> <li>The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces:</li> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/DSI transmitter</li> <li>MIPI/CSI-2 receiver</li> <li>The processing includes:</li> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> |  |  |  |

| KPP                                                            | Key Pad Port                                  | Connectivity<br>Peripherals      | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

## 4.1.3 Operating Ranges

Table 6 provides the operating ranges of the i.MX 6Dual/6Quad processors.

| Parameter<br>Description                          | Symbol                                  | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment <sup>2</sup>                                                                                                                                                                           |

|---------------------------------------------------|-----------------------------------------|----------------------|------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode:<br>LDO enabled                          | VDD_ARM_IN<br>VDD_ARM23_IN <sup>3</sup> | 1.35 <sup>4</sup>    | _    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 1.225 V minimum for operation up to 852 MHz or 996 MHz (depending on the device speed grade).                                              |

|                                                   |                                         | 1.275 <sup>4</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 1.150 V minimum for operation up to 792 MHz.                                                                                               |

|                                                   |                                         | 1.05 <sup>4</sup>    | —    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 0.925 V minimum for operation up to 396 MHz.                                                                                               |

|                                                   | VDD_SOC_IN <sup>6</sup>                 | 1.350 <sup>4</sup>   | _    | 1.5              | V    | 264 MHz < VPU $\leq$ 352 MHz; VDDSOC and VDDPU LDO outputs (VDD_SOC_CAP and VDD_PU_CAP) require 1.225 V minimum.                                                                               |

|                                                   |                                         | 1.275 <sup>4,7</sup> | —    | 1.5              | V    | VPU $\leq$ 264 MHz; VDDSOC and VDDPU LDO outputs (VDD_SOC_CAP and VDD_PU_CAP) require 1.15 V minimum.                                                                                          |

| Run mode:<br>LDO bypassed <sup>8</sup>            | VDD_ARM_IN<br>VDD_ARM23_IN <sup>3</sup> | 1.225                | —    | 1.3              | V    | LDO bypassed for operation up to 852 MHz or<br>996 MHz (depending on the device speed<br>grade).                                                                                               |

|                                                   |                                         | 1.150                | -    | 1.3              | V    | LDO bypassed for operation up to 792 MHz.                                                                                                                                                      |

|                                                   |                                         | 0.925                | _    | 1.3              | V    | LDO bypassed for operation up to 396 MHz.                                                                                                                                                      |

|                                                   | VDD_SOC_IN <sup>6</sup>                 | 1.225                | —    | 1.3              | V    | 264 MHz < VPU ≤ 352 MHz                                                                                                                                                                        |

|                                                   |                                         | 1.15                 | _    | 1.3              | V    | VPU ≤ 264 MHz                                                                                                                                                                                  |

| Standby/DSM mode                                  | VDD_ARM_IN<br>VDD_ARM23_IN <sup>3</sup> | 0.9                  | -    | 1.3              | V    | See Table 9, "Stop Mode Current and Power Consumption," on page 26.                                                                                                                            |

|                                                   | VDD_SOC_IN                              | 0.9                  | _    | 1.3              | V    |                                                                                                                                                                                                |

| VDD_HIGH internal<br>regulator                    | VDD_HIGH_IN <sup>9</sup>                | 2.7                  | —    | 3.3              | V    | Must match the range of voltages that the rechargeable backup battery supports.                                                                                                                |

| Backup battery supply range                       | VDD_SNVS_IN <sup>9</sup>                | 2.8                  | —    | 3.3              | V    | Should be supplied from the same supply as VDD_HIGH_IN, if the system does not require keeping real time and other data on OFF state.                                                          |

| USB supply voltages                               | USB_OTG_VBUS                            | 4.4                  | —    | 5.25             | V    | —                                                                                                                                                                                              |

|                                                   | USB_H1_VBUS                             | 4.4                  | _    | 5.25             | V    | -                                                                                                                                                                                              |

| DDR I/O supply                                    | NVCC_DRAM                               | 1.14                 | 1.2  | 1.3              | V    | LPDDR2                                                                                                                                                                                         |

|                                                   |                                         | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                                                           |

|                                                   |                                         | 1.283                | 1.35 | 1.45             | V    | DDR3_L                                                                                                                                                                                         |

| Supply for RGMII I/O<br>power group <sup>10</sup> | NVCC_RGMII                              | 1.15                 | _    | 2.625            | V    | <ul> <li>1.15 V – 1.30 V in HSIC 1.2 V mode</li> <li>1.43 V – 1.58 V in RGMII 1.5 V mode</li> <li>1.70 V – 1.90 V in RGMII 1.8 V mode</li> <li>2.25 V – 2.625 V in RGMII 2.5 V mode</li> </ul> |

## Table 6. Operating Ranges

| Parameter<br>Description    | Symbol                                                                                                                                                                      | Min   | Тур                 | Max <sup>1</sup> | Unit | Comment <sup>2</sup>                                                                                                                                                                                                              |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO supplies <sup>10</sup> | NVCC_CSI,<br>NVCC_EIM0,<br>NVCC_EIM1,<br>NVCC_EIM2,<br>NVCC_ENET,<br>NVCC_GPI0,<br>NVCC_GPI0,<br>NVCC_LCD,<br>NVCC_LCD,<br>NVCC_SD1,<br>NVCC_SD2,<br>NVCC_SD3,<br>NVCC_JTAG | 1.65  | 1.8,<br>2.8,<br>3.3 | 3.6              | V    | Isolation between the NVCC_EIMx and<br>NVCC_SDx different supplies allow them to<br>operate at different voltages within the specified<br>range.<br>Example: NVCC_EIM1 can operate at 1.8 V<br>while NVCC_EIM2 operates at 3.3 V. |

|                             | NVCC_LVDS_2P5 <sup>11</sup><br>NVCC_MIPI                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    |                                                                                                                                                                                                                                   |

| HDMI supply voltages        | HDMI_VP                                                                                                                                                                     | 0.99  | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | HDMI_VPH                                                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

| PCIe supply voltages        | PCIE_VP                                                                                                                                                                     | 1.023 | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | PCIE_VPH                                                                                                                                                                    | 2.325 | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

|                             | PCIE_VPTX                                                                                                                                                                   | 1.023 | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

| SATA Supply voltages        | SATA_VP                                                                                                                                                                     | 0.99  | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | SATA_VPH                                                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

| Junction temperature        | TJ                                                                                                                                                                          | -40   | 95                  | 125              | °C   | See <i>i.MX</i> 6Dual/6Quad Product Lifetime Usage<br>Estimates Application Note, AN4724, for<br>information on product lifetime (power-on<br>years) for this processor.                                                          |

#### Table 6. Operating Ranges (continued)

Applying the maximum voltage results in maximum power consumption and heat generation. Freescale recommends a voltage set point = (Vmin + the supply tolerance). This results in an optimized power/speed ratio.

<sup>2</sup> See the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG) for bypass capacitors requirements for each of the \*\_CAP supply outputs.

- <sup>3</sup> For Quad core system, connect to VDD\_ARM\_IN. For Dual core system, may be shorted to GND together with VDD\_ARM23\_CAP to reduce leakage.

- <sup>4</sup> VDD\_ARM\_IN and VDD\_SOC\_IN must be at least 125 mV higher than the LDO Output Set Point for correct voltage regulation.

- <sup>5</sup> VDD\_ARM\_CAP must not exceed VDD\_CACHE\_CAP by more than +50 mV. VDD\_CACHE\_CAP must not exceed VDD\_ARM\_CAP by more than 200 mV.

- <sup>6</sup> VDD\_SOC\_CAP and VDD\_PU\_CAP must be equal.

- <sup>7</sup> In LDO enabled mode, the internal LDO output set points must be configured such that the:

VDD\_ARM LDO output set point does not exceed the VDD\_SOC LDO output set point by more than 100 mV.

VDD\_SOC LDO output set point is equal to the VDD\_PU LDO output set point.

The VDD\_ARM LDO output set point can be lower than the VDD\_SOC LDO output set point, however, the minimum output set points shown in this table must be maintained.

- <sup>8</sup> In LDO bypassed mode, the external power supply must ensure that VDD\_ARM\_IN does not exceed VDD\_SOC\_IN by more than 100 mV. The VDD\_ARM\_IN supply voltage can be lower than the VDD\_SOC\_IN supply voltage. The minimum voltages shown in this table must be maintained.

- <sup>9</sup> To set VDD\_SNVS\_IN voltage with respect to Charging Currents and RTC, see the *Hardware Development Guide for i.MX* 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

#### i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors, Rev. 4, 07/2015

1

| Parameter                                              | Symbol           | Test Conditions                           | Min  | Max  | Unit |

|--------------------------------------------------------|------------------|-------------------------------------------|------|------|------|

| Output Differential Voltage                            | V <sub>OD</sub>  | Rload = 50 $\Omega$ between padP and padN | 300  | 500  | mV   |

| Output High Voltage                                    | V <sub>OH</sub>  |                                           | 1.15 | 1.75 | V    |

| Output Low Voltage                                     | V <sub>OL</sub>  |                                           | 0.75 | 1.35 | V    |

| Common-mode Output Voltage<br>((Vpad_P + Vpad_N) / 2)) | V <sub>OCM</sub> |                                           | 1    | 1.5  | V    |

| Differential Output Impedance                          | Z <sub>O</sub>   | —                                         | 1.6  |      | kΩ   |

## Table 26. MLB I/O DC Parameters

## 4.7 I/O AC Parameters

This section includes the AC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

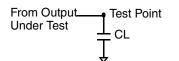

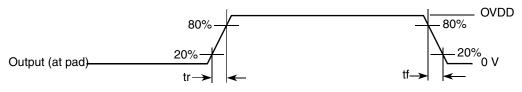

The GPIO and DDR I/O load circuit and output transition time waveforms are shown in Figure 4 and Figure 5.

CL includes package, probe and fixture capacitance

## Figure 4. Load Circuit for Output

Figure 5. Output Transition Time Waveform

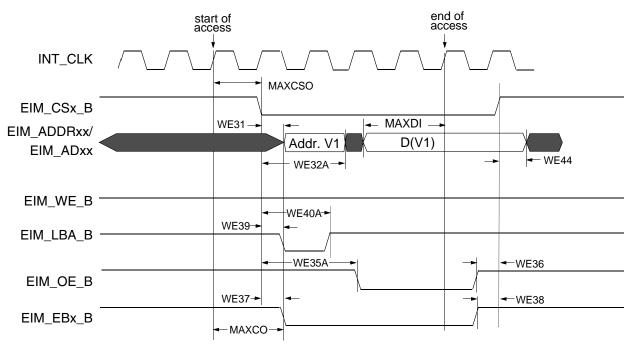

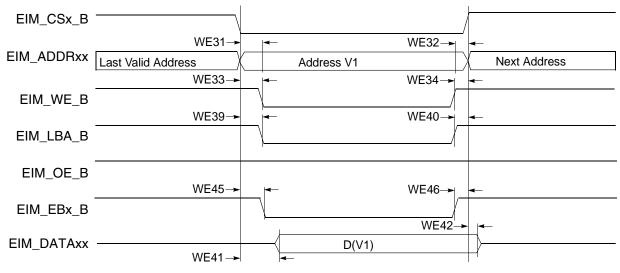

Figure 20. Asynchronous Memory Write Access

## 4.10.1 Asynchronous Mode AC Timing (ONFI 1.0 Compatible)

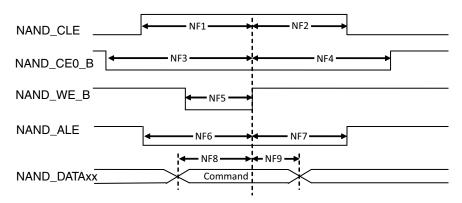

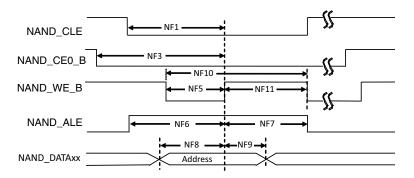

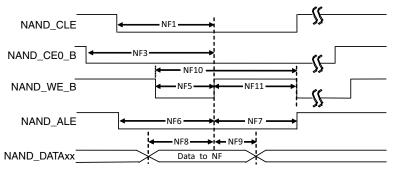

Asynchronous mode AC timings are provided as multiplications of the clock cycle and fixed delay. The Maximum I/O speed of GPMI in Asynchronous mode is about 50 MB/s. Figure 30 through Figure 33 depict the relative timing between GPMI signals at the module level for different operations under Asynchronous mode. Table 48 describes the timing parameters (NF1–NF17) that are shown in the figures.

Figure 30. Command Latch Cycle Timing Diagram

Figure 31. Address Latch Cycle Timing Diagram

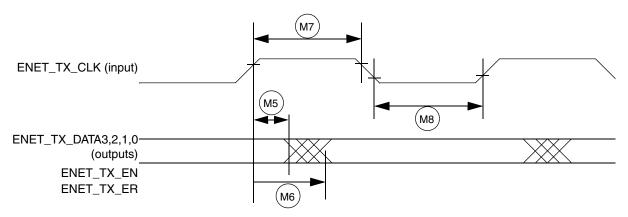

# 4.11.5.1.2 MII Transmit Signal Timing (ENET\_TX\_DATA3,2,1,0, ENET\_TX\_EN, ENET\_TX\_ER, and ENET\_TX\_CLK)

The transmitter functions correctly up to an ENET\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_TX\_CLK frequency.

Figure 49 shows MII transmit signal timings. Table 58 describes the timing parameters (M5–M8) shown in the figure.

Figure 49. MII Transmit Signal Timing Diagram

| Table 58 | 3. MII | Transmit | Signal | Timing |

|----------|--------|----------|--------|--------|

|----------|--------|----------|--------|--------|

| ID | Characteristic <sup>1</sup>                                           | Min | Max | Unit               |

|----|-----------------------------------------------------------------------|-----|-----|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER invalid | 5   | _   | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid   | _   | 20  | ns                 |

| M7 | ENET_TX_CLK pulse width high                                          | 35% | 65% | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                           | 35% | 65% | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

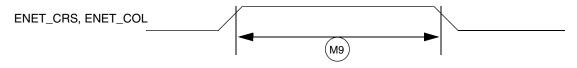

## 4.11.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 50 shows MII asynchronous input timings. Table 59 describes the timing parameter (M9) shown in the figure.

Figure 50. MII Async Inputs Timing Diagram

| i.MX 6Dual/6Quad        |                             |                                         |               | LCD                    |                             |                                                                    |                 |                                              |  |

|-------------------------|-----------------------------|-----------------------------------------|---------------|------------------------|-----------------------------|--------------------------------------------------------------------|-----------------|----------------------------------------------|--|

|                         | RGB,                        | RGB, RGB/TV Signal Allocation (Example) |               |                        |                             |                                                                    |                 | Comment <sup>1,2</sup>                       |  |

| Port Name<br>(x = 0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB                           | 18-bit<br>RGB | 24 Bit<br>RGB          | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb                                                    | 20-bit<br>YCrCb |                                              |  |

| IPUx_DIx_D0_CS          |                             |                                         |               |                        |                             | _                                                                  |                 |                                              |  |

| IPUx_DIx_D1_CS          |                             | _                                       |               |                        |                             | Alternate mode of PWM output for<br>contrast or brightness control |                 |                                              |  |

| IPUx_DIx_PIN11          |                             |                                         |               | _                      |                             |                                                                    |                 | _                                            |  |

| IPUx_DIx_PIN12          |                             |                                         |               | _                      |                             |                                                                    |                 | —                                            |  |

| IPUx_DIx_PIN13          |                             | — Register select signal                |               | Register select signal |                             |                                                                    |                 |                                              |  |

| IPUx_DIx_PIN14          |                             |                                         |               |                        | Optional RS2                |                                                                    |                 |                                              |  |

| IPUx_DIx_PIN15          |                             | DRDY/DV                                 |               |                        |                             | Data validation/blank, data enable                                 |                 |                                              |  |

| IPUx_DIx_PIN16          |                             |                                         |               |                        |                             | Additional data synchronous                                        |                 |                                              |  |

| IPUx_DIx_PIN17          |                             |                                         |               | Q                      |                             |                                                                    |                 | signals with programmable<br>features/timing |  |

#### Table 68. Video Signal Cross-Reference (continued)

<sup>1</sup> Signal mapping (both data and control/synchronization) is flexible. The table provides examples.

<sup>2</sup> Restrictions for ports IPUx\_DISPx\_DAT00 through IPUx\_DISPx\_DAT23 are as follows:

• A maximum of three continuous groups of bits can be independently mapped to the external bus. Groups must not overlap.

• The bit order is expressed in each of the bit groups, for example, B[0] = least significant blue pixel bit.

<sup>3</sup> This mode works in compliance with recommendation ITU-R BT.656. The timing reference signals (frame start, frame end, line start, and line end) are embedded in the 8-bit data bus. Only video data is supported, transmission of non-video related data during blanking intervals is not supported.

## NOTE

Table 68 provides information for both the DISP0 and DISP1 ports. However, DISP1 port has reduced pinout depending on IOMUXC configuration and therefore may not support all configurations. See the IOMUXC table for details.

## 4.11.10.5 IPU Display Interface Timing

The IPU Display Interface supports two kinds of display accesses: synchronous and asynchronous. There are two groups of external interface pins to provide synchronous and asynchronous controls.

## 4.11.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent waveform.

There are special physical outputs to provide synchronous controls:

• The ipp\_disp\_clk is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

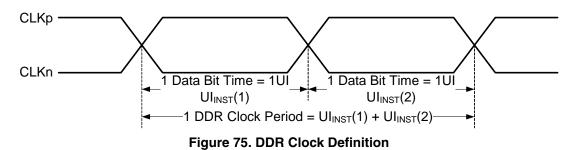

## 4.11.12.7 Forward High-Speed Data Transmission Timing

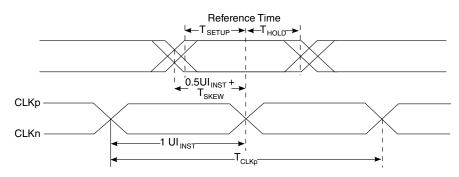

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 76:

Figure 76. Data to Clock Timing Definitions

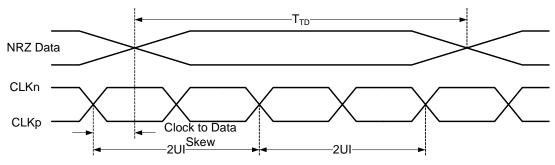

## 4.11.12.8 Reverse High-Speed Data Transmission Timing

Figure 77. Reverse High-Speed Data Transmission Timing at Slave Side

| ID   | Parameter                      | Min   | Мах | Unit |

|------|--------------------------------|-------|-----|------|

|      | Oversampling Clock Oper        | ation |     |      |

| SS47 | Oversampling clock period      | 15.04 | _   | ns   |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |

| SS49 | Oversampling clock rise time   | _     | 3.0 | ns   |

| SS50 | Oversampling clock low period  | 6.0   |     | ns   |

| SS51 | Oversampling clock fall time   | —     | 3.0 | ns   |

### Table 87. SSI Receiver Timing with Internal Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- AUDx\_TXC and AUDx\_RXC refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

## 5 Boot Mode Configuration

This section provides information on boot mode configuration pins allocation and boot devices interfaces allocation.

## 5.1 Boot Mode Configuration Pins

Table 97 provides boot options, functionality, fuse values, and associated pins. Several input pins are also sampled at reset and can be used to override fuse values, depending on the value of BT\_FUSE\_SEL fuse. The boot option pins are in effect when BT\_FUSE\_SEL fuse is '0' (cleared, which is the case for an unblown fuse). For detailed boot mode options configured by the boot mode pins, see the i.MX 6Dual/6Quad Fuse Map document and the System Boot chapter of the i.MX 6Dual/6Quad reference manual (IMX6DQRM).

| Pin                 | Direction at Reset        | eFuse Name          |  |  |  |  |  |

|---------------------|---------------------------|---------------------|--|--|--|--|--|

| Boot Mode Selection |                           |                     |  |  |  |  |  |

| BOOT_MODE1          | Input                     | Boot Mode Selection |  |  |  |  |  |

| BOOT_MODE0          | Input                     | Boot Mode Selection |  |  |  |  |  |

|                     | Boot Options <sup>1</sup> |                     |  |  |  |  |  |

| EIM_DA0             | Input                     | BOOT_CFG1[0]        |  |  |  |  |  |

| EIM_DA1             | Input                     | BOOT_CFG1[1]        |  |  |  |  |  |

| EIM_DA2             | Input                     | BOOT_CFG1[2]        |  |  |  |  |  |

| EIM_DA3             | Input                     | BOOT_CFG1[3]        |  |  |  |  |  |

| EIM_DA4             | Input                     | BOOT_CFG1[4]        |  |  |  |  |  |

| EIM_DA5             | Input                     | BOOT_CFG1[5]        |  |  |  |  |  |

| EIM_DA6             | Input                     | BOOT_CFG1[6]        |  |  |  |  |  |

| EIM_DA7             | Input                     | BOOT_CFG1[7]        |  |  |  |  |  |

| EIM_DA8             | Input                     | BOOT_CFG2[0]        |  |  |  |  |  |

| EIM_DA9             | Input                     | BOOT_CFG2[1]        |  |  |  |  |  |

| EIM_DA10            | Input                     | BOOT_CFG2[2]        |  |  |  |  |  |

| EIM_DA11            | Input                     | BOOT_CFG2[3]        |  |  |  |  |  |

| EIM_DA12            | Input                     | BOOT_CFG2[4]        |  |  |  |  |  |

| EIM_DA13            | Input                     | BOOT_CFG2[5]        |  |  |  |  |  |

| EIM_DA14            | Input                     | BOOT_CFG2[6]        |  |  |  |  |  |

| EIM_DA15            | Input                     | BOOT_CFG2[7]        |  |  |  |  |  |

| EIM_A16             | Input                     | BOOT_CFG3[0]        |  |  |  |  |  |

| EIM_A17             | Input                     | BOOT_CFG3[1]        |  |  |  |  |  |

i.MX 6Dual/6Quad Automotive and Infotainment Applications Processors, Rev. 4, 07/2015

Package Information and Contact Assignments

# 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

## 6.1 Updated Signal Naming Convention

The signal names of the i.MX6 series of products have been standardized to better align the signal names within the family and across the documentation. Some of the benefits of these changes are as follows:

- The names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- The names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This change applies only to signal names. The original ball names have been preserved to prevent the need to change schematics, BSDL models, IBIS models, etc.

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, *IMX 6 Series Signal Name Mapping* (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

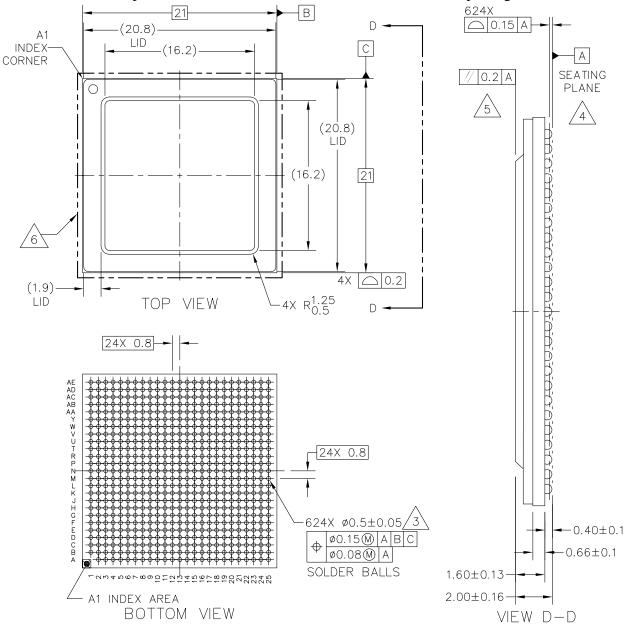

## 6.2 21 x 21 mm Package Information

## 6.2.1 Case FCPBGA, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

## 6.2.1.1 21 x 21 mm Lidded Package

Figure 107 shows the top, bottom, and side views of the  $21 \times 21$  mm lidded package.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUT | ΓLINE                     | PRINT VERSION NOT TO SCALE |

|---------------------------------------------------------|----------------|---------------------------|----------------------------|

| TITLE: 624 I/O FC PBC                                   | DOCUMEN        | NT NO: 98ASA00330D REV: D |                            |

| 21 X 21 X 2 PK                                          | STANDAF        | RD: NON-JEDEC             |                            |

| 0.8 MM PITCH, STAMI                                     |                | 08 OCT 2013               |                            |

Figure 106. 21 x 21 mm Lidded Package Top, Bottom, and Side Views (Sheet 1 of 2)

|             |      |             |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |

|-------------|------|-------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|

| Ball Name   | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |

| DISP0_DAT18 | V25  | NVCC_LCD    | GPIO      | ALT5                                | GPIO5_IO12                        | Input        | PU (100K)          |

| DISP0_DAT19 | U23  | NVCC_LCD    | GPIO      | ALT5                                | GPIO5_IO13                        | Input        | PU (100K)          |

| DISP0_DAT2  | P23  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO23                        | Input        | PU (100K)          |

| DISP0_DAT20 | U22  | NVCC_LCD    | GPIO      | ALT5                                | GPIO5_IO14                        | Input        | PU (100K)          |

| DISP0_DAT21 | T20  | NVCC_LCD    | GPIO      | ALT5                                | GPIO5_IO15                        | Input        | PU (100K)          |

| DISP0_DAT22 | V24  | NVCC_LCD    | GPIO      | ALT5                                | GPIO5_IO16                        | Input        | PU (100K)          |

| DISP0_DAT23 | W24  | NVCC_LCD    | GPIO      | ALT5                                | GPI05_I017                        | Input        | PU (100K)          |

| DISP0_DAT3  | P21  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO24                        | Input        | PU (100K)          |

| DISP0_DAT4  | P20  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO25                        | Input        | PU (100K)          |

| DISP0_DAT5  | R25  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO26                        | Input        | PU (100K)          |

| DISP0_DAT6  | R23  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_I027                        | Input        | PU (100K)          |

| DISP0_DAT7  | R24  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO28                        | Input        | PU (100K)          |

| DISP0_DAT8  | R22  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO29                        | Input        | PU (100K)          |

| DISP0_DAT9  | T25  | NVCC_LCD    | GPIO      | ALT5                                | GPIO4_IO30                        | Input        | PU (100K)          |

| DRAM_A0     | AC14 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR00                       | Output       | 0                  |

| DRAM_A1     | AB14 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR01                       | Output       | 0                  |

| DRAM_A10    | AA15 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR10                       | Output       | 0                  |

| DRAM_A11    | AC12 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR11                       | Output       | 0                  |

| DRAM_A12    | AD12 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR12                       | Output       | 0                  |

| DRAM_A13    | AC17 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR13                       | Output       | 0                  |

| DRAM_A14    | AA12 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR14                       | Output       | 0                  |

| DRAM_A15    | Y12  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR15                       | Output       | 0                  |

| DRAM_A2     | AA14 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR02                       | Output       | 0                  |

| DRAM_A3     | Y14  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR03                       | Output       | 0                  |

| DRAM_A4     | W14  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR04                       | Output       | 0                  |

| DRAM_A5     | AE13 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR05                       | Output       | 0                  |

| DRAM_A6     | AC13 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR06                       | Output       | 0                  |

| DRAM_A7     | Y13  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR07                       | Output       | 0                  |

| DRAM_A8     | AB13 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR08                       | Output       | 0                  |

| DRAM_A9     | AE12 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_ADDR09                       | Output       | 0                  |

| DRAM_CAS    | AE16 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_CAS_B                        | Output       | 0                  |

| DRAM_CS0    | Y16  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_CS0_B                        | Output       | 0                  |

| DRAM_CS1    | AD17 | NVCC_DRAM   | DDR       | ALT0                                | DRAM_CS1_B                        | Output       | 0                  |

| DRAM_D0     | AD2  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_DATA00                       | Input        | PU (100K)          |

| DRAM_D1     | AE2  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_DATA01                       | Input        | PU (100K)          |

| DRAM_D10    | AA6  | NVCC_DRAM   | DDR       | ALT0                                | DRAM_DATA10                       | Input        | PU (100K)          |

Table 100. 21 x 21 mm Functional Contact Assignments (continued)

### Package Information and Contact Assignments

|             |      |               |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |

|-------------|------|---------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|

| Ball Name   | Ball | Power Group   | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |

| LVDS0_TX3_P | W1   | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS0_TX3_P                       | Input        | Keeper             |

| LVDS1_CLK_N | Y3   | NVCC_LVDS_2P5 | LVDS      | —                                   | LVDS1_CLK_N                       | —            | _                  |

| LVDS1_CLK_P | Y4   | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS1_CLK_P                       | Input        | Keeper             |

| LVDS1_TX0_N | Y1   | NVCC_LVDS_2P5 | LVDS      | —                                   | LVDS1_TX0_N                       | —            |                    |

| LVDS1_TX0_P | Y2   | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS1_TX0_P                       | Input        | Keeper             |

| LVDS1_TX1_N | AA2  | NVCC_LVDS_2P5 | LVDS      | —                                   | LVDS1_TX1_N                       | —            |                    |

| LVDS1_TX1_P | AA1  | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS1_TX1_P                       | Input        | Keeper             |

| LVDS1_TX2_N | AB1  | NVCC_LVDS_2P5 | LVDS      | —                                   | LVDS1_TX2_N                       | —            | _                  |

| LVDS1_TX2_P | AB2  | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS1_TX2_P                       | Input        | Keeper             |

| LVDS1_TX3_N | AA3  | NVCC_LVDS_2P5 | LVDS      | —                                   | LVDS1_TX3_N                       | —            | _                  |

| LVDS1_TX3_P | AA4  | NVCC_LVDS_2P5 | LVDS      | ALT0                                | LVDS1_TX3_P                       | Input        | Keeper             |

| MLB_CN      | A11  | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_CLK_N                         | —            | —                  |

| MLB_CP      | B11  | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_CLK_P                         | _            | —                  |

| MLB_DN      | B10  | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_DATA_N                        | —            | —                  |

| MLB_DP      | A10  | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_DATA_P                        | —            | —                  |

| MLB_SN      | A9   | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_SIG_N                         | _            | —                  |

| MLB_SP      | B9   | VDD_HIGH_CAP  | LVDS      | —                                   | MLB_SIG_P                         | —            | _                  |

| NANDF_ALE   | A16  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_IO08                        | Input        | PU (100K)          |

| NANDF_CLE   | C15  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_I007                        | Input        | PU (100K)          |

| NANDF_CS0   | F15  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_IO11                        | Input        | PU (100K)          |

| NANDF_CS1   | C16  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_IO14                        | Input        | PU (100K)          |

| NANDF_CS2   | A17  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_IO15                        | Input        | PU (100K)          |

| NANDF_CS3   | D16  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO6_IO16                        | Input        | PU (100K)          |

| NANDF_D0    | A18  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO2_I000                        | Input        | PU (100K)          |

| NANDF_D1    | C17  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO2_IO01                        | Input        | PU (100K)          |

| NANDF_D2    | F16  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO2_I002                        | Input        | PU (100K)          |

| NANDF_D3    | D17  | NVCC_NANDF    | GPIO      | ALT5                                | GPIO2_I003                        | Input        | PU (100K)          |