# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q4avt10acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Modules List

| Block<br>Mnemonic                                                  | Block Name                           | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EPIT-1<br>EPIT-2                                                   | Enhanced Periodic<br>Interrupt Timer | Timer<br>Peripherals             | Each EPIT is a 32-bit "set and forget" timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler for division of input clock frequency to get the required time setting for the interrupts to occur, and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| ESAI                                                               | Enhanced Serial<br>Audio Interface   | Connectivity<br>Peripherals      | The Enhanced Serial Audio Interface (ESAI) provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other processors. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. All serial transfers are synchronized to a clock. Additional synchronization signals are used to delineate the word frames. The normal mode of operation is used to transfer data at a periodic rate, one word per period. The network mode is also intended for periodic transfers; however, it supports up to 32 words (time slots) per period. This mode can be used to build time division multiplexed (TDM) networks. In contrast, the on-demand mode is intended for non-periodic transfers of data and to transfer data serially at high speed when the data becomes available. The ESAI has 12 pins for data and clocking connection to external devices. |  |

| FlexCAN-1<br>FlexCAN-2                                             | Flexible Controller<br>Area Network  | Connectivity<br>Peripherals      | The CAN protocol was primarily, but not only, designed to be used as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the Electromagnetic interference (EMI) environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module is a full implementation of the CAN protocol specification, Version 2.0 B, which supports both standard and extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7 | General Purpose I/O<br>Modules       | System<br>Control<br>Peripherals | Used for general purpose input/output to external devices. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| GPMI                                                               | General Purpose<br>Media Interface   | Connectivity<br>Peripherals      | The GPMI module supports up to 8x NAND devices. 40-bit ECC<br>encryption/decryption for NAND Flash controller (GPMI2). The GPMI<br>supports separate DMA channels per NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| GPT                                                                | General Purpose<br>Timer             | Timer<br>Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget" mode timer with programmable prescaler and compare and capture register. A timer counter value can be captured using an external event and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in "set and forget" mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                                                                                                                                   |  |

Modules List

| Block<br>Mnemonic                | Block Name Subsystem          |                                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------------------------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LDB                              | LVDS Display Bridge           | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image Processing Unit) to External LVDS Display Interface. LDB supports two channels; each channel has following signals:</li> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad (PadP, PadM).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| MLB150                           | MediaLB                       | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 150 Mbps). The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| MMDC                             | Multi-Mode DDR<br>Controller  | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Support 16/32/64-bit DDR3-1066 (LV) or LPDDR2-1066</li> <li>Supports both dual x32 for LPDDR2 and x64 DDR3 / LPDDR2 configurations (including 2x32 interleaved mode)</li> <li>Support up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| OCOTP_CTRL                       | OTP Controller                | Security                                    | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |  |  |

| OCRAM                            | On-Chip Memory<br>Controller  | Data Path                                   | The On-Chip Memory controller (OCRAM) module is designed as an interface between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6Dual/6Quad processors, the OCRAM is used for controlling the 256 KB multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| OSC 32 kHz                       | OSC 32 kHz                    | Clocking                                    | Generates 32.768 kHz clock from an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals                 | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PMU                              | Power-Management<br>Functions | Data Path                                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation     | Connectivity<br>Peripherals                 | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| RAM<br>16 KB                     | Secure/non-secure<br>RAM      | Secured<br>Internal<br>Memory               | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| RAM<br>256 KB                    | Internal RAM                  | Internal<br>Memory                          | Internal RAM, which is accessed through OCRAM memory controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Modules List

| Block<br>Mnemonic | Block Name                      | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-2<br>(TZ)    | Watchdog<br>(TrustZone)         | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such a situation is<br>undesirable as it can compromise the system's security. Once the TZ<br>WDOG module is activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer times out. Upon<br>a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces<br>switching to the TZ mode. If it is still not served, the TZ WDOG asserts a<br>security violation signal to the CSU. The TZ WDOG module cannot be<br>programmed or deactivated by a normal mode Software. |

| EIM               | NOR-Flash /PSRAM<br>interface   | Connectivity<br>Peripherals | <ul> <li>The EIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTALOSC           | Crystal Oscillator<br>interface | —                           | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### 3.1 Special Signal Considerations

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are defined in the i.MX 6Dual/6Quad reference manual (IMX6DQRM). Special signal consideration information is contained in the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

### 3.2 Recommended Connections for Unused Analog Interfaces

The recommended connections for unused analog interfaces can be found in the section, "Unused analog interfaces," of the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

### 4.4.4 480 MHz PLL

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

#### Table 17. 480 MHz PLL Electrical Parameters

### 4.4.5 MLB PLL

The MediaLB PLL is necessary in the MediaLB 6-Pin implementation to phase align the internal and external clock edges, effectively tuning out the delay of the differential clock receiver and is also responsible for generating the higher speed internal clock, when the internal-to-external clock ratio is not 1:1.

#### Table 18. MLB PLL Electrical Parameters

| Parameter | Value   |

|-----------|---------|

| Lock time | <1.5 ms |

### 4.4.6 ARM PLL

#### Table 19. ARM PLL Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz~1.3 GHz        |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

### 4.5 **On-Chip Oscillators**

### 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

### 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered

### 4.6.2 General Purpose I/O (GPIO) DC Parameters

Table 22 shows DC parameters for GPIO pads. The parameters in Table 22 are guaranteed per the operating ranges in Table 6, unless otherwise noted.

| Parameter                                   | Symbol | Test Conditions                                                                               | Min                      | Max                      | Unit |

|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|

| High-level output voltage <sup>1</sup>      | Voh    | loh = -0.1 mA (DSE <sup>2</sup> = 001, 010)<br>loh = -1 mA<br>(DSE = 011, 100, 101, 110, 111) | OVDD - 0.15              | _                        | V    |

| Low-level output voltage <sup>1</sup>       | Vol    | lol = 0.1 mA (DSE <sup>2</sup> = 001, 010)<br>lol = 1mA<br>(DSE = 011, 100, 101, 110, 111)    | _                        | 0.15                     | V    |

| High-Level DC input voltage <sup>1, 3</sup> | Vih    | —                                                                                             | $0.7 \times \text{OVDD}$ | OVDD                     | V    |

| Low-Level DC input voltage <sup>1, 3</sup>  | Vil    |                                                                                               | 0                        | $0.3 \times \text{OVDD}$ | V    |

| Input Hysteresis                            | Vhys   | OVDD = 1.8 V<br>OVDD = 3.3 V                                                                  | 0.25                     | _                        | V    |

| Schmitt trigger VT+ <sup>3, 4</sup>         | VT+    | _                                                                                             | 0.5 	imes OVDD           | _                        | V    |

| Schmitt trigger VT-3, 4                     | VT–    |                                                                                               |                          | $0.5 \times \text{OVDD}$ | V    |

| Input current (no pull-up/down)             | lin    | Vin = OVDD or 0                                                                               | -1                       | 1                        | μA   |

| Input current (22 kΩ pull-up)               | lin    | Vin = 0 V<br>Vin = OVDD                                                                       | —                        | 212<br>1                 | μA   |

| Input current (47 kΩ pull-up)               | lin    | Vin = 0 V<br>Vin = OVDD                                                                       | —                        | 100<br>1                 | μA   |

| Input current (100 kΩ pull-up)              | lin    | Vin = 0 V<br>Vin= OVDD                                                                        | —                        | 48<br>1                  | μA   |

| Input current (100 kΩ pull-down)            | lin    | Vin = 0 V<br>Vin = OVDD                                                                       | —                        | 1<br>48                  | μA   |

| Keeper circuit resistance                   | Rkeep  | Vin = 0.3 x OVDD<br>Vin = 0.7 x OVDD                                                          | 105                      | 175                      | kΩ   |

#### Table 22. GPIO I/O DC Parameters

<sup>1</sup> Overshoot and undershoot conditions (transitions above OVDD and below GND) on switching pads must be held below 0.6 V, and the duration of the overshoot/undershoot must not exceed 10% of the system clock cycle. Overshoot/ undershoot must be controlled through printed circuit board layout, transmission line impedance matching, signal line termination, or other methods. Non-compliance to this specification may affect device reliability or cause permanent damage to the device.

<sup>2</sup> DSE is the Drive Strength Field setting in the associated IOMUX control register.

<sup>3</sup> To maintain a valid level, the transition edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, Vil or Vih. Monotonic input transition time is from 0.1 ns to 1 s.

<sup>4</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled.

### 4.6.3 DDR I/O DC Parameters

The DDR I/O pads support LPDDR2 and DDR3/DDR3L operational modes.

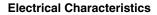

Figure 7. Differential MLB Driver Transition Time Waveform

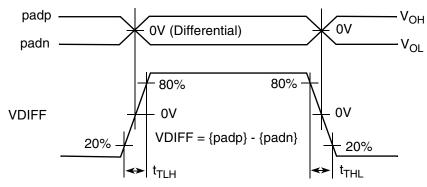

A 4-stage pipeline is used in the MLB 6-pin implementation to facilitate design, maximize throughput, and allow for reasonable PCB trace lengths. Each cycle is one ipp\_clk\_in\* (internal clock from MLB PLL) clock period. Cycles 2, 3, and 4 are MLB PHY related. Cycle 2 includes clock-to-output delay of Signal/Data sampling flip-flop and Transmitter, Cycle 3 includes clock-to-output delay of Signal/Data clocked receiver, Cycle 4 includes clock-to-output delay of Signal/Data sampling flip-flop.

MLB 6-pin pipeline diagram is shown in Figure 8.

Figure 8. MLB 6-Pin Pipeline Diagram

Table 32 shows the AC parameters for MLB I/O.

| Table 32. I/O AC | Parameters of MLB PHY |

|------------------|-----------------------|

|------------------|-----------------------|

| Parameter                                | Symbol           | Test Condition      | Min | Тур | Max   | Unit |

|------------------------------------------|------------------|---------------------|-----|-----|-------|------|

| Differential pulse skew <sup>1</sup>     | t <sub>SKD</sub> | Rload = 50 $\Omega$ | _   |     | 0.1   |      |

| Transition Low to High Time <sup>2</sup> | t <sub>TLH</sub> | between padP        | _   |     | 1     | ns   |

| Transition High to Low Time              | t <sub>THL</sub> | and padN            | _   |     | 1     |      |

| MLB external clock Operating Frequency   | fclk_ext         | —                   | _   |     | 102.4 | MHz  |

| MLB PLL clock Operating Frequency        | fclk_pll         | —                   | _   |     | 307.2 | MHz  |

<sup>1</sup> t<sub>SKD</sub> = | t<sub>PHLD</sub> - t<sub>PLHD</sub> |, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

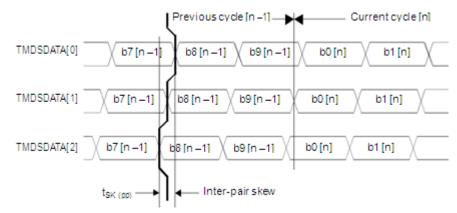

<sup>2</sup> Measurement levels are 20-80% from output voltage.

### 4.8.1 GPIO Output Buffer Impedance

Table 33 shows the GPIO output buffer impedance (OVDD 1.8 V).

#### Table 33. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

| Parameter     | Symbol | Drive Strength (ipp_dse) | Typ Value | Unit |

|---------------|--------|--------------------------|-----------|------|

|               |        | 001                      | 260       |      |

|               | Rdrv   | 010                      | 130       |      |

|               |        | 011                      | 90        |      |

| Output Driver |        | 100                      | 60        | Ω    |

| Impedance     |        | 101                      | 50        |      |

|               |        | 110                      | 40        |      |

|               |        | 111                      | 33        |      |

Table 34 shows the GPIO output buffer impedance (OVDD 3.3 V).

#### Table 34. GPIO Output Buffer Average Impedance (OVDD 3.3 V)

| Parameter                  | Symbol | Drive Strength (ipp_dse) | Typ Value | Unit |

|----------------------------|--------|--------------------------|-----------|------|

|                            |        | 001                      | 150       |      |

|                            | Rdrv   | 010                      | 75        |      |

|                            |        | 011                      | 50        |      |

| Output Driver<br>Impedance |        | 100                      | 37        | Ω    |

| Impedance                  |        | 101                      | 30        |      |

|                            |        | 110                      |           |      |

|                            |        | 111                      | 20        |      |

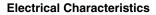

### 4.9.3.4 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22 and Table 41 provide timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the i.MX 6Dual/6Quad reference manual (IMX6DQRM) for the EIM programming model.

Figure 18. Asynchronous Memory Read Access (RWSC = 5)

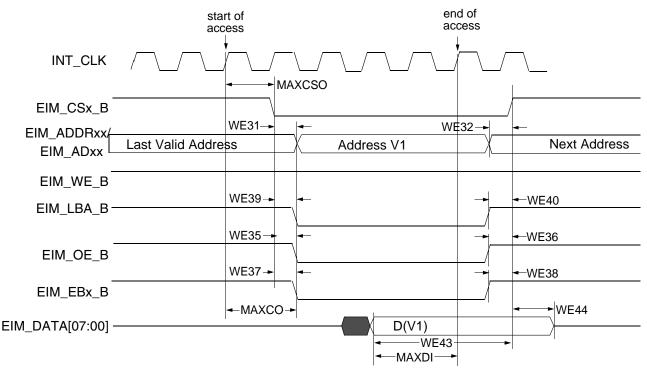

### 4.10.1 Asynchronous Mode AC Timing (ONFI 1.0 Compatible)

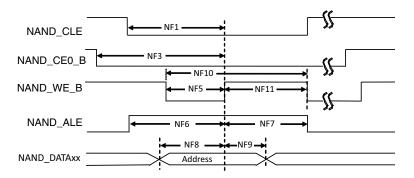

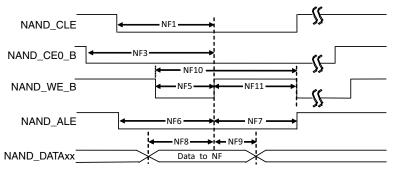

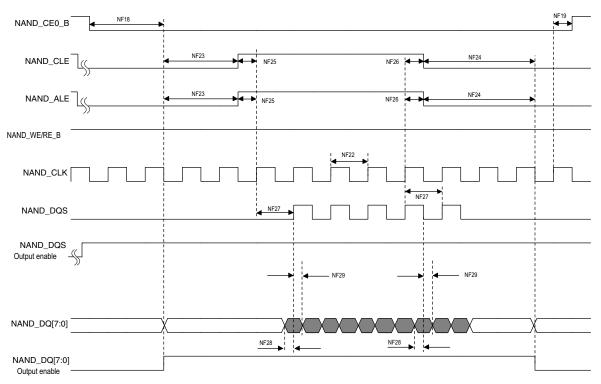

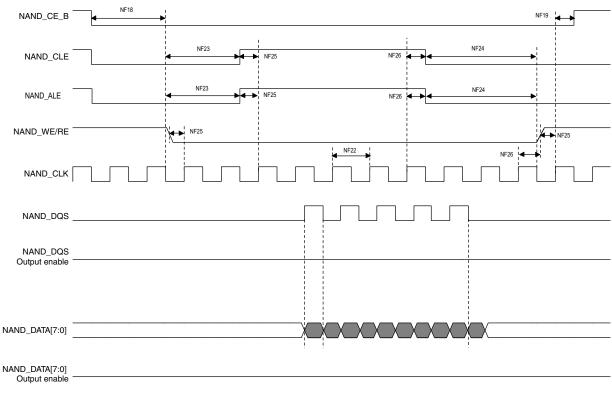

Asynchronous mode AC timings are provided as multiplications of the clock cycle and fixed delay. The Maximum I/O speed of GPMI in Asynchronous mode is about 50 MB/s. Figure 30 through Figure 33 depict the relative timing between GPMI signals at the module level for different operations under Asynchronous mode. Table 48 describes the timing parameters (NF1–NF17) that are shown in the figures.

Figure 30. Command Latch Cycle Timing Diagram

Figure 31. Address Latch Cycle Timing Diagram

**Electrical Characteristics**

#### Figure 63. TMDS Output Signals Rise and Fall Time Definition

| Symbol         | Parameter                            | Conditions                                                              | Min  | Тур | Max    | Unit |

|----------------|--------------------------------------|-------------------------------------------------------------------------|------|-----|--------|------|

|                | T                                    | MDS Drivers Specifications                                              |      |     |        |      |

|                | Maximum serial data rate             | —                                                                       | —    | —   | 3.4    | Gbps |

| F<br>TMDSCLK   | TMDSCLK frequency                    | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz  |

| P<br>TMDSCLK   | TMDSCLK period                       | RL = 50 $\Omega$<br>See Figure 59.                                      | 2.94 | _   | 40     | ns   |

| t<br>CDC       | TMDSCLK duty cycle                   | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 59. | 40   | 50  | 60     | %    |

| t<br>CPH       | TMDSCLK high time                    | RL = 50 $\Omega$<br>See Figure 59.                                      | 4    | 5   | 6      | UI   |

| t<br>CPL       | TMDSCLK low time                     | RL = 50 Ω<br>See Figure 59.                                             | 4    | 5   | 6      | UI   |

| _              | TMDSCLK jitter <sup>1</sup>          | RL = 50 Ω                                                               | _    | —   | 0.25   | UI   |

| t<br>SK(p)     | Intra-pair (pulse) skew              | RL = 50 $\Omega$<br>See Figure 61.                                      | -    | _   | 0.15   | UI   |

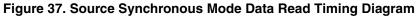

| t<br>SK(pp)    | Inter-pair skew                      | RL = 50 Ω<br>See Figure 62.                                             | -    | —   | 1      | UI   |

| t <sub>R</sub> | Differential output signal rise time | 20–80%<br>RL = 50 $\Omega$<br>See Figure 63.                            | 75   | —   | 0.4 UI | ps   |

#### Table 64. Switching Characteristics

### 4.11.10.1 IPU Sensor Interface Signal Mapping

The IPU supports a number of sensor input formats. Table 66 defines the mapping of the Sensor Interface Pins used for various supported interface formats.

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>2 cycles | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| IPUx_CSIx_<br>DATA00        | —                            | —                                         | —                                         | _                            |                                          | —                                          | —                                        | 0                                        | C[0]                                     |

| IPUx_CSIx_<br>DATA01        | —                            | —                                         | _                                         |                              | —                                        | _                                          | —                                        | 0                                        | C[1]                                     |

| IPUx_CSIx_<br>DATA02        | —                            | —                                         | —                                         | _                            | —                                        | -                                          | —                                        | C[0]                                     | C[2]                                     |

| IPUx_CSIx_<br>DATA03        | —                            | —                                         | _                                         | _                            |                                          | —                                          | —                                        | C[1]                                     | C[3]                                     |

| IPUx_CSIx_<br>DATA04        | —                            | —                                         | _                                         | _                            |                                          | B[0]                                       | C[0]                                     | C[2]                                     | C[4]                                     |

| IPU2_CSIx_<br>DATA_05       | —                            | —                                         | _                                         | _                            |                                          | B[1]                                       | C[1]                                     | C[3]                                     | C[5]                                     |

| IPUx_CSIx_<br>DATA06        | —                            | —                                         | —                                         | _                            | _                                        | B[2]                                       | C[2]                                     | C[4]                                     | C[6]                                     |

| IPUx_CSIx_<br>DATA07        |                              | _                                         | _                                         | _                            |                                          | B[3]                                       | C[3]                                     | C[5]                                     | C[7]                                     |

| IPUx_CSIx_<br>DATA08        | _                            | —                                         | _                                         |                              |                                          | B[4]                                       | C[4]                                     | C[6]                                     | C[8]                                     |

| IPUx_CSIx_<br>DATA09        | —                            | —                                         | _                                         | _                            |                                          | G[0]                                       | C[5]                                     | C[7]                                     | C[9]                                     |

| IPUx_CSIx_<br>DATA10        | —                            | —                                         | —                                         | _                            |                                          | G[1]                                       | C[6]                                     | 0                                        | Y[0]                                     |

| IPUx_CSIx_<br>DATA11        | —                            | —                                         | _                                         | _                            |                                          | G[2]                                       | C[7]                                     | 0                                        | Y[1]                                     |

| IPUx_CSIx_<br>DATA12        | B[0], G[3]                   | R[2],G[4],B[2]                            | R/G/B[4]                                  | R/G/B[0]                     | Y/C[0]                                   | G[3]                                       | Y[0]                                     | Y[0]                                     | Y[2]                                     |

| IPUx_CSIx_<br>DATA13        | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                       | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| IPUx_CSIx_<br>DATA14        | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                       | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| IPUx_CSIx_<br>DATA15        | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                       | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| IPUx_CSIx_<br>DATA16        | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                       | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| IPUx_CSIx_<br>DATA17        | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                       | Y[5]                                     | Y[5]                                     | Y[7]                                     |

| IPUx_CSIx_<br>DATA18        | G[1], R[3]                   | R[3],G[4],B[3]                            | R/G/B[4]                                  | R/G/B[6]                     | Y/C[6]                                   | R[3]                                       | Y[6]                                     | Y[6]                                     | Y[8]                                     |

| IPUx_CSIx_<br>DATA19        | G[2], R[4]                   | R[4],G[5],B[4]                            | R/G/B[5]                                  | R/G/B[7]                     | Y/C[7]                                   | R[4]                                       | Y[7]                                     | Y[7]                                     | Y[9]                                     |

Table 66. Camera Input Signal Cross Reference, Format, and Bits Per Cycle

<sup>1</sup> IPU2\_CSIx stands for IPU2\_CSI1 or IPU2\_CSI2.

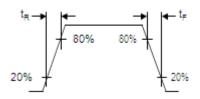

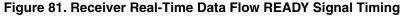

### 4.11.13.3 Receiver Real-Time Data Flow

Figure 82. Synchronized Data Flow Transmission with WAKE

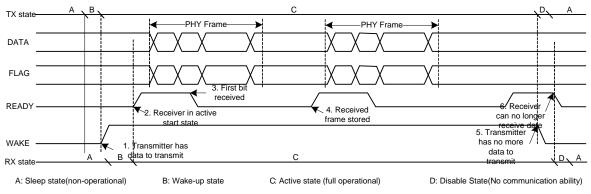

### 4.11.13.5 Stream Transmission Mode Frame Transfer

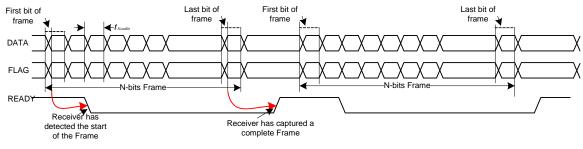

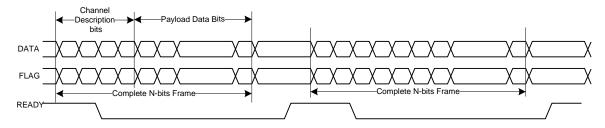

### 4.11.13.9 DATA and FLAG Signal Timing

Figure 86. DATA and FLAG Signal Timing

### 4.11.14 MediaLB (MLB) Characteristics

### 4.11.14.1 MediaLB (MLB) DC Characteristics

Table 75 lists the MediaLB 3-pin interface electrical characteristics.

| Parameter                   | Symbol          | Test Conditions         | Min | Мах | Unit |

|-----------------------------|-----------------|-------------------------|-----|-----|------|

| Maximum input voltage       | —               | _                       | —   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | _                       | _   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>   | 1.8 | —   | V    |

| Low level output threshold  | V <sub>OL</sub> | I <sub>OL</sub> = 6 mA  | _   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = -6 mA | 2.0 | —   | V    |

| Input leakage current       | ΙL              | $0 < V_{in} < VDD$      | —   | ±10 | μA   |

<sup>1</sup> Higher V<sub>IH</sub> thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

Table 76 lists the MediaLB 6-pin interface electrical characteristics.

Table 76. MediaLB 6-Pin Interface Electrical DC Specifications

| Parameter                                                                                                                          | Symbol           | Symbol Test Conditions |     | Мах | Unit |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|-----|-----|------|--|--|

| Driver Characteristics                                                                                                             |                  |                        |     |     |      |  |  |

| Differential output voltage (steady-state): I $V_{O_{+}}$ - $V_{O_{-}}$ I                                                          | V <sub>OD</sub>  | See Note <sup>1</sup>  | 300 | 500 | mV   |  |  |

| Difference in differential output voltage<br>between (high/low) steady-states:<br>I V <sub>OD, high</sub> - V <sub>OD, low</sub> I | ΔV <sub>OD</sub> | _                      | -50 | 50  | mV   |  |  |

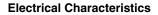

| ID   | Parameter                                           | Min  | Max  | Unit |  |  |  |

|------|-----------------------------------------------------|------|------|------|--|--|--|

|      | Internal Clock Operation                            |      |      |      |  |  |  |

| SS1  | SS1 AUDx_TXC/AUDx_RXC clock period                  |      | —    | ns   |  |  |  |

| SS2  | AUDx_TXC/AUDx_RXC clock high period                 | 36.0 | —    | ns   |  |  |  |

| SS4  | AUDx_TXC/AUDx_RXC clock low period                  | 36.0 | —    | ns   |  |  |  |

| SS6  | AUDx_TXC high to AUDx_TXFS (bl) high                | —    | 15.0 | ns   |  |  |  |

| SS8  | AUDx_TXC high to AUDx_TXFS (bl) low                 | —    | 15.0 | ns   |  |  |  |

| SS10 | AUDx_TXC high to AUDx_TXFS (wl) high                | _    | 15.0 | ns   |  |  |  |

| SS12 | AUDx_TXC high to AUDx_TXFS (wl) low                 | _    | 15.0 | ns   |  |  |  |

| SS14 | AUDx_TXC/AUDx_RXC Internal AUDx_TXFS rise time      | _    | 6.0  | ns   |  |  |  |

| SS15 | AUDx_TXC/AUDx_RXC Internal AUDx_TXFS fall time      | —    | 6.0  | ns   |  |  |  |

| SS16 | AUDx_TXC high to AUDx_TXD valid from high impedance | —    | 15.0 | ns   |  |  |  |

| SS17 | AUDx_TXC high to AUDx_TXD high/low                  | —    | 15.0 | ns   |  |  |  |

| SS18 | AUDx_TXC high to AUDx_TXD high impedance            | —    | 15.0 | ns   |  |  |  |

|      | Synchronous Internal Clock Operation                |      |      |      |  |  |  |

| SS42 | AUDx_RXD setup before AUDx_TXC falling              | 10.0 | _    | ns   |  |  |  |

| SS43 | AUDx_RXD hold after AUDx_TXC falling                | 0.0  | —    | ns   |  |  |  |

#### Table 86. SSI Transmitter Timing with Internal Clock

#### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is the same as that of transmit data (for example, during AC97 mode of operation).

### 4.11.20.2 SSI Receiver Timing with Internal Clock

Figure 97 depicts the SSI receiver internal clock timing and Table 87 lists the timing parameters for the receiver timing with the internal clock.

Figure 97. SSI Receiver Internal Clock Timing Diagram

| ID   | Parameter                               | Min  | Мах  | Unit |

|------|-----------------------------------------|------|------|------|

|      | Internal Clock Operatio                 | n    |      |      |

| SS1  | AUDx_TXC/AUDx_RXC clock period          | 81.4 | _    | ns   |

| SS2  | AUDx_TXC/AUDx_RXC clock high period     | 36.0 | _    | ns   |

| SS3  | AUDx_TXC/AUDx_RXC clock rise time       |      | 6.0  | ns   |

| SS4  | AUDx_TXC/AUDx_RXC clock low period      | 36.0 | _    | ns   |

| SS5  | AUDx_TXC/AUDx_RXC clock fall time       | _    | 6.0  | ns   |

| SS7  | AUDx_RXC high to AUDx_TXFS (bl) high    | _    | 15.0 | ns   |

| SS9  | AUDx_RXC high to AUDx_TXFS (bl) low     | —    | 15.0 | ns   |

| SS11 | AUDx_RXC high to AUDx_TXFS (wl) high    | —    | 15.0 | ns   |

| SS13 | AUDx_RXC high to AUDx_TXFS (wl) low     | —    | 15.0 | ns   |

| SS20 | AUDx_RXD setup time before AUDx_RXC low | 10.0 | —    | ns   |

| SS21 | AUDx_RXD hold time after AUDx_RXC low   | 0.0  | _    | ns   |

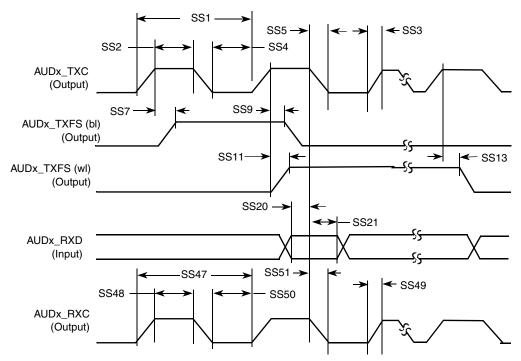

### 4.11.22 USB HSIC Timings

This section describes the electrical information of the USB HSIC port.

#### NOTE

HSIC is a DDR signal. The following timing specification is for both rising and falling edges.

### 4.11.22.1 Transmit Timing

Figure 104. USB HSIC Transmit Waveform

#### Table 95. USB HSIC Transmit Parameters

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | _                              |

| Todelay | data output delay time          | 550   | 1350  | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

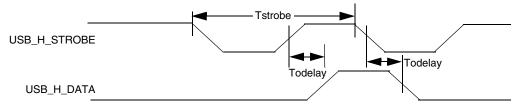

### 4.11.22.2 Receive Timing

Figure 105. USB HSIC Receive Waveform

#### Table 96. USB HSIC Receive Parameters<sup>1</sup>

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   | _                              |

| Thold   | data hold time                  | 300   | _     | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   | _     | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

**Package Information and Contact Assignments**

## 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

### 6.1 Updated Signal Naming Convention

The signal names of the i.MX6 series of products have been standardized to better align the signal names within the family and across the documentation. Some of the benefits of these changes are as follows:

- The names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- The names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This change applies only to signal names. The original ball names have been preserved to prevent the need to change schematics, BSDL models, IBIS models, etc.

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, *IMX 6 Series Signal Name Mapping* (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

### 6.2 21 x 21 mm Package Information

### 6.2.1 Case FCPBGA, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

|               |                      |              |           | Out of Reset Condition <sup>1</sup> |                                   |              |                                 |  |  |  |  |  |

|---------------|----------------------|--------------|-----------|-------------------------------------|-----------------------------------|--------------|---------------------------------|--|--|--|--|--|

| Ball Name     | Ball                 | Power Group  | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup>              |  |  |  |  |  |

| PCIE_TXM      | PCIE_TXM A3 PCIE_VPH |              | —         | _                                   | PCIE_TX_N                         | —            | —                               |  |  |  |  |  |

| PCIE_TXP      | B3                   | PCIE_VPH     | —         | _                                   | PCIE_TX_P                         | —            | —                               |  |  |  |  |  |

| PMIC_ON_REQ   | D11                  | VDD_SNVS_IN  | GPIO      | ALT0                                | SNVS_PMIC_ON_REQ                  | Output       | Open<br>Drain with<br>PU (100K) |  |  |  |  |  |

| PMIC_STBY_REQ | F11                  | VDD_SNVS_IN  | GPIO      | ALT0                                | CCM_PMIC_STBY_REQ                 | Output       | 0                               |  |  |  |  |  |

| POR_B         | C11                  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_POR_B                         | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_RD0     | C24                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO25                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_RD1     | B23                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO27                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_RD2     | B24                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO28                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_RD3     | D23                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO29                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_RX_CTL  | D22                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO24                        | Input        | PD (100K)                       |  |  |  |  |  |

| RGMII_RXC     | B25                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO30                        | Input        | PD (100K)                       |  |  |  |  |  |

| RGMII_TD0     | C22                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO20                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_TD1     | F20                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO21                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_TD2     | E21                  | NVCC_RGMII   | DDR       | ALT5                                | GPI06_I022                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_TD3     | A24                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO23                        | Input        | PU (100K)                       |  |  |  |  |  |

| RGMII_TX_CTL  | C23                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO26                        | Input        | PD (100K)                       |  |  |  |  |  |

| RGMII_TXC     | D21                  | NVCC_RGMII   | DDR       | ALT5                                | GPIO6_IO19                        | Input        | PD (100K)                       |  |  |  |  |  |

| RTC_XTALI     | D9                   | VDD_SNVS_CAP | —         | _                                   | RTC_XTALI                         | —            |                                 |  |  |  |  |  |

| RTC_XTALO     | C9                   | VDD_SNVS_CAP | —         | _                                   | RTC_XTALO                         | —            |                                 |  |  |  |  |  |

| SATA_RXM      | A14                  | SATA_VPH     | —         | _                                   | SATA_PHY_RX_N                     | _            | _                               |  |  |  |  |  |

| SATA_RXP      | B14                  | SATA_VPH     | —         | _                                   | SATA_PHY_RX_P                     | _            | _                               |  |  |  |  |  |

| SATA_TXM      | B12                  | SATA_VPH     | —         | _                                   | SATA_PHY_TX_N                     | _            | —                               |  |  |  |  |  |

| SATA_TXP      | A12                  | SATA_VPH     | —         | _                                   | SATA_PHY_TX_P                     | _            | _                               |  |  |  |  |  |

| SD1_CLK       | D20                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO20                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD1_CMD       | B21                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO18                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD1_DAT0      | A21                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO16                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD1_DAT1      | C20                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO17                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD1_DAT2      | E19                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO19                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD1_DAT3      | F18                  | NVCC_SD1     | GPIO      | ALT5                                | GPIO1_IO21                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_CLK       | C21                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO10                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_CMD       | F19                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO11                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_DAT0      | A22                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO15                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_DAT1      | E20                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO14                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_DAT2      | A23                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO13                        | Input        | PU (100K)                       |  |  |  |  |  |

| SD2_DAT3      | B22                  | NVCC_SD2     | GPIO      | ALT5                                | GPIO1_IO12                        | Input        | PU (100K)                       |  |  |  |  |  |

| Table 100. 21 x 21 m | m Functional Con | ntact Assignments | (continued) |

|----------------------|------------------|-------------------|-------------|

|----------------------|------------------|-------------------|-------------|

#### Package Information and Contact Assignments

|    | -           | 7           | e            | 4           | 5          | 9          | 2            | 8   | 6                    | 10                 | 11                        | 12            | 13         | 14         | 15        | 16        | 17        | 18        | 19           | 20          | 21          | 22           | 23          | 24          | 25          |

|----|-------------|-------------|--------------|-------------|------------|------------|--------------|-----|----------------------|--------------------|---------------------------|---------------|------------|------------|-----------|-----------|-----------|-----------|--------------|-------------|-------------|--------------|-------------|-------------|-------------|

| M  | CSI0_DAT10  | CSI0_DAT12  | CSI0_DAT11   | CSI0_DAT14  | CSI0_DAT15 | CSI0_DAT18 | HDMI_VPH     | GND | VDDARM23_IN          | GND                | VDDARM23_CAP              | GND           | VDDARM_CAP | VDDARM_IN  | GND       |           | VDDPU_CAP | GND       | NVCC_EIM2    | EIM_DA11    | EIM_DA9     | EIM_DA10     | EIM_DA13    | EIM_DA12    | EIM_WAIT    |

| z  | CSI0_DAT4   | CSI0_VSYNC  | CSI0_DAT7    | CSI0_DAT6   | CSI0_DAT9  | CSI0_DAT8  | NVCC_CSI     | GND | VDDARM23_IN          | GND                | VDDARM23_CAP              | VDD_CACHE_CAP | VDDARM_CAP | VDDARM_IN  | GND       | VDDSOC_IN | VDDPU_CAP | GND       | DI0_DISP_CLK | DI0_PIN3    | DI0_PIN15   | EIM_BCLK     | EIM_DA14    | EIM_DA15    | DI0_PIN2    |

| ٩. | CSI0_PIXCLK | CSI0_DAT5   | CSI0_DATA_EN | CSI0_MCLK   | GPIO_19    | GPIO_18    | NVCC_GPIO    | GND | VDDARM23_IN          | GND                | VDDARM23_CAP              | GND           | VDDARM_CAP | VDDARM_IN  | GND       | VDDSOC_IN | VDDPU_CAP | GND       | NVCC_LCD     | DISP0_DAT4  | DISP0_DAT3  | DISP0_DAT1   | DISP0_DAT2  | DISP0_DAT0  | DI0_PIN4    |

| æ  | GPIO_17     | GPIO_16     | GPIO_7       | GPIO_5      | GPIO_8     | GPIO_4     | GPIO_3       | GND | VDDARM23_IN          | VDDSOC_CAP         | VDDARM23_CAP VDDARM23_CAP | GND           | VDDARM_CAP | VDDARM_IN  | GND       |           | GND       | NVCC_DRAM | NVCC_ENET    | DISP0_DAT13 | DISP0_DAT10 | DISP0_DAT8   | DISP0_DAT6  | DISP0_DAT7  | DISP0_DAT5  |

| F  | GPIO_2      | GPIO_9      | GPIO_6       | GPIO_1      | GPIO_0     | KEY_COL4   | KEY_ROW3     | GND | ARM23_IN VDDARM23_IN | SOC_CAP VDDSOC_CAP | GND                       | GND           | VDDSOC_CAP | VDDSOC_CAP | GND       |           | GND       | NVCC_DRAM | GND          | DISP0_DAT21 | DISP0_DAT16 | DISP0_DAT15  | DISP0_DAT11 | DISP0_DAT12 | DISP0_DAT9  |

| Þ  | LVDS0_TX0_P | LVDS0_TX0_N | LVDS0_TX1_P  | LVDS0_TX1_N | KEY_COL3   | KEY_ROW1   | KEY_COL1     | GND | VDDARM23_IN          | VDDSOC_CAP         | GND                       | GND           | VDDSOC_CAP | VDDSOC_CAP | GND       | VDDSOC_IN | GND       | NVCC_DRAM | GND          | ENET_TXD0   | ENET_CRS_DV | DISP0_DAT20  | DISP0_DAT19 | DISP0_DAT17 | DISP0_DAT14 |

| >  | LVDS0_TX2_P | LVDS0_TX2_N | LVDS0_CLK_P  | LVDS0_CLK_N | KEY_ROW4   | KEY_ROW0   | NVCC_LVDS2P5 | GND | NVCC_DRAM            | NVCC_DRAM          | NVCC_DRAM                 | NVCC_DRAM     | NVCC_DRAM  | NVCC_DRAM  | NVCC_DRAM | NVCC_DRAM | NVCC_DRAM | NVCC_DRAM | GND          | ENET_MDC    | ENET_TX_EN  | ENET_REF_CLK | ENET_MDIO   | DISP0_DAT22 | DISP0_DAT18 |

| M  | LVDS0_TX3_P | LVDS0_TX3_N | GND          | KEY_ROW2    | KEY_COL0   | KEY_COL2   | GND          | GND | GND                  | GND                | GND                       | GND           | GND        | DRAM_A4    | GND       | GND       | GND       | GND       | GND          | ENET_TXD1   | ENET_RXD0   | ENET_RXD1    | ENET_RX_ER  | DISP0_DAT23 | DRAM_D63    |